Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 12                                                                           |

| Program Memory Size        | 14KB (8K x 14)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                               |

| Supplier Device Package    | 14-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15325t-i-sl |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

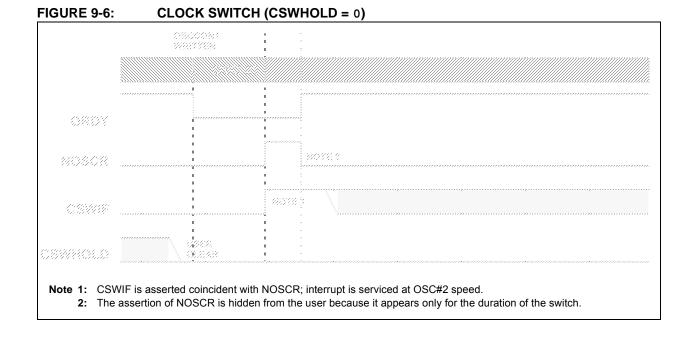

Changing the clock post-divider without changing the clock source (e.g., changing Fosc from 1 MHz to 2 MHz) is handled in the same manner as a clock source change, as described previously. The clock source will already be active, so the switch is relatively quick. CSWHOLD must be clear (CSWHOLD = 0) for the switch to complete.

The current COSC and CDIV are indicated in the OSCCON2 register up to the moment when the switch actually occurs, at which time OSCCON2 is updated and ORDY is set. NOSCR is cleared by hardware to indicate that the switch is complete.

#### 9.3.2 PLL INPUT SWITCH

Switching between the PLL and any non-PLL source is managed as described above. The input to the PLL is established when NOSC selects the PLL, and maintained by the COSC setting.

When NOSC and COSC select the PLL with different input sources, the system continues to run using the COSC setting, and the new source is enabled per NOSC. When the new oscillator is ready (and CSWHOLD = 0), system operation is suspended while the PLL input is switched and the PLL acquires lock.

Note: If the PLL fails to lock, the FSCM will trigger.

### 9.3.3 CLOCK SWITCH AND SLEEP

If OSCCON1 is written with a new value and the device is put to Sleep before the switch completes, the switch will not take place and the device will enter Sleep mode.

When the device wakes from Sleep and the CSWHOLD bit is clear, the device will wake with the 'new' clock active, and the clock switch interrupt flag bit (CSWIF) will be set.

When the device wakes from Sleep and the CSWHOLD bit is set, the device will wake with the 'old' clock active and the new clock will be requested again.

| Name    | Bit 7   | Bit 6   | Bit 5          | Bit 4  | Bit 3     | Bit 2     | Bit 1     | Bit 0   | Register<br>on Page |

|---------|---------|---------|----------------|--------|-----------|-----------|-----------|---------|---------------------|

| OSCCON1 | —       |         | NOSC<2:0>      |        |           | NDIV<3:0> |           |         |                     |

| OSCCON2 | —       |         | COSC<2:0>      |        |           | CDIV<     | 3:0>      |         | 113                 |

| OSCCON3 | CSWHOLD | SOSCPWR | SOSCPWR — ORDY |        |           | —         | —         | —       | 114                 |

| PCON0   | STKOVF  | STKUNF  | WDTWV          | RWDT   | RMCLR     | RI        | POR       | BOR     | 102                 |

| STATUS  |         | —       | _              | TO     | PD        | Z         | DC        | С       | 36                  |

| WDTCON0 |         | —       |                |        | WDTPS<4:0 | )>        |           | SWDTEN  | 153                 |

| WDTCON1 |         | V       | VDTCS<2:0>     |        | _         | WI        | NDOW<2:0> | >       | 154                 |

| WDTPSL  |         |         | PSCNT<7:       |        | T<7:0>    | <7:0>     |           |         |                     |

| WDTPSH  |         |         | PSCNT<15:8>    |        |           |           |           | 155     |                     |

| WDTTMR  |         |         | WDTTM          | R<4:0> |           | STATE     | PSCNT     | <17:16> | 155                 |

#### TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

**Legend:** – = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 12-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5   | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1    | Bit 8/0  | Register<br>on Page |

|---------|------|---------|---------|------------|----------|----------|----------|------------|----------|---------------------|

|         | 13:8 |         | _       | FCMEN      | _        | CSWEN    | _        | _          | CLKOUTEN | 00                  |

| CONFIG1 | 7:0  | _       | F       | RSTOSC<2:0 | >        | _        | F        | EXTOSC<2:0 | >        | 80                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

#### 14.2.6 ANALOG CONTROL

The ANSELA register (Register 14-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with its TRIS bit clear and its ANSEL bit set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELA bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 14.2.7 WEAK PULL-UP CONTROL

The WPUA register (Register 14-5) controls the individual weak pull-ups for each PORT pin.

#### 14.2.8 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic or by enabling an analog output, such as the DAC. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

| R = Readable bitW = Writable bitu = Bit is unchangedx = Bit is unknown |                      |         |         | U = Unimplemented bit, read as '0'<br>-n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

|------------------------------------------------------------------------|----------------------|---------|---------|---------------------------------------------------------------------------------------------|---------|---------|---------|--|--|

| Legend:                                                                | :                    |         |         |                                                                                             |         |         |         |  |  |

| bit 7                                                                  | 7                    |         |         |                                                                                             |         |         | bit 0   |  |  |

| ODCC7 <sup>(1)</sup>                                                   | ODCC6 <sup>(1)</sup> | ODCC5   | ODCC4   | ODCC3                                                                                       | ODCC2   | ODCC1   | ODCC0   |  |  |

| R/W-0/0                                                                | R/W-0/0              | R/W-0/0 | R/W-0/0 | R/W-0/0                                                                                     | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

#### REGISTER 14-22: ODCONC: PORTC OPEN-DRAIN CONTROL REGISTER

bit 7-0 **ODCC<7:0>:** PORTC Open-Drain Enable bits For RC<7:0> pins, respectively 1 = Port pin operates as open-drain drive (sink current only) 0 = Port pin operates as standard push-pull drive (source and sink current)

'0' = Bit is cleared

**Note 1:** Present on PIC16(L)F15345 only.

1' = Bit is set

#### REGISTER 14-23: SLRCONC: PORTC SLEW RATE CONTROL REGISTER

| R/W-1/1              | R/W-1/1              | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| SLRC7 <sup>(1)</sup> | SLRC6 <sup>(1)</sup> | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SLRC<7:0>: PORTC Slew Rate Enable bits For RC<7:0> pins, respectively 1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

Note 1: Present on PIC16(L)F15345 only.

#### REGISTER 14-24: INLVLC: PORTC INPUT LEVEL CONTROL REGISTER

| R/W-1/1                | R/W-1/1                | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|------------------------|------------------------|---------|---------|---------|---------|---------|---------|

| INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 |

| bit 7                  |                        |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

INLVLC<7:0>: PORTC Input Level Select bits

For RC<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

Note 1: Present on PIC16(L)F15345 only.

# TABLE 15-6: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE (CONTINUED)

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0 | Register<br>on page |

|-----------------------|-------|-------|-------|-------|-------|---------|-------|-------|---------------------|

| RC1PPS                | —     | -     | —     |       |       | RC1PPS< | 4:0>  |       | 200                 |

| RC2PPS                | —     | _     | —     |       |       | RC2PPS< | 4:0>  |       | 200                 |

| RC3PPS                | —     | _     | —     |       |       | RC3PPS< | 4:0>  |       | 200                 |

| RC4PPS                | _     | _     | —     |       |       | RC4PPS< | 4:0>  |       | 200                 |

| RC5PPS                | _     | _     | _     |       |       | RC5PPS< | 4:0>  |       | 200                 |

| RC6PPS <sup>(1)</sup> | —     | _     | —     |       |       | RC6PPS< | 4:0>  |       | 200                 |

| RC7PPS <sup>(1)</sup> | _     | _     | —     |       |       | RC7PPS< | 4:0>  |       | 200                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

Note 1: Present on PIC16(L)F15345 only.

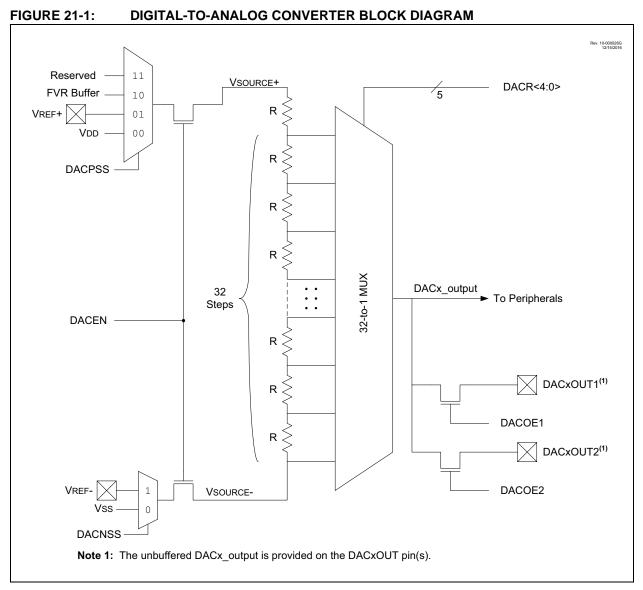

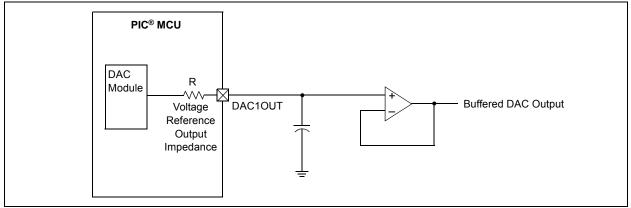

#### FIGURE 21-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

© 2016 Microchip Technology Inc.

DS40001865B-page 240

# 21.4 Operation During Sleep

The DAC continues to function during Sleep. When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DAC1CON0 register are not affected.

# 21.5 Effects of a Reset

A device Reset affects the following:

- DAC is disabled.

- DAC output voltage is removed from the DAC10UT1/2 pins.

- The DAC1R<4:0> range select bits are cleared.

# PIC16(L)F15325/45

| R/W-0/0          | U-0                           | R-0                             | R/W-0/0         | R/W-0/0             | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|-------------------------------|---------------------------------|-----------------|---------------------|------------------|------------------|-------------|

| T0EN             |                               | TOOUT                           | T016BIT         |                     | TOOUT            | PS<3:0>          |             |

| bit 7            |                               |                                 |                 | •                   |                  |                  | bit C       |

|                  |                               |                                 |                 |                     |                  |                  |             |

| Legend:          |                               |                                 |                 |                     |                  |                  |             |

| R = Readable     | e bit                         | W = Writable                    | bit             | U = Unimplen        | nented bit, read | 1 as '0'         |             |

| u = Bit is uncl  | hanged                        | x = Bit is unk                  | nown            | -n/n = Value a      | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |                               | '0' = Bit is cle                | ared            |                     |                  |                  |             |

|                  |                               |                                 |                 |                     |                  |                  |             |

| bit 7            | TOEN: Timer(                  | ) Enable bit<br>lule is enabled | and operating   |                     |                  |                  |             |

|                  |                               |                                 |                 | a<br>vest power mod | de               |                  |             |

| bit 6            |                               | ted: Read as                    |                 | ·                   |                  |                  |             |

| bit 5            | TOOUT: Time                   | r0 Output bit (                 | read-only)      |                     |                  |                  |             |

|                  | Timer0 output                 |                                 | 5,              |                     |                  |                  |             |

| bit 4            |                               | er0 Operating                   |                 | er Select bit       |                  |                  |             |

|                  |                               | a 16-bit timer                  |                 |                     |                  |                  |             |

|                  |                               | an 8-bit timer                  |                 |                     |                  |                  |             |

| bit 3-0          | 11111 = 1:16                  |                                 | itput postscale | er (divider) seled  | CT DITS          |                  |             |

|                  | 1110 = 1:15                   |                                 |                 |                     |                  |                  |             |

|                  | 1101 <b>= 1:14  </b>          | Postscaler                      |                 |                     |                  |                  |             |

|                  | 1100 <b>= 1:13  </b>          |                                 |                 |                     |                  |                  |             |

|                  | 1011 <b>= 1:12</b>            |                                 |                 |                     |                  |                  |             |

|                  | 1010 = 1:11                   |                                 |                 |                     |                  |                  |             |

|                  | 1001 = 1:10  <br>1000 = 1:9 P |                                 |                 |                     |                  |                  |             |

|                  | 0111 = <b>1</b> :8 P          |                                 |                 |                     |                  |                  |             |

|                  | 0110 = 1:7 P                  |                                 |                 |                     |                  |                  |             |

|                  | 0101 <b>= 1:6</b> P           |                                 |                 |                     |                  |                  |             |

|                  | 0100 <b>= 1:5</b> P           | ostscaler                       |                 |                     |                  |                  |             |

|                  | 0011 <b>= 1:4 P</b>           | ostscaler                       |                 |                     |                  |                  |             |

|                  | 0010 = 1:3 P                  | ostscaler                       |                 |                     |                  |                  |             |

|                  | 0001 = 1:2 P                  | ostscaler                       |                 |                     |                  |                  |             |

#### 27.5.6 EDGE-TRIGGERED ONE-SHOT MODE

The Edge-Triggered One-Shot modes start the timer on an edge from the external signal input, after the ON bit is set, and clear the ON bit when the timer matches the PRx period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 01001)

- Falling edge (MODE<4:0> = 01010)

- Rising or Falling edge (MODE<4:0> = 01011)

If the timer is halted by clearing the ON bit then another TMRx\_ers edge is required after the ON bit is set to resume counting. Figure 27-9 illustrates operation in the rising edge One-Shot mode.

When Edge-Triggered One-Shot mode is used in conjunction with the CCP then the edge-trigger will activate the PWM drive and the PWM drive will deactivate when the timer matches the CCPRx pulse width value and stay deactivated when the timer halts at the PRx period count match.

#### FIGURE 27-9: EDGE-TRIGGERED ONE-SHOT MODE TIMING DIAGRAM (MODE = 01001)

|                              | Rev. 10.0002008<br>519/0016                                                                                                                                  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE                         | 0b01001                                                                                                                                                      |

| TMRx_clk                     |                                                                                                                                                              |

| PRx                          | 5                                                                                                                                                            |

| Instruction <sup>(1)</sup> — | BSF BSF                                                                                                                                                      |

| ON                           |                                                                                                                                                              |

| TMRx_ers                     |                                                                                                                                                              |

| TMRx                         | $0 \qquad \begin{pmatrix} 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \qquad \end{pmatrix} \qquad 0 \qquad \begin{pmatrix} 1 \\ 2 \\ 2 \\ 2 \\ 2 \\ 2 \\ 2 \\ 2 \\ 2 \\ 2 \\$ |

| CCP_pset                     |                                                                                                                                                              |

| TMRx_postscaled              |                                                                                                                                                              |

| PWM Duty<br>Cycle            | 3                                                                                                                                                            |

| PWM Output                   |                                                                                                                                                              |

| R/W-x/u          | R/W-x/u      | R/W-x/u                                | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|--------------|----------------------------------------|-----------------|----------------|------------------|------------------|-------------|

| LCxG3D4T         | LCxG3D4N     | LCxG3D3T                               | LCxG3D3N        | LCxG3D2T       | LCxG3D2N         | LCxG3D1T         | LCxG3D1N    |

| bit 7            |              |                                        |                 |                |                  |                  | bit (       |

|                  |              |                                        |                 |                |                  |                  |             |

| Legend:          |              |                                        |                 |                |                  | ( <b>a</b> )     |             |

| R = Readable     |              | W = Writable                           |                 |                | nented bit, read |                  |             |

| u = Bit is unch  | anged        | x = Bit is unkr                        |                 | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |              | '0' = Bit is clea                      | ared            |                |                  |                  |             |

| bit 7            |              | Noto 2 Doto 4 1                        | True (non inve  | rtad) bit      |                  |                  |             |

|                  |              | Gate 2 Data 4 1<br>(true) is gated i   |                 | ,              |                  |                  |             |

|                  |              | (true) is not gate                     |                 |                |                  |                  |             |

| bit 6            |              | Gate 2 Data 4 I                        |                 |                |                  |                  |             |

|                  |              | (inverted) is ga                       | •               |                |                  |                  |             |

|                  |              | (inverted) is no                       |                 |                |                  |                  |             |

| bit 5            | LCxG3D3T: 0  | Gate 2 Data 3 1                        | rue (non-inve   | rted) bit      |                  |                  |             |

|                  | 1 = CLCIN2 ( | (true) is gated i                      | nto CLCx Gate   | e 2            |                  |                  |             |

|                  | 0 = CLCIN2   | (true) is not gat                      | ed into CLCx    | Gate 2         |                  |                  |             |

| bit 4            | LCxG3D3N:    | Gate 2 Data 3                          | Negated (inver  | rted) bit      |                  |                  |             |

|                  |              | (inverted) is ga                       |                 |                |                  |                  |             |

|                  |              | (inverted) is no                       | •               |                |                  |                  |             |

| bit 3            |              | Gate 2 Data 2 T                        | · ·             |                |                  |                  |             |

|                  |              | (true) is gated i<br>(true) is not gat |                 |                |                  |                  |             |

| bit 2            |              | Gate 2 Data 2                          |                 |                |                  |                  |             |

|                  |              | (inverted) is ga                       | • ·             | ,              |                  |                  |             |

|                  |              | (inverted) is no                       |                 |                |                  |                  |             |

| bit 1            |              | Sate 2 Data 1 1                        | •               |                |                  |                  |             |

|                  |              | (true) is gated i                      |                 | ,              |                  |                  |             |

|                  | 0 = CLCIN0   | (true) is not gat                      | ted into CLCx   | Gate 2         |                  |                  |             |

| bit 0            | LCxG3D1N:    | Gate 2 Data 1 I                        | Negated (inver  | rted) bit      |                  |                  |             |

|                  |              | (inverted) is ga                       |                 |                |                  |                  |             |

|                  | 0 = CLCIN0   | (inverted) is no                       | t gated into Cl | Cx Gate 2      |                  |                  |             |

# REGISTER 31-9: CLCxGLS2: GATE 2 LOGIC SELECT REGISTER

| TABLE 31-4: | SUMMARY OF REGISTERS ASSOCIATED WITH CLCx (continued) |

|-------------|-------------------------------------------------------|

|-------------|-------------------------------------------------------|

| Name      | Bit 7 | Bit 6 | Bit 5    | Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0                   |          |          |          |          |     |  |

|-----------|-------|-------|----------|-------------------------------------------------------|----------|----------|----------|----------|-----|--|

| CLC4GLS1  | —     | _     | LC4G2D3T | LC4G2D3N                                              | LC4G2D2T | LC4G2D2N | LC4G2D1T | LC4G2D1N | 369 |  |

| CLC4GLS2  | -     | _     | LC4G3D3T | LC4G3D3N                                              | LC4G3D2T | LC4G3D2N | LC4G3D1T | LC4G3D1N | 370 |  |

| CLC4GLS3  | _     | _     | LC4G4D3T | LC4G4D3T LC4G4D3N LC4G4D2T LC4G4D2N LC4G4D1T LC4G4D1N |          |          |          |          |     |  |

| CLCIN0PPS | _     | _     |          | CLCIN0PPS<5:0>                                        |          |          |          |          |     |  |

| CLCIN1PPS | -     | _     |          | CLCIN1PPS<5:0>                                        |          |          |          |          |     |  |

| CLCIN2PPS | _     | _     |          | CLCIN2PPS<5:0>                                        |          |          |          |          |     |  |

| CLCIN3PPS | _     | _     |          |                                                       | CLCIN3   | PPS<5:0> |          |          | 199 |  |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the CLCx modules.

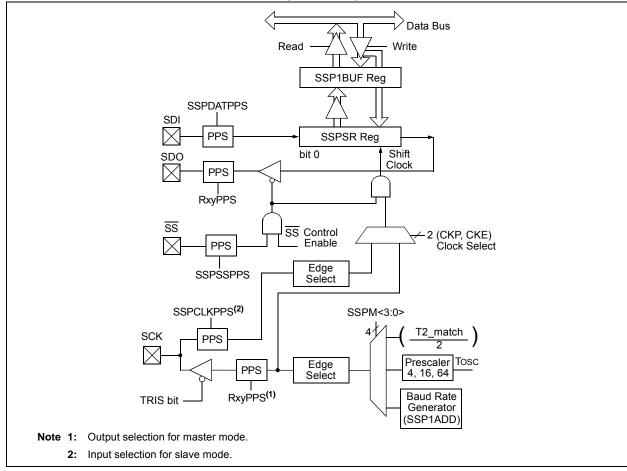

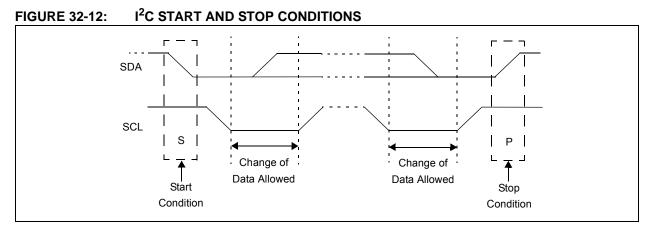

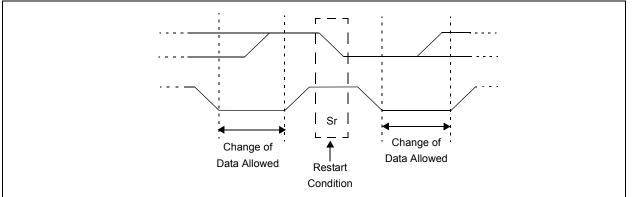

# 32.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP1) MODULE

# 32.1 MSSP Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 32-1 is a block diagram of the SPI interface module.

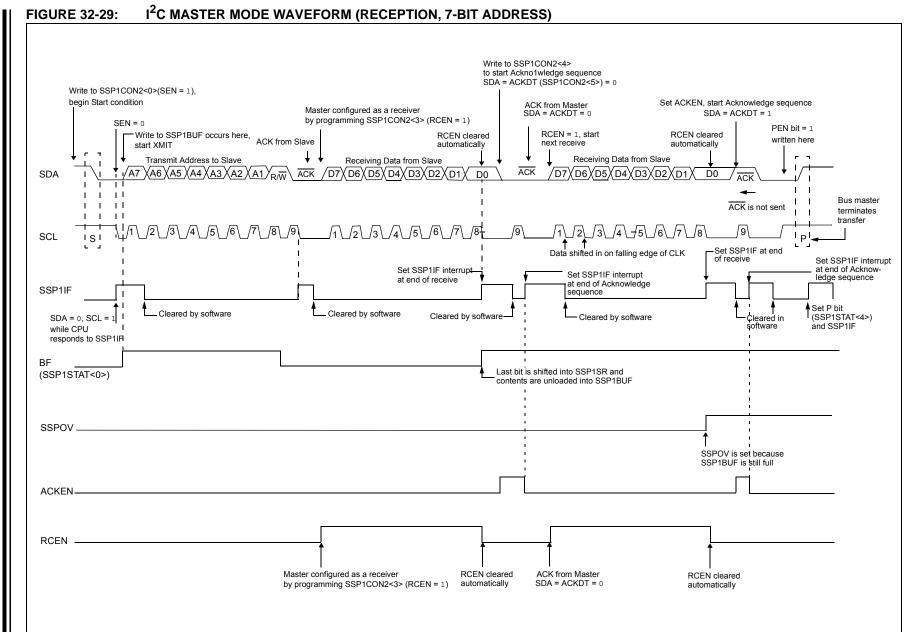

#### 32.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{\text{ACK}}$  is placed in the ACKSTAT bit of the SSP1CON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the  $\overline{ACK}$  value sent back to the transmitter. The ACKDT bit of the SSP1CON2 register is set/cleared to determine the response.

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSP1STAT register or the SSPOV bit of the SSP1CON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSP1CON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

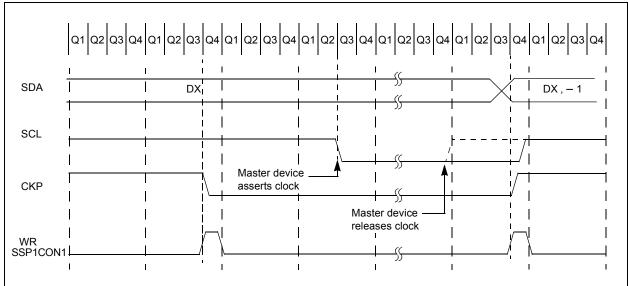

#### 32.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low, effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSP1CON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

#### 32.5.6.1 Normal Clock Stretching

Following an ACK if the R/W bit of SSP1STAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSP1BUF with data to transfer to the master. If the SEN bit of SSP1CON2 is set, the slave hardware will always stretch the clock after the ACK sequence. Once the slave is ready; CKP is set by software and communication resumes.

#### 32.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSP1ADD.

#### 32.5.6.3 Byte NACKing

When AHEN bit of SSP1CON3 is set; CKP is cleared by hardware after the eighth falling edge of SCL for a received matching address byte. When DHEN bit of SSP1CON3 is set; CKP is cleared after the eighth falling edge of SCL for received data.

Stretching after the eighth falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

# 32.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 32-23).

#### FIGURE 32-23: CLOCK SYNCHRONIZATION TIMING

PIC16(L)F15325/45

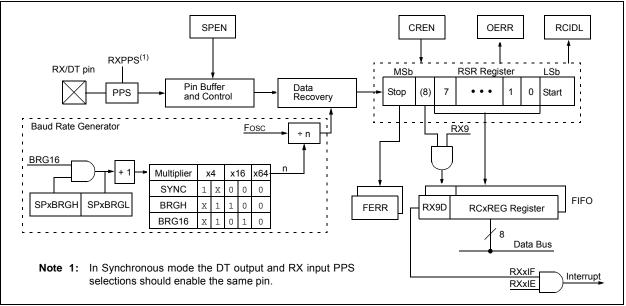

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXxSTA)

- Receive Status and Control (RCxSTA)

- Baud Rate Control (BAUDxCON)

These registers are detailed in Register 33-1, Register 33-2 and Register 33-3, respectively.

The RX input pin is selected with the RXPPS. The CK input is selected with the TXPPS register. TX, CK, and DT output pins are selected with each pin's RxyPPS register. Since the RX input is coupled with the DT output in Synchronous mode, it is the user's responsibility to select the same pin for both of these functions when operating in Synchronous mode. The EUSART control logic will control the data direction drivers automatically.

| TABLE          | ABLE 37-3:     POWER-DOWN CURRENT (IPD) <sup>(1,2)</sup>                |                                          |                                                                                                    |                                                                       |               |                |       |                   |                       |  |

|----------------|-------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------|----------------|-------|-------------------|-----------------------|--|

| PIC16LF        | PIC16LF15325/45 Standard Operating Conditions (unless otherwise stated) |                                          |                                                                                                    |                                                                       |               |                |       | otherwise stated) |                       |  |

| PIC16F15325/45 |                                                                         |                                          |                                                                                                    | Standard Operating Conditions (unless otherwise stated)<br>VREGPM = 1 |               |                |       |                   |                       |  |

| Param.<br>No.  | Symbol                                                                  | Device Characteristics                   | Min.                                                                                               | Тур.†                                                                 | Max.<br>+85°C | Max.<br>+125°C | Units | VDD               | Conditions<br>Note    |  |

| D200           | IPD                                                                     | IPD Base                                 | -                                                                                                  | 0.06                                                                  | 2             | 9              | μΑ    | 3.00              | $\langle \rangle$     |  |

| D200           | IPD                                                                     | IPD Base                                 | _                                                                                                  | 0.4                                                                   | 4             | 12             | /#A   | 3.0V              | $\langle \rangle$     |  |

| D200A          |                                                                         |                                          | _                                                                                                  | 18                                                                    | 22            | 27 🔇           | ДĄ    | 3.0∀              | VREGPM = 0            |  |

| D201           | IPD_WDT                                                                 | Low-Frequency Internal<br>Oscillator/WDT | —                                                                                                  | 0.8                                                                   | 4.0           | 11.5           | \μÀ   | 73.0₩             | /                     |  |

| D201           | IPD_WDT                                                                 | Low-Frequency Internal<br>Oscillator/WDT | —                                                                                                  | 0.9                                                                   | 5.0 <         | 13             | μA    | 3.0V              |                       |  |

| D202           | IPD_SOSC                                                                | Secondary Oscillator (SOSC)              | -                                                                                                  | 0.6                                                                   | <u>_</u> 5_   | 13             | μA    | 3.0V              |                       |  |

| D202           | IPD_SOSC                                                                | Secondary Oscillator (SOSC)              | _                                                                                                  | 0.8                                                                   | 8.5           | 15             | μÀ    | 3.0V              |                       |  |

| D203           | IPD_FVR                                                                 | FVR                                      | -                                                                                                  | 33                                                                    | 47            | 47             | μA    | 3.0V              |                       |  |

| D203           | IPD_FVR                                                                 | FVR                                      | _                                                                                                  | 28                                                                    | 44            | 44             | μΑ    | 3.0V              |                       |  |

| D204           | IPD_BOR                                                                 | Brown-out Reset (BOR)                    |                                                                                                    | 10                                                                    | 17            | 19             | μΑ    | 3.0V              |                       |  |

| D204           | IPD_BOR                                                                 | Brown-out Reset (BOR)                    | Ź                                                                                                  | 14                                                                    | 18            | > 20           | μΑ    | 3.0V              |                       |  |

| D205           | IPD_LPBOR                                                               | Low-Power Brown-out Reset (LPBOR)        | $\langle - \rangle$                                                                                | 0.5                                                                   | 4             | 10             | μΑ    | 3.0V              |                       |  |

| D207           | IPD_ADCA                                                                | ADC - Active                             | /-                                                                                                 | 250                                                                   | $\searrow$    | _              | μΑ    | 3.0V              | ADC is converting (4) |  |

| D207           | IPD_ADCA                                                                | ADC - Active                             | P                                                                                                  | 280                                                                   | _             |                | μΑ    | 3.0V              | ADC is converting (4) |  |

| D208           | IPD_CMP                                                                 | Comparator                               | $\left( \left( \left$ | 30                                                                    | 42            | 44             | μΑ    | 3.0V              |                       |  |

| D208           | IPD_CMP                                                                 | Comparator                               |                                                                                                    | 33                                                                    | 44            | 45             | μΑ    | 3.0V              |                       |  |

# v(1 2)

Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

Note 1: The peripheral current is the sum of the base IDD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max. values should be used when calculating total current consumption.

The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part 2: in Sleep mode with all I/O pins in high-impedance state and tied to Vss.

All peripheral ourrents listed are on a per-peripheral basis if more than one instance of a peripheral is available. 3:

4: ADC clock source is FRC, 5: = F device

| TABLE 37-9: PLL SPECIFICATIONS | TABLE 37-9: | PLL SPECIFICATIONS |

|--------------------------------|-------------|--------------------|

|--------------------------------|-------------|--------------------|

|               | •••••      | 0 0                                         |          |       |                     | Δ                 |            |

|---------------|------------|---------------------------------------------|----------|-------|---------------------|-------------------|------------|

| Standar       | d Operatir | ng Conditions (unless otherwise stated) VD  | D ≥ 2.5V |       |                     | $\langle \rangle$ |            |

| Param.<br>No. | Sym.       | Characteristic                              | Min.     | Тур†  | Max.                | Units             | Conditions |

| PLL01         | FPLLIN     | PLL Input Frequency Range                   | 4        | _     | 8                   | MHz               | $\searrow$ |

| PLL02         | FPLLOUT    | PLL Output Frequency Range                  | 16       | —     | 32                  | MHz               | Note 1     |

| PLL03         | TPLLST     | PLL Lock Time from Start-up                 | _        | 200 🦯 | $\langle - \rangle$ | _µ\$              | -          |

| PLL04         | FPLLJIT    | PLL Output Frequency Stability (Jitter)     | -0.25    | _ \   | 0.25                | ~%/               |            |

| *             | These p    | arameters are characterized but not tested. |          |       |                     |                   |            |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

Note 1: The output frequency of the PLL must meet the Fosc requirements listed in Parameter D002.

| Param. | Symbol  | Characteristic         |              | Min.       | Max. | Units | Conditions                                  |  |  |

|--------|---------|------------------------|--------------|------------|------|-------|---------------------------------------------|--|--|

| No.    | C y     | onaraota               |              |            | maxi | onno  | Conditions                                  |  |  |

| SP100* | Тнідн   | Clock high time        | 100 kHz mode | 4.0        | _    | μS    | Device must operate at a minimum of 1.5 MHz |  |  |

|        |         |                        | 400 kHz mode | 0.6        | —    | μS    | Device must operate at a minimum of 10 MHz  |  |  |

|        |         |                        | SSP module   | 1.5Tcy     |      |       |                                             |  |  |

| SP101* | TLOW    | Clock low time         | 100 kHz mode | 4.7        | —    | μS    | Device must operate at a minimum of 1.5 MHz |  |  |

|        |         |                        | 400 kHz mode | 1.3        | _    | μS    | Device must operate at a minimum of 10 MHz  |  |  |

|        |         |                        | SSP module   | 1.5Tcy     | _    |       |                                             |  |  |

| SP102* | TR      | SDA and SCL rise       | 100 kHz mode | —          | 1000 | ns    |                                             |  |  |

|        | time    |                        | 400 kHz mode | 20 + 0.1CB | 300  | ns    | CB is specified to be from 10-400 pF        |  |  |

| SP103* | TF      | SDA and SCL fall time  | 100 kHz mode | —          | 250  | ns    |                                             |  |  |

|        |         |                        | 400 kHz mode | 20 + 0.1CB | 250  | ns    | CB is specified to be from 10-400 pF        |  |  |

| SP106* | THD:DAT | Data input hold time   | 100 kHz mode | 0          | _    | ns    |                                             |  |  |

|        |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                             |  |  |

| SP107* | TSU:DAT | Data input setup time  | 100 kHz mode | 250        | _    | ns    | (Note 2)                                    |  |  |

|        |         |                        | 400 kHz mode | 100        | _    | ns    |                                             |  |  |

| SP109* | ΤΑΑ     | Output valid from      | 100 kHz mode | —          | 3500 | ns    | (Note 1)                                    |  |  |

|        |         | clock                  | 400 kHz mode | —          | _    | ns    |                                             |  |  |

| SP110* | TBUF    |                        | 100 kHz mode | 4.7        | _    | μs    | Time the bus must be free                   |  |  |

|        |         |                        | 400 kHz mode | 1.3        | —    | μs    | before a new transmission can start         |  |  |

| SP111  | Св      | Bus capacitive loading |              | _          | 400  | pF    |                                             |  |  |

# TABLE 37-25: I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + Tsu:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

# 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |                |          |      |  |  |

|-------------------------|-------------|----------------|----------|------|--|--|

| Dimension               | Limits      | MIN            | NOM      | MAX  |  |  |

| Number of Terminals     | N           | 20             |          |      |  |  |

| Pitch                   | е           |                | 0.50 BSC |      |  |  |

| Overall Height          | Α           | 0.45           | 0.50     | 0.55 |  |  |

| Standoff                | A1          | 0.00           | 0.02     | 0.05 |  |  |

| Terminal Thickness      | A3          | 0.127 REF      |          |      |  |  |

| Overall Width           | E           | 4.00 BSC       |          |      |  |  |

| Exposed Pad Width       | E2          | 2.60 2.70 2.80 |          |      |  |  |

| Overall Length          | D           | 4.00 BSC       |          |      |  |  |

| Exposed Pad Length      | D2          | 2.60           | 2.70     | 2.80 |  |  |

| Terminal Width          | b           | 0.20 0.25 0.30 |          |      |  |  |

| Terminal Length         | L           | 0.30 0.40 0.50 |          |      |  |  |

| Terminal-to-Exposed-Pad | К           | 0.20           | -        | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-255A Sheet 2 of 2