Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 224 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 20-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15345-e-p |

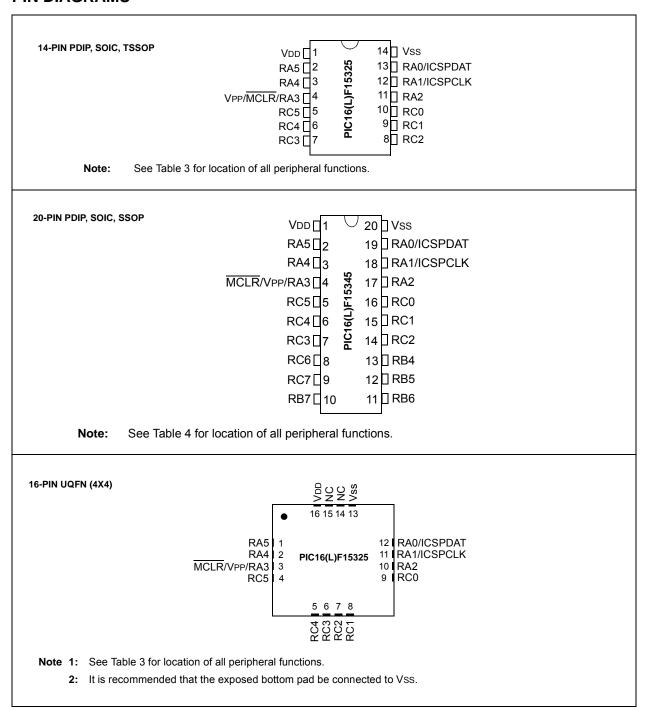

## **PIN DIAGRAMS**

Program Flash Memory RAM **PORTA** Timing Generation CLKOUT /OSC2 **EXTOSC** CPU Oscillator CLKIN/ OSC1 (Note 3) SOSCIN/ SOSCI Secondary Oscillator (SOSC) sosco MCLR ⊠→ ADC 10-bit PWM6 PWM5 PWM4 PWM3 Timer2 Timer1 Timer0 C2 C1 TIM DAC FVR

PIC16(L)F15325/45

#### FIGURE 1-1: PIC16(L)F15325 BLOCK DIAGRAM

Note 1: See applicable chapters for more information on peripherals.

EUSART2

2: See Table 1-1 for peripherals available on specific devices.

MSSP1

CLC4

CLC3

CLC2

CLC1

ZCD1

CCP1

CCP2

**3:** See Figure 3-1.

NCO1

EUSART2

CWG1

**TABLE 1-2:** PIC16(L)F15325 PINOUT DESCRIPTION

| Name                                                                          | Function              | Input<br>Type | Output Type | Description                                                         |

|-------------------------------------------------------------------------------|-----------------------|---------------|-------------|---------------------------------------------------------------------|

| RA0/ANA0/C1IN0+/DAC1OUT/<br>ICSPDAT/IOCA0                                     | RA0                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| ICSPDAT/IOCAU                                                                 | ANA0                  | AN            | _           | ADC Channel A0 input.                                               |

|                                                                               | C1IN0+                | AN            | _           | Comparator 1 positive input.                                        |

|                                                                               | DAC1OUT               | _             | AN          | Digital-to-Analog Converter output.                                 |

|                                                                               | ICSPDAT               | ST            | CMOS        | In-Circuit Serial Programming™ and debugging data input/<br>output. |

|                                                                               | IOCA0                 | TTL/ST        | _           | Interrupt-on-change input.                                          |

| RA1/ANA1/VREF+/C1IN0-/C2IN0-/<br>DAC1REF+/T0CKI <sup>(1)</sup> /ICSPCLK/IOCA1 | RA1                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| DACTREF TOOK! TICSF CENTOCAT                                                  | ANA1                  | AN            | _           | ADC Channel A1 input.                                               |

|                                                                               | VREF+                 | AN            | _           | External ADC and/or DAC positive reference input.                   |

|                                                                               | C1IN0-                | AN            | _           | Comparator 1 negative input.                                        |

|                                                                               | C2IN0-                | AN            | _           | Comparator 2 negative input.                                        |

|                                                                               | DAC1REF+              | TTL/ST        | AN          | DAC positive reference.                                             |

|                                                                               | T0CKI <sup>(1)</sup>  | TTL/ST        | _           | Timer0 clock input.                                                 |

|                                                                               | ICSPCLK               | ST            | _           | In-Circuit Serial Programming™ and debugging clock input.           |

|                                                                               | IOCA1                 | TTL/ST        | _           | Interrupt-on-change input.                                          |

| RA2/ANA2/CWG1IN <sup>(1)</sup> /ZCD1/INT <sup>(1)</sup> /                     | RA2                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| IOCA2                                                                         | ANA2                  | AN            | _           | ADC Channel A2 input.                                               |

|                                                                               | CWG1IN <sup>(1)</sup> | TTL/ST        | _           | Complementary Waveform Generator 1 input.                           |

|                                                                               | ZCD1                  | AN            | AN          | Zero-cross detect input pin (with constant current sink/ source).   |

|                                                                               | INT <sup>(1)</sup>    | TTL/ST        | _           | External interrupt request input.                                   |

|                                                                               | IOCA2                 | TTL/ST        | _           | Interrupt-on-change input.                                          |

| RA3/MCLR/Vpp/IOCA3                                                            | RA3                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

|                                                                               | MCLR                  | ST            | _           | Master clear input with internal weak pull up resistor.             |

|                                                                               | VPP                   | HV            | _           | ICSP™ High-Voltage Programming mode entry input.                    |

|                                                                               | IOCA3                 | TTL/ST        | _           | Interrupt-on-change input.                                          |

| RA4/ANA4/C1IN1-/T1G <sup>(1)</sup> /SOSCO/                                    | RA4                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| CLKOUT/OSC2/IOCA4                                                             | ANA4                  | AN            | _           | ADC Channel A4 input.                                               |

|                                                                               | C1IN1-                | AN            | _           | Comparator 1 negative input.                                        |

|                                                                               | T1G <sup>(1)</sup>    | ST            | _           | Timer1 Gate input.                                                  |

|                                                                               | SOSCO                 | _             | AN          | 32.768 kHz secondary oscillator crystal driver output.              |

|                                                                               | CLKOUT                | _             | CMOS/OD     | Fosc/4 digital output (in non-crystal/resonator modes).             |

|                                                                               | OSC2                  |               | XTAL        | External Crystal/Resonator (LP, XT, HS modes) driver output.        |

|                                                                               | IOCA4                 | TTL/ST        | _           | Interrupt-on-change input.                                          |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output

OD = Open-Drain

TTL = TTL compatible input HV = High Voltage

ST = Schmitt Trigger input with CMOS levels

= Schmitt Trigger input with I<sup>2</sup>C

Note

XTAL = Crystal levels

1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx

pins. Refer to Table 15-3 for details on which PORT pins may be used for this signal.

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin

options as described in Table 15-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

TABLE 4-9: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (ALL BANKS)

| Bank Offset<br>Bank 0-Bank 63 | Name      | Bit 7      | Bit 6                                                                                                                   | Bit 5     | Bit 4       | Bit 3       | Bit 2 | Bit 1     | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-------------------------------|-----------|------------|-------------------------------------------------------------------------------------------------------------------------|-----------|-------------|-------------|-------|-----------|-----------|-----------------------|----------------------------|

| All Banks                     | All Banks |            |                                                                                                                         |           |             |             |       |           |           |                       |                            |

| x00h or x80h                  | INDF0     |            | dressing this location uses contents of FSR0H/FSR0L to address data memory (not a sysical register)                     |           |             |             |       | xxxx xxxx | xxxx xxxx |                       |                            |

| x01h or x81h                  | INDF1     |            | dressing this location uses contents of FSR1H/FSR1L to address data memory (not a sixxx xxxx xxxx xxxx xxxx xxxx xxxx x |           |             |             |       | xxxx xxxx | xxxx xxxx |                       |                            |

| x02h or x82h                  | PCL       |            | PCL                                                                                                                     |           |             |             |       | 0000 0000 | 0000 0000 |                       |                            |

| x03h or x83h                  | STATUS    | _          | _                                                                                                                       | _         | TO          | PD          | Z     | DC        | С         | 1 1000                | q quuu                     |

| x04h or x84h                  | FSR0L     | FSR0L      | ROL Indirect Data Memory Address 0 Low Pointer 0                                                                        |           |             |             |       | 0000 0000 | uuuu uuuu |                       |                            |

| x05h or x85h                  | FSR0H     | FSR0H      | Indirect Da                                                                                                             | ta Memory | Address 0 I | High Pointe | r     |           |           | 0000 0000             | 0000 0000                  |

| x06h or x86h                  | FSR1L     | FSR1L      | Indirect Da                                                                                                             | ta Memory | Address 1 I | _ow Pointer | •     |           |           | 0000 0000             | uuuu uuuu                  |

| x07h or x87h                  | FSR1H     | FSR1H      | Indirect Da                                                                                                             | ta Memory | Address 1 I | High Pointe | r     |           |           | 0000 0000             | 0000 0000                  |

| x08h or x88h                  | BSR       | _          | _                                                                                                                       |           |             | BSR         | <5:0> |           |           | 00 0000               | 00 0000                    |

| x09h or x89h                  | WREG      | Working Re | Working Register 0000 0000                                                                                              |           |             |             |       | 0000 0000 | uuuu uuuu |                       |                            |

| x0Ah or x8Ah                  | PCLATH    | _          | — Write Buffer for the upper 7 bits of the Program Counter −000 0000                                                    |           |             |             |       | -000 0000 |           |                       |                            |

| x0Bh or x8Bh                  | INTCON    | GIE        | PEIE                                                                                                                    | _         | _           | _           | _     | _         | INTEDG    | 001                   | 001                        |

**Legend:** x = unknown, u = unchanged, q = depends on condition, -= unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: These Registers can be accessed from any bank.

TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address             | Name                | Bit 7         | Bit 6             | Bit 5             | Bit 4 | Bit 3 | Bit 2    | Bit 1   | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------------------|---------------------|---------------|-------------------|-------------------|-------|-------|----------|---------|---------|-----------------------|----------------------------|

| Bank 61 (C          | Bank 61 (Continued) |               |                   |                   |       |       |          |         |         |                       |                            |

| 1EC5h               | SSP1CLKPPS          | _             | — SSP1CLKPPS<5:0> |                   |       |       |          |         | 01 0011 | uu uuuu               |                            |

| 1EC6h               | SSP1DATPPS          | _             | _                 | — SSP1DATPPS<5:0> |       |       |          | 01 0100 | uu uuuu |                       |                            |

| 1EC7h               | SSP1SSPPS           | _             |                   |                   |       |       |          | 00 0101 | uu uuuu |                       |                            |

| 1EC8h<br>—<br>1ECAh |                     | Unimplemented |                   |                   |       |       |          | _       | _       |                       |                            |

| 1ECBh               | RX1DTPPS            | _             | _                 |                   |       | RX1DT | PPS<5:0> |         |         | 01 0111               | uu uuuu                    |

| 1ECCh               | TX1CKPPS            | _             | _                 |                   |       | TX1CK | PPS<5:0> |         |         | 01 0110               | uu uuuu                    |

| 1ECDh               | RX2DTPPS            | _             | _                 |                   |       | RX2DT | PPS<5:0> |         |         | 00 1111               | uu uuuu                    |

| 1ECEh               | TX2CKPPS            | _             | _                 | TX2CKPPS<5:0>     |       |       |          | 00 1110 | uu uuuu |                       |                            |

| 1ECFh<br>—<br>1EEFh |                     | Unimplemented |                   |                   |       |       | _        | _       |         |                       |                            |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

## 14.7 Register Definitions: PORTC

### **REGISTER 14-17: PORTC: PORTC REGISTER**

| R/W-x/u            | R/W-x/u            | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|--------------------|--------------------|---------|---------|---------|---------|---------|---------|

| RC7 <sup>(2)</sup> | RC6 <sup>(2)</sup> | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     |

| bit 7              |                    |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1)</sup>

1 = Port pin is  $\geq$  VIH 0 = Port pin is  $\leq$  VIL

Note 1: Writes to PORTC are actually written to corresponding LATC register. The actual I/O pin values are read from

the PORTC register.

2: Present on PIC16(L)F15345 only.

### **REGISTER 14-18: TRISC: PORTC TRI-STATE REGISTER**

|   | R/W-1/1               | R/W-1/1               | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|---|-----------------------|-----------------------|---------|---------|---------|---------|---------|---------|

|   | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| ĺ | bit 7                 |                       |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 TRISC<7:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

Note 1: Present on PIC16(L)F15345 only.

#### **REGISTER 14-19: LATC: PORTC DATA LATCH REGISTER**

| R/W-x/u              | R/W-x/u              | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| LATC7 <sup>(2)</sup> | LATC6 <sup>(2)</sup> | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

Note 1: Writes to PORTC are actually written to corresponding LATC register. The actual I/O pin values are read from the PORTC register.

2: Present on PIC16(L)F15345 only.

### REGISTER 17-4: IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| IOCBP7  | IOCBP6  | IOCBP5  | IOCBP4  | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-4 **IOCBP<7:4>:** Interrupt-on-Change PORTB Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive-going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

bit 3-0 **Unimplemented:** read as '0'

### REGISTER 17-5: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-4 IOCBN<7:4>: Interrupt-on-Change PORTB Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative-going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

bit 3-0 **Unimplemented:** read as '0'

### 22.2 FIXED DUTY CYCLE MODE

In Fixed Duty Cycle (FDC) mode, every time the accumulator overflows (NCO\_overflow), the output is toggled at a frequency rate half of the FOVERFLOW. This provides a 50% duty cycle, provided that the increment value remains constant. For more information, see Figure 22-2.

The FDC mode is selected by clearing the N1PFM bit in the NCO1CON register.

### 22.3 PULSE FREQUENCY MODE

In Pulse Frequency (PF) mode, every time the Accumulator overflows, the output becomes active for one or more clock periods. Once the clock period expires, the output returns to an inactive state. This provides a pulsed output. The output becomes active on the rising clock edge immediately following the overflow event. For more information, see Figure 22-2.

The value of the active and inactive states depends on the polarity bit, N1POL in the NCO1CON register.

The PF mode is selected by setting the N1PFM bit in the NCO1CON register.

### 22.3.1 OUTPUT PULSE WIDTH CONTROL

When operating in PF mode, the active state of the output can vary in width by multiple clock periods. Various pulse widths are selected with the N1PWS<2:0> bits in the NCO1CLK register.

When the selected pulse width is greater than the Accumulator overflow time frame, then NCO1 output does not toggle.

### 22.4 OUTPUT POLARITY CONTROL

The last stage in the NCO module is the output polarity. The N1POL bit in the NCO1CON register selects the output polarity. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

The NCO output signal (NCO1\_out) is available to the following peripherals:

- CLC

- CWG

- Timer1

- Timer2

- CLKR

### 22.5 Interrupts

When the accumulator overflows (NCO\_overflow), the NCO Interrupt Flag bit, NCO1IF, of the PIR7 register is set. To enable the interrupt event (NCO\_interrupt), the following bits must be set:

- · N1EN bit of the NCO1CON register

- · NCO1IE bit of the PIE7 register

- PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt must be cleared by software by clearing the NCO1IF bit in the Interrupt Service Routine.

### 22.6 Effects of a Reset

All of the NCO registers are cleared to zero as the result of a Reset.

### 22.7 Operation in Sleep

The NCO module operates independently from the system clock and will continue to run during Sleep, provided that the clock source selected remains active.

The HFINTOSC remains active during Sleep when the NCO module is enabled and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the NCO clock source, when the NCO is enabled, the CPU will go idle during Sleep, but the NCO will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

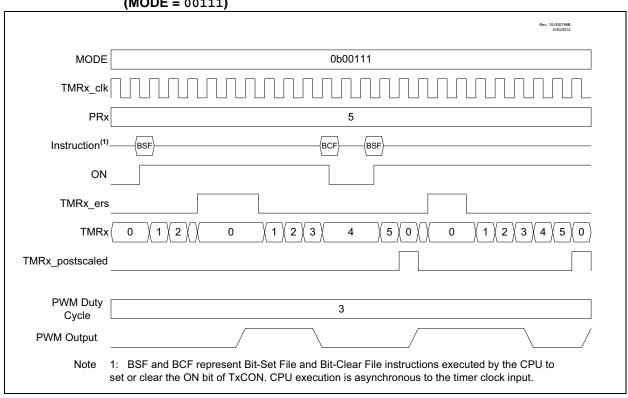

## 27.5.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

In the Level-Triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMRx\_ers, as shown in Figure 27-7. Selecting MODE<4:0> = 00110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 00111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMRx\_ers = 1. ON is controlled by BSF and BCF instructions. When ON = 0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the PRx value or two clock periods after the external Reset signal goes true and stays true.

The timer starts counting, and the PWM output is set high, on either the clock following the PRx match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

FIGURE 27-7: LEVEL-TRIGGERED HARDWARE LIMIT MODE TIMING DIAGRAM (MODE = 00111)

## REGISTER 30-6: CWG1AS1: CWG1 AUTO-SHUTDOWN CONTROL REGISTER 1

| U-1   | U-1 | U-1 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|---------|---------|---------|

| _     | _   | _   | AS4E    | AS3E    | AS2E    | AS1E    | AS0E    |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| Unimplemented: Read as '0'                              |

|---------------------------------------------------------|

| AS4E: CLC2 Output bit                                   |

| 1 = LC2_out shut-down is enabled                        |

| 0 = LC2_out shut-down is disabled                       |

| AS3E: Comparator C2 Output bit                          |

| 1 = C2 output shut-down is enabled                      |

| 0 = C2 output shut-down is disabled                     |

| AS2E: Comparator C1 Output bit                          |

| 1 = C1 output shut-down is enabled                      |

| 0 = C1 output shut-down is disabled                     |

| AS1E: TMR2 Postscale Output bit                         |

| 1 = TMR2 Postscale shut-down is enabled                 |

| 0 = TMR2 Postscale shut-down is disabled                |

| AS0E: CWG1 Input Pin bit                                |

| 1 = Input pin selected by CWG1PPS shut-down is enabled  |

| 0 = Input pin selected by CWG1PPS shut-down is disabled |

|                                                         |

### 32.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- · Serial Clock (SCK)

- Serial Data Out (SDO)

- · Serial Data In (SDI)

- Slave Select (SS)

Figure 32-1 shows the block diagram of the MSSP module when operating in SPI mode.

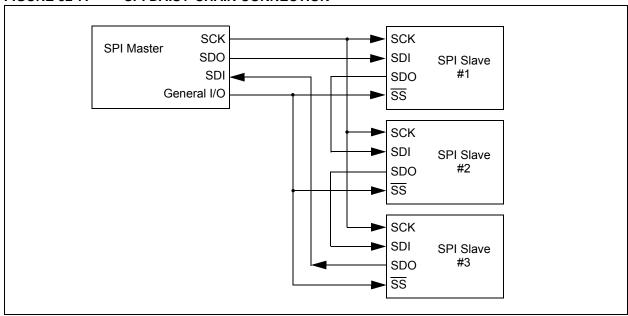

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 32-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. Data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 32-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDO output pin which is connected to, and received by, the slave's SDI input pin. The slave device transmits information out on its SDO output pin, which is connected to, and received by, the master's SDI input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register. During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDO pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data

- Master sends useful data and slave sends useful data

- Master sends dummy data and slave sends useful data

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

FIGURE 32-7: SPI DAISY-CHAIN CONNECTION

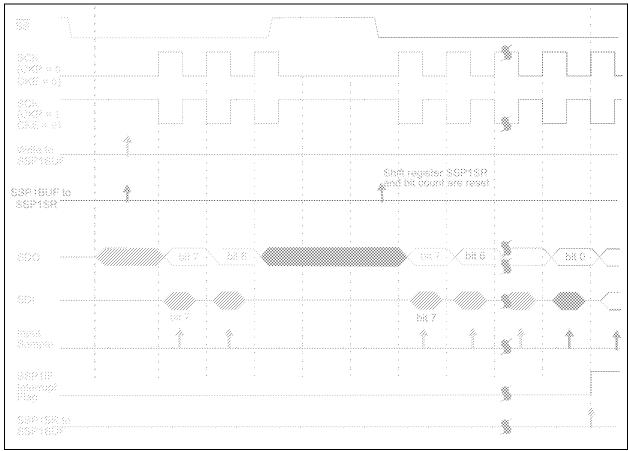

FIGURE 32-8: SLAVE SELECT SYNCHRONOUS WAVEFORM

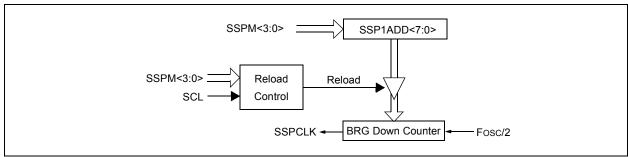

### 32.7 BAUD RATE GENERATOR

The MSSP module has a Baud Rate Generator available for clock generation in both I<sup>2</sup>C and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSP1ADD register (Register 32-6). When a write occurs to SSP1BUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 32-40 triggers the value from SSP1ADD to be loaded into the BRG counter. This occurs twice for each oscillation of the

module clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP is being operated in.

Table 32-4 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSP1ADD.

### **EQUATION 32-1:**

$$FCLOCK = \frac{FOSC}{(SSP1ADD + I)(4)}$$

FIGURE 32-40: BAUD RATE GENERATOR BLOCK DIAGRAM

Note: Values of 0x00, 0x01 and 0x02 are not valid for SSP1ADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

TABLE 32-2: MSSP CLOCK RATE W/BRG

| Fosc   | Fcy   | BRG Value | FCLOCK<br>(2 Rollovers of BRG) |

|--------|-------|-----------|--------------------------------|

| 32 MHz | 8 MHz | 13h       | 400 kHz                        |

| 32 MHz | 8 MHz | 19h       | 308 kHz                        |

| 32 MHz | 8 MHz | 4Fh       | 100 kHz                        |

| 16 MHz | 4 MHz | 09h       | 400 kHz                        |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                        |

| 16 MHz | 4 MHz | 27h       | 100 kHz                        |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                        |

**Note:** Refer to the I/O port electrical specifications in Table 37-4 to ensure the system is designed to support IoL requirements.

## 33.6 Register Definitions: EUSART Control

### REGISTER 33-1: TXxSTA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-/0 | R/W-0/0 | R/W-0/0             | R/W-0/0 | R/W-0/0 | R/W-0/0 | R-1/1 | R/W-0/0 |

|--------|---------|---------------------|---------|---------|---------|-------|---------|

| CSRC   | TX9     | TXEN <sup>(1)</sup> | SYNC    | SENDB   | BRGH    | TRMT  | TX9D    |

| bit 7  |         |                     |         |         |         |       | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 CSRC: Clock Source Select bit

Asynchronous mode:

Unused in this mode - value ignored

Synchronous mode:

1 = Master mode (clock generated internally from BRG)

0 = Slave mode (clock from external source)

bit 6 TX9: 9-bit Transmit Enable bit

1 = Selects 9-bit transmission0 = Selects 8-bit transmission

bit 5 **TXEN:** Transmit Enable bit<sup>(1)</sup>

1 = Transmit enabled

0 = Transmit disabled

bit 4 SYNC: EUSART Mode Select bit

1 = Synchronous mode0 = Asynchronous mode

bit 3 **SENDB:** Send Break Character bit

Asynchronous mode:

1 = Send SYNCH BREAK on next transmission – Start bit, followed by 12 '0' bits, followed by Stop

bit; cleared by hardware upon completion

0 = SYNCH BREAK transmission disabled or completed

Synchronous mode:

Unused in this mode - value ignored

bit 2 BRGH: High Baud Rate Select bit

Asynchronous mode:

1 = High speed

0 = Low speed

Synchronous mode:

Unused in this mode – value ignored

bit 1 TRMT: Transmit Shift Register Status bit

1 = TSR empty 0 = TSR full

bit 0 **TX9D:** Ninth bit of Transmit Data

Can be address/data bit or a parity bit.

Note 1: SREN/CREN overrides TXEN in Sync mode.

### REGISTER 33-2: RCxSTA: RECEIVE STATUS AND CONTROL REGISTER

| R/W-0/0             | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R-0/0 | R-0/0 | R-0/0 |

|---------------------|---------|---------|---------|---------|-------|-------|-------|

| SPEN <sup>(1)</sup> | RX9     | SREN    | CREN    | ADDEN   | FERR  | OERR  | RX9D  |

| bit 7               |         |         |         |         |       |       | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 SPEN: Serial Port Enable bit<sup>(1)</sup>

1 = Serial port enabled

0 = Serial port disabled (held in Reset)

bit 6 **RX9:** 9-Bit Receive Enable bit

1 = Selects 9-bit reception 0 = Selects 8-bit reception

bit 5 SREN: Single Receive Enable bit

Asynchronous mode:

Unused in this mode – value ignored

Synchronous mode - Master:

1 = Enables single receive

0 = Disables single receive

This bit is cleared after reception is complete.

Synchronous mode - Slave

Unused in this mode - value ignored

bit 4 CREN: Continuous Receive Enable bit

Asynchronous mode:

1 = Enables continuous receive until enable bit CREN is cleared

0 = Disables continuous receive

Synchronous mode:

1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)

0 = Disables continuous receive

bit 3 ADDEN: Address Detect Enable bit

Asynchronous mode 9-bit (RX9 = 1):

1 = Enables address detection – enable interrupt and load of the receive buffer when the ninth bit in the receive buffer is set

0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit

Asynchronous mode 8-bit (RX9 = 0):

Unused in this mode – value ignored

bit 2 **FERR:** Framing Error bit

1 = Framing error (can be updated by reading RCxREG register and receive next valid byte)

0 = No framing error

bit 1 **OERR:** Overrun Error bit

1 = Overrun error (can be cleared by clearing bit CREN)

0 = No overrun error

bit 0 RX9D: Ninth bit of Received Data

This can be address/data bit or a parity bit and must be calculated by user firmware.

**Note 1:** The EUSART module automatically changes the pin from tri-state to drive as needed. Configure the associated TRIS bits for TX/CK and RX/DT to 1.

## 36.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- · Byte Oriented

- · Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 36-3 lists the instructions recognized by the MPASM  $^{\text{TM}}$  assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine entry takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 36.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

TABLE 36-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                  |

| W     | Working register (accumulator)                                                                                                                                        |

| b     | Bit address within an 8-bit file register                                                                                                                             |

| k     | Literal field, constant data or label                                                                                                                                 |

| х     | Don't care location (= 0 or 1).  The assembler will generate code with x = 0.  It is the recommended form of use for compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                         |

| n     | FSR or INDF number. (0-1)                                                                                                                                             |

| mm    | Prepost increment-decrement mode selection                                                                                                                            |

# TABLE 36-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |

|-------|-----------------|

| PC    | Program Counter |

| TO    | Time-Out bit    |

| С     | Carry bit       |

| DC    | Digit Carry bit |

| Z     | Zero bit        |

| PD    | Power-Down bit  |

| MOVWI            | Move W to INDFn                                                                                                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVWI ++FSRn<br>[ label ] MOVWIFSRn<br>[ label ] MOVWI FSRn++<br>[ label ] MOVWI FSRn<br>[ label ] MOVWI k[FSRn]                                                                                                                       |

| Operands:        | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ -32 \leq k \leq 31 \end{array}$                                                                                                                                                         |

| Operation:       | W → INDFn  Effective address is determined by  • FSR + 1 (preincrement)  • FSR - 1 (predecrement)  • FSR + k (relative offset)  After the Move, the FSR value will be either:  • FSR + 1 (all increments)  • FSR - 1 (all decrements)  Unchanged |

| Status Affected: | None                                                                                                                                                                                                                                             |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h-FFFFh.

Incrementing/decrementing it beyond these bounds will cause it to

wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP                                                        | No Operation                                                                                                                                                                                   |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                    | [ label ] NOP                                                                                                                                                                                  |

| Operands:                                                  | None                                                                                                                                                                                           |

| Operation:                                                 | No operation                                                                                                                                                                                   |

| Status Affected:                                           | None                                                                                                                                                                                           |

| Description:                                               | No operation.                                                                                                                                                                                  |

| Words:                                                     | 1                                                                                                                                                                                              |

| Cycles:                                                    | 1                                                                                                                                                                                              |

| Example:                                                   | NOP                                                                                                                                                                                            |

|                                                            |                                                                                                                                                                                                |

| RESET                                                      | Software Reset                                                                                                                                                                                 |

| Syntax:                                                    | [ label ] RESET                                                                                                                                                                                |

| Syntax:<br>Operands:                                       | [ label ] RESET None                                                                                                                                                                           |

| Syntax:                                                    | [ label ] RESET None                                                                                                                                                                           |

| Syntax:<br>Operands:                                       | [ label ] RESET  None  Execute a device Reset. Resets the                                                                                                                                      |

| Syntax:<br>Operands:<br>Operation:                         | [ label ] RESET  None  Execute a device Reset. Resets the RI flag of the PCON register.                                                                                                        |

| Syntax: Operands: Operation: Status Affected:              | [ label ] RESET  None  Execute a device Reset. Resets the RI flag of the PCON register.  None  This instruction provides a way to execute a hardware Reset by software.  Return from Interrupt |

| Syntax: Operands: Operation: Status Affected: Description: | [ label ] RESET  None  Execute a device Reset. Resets the RI flag of the PCON register.  None  This instruction provides a way to execute a hardware Reset by software.                        |

| Syntax: Operands: Operation: Status Affected: Description: | [ label ] RESET  None  Execute a device Reset. Resets the RI flag of the PCON register.  None  This instruction provides a way to execute a hardware Reset by software.  Return from Interrupt |

| RETFIE           | Return from Interrupt                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] RETFIE k                                                                                                                                                                               |

| Operands:        | None                                                                                                                                                                                             |

| Operation:       | $\begin{aligned} TOS &\to PC, \\ 1 &\to GIE \end{aligned}$                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                             |

| Description:     | Return from Interrupt. Stack is POPed and Top-of-Stack (TOS) is loaded in the PC. Interrupts are enabled by setting Global Interrupt Enable bit, GIE (INTCON<7>). This is a 2-cycle instruction. |

| Words:           | 1                                                                                                                                                                                                |

| Cycles:          | 2                                                                                                                                                                                                |

| Example:         | RETFIE                                                                                                                                                                                           |

|                  | After Interrupt PC = TOS                                                                                                                                                                         |

GIE =

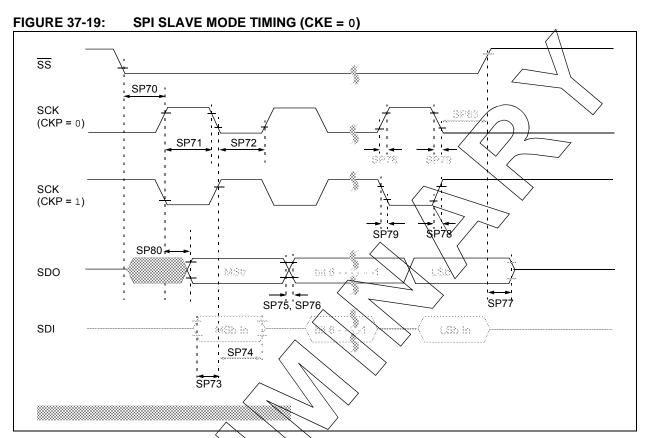

SPI SLAVE MODE TIMING (CKE = 1) FIGURE 37-20: SS SCK (CKP = 0)SP72 SCK (CKP \$ SP80 MSb bit 6 LSb SØ0 ► SP77 → **←** SP75, SP76 SDI LSb In MSb In SP74

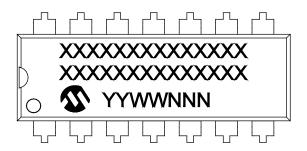

## 40.0 PACKAGING INFORMATION

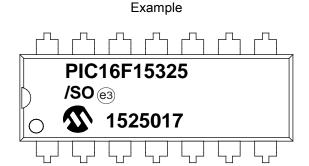

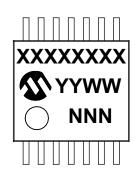

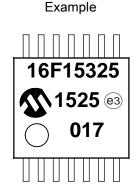

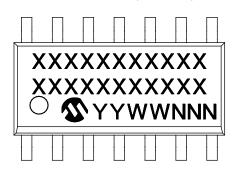

## 40.1 Package Marking Information

14-Lead PDIP (300 mil)

14-Lead TSSOP (4.4 mm)

14-Lead SOIC (3.90 mm)

**Legend:** XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3) can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

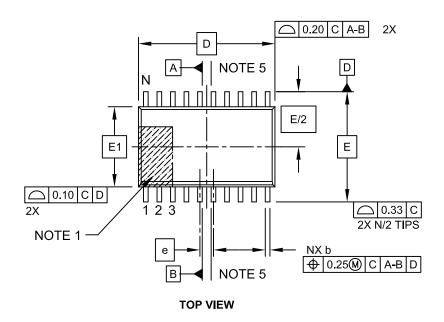

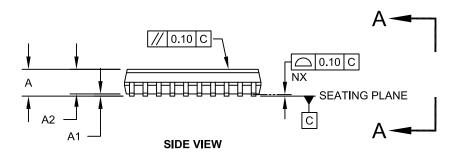

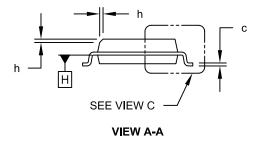

## 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**ote:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-094C Sheet 1 of 2