#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 20-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15345-e-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| lame               | Function              | Input<br>Type | Output Type | Description                                        |

|--------------------|-----------------------|---------------|-------------|----------------------------------------------------|

| DUT <sup>(2)</sup> | C1OUT                 | _             | CMOS/OD     | Comparator 1 output.                               |

|                    | C2OUT                 | _             | CMOS/OD     | Comparator 2 output.                               |

|                    | SDO1                  | _             | CMOS/OD     | MSSP1 SPI serial data output.                      |

|                    | SCK1                  | _             | CMOS/OD     | MSSP1 SPI serial clock output.                     |

|                    | DT1 <sup>(3)</sup>    | _             | CMOS/OD     | EUSART Synchronous mode data output.               |

|                    | TX1                   | _             | CMOS/OD     | EUSART1 Asynchronous mode transmitter data output. |

|                    | CK1                   | _             | CMOS/OD     | EUSART1 Synchronous mode clock output.             |

|                    | DT2 <sup>(3)</sup>    | _             | CMOS/OD     | EUSART Synchronous mode data output.               |

|                    | TX2                   | _             | CMOS/OD     | EUSART2 Asynchronous mode transmitter data output. |

|                    | CK2                   | _             | CMOS/OD     | EUSART2 Synchronous mode clock output.             |

|                    | SCL1 <sup>(3,4)</sup> | _             | CMOS/OD     | MSSP1 I <sup>2</sup> C output.                     |

|                    | SDA1 <sup>(3,4)</sup> | _             | CMOS/OD     | MSSP1 I <sup>2</sup> C output.                     |

|                    | DT1 <sup>(3)</sup>    |               | CMOS/OD     | EUSART Synchronous mode data output.               |

|                    | TMR0                  | _             | CMOS/OD     | Timer0 output.                                     |

|                    | CCP1                  | _             | CMOS/OD     | CCP1 output (compare/PWM functions).               |

|                    | CCP2                  | _             | CMOS/OD     | CCP2 output (compare/PWM functions).               |

|                    | PWM3OUT               | _             | CMOS/OD     | PWM3 output.                                       |

|                    | PWM4OUT               |               | CMOS/OD     | PWM4 output.                                       |

|                    | PWM5OUT               |               | CMOS/OD     | PWM5 output.                                       |

|                    | PWM6OUT               |               | CMOS/OD     | PWM6 output.                                       |

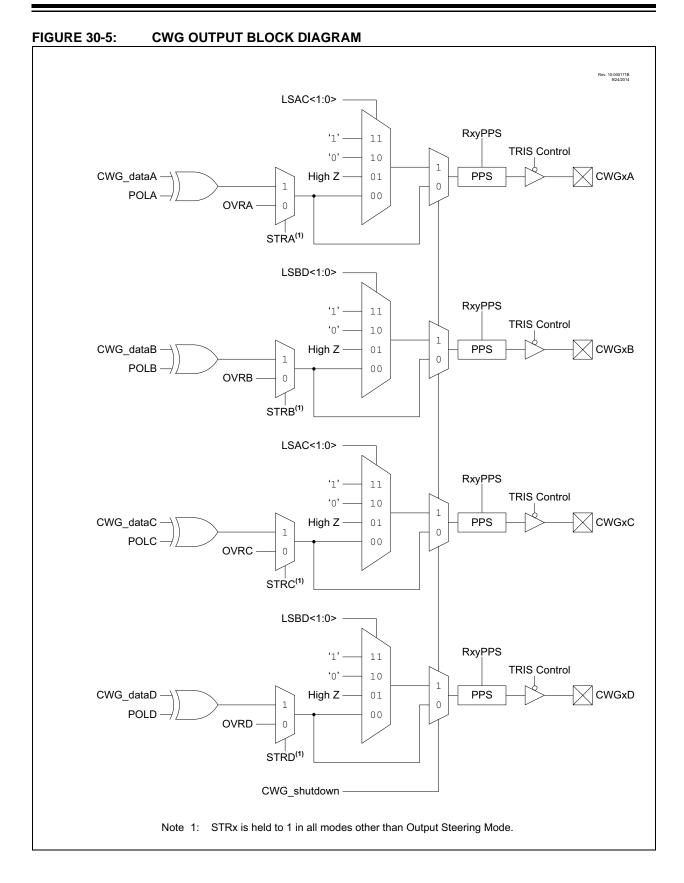

|                    | CWG1A                 |               | CMOS/OD     | Complementary Waveform Generator 1 output A.       |

|                    | CWG1B                 |               | CMOS/OD     | Complementary Waveform Generator 1 output B.       |

|                    | CWG1C                 |               | CMOS/OD     | Complementary Waveform Generator 1 output C.       |

|                    | CWG1D                 | _             | CMOS/OD     | Complementary Waveform Generator 1 output D.       |

|                    | CLC1OUT               | _             | CMOS/OD     | Configurable Logic Cell 1 output.                  |

|                    | CLC2OUT               | _             | CMOS/OD     | Configurable Logic Cell 2 output.                  |

|                    | CLC3OUT               | _             | CMOS/OD     | Configurable Logic Cell 3 output.                  |

|                    | CLC4OUT               | _             | CMOS/OD     | Configurable Logic Cell 4 output.                  |

|                    | NCO10UT               | _             | CMOS/OD     | Numerically Controller Oscillator output.          |

|                    | CLKR                  | _             | CMOS/OD     | Clock Reference module output.                     |

TABLE 1-3: PIC16(L)F15345 PINOUT DESCRIPTION (CONTINUED)

HV = High Voltage XTAL = Crystal levels

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-3 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

5: For 14/16-pin package only.

6: For 20-pin package only

| Address | Name     | Bit 7    | Bit 6    | Bit 5    | Bit 4         | Bit 3             | Bit 2     | Bit 1       | Bit 0    | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|----------|----------|----------|----------|---------------|-------------------|-----------|-------------|----------|-----------------------|----------------------------|

| Bank 60 |          |          |          |          |               |                   |           |             |          |                       |                            |

|         |          |          |          | CPU COF  | RE REGISTERS; | see Table 4-3 for | specifics |             |          |                       |                            |

| 1E0Ch   | _        |          |          |          | Unimpler      | mented            |           |             |          | _                     | —                          |

| 1E0Dh   | _        |          |          |          | Unimpler      | nented            |           |             |          | _                     | -                          |

| 1E0Eh   | _        |          |          |          | Unimpler      | nented            |           |             |          | _                     | -                          |

| 1E0Fh   | CLCDATA  | _        | _        | _        | _             | MLC4OUT           | MLC3OUT   | MLC2OUT     | MLC1OUT  | xxxx                  | uuuu                       |

| 1E10h   | CLCCON   | LC1EN    | _        | LC10UT   | LC1INTP       | LC1INTN           |           | LC1MODE<2:0 | )>       | 0-00 0000             | 0-00 0000                  |

| 1E11h   | CLC1POL  | LC1POL   | _        | _        | —             | LC1G4POL          | LC1G3POL  | LC1G2POL    | LC1G1POL | 0 xxxx                | 0 uuuu                     |

| 1E12h   | CLC1SEL0 | _        |          |          |               | LC1D              | )1S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E13h   | CLC1SEL1 | _        | _        |          |               | LC1D              | )2S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E14h   | CLC1SEL2 | _        | _        |          |               | LC1E              | )3S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E15h   | CLC1SEL3 | _        | _        |          |               | LC1D              | )4S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E16h   | CLC1GLS0 | LC1G1D4T | LC1G4D3N | LC1G1D3T | LC1G1D3N      | LC1G1D2T          | LC1G1D2N  | LC1G1D1T    | LC1G1D1N | xxxx xxxx             | uuuu uuu                   |

| 1E17h   | CLC1GLS1 | LC1G2D4T | LC1G4D3N | LC1G2D3T | LC1G2D3N      | LC1G2D2T          | LC1G2D2N  | LC1G2D1T    | LC1G2D1N | xxxx xxxx             | uuuu uuu                   |

| 1E18h   | CLC1GLS2 | LC1G3D4T | LC1G4D3N | LC1G3D3T | LC1G3D3N      | LC1G3D2T          | LC1G3D2N  | LC1G3D1T    | LC1G3D1N | xxxx xxxx             | uuuu uuu                   |

| 1E19h   | CLC1GLS3 | LC1G4D4T | LC1G4D3N | LC1G4D3T | LC1G4D3N      | LC1G4D2T          | LC1G4D2N  | LC1G4D1T    | LC1G4D1N | xxxx xxxx             | uuuu uuu                   |

| 1E1Ah   | CLC2CON  | LC2EN    | _        | LC2OUT   | LC2INTP       | LC2INTN           |           | LC2MODE<2:0 | )>       | 0-00 0000             | 0-00 000                   |

| 1E1Bh   | CLC2POL  | LC2POL   | _        | _        |               | LC2G4POL          | LC2G3POL  | LC2G2POL    | LC2G1POL | 0 xxxx                | 0 uuu                      |

| 1E1Ch   | CLC2SEL0 | _        | _        |          |               | LC2D              | 01S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E1Dh   | CLC2SEL1 | _        | _        |          |               | LC2D              | )2S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E1Eh   | CLC2SEL2 | _        | _        |          |               | LC2D              | )3S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E1Fh   | CLC2SEL3 | _        | _        |          |               | LC2D              | )4S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E20h   | CLC2GLS0 | LC2G1D4T | LC2G4D3N | LC2G1D3T | LC2G1D3N      | LC2G1D2T          | LC2G1D2N  | LC2G1D1T    | LC2G1D1N | xxxx xxxx             | uuuu uuu                   |

| 1E21h   | CLC2GLS1 | LC2G2D4T | LC2G4D3N | LC2G2D3T | LC2G2D3N      | LC2G2D2T          | LC2G2D2N  | LC2G2D1T    | LC2G2D1N | xxxx xxxx             | uuuu uuu                   |

| 1E22h   | CLC2GLS2 | LC2G3D4T | LC2G4D3N | LC2G3D3T | LC2G3D3N      | LC2G3D2T          | LC2G3D2N  | LC2G3D1T    | LC2G3D1N | xxxx xxxx             | uuuu uuu                   |

| 1E23h   | CLC2GLS3 | LC2G4D4T | LC2G4D3N | LC2G4D3T | LC2G4D3N      | LC2G4D2T          | LC2G4D2N  | LC2G4D1T    | LC2G4D1N | xxxx xxxx             | uuuu uuu                   |

| 1E24h   | CLC3CON  | LC3EN    | —        | LC3OUT   | LC3INTP       | LC3INTN           |           | LC3MODE     |          | 0-00 0000             | 0-00 000                   |

| 1E25h   | CLC3POL  | LC3POL   | —        | —        | —             | LC3G4POL          | LC3G3POL  | LC3G2POL    | LC3G1POL | 0 xxxx                | 0 uuu                      |

| 1E26h   | CLC3SEL0 | —        | —        |          |               | LC3D              | )1S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E27h   | CLC3SEL1 | —        | —        |          |               | LC3D              | )2S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E28h   | CLC3SEL2 | —        | —        |          |               | LC3D              | )3S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E29h   | CLC3SEL3 | —        | —        |          |               | LC3D              | )4S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E2Ah   | CLC3GLS0 | LC3G1D4T | LC3G4D3N | LC3G1D3T | LC3G1D3N      | LC3G1D2T          | LC3G1D2N  | LC3G1D1T    | LC3G1D1N | xxxx xxxx             | นนนน นนนเ                  |

#### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| REGIST  | REGISTER 5-7: REVIS |           |   | REVISIONID: REVISION ID REGISTER |        |           |          |             |         |          |    |   |       |

|---------|---------------------|-----------|---|----------------------------------|--------|-----------|----------|-------------|---------|----------|----|---|-------|

| R       | R                   | R         | R | R                                | R      | R         | R        | R           | R       | R        | R  | R | R     |

| 1       | 0                   |           |   | MJRRE                            | V<5:0> |           |          | MNRREV<5:0> |         |          |    |   |       |

| bit 13  |                     |           |   |                                  |        |           |          |             |         |          |    |   | bit 0 |

|         |                     |           |   |                                  |        |           |          |             |         |          |    |   |       |

| Legend: |                     |           |   |                                  |        |           |          |             |         |          |    |   |       |

|         | R = Read            | lable bit |   |                                  |        |           |          |             |         |          |    |   |       |

|         | '0' = Bit is        | cleared   |   |                                  |        | '1' = Bit | t is set |             | x = Bit | is unkno | wn |   |       |

bit 13-12 **Fixed Value**: Read-only bits These bits are fixed with value '10' for all devices included in this data sheet.

bit 11-6 **MJRREV<5:0>**: Major Revision ID bits These bits are used to identify a major revision. bit 5-0 **MNRREV<5:0>**: Minor Revision ID bits

These bits are used to identify a minor revision.

## 8.3 Register Definitions: Brown-out Reset Control

Legend:

REGISTER 8-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u               | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|-----------------------|-----|-----|-----|-----|-----|-----|--------|

| SBOREN <sup>(1)</sup> | _   | —   | —   | —   | —   | —   | BORRDY |

| bit 7                 |     |     |     |     |     |     | bit 0  |

| -                     |     |     |     |     |     |     |        |

| Logona.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit <sup>(1)</sup> |

|---------|------------------------------------------------------------|

|         | If BOREN <1:0> in Configuration Words $\neq 01$ :          |

|         | SBOREN is read/write, but has no effect on the BOR.        |

|         | If BOREN <1:0> in Configuration Words = 01:                |

|         | 1 = BOR Enabled                                            |

|         | 0 = BOR Disabled                                           |

| bit 6-1 | Unimplemented: Read as '0'                                 |

| bit 0   | BORRDY: Brown-out Reset Circuit Ready Status bit           |

|         | 1 = The Brown-out Reset circuit is active                  |

0 = The Brown-out Reset circuit is inactive

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

## 8.12 Memory Execution Violation

A Memory Execution Violation Reset occurs if executing an instruction being fetched from outside the valid execution area. The different valid execution areas are defined as follows:

- Flash Memory: Table 4-1 shows the addresses available on the PIC16(L)F15325/45 devices based on user Flash size. Execution outside this region generates a memory execution violation.

- Storage Area Flash (SAF): If Storage Area Flash (SAF) is enabled (Section 4.2.3 "Storage Area Flash"), the SAF area (Table 4-2) is not a valid execution area.

Prefetched instructions that are not executed do not cause memory execution violations. For example, a GOTO instruction in the last memory location will prefetch from an invalid location; this is not an error. If an instruction from an invalid location tries to execute, the memory violation is generated immediately, and any concurrent interrupt requests are ignored. When a memory execution violation is generated, the device is reset and flag MEMV is cleared in PCON1 (Register 8-3) to signal the cause. The flag needs to be set in code after a memory execution violation.

| Name                 | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------------------|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|---------------------|

| INTCON               | GIE                   | PEIE                  | -      | -      | _      | _      | -      | INTEDG | 124                 |

| PIE0                 | —                     | —                     | TMR0IE | IOCIE  | _      | _      | _      | INTE   | 125                 |

| IOCAP                | IOCAP7 <sup>(1)</sup> | IOCAP6 <sup>(1)</sup> | IOCAP5 | IOCAP4 | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 213                 |

| IOCAN                | IOCAN7 <sup>(1)</sup> | IOCAN6 <sup>(1)</sup> | IOCAN5 | IOCAN4 | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 213                 |

| IOCAF                | IOCAF7 <sup>(1)</sup> | IOCAF6 <sup>(1)</sup> | IOCAF5 | IOCAF4 | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 214                 |

| IOCBP <sup>(1)</sup> | IOCBP7                | IOCBP6                | IOCBP5 | IOCBP4 |        | -      | -      | —      | 215                 |

| IOCBN <sup>(1)</sup> | IOCBN7                | IOCBN6                | IOCBN5 | IOCBN4 | _      | _      | _      | —      | 215                 |

| IOCBF <sup>(1)</sup> | IOCBF7                | IOCBF6                | IOCBF5 | IOCBF4 | _      | _      | _      | —      | 216                 |

| IOCCP                | IOCCP7 <sup>(1)</sup> | IOCCP6 <sup>(1)</sup> | IOCCP5 | IOCCP4 | IOCCP3 | IOCCP2 | IOCCP1 | IOCCP0 | 217                 |

| IOCCN                | IOCCN7 <sup>(1)</sup> | IOCCN6 <sup>(1)</sup> | IOCCN5 | IOCCN4 | IOCCN3 | IOCCN2 | IOCCN1 | IOCCN0 | 217                 |

| IOCCF                | IOCCF7 <sup>(1)</sup> | IOCCF6 <sup>(1)</sup> | IOCCF5 | IOCCF4 | IOCCF3 | IOCCF2 | IOCCF1 | IOCCF0 | 217                 |

| TABLE 17-1: | SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE |

|-------------|----------------------------------------------------------|

|-------------|----------------------------------------------------------|

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

Note 1: Present only in PIC16(L)F15345.

## 23.3 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See Comparator Specifications in Table 37-14 for more information.

## 23.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 26.6 "Timer Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 23.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from a comparator can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 23-2) and the Timer1 Block Diagram (Figure 26-1) for more information.

#### 23.5 Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- CxON, CxPOL and CxSP bits of the CMxCON0 register

- CxIE bit of the PIE2 register

- CxINTP bit of the CMxCON1 register (for a rising edge detection)

- CxINTN bit of the CMxCON1 register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

**Note:** Although a comparator is disabled, an interrupt can be generated by changing the output polarity with the CxPOL bit of the CMxCON0 register, or by switching the comparator on or off with the CxON bit of the CMxCON0 register.

## 23.6 Comparator Positive Input Selection

Configuring the CxPCH<2:0> bits of the CMxPSEL register directs an internal voltage reference or an analog pin to the noninverting input of the comparator:

- CxIN0+ analog pin

- DAC output

- FVR (Fixed Voltage Reference)

- · Vss (Ground)

See **Section 18.0 "Fixed Voltage Reference (FVR)"** for more information on the Fixed Voltage Reference module.

See Section 21.0 "5-Bit Digital-to-Analog Converter (DAC1) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

## 23.7 Comparator Negative Input Selection

The CxNCH<2:0> bits of the CMxCON1 register direct an analog input pin and internal reference voltage or analog ground to the inverting input of the comparator:

- CxIN- pin

- FVR (Fixed Voltage Reference)

- · Analog Ground

Note: To use CxINy+ and CxINy- pins as analog input, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

#### EXAMPLE 24-1:

VRMS = 120 VPEAK =VRMS\*  $\sqrt{2}$  = 169.7 f = 60 Hz C = 0.1 uF Z = VPEAK/3x10<sup>-4</sup> = 169.7/(3x10<sup>-4</sup>) = 565.7 kOhms Xc = 1/(2 $\Pi$ fC) = 1/(2 $\Pi$ \*60\*1\*10<sup>-7</sup>) = 26.53 kOhms R =  $\sqrt{(Z^2 - Xc^2)}$  = 565.1 kOhms (computed) R = 560 kOhms (used) ZR =  $\sqrt{(R^2 + Xc^2)}$  = 560.6 kOhms (using actual resistor) IPEAK = VPEAK/ZR = 302.7\*10<sup>-6</sup> VC = Xc\* IPEAK = 8.0 V  $\Phi$  = Tan<sup>-1</sup>(Xc/R) = 0.047 radians T $_{\Phi}$  =  $\Phi/(2\Pi$ f) = 125.6 us

#### 24.5.2 CORRECTION BY OFFSET CURRENT

When the waveform is varying relative to Vss, then the zero cross is detected too early as the waveform falls and too late as the waveform rises. When the waveform is varying relative to VDD, then the zero cross is detected too late as the waveform rises and too early as the waveform falls. The actual offset time can be determined for sinusoidal waveforms with the corresponding equations shown in Equation 24-3.

## EQUATION 24-3: ZCD EVENT OFFSET

When External Voltage Source is relative to Vss:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{Vcpinv}{VPEAK}\right)}{2\pi \bullet Freq}$$

When External Voltage Source is relative to VDD:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{VDD - Vcpinv}{VPEAK}\right)}{2\pi \bullet Freq}$$

This offset time can be compensated for by adding a pull-up or pull-down biasing resistor to the ZCD pin. A pull-up resistor is used when the external voltage source is varying relative to Vss. A pull-down resistor is used when the voltage is varying relative to VDD. The resistor adds a bias to the ZCD pin so that the target external voltage source must go to zero to pull the pin voltage to the VCPINV switching voltage. The pull-up or pull-down value can be determined with the equation shown in Equation 24-4.

### EQUATION 24-4: ZCD PULL-UP/DOWN

When External Signal is relative to Vss:

$$RPULLUP = \frac{RSERIES(VPULLUP - Vcpinv)}{Vcpinv}$$

When External Signal is relative to VDD:

$$\left(RPULLDOWN = \frac{RSERIES \times (Vcpinv)}{(VDD - Vcpinv)}\right)$$

## 24.6 Handling VPEAK variations

If the peak amplitude of the external voltage is expected to vary, the series resistor must be selected to keep the ZCD current source and sink below the design maximum range of  $\pm$  600 µA and above a reasonable minimum range. A general rule of thumb is that the maximum peak voltage can be no more than six times the minimum peak voltage. To ensure that the maximum current does not exceed  $\pm$  600 µA and the minimum is at least  $\pm$  100 µA, compute the series resistance as shown in Equation 24-5. The compensating pull-up for this series resistance can be determined with Equation 24-4 because the pull-up value is not dependent from the peak voltage.

#### EQUATION 24-5: SERIES R FOR V RANGE

$$R_{SERIES} = \frac{V_{MAXPEAK} + V_{MINPEAK}}{7 \times 10^{-4}}$$

### 26.3 Timer Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## 26.4 Secondary Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins SOSCI (input) and SOSCO (amplifier output). This internal circuit is designed to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the SOSCEN bit of the OSCEN register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, SOSCEN should be set and a suitable delay observed prior to using Timer1 with the SOSC source. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

#### 26.5 Timer Operation in Asynchronous Counter Mode

If the control bit SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 26.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

#### 26.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

## 26.6 Timer Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using the time gate circuitry. This is also referred to as Timer Gate Enable.

The timer gate can also be driven by multiple selectable sources.

#### 26.6.1 TIMER GATE ENABLE

The Timer Gate Enable mode is enabled by setting the GE bit of the T1GCON register. The polarity of the Timer Gate Enable mode is configured using the GPOL bit of the T1GCON register.

When Timer Gate Enable signal is enabled, the timer will increment on the rising edge of the Timer1 clock source. When Timer Gate Enable signal is disabled, the timer always increments, regardless of the GE bit. See Figure 26-3 for timing details.

TABLE 26-2: TIMER GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer Operation |

|------------|--------|-----|-----------------|

| $\uparrow$ | 1      | 1   | Counts          |

| $\uparrow$ | 1      | 0   | Holds Count     |

| $\uparrow$ | 0      | 1   | Holds Count     |

| 1          | 0      | 0   | Counts          |

### REGISTER 27-4: T2RST: TIMER2 EXTERNAL RESET SIGNAL SELECTION REGISTER

| U-0                                     | U-0 | U-0               | U-0  | R/W-0/0                                               | R/W-0/0          | R/W-0/0  | R/W-0/0 |  |

|-----------------------------------------|-----|-------------------|------|-------------------------------------------------------|------------------|----------|---------|--|

| _                                       | —   | _                 | _    |                                                       | RSEL             | <3:0>    |         |  |

| bit 7                                   |     |                   |      |                                                       |                  |          | bit 0   |  |

|                                         |     |                   |      |                                                       |                  |          |         |  |

| Legend:                                 |     |                   |      |                                                       |                  |          |         |  |

| R = Readable                            | bit | W = Writable      | bit  | U = Unimplen                                          | nented bit, read | d as '0' |         |  |

| u = Bit is unchanged x = Bit is unknown |     |                   | nown | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |         |  |

| '1' = Bit is set                        |     | '0' = Bit is clea | ared |                                                       |                  |          |         |  |

|                                         |     |                   |      |                                                       |                  |          |         |  |

| bit 7-4 | Unimplemented: Read as '0'                                    |

|---------|---------------------------------------------------------------|

| bit 3-0 | RSEL<3:0>: Timer2 External Reset Signal Source Selection bits |

|         | 1111 = Reserved                                               |

|         | 1101 = LC4_out                                                |

|         | 1100 = LC3_out                                                |

|         | 1011 = LC2_out                                                |

|         | 1010 = LC1_out                                                |

|         | 1001 = ZCD1_output                                            |

|         | 1000 = C2OUT_sync                                             |

|         | 0111 = C1OUT_sync                                             |

|         | 0110 = PWM6_out                                               |

|         | 0101 = PWM5_out                                               |

|         | 0100 = PWM4_out                                               |

|         | 0011 = PWM3_out                                               |

|         | 0010 = CCP2_out                                               |

|         | 0001 = CCP1_out                                               |

|         | 0000 = T2INPPS                                                |

|         |                                                               |

#### 32.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 32.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 32.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSP1STAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCL1IF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

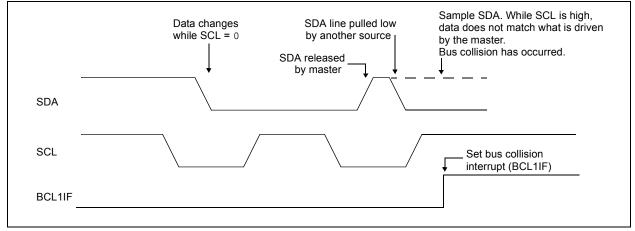

#### 32.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCL1IF and reset the I<sup>2</sup>C port to its Idle state (Figure 32-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSP1BUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSP1CON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSP1IF bit will be set.

A write to the SSP1BUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSP1STAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 32-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

| R/W-1/1                                                         | R/W-1/1                                                                                              | R/W-1/1          | R/W-1/1         | R/W-1/1                                            | R/W-1/1          | R/W-1/1  | R/W-1/1      |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------|-----------------|----------------------------------------------------|------------------|----------|--------------|

|                                                                 |                                                                                                      |                  | SSP1N           | ISK<7:0>                                           |                  |          |              |

| bit 7                                                           |                                                                                                      |                  |                 |                                                    |                  |          | bit 0        |

|                                                                 |                                                                                                      |                  |                 |                                                    |                  |          |              |

| Legend:                                                         |                                                                                                      |                  |                 |                                                    |                  |          |              |

| R = Readable                                                    | e bit                                                                                                | W = Writable     | bit             | U = Unimpler                                       | nented bit, read | l as '0' |              |

| u = Bit is unchanged                                            |                                                                                                      | x = Bit is unkr  | nown            | -n/n = Value at POR and BOR/Value at all other Res |                  |          | other Resets |

| '1' = Bit is set                                                |                                                                                                      | '0' = Bit is cle | ared            |                                                    |                  |          |              |

|                                                                 |                                                                                                      |                  |                 |                                                    |                  |          |              |

| bit 7-1                                                         |                                                                                                      | 7:1>: Mask bits  |                 |                                                    |                  |          |              |

|                                                                 | 1 = The received address bit n is compared to SSP1ADD <n> to detect I<sup>2</sup>C address match</n> |                  |                 |                                                    |                  |          |              |

|                                                                 | 0 = The received address bit n is not used to detect I <sup>2</sup> C address match                  |                  |                 |                                                    |                  |          |              |

| bit 0                                                           | SSP1MSK<0>: Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address                                 |                  |                 |                                                    |                  |          |              |

| $I^{2}C$ Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111): |                                                                                                      |                  |                 |                                                    |                  |          |              |

|                                                                 | 1 = The received address bit 0 is compared to SSP1ADD<0> to detect I <sup>2</sup> C address match    |                  |                 |                                                    |                  |          |              |

|                                                                 | 0 = The rec                                                                                          | eived address b  | it 0 is not use | d to detect I <sup>2</sup> C                       | address match    |          |              |

|                                                                 | <u>l<sup>2</sup>C Slave mode, 7-bit address:</u>                                                     |                  |                 |                                                    |                  |          |              |

## REGISTER 32-5: SSP1MSK: SSP1 MASK REGISTER

MSK0 bit is ignored.

## REGISTER 32-6: SSP1ADD: MSSP1 ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | SSP1AD  | D<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### Master mode:

| bit 7-0 | SSP1ADD<7:0>: Baud Rate Clock Divider bits      |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

#### <u>10-Bit Slave mode – Most Significant Address Byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 SSP1ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### <u>10-Bit Slave mode – Least Significant Address Byte:</u>

bit 7-0 SSP1ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

- bit 7-1 SSP1ADD<7:1>: 7-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

## 36.2 General Format for Instructions

| Mnemonic,<br>Operands |         | Description                   |               | 14-Bit Opcode |      |      |      | Status   | Notes |

|-----------------------|---------|-------------------------------|---------------|---------------|------|------|------|----------|-------|

|                       |         | Description                   | Cycles        | MSb           |      |      | LSb  | Affected | Notes |

|                       |         | BYTE-ORIENTED FILE            | REGISTER OPE  | RATIC         | ONS  |      |      |          |       |

| ADDWF                 | f, d    | Add W and f                   | 1             | 00            | 0111 | dfff | ffff | C, DC, Z | 2     |

| ADDWFC                | f, d    | Add with Carry W and f        | 1             | 11            | 1101 | dfff | ffff | C, DC, Z | 2     |

| ANDWF                 | f, d    | AND W with f                  | 1             | 00            | 0101 | dfff | ffff | Z        | 2     |

| ASRF                  | f, d    | Arithmetic Right Shift        | 1             | 11            | 0111 | dfff | ffff | C, Z     | 2     |

| LSLF                  | f, d    | Logical Left Shift            | 1             | 11            | 0101 | dfff | ffff | C, Z     | 2     |

| LSRF                  | f, d    | Logical Right Shift           | 1             | 11            | 0110 | dfff | ffff | C, Z     | 2     |

| CLRF                  | f       | Clear f                       | 1             | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW                  | _       | Clear W                       | 1             | 00            | 0001 | 0000 | 00xx | Z        |       |

| COMF                  | f, d    | Complement f                  | 1             | 00            | 1001 | dfff | ffff | Z        | 2     |

| DECF                  | f, d    | Decrement f                   | 1             | 00            | 0011 | dfff | ffff | Z        | 2     |

| INCF                  | f, d    | Increment f                   | 1             | 00            | 1010 | dfff | ffff | Z        | 2     |

| IORWF                 | f, d    | Inclusive OR W with f         | 1             | 00            | 0100 | dfff | ffff | Z        | 2     |

| MOVF                  | f, d    | Move f                        | 1             | 00            | 1000 | dfff | ffff | Z        | 2     |

| MOVWF                 | f       | Move W to f                   | 1             | 00            | 0000 | 1fff | ffff |          | 2     |

| RLF                   | f, d    | Rotate Left f through Carry   | 1             | 00            | 1101 | dfff | ffff | С        | 2     |

| RRF                   | f, d    | Rotate Right f through Carry  | 1             | 00            | 1100 | dfff | ffff | С        | 2     |

| SUBWF                 | f, d    | Subtract W from f             | 1             | 00            | 0010 | dfff | ffff | C, DC, Z | 2     |

| SUBWFB                | f, d    | Subtract with Borrow W from f | 1             | 11            | 1011 | dfff | ffff | C, DC, Z | 2     |

| SWAPF                 | f, d    | Swap nibbles in f             | 1             | 00            | 1110 | dfff | ffff | -, -,    | 2     |

| XORWF                 | f, d    | Exclusive OR W with f         | 1             | 00            | 0110 | dfff | ffff | Z        | 2     |

|                       |         | BYTE ORIENTED                 | SKIP OPERATIO | ONS           |      |      |      |          | •     |

| DECFSZ                | f, d    | Decrement f, Skip if 0        | 1(2)          | 00            | 1011 | dfff | ffff |          | 1, 2  |

| INCFSZ                | f, d    | Increment f, Skip if 0        | 1(2)          | 00            | 1111 | dfff | ffff |          | 1, 2  |

|                       |         | BIT-ORIENTED FILE             |               |               | NS   |      |      | 1        |       |

| BCF                   | f, b    | Bit Clear f                   | 1             | 01            | 00bb | bfff | ffff |          | 2     |

| BSF                   | f, b    | Bit Set f                     | 1             | 01            | 01bb | bfff | ffff |          | 2     |

|                       |         | BIT-ORIENTED                  | SKIP OPERATIO | NS            |      |      |      |          | 1     |

| BTFSC                 | f, b    | Bit Test f, Skip if Clear     | 1 (2)         | 01            | 10bb | bfff | ffff |          | 1, 2  |

| BTFSS                 | f, b    | Bit Test f, Skip if Set       | 1 (2)         | 01            | 11bb | bfff | ffff |          | 1, 2  |

| LITERAL (             | OPERATI |                               |               |               |      |      |      |          |       |

| ADDLW                 | k       | Add literal and W             | 1             | 11            | 1110 | kkkk | kkkk | C, DC, Z |       |

| ANDLW                 | k       | AND literal with W            | 1             | 11            | 1001 | kkkk | kkkk | Z        |       |

| IORLW                 | k       | Inclusive OR literal with W   | 1             | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLB                 | k       | Move literal to BSR           | 1             | 00            | 000  | 0k   | kkkk |          |       |

| MOVLP                 | k       | Move literal to PCLATH        | 1             | 11            | 0001 | 1kkk | kkkk |          |       |

| MOVLW                 | k       | Move literal to W             | 1             | 11            | 0000 | kkkk | kkkk |          |       |

| SUBLW                 | k       | Subtract W from literal       | 1             | 11            | 1100 | kkkk | kkkk | C, DC, Z |       |

| XORLW                 | k       | Exclusive OR literal with W   | 1             | 11            | 1010 | kkkk | kkkk | Z        |       |

#### TABLE 36-3: INSTRUCTION SET

**Note 1:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |

| Operation:       | k → PC<10:0><br>PCLATH<6:3> → PC<14:11>                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                    |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                              |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                              |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |

| IORLW            | Inclusive OR literal with W                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                           |

| Operands:        | $0 \leq k \leq 255$                                                                                                |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                       |

| Status Affected: | Z                                                                                                                  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |

| INCF             | Increment f                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                         |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

| ΜΟΥΨΙ            | Move W to INDFn                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                                                                                       |

| Operands:        | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ \textbf{-32} \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                                   |

| Operation:       | $\label{eq:W} \begin{split} & W \rightarrow INDFn \\ & \text{Effective address is determined by} \\ & FSR + 1 (\text{preincrement}) \\ & FSR + 1 (\text{predecrement}) \\ & FSR + k (\text{relative offset}) \\ & \text{After the Move, the FSR value will be either:} \\ & FSR + 1 (\text{all increments}) \\ & FSR + 1 (\text{all increments}) \\ & \text{Unchanged} \end{split}$ |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                                                                |

| Mode          | Syntax | mm |  |

|---------------|--------|----|--|

| Preincrement  | ++FSRn | 00 |  |

| Predecrement  | FSRn   | 01 |  |

| Postincrement | FSRn++ | 10 |  |

| Postdecrement | FSRn   | 11 |  |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h-FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| RESET            | Software Reset                                                                 |

|------------------|--------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                  |

| Operands:        | None                                                                           |

| Operation:       | Execute a device Reset. Resets the RI flag of the PCON register.               |

| Status Affected: | None                                                                           |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by<br>software. |

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] RETFIE k                                                                                                                                                                                       |  |  |  |

| Operands:        | None                                                                                                                                                                                                            |  |  |  |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$                                                                                                                                                                      |  |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |  |  |  |

| Words:           | 1                                                                                                                                                                                                               |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                               |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                          |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                          |  |  |  |

© 2016 Microchip Technology Inc.

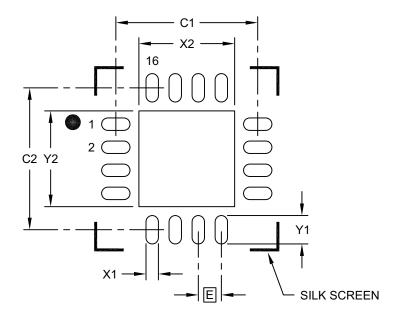

## 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                            |        |     |            | •    |

|----------------------------|--------|-----|------------|------|

|                            | Units  | N   | IILLIMETER | S    |

| Dimensior                  | Limits | MIN | NOM        | MAX  |

| Contact Pitch              | E      |     | 0.65 BSC   |      |

| Optional Center Pad Width  | X2     |     |            | 2.70 |

| Optional Center Pad Length | Y2     |     |            | 2.70 |

| Contact Pad Spacing        | C1     |     | 4.00       |      |

| Contact Pad Spacing        | C2     |     | 4.00       |      |

| Contact Pad Width (X16)    | X1     |     |            | 0.35 |

| Contact Pad Length (X16)   | Y1     |     |            | 0.80 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2257A

For the most current package drawings, please see the Microchip Packaging Specification located at

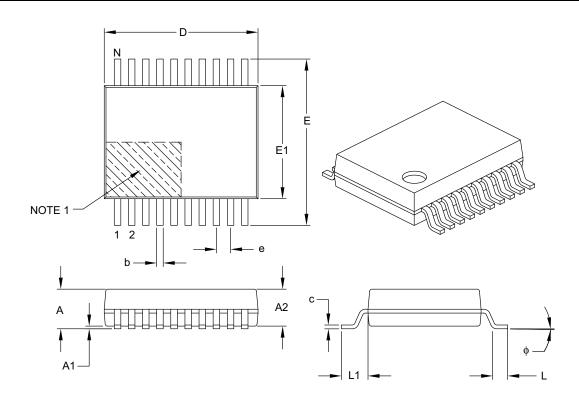

#### 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

http://www.microchip.com/packaging

|                          | Units        |          | MILLIMETERS | 6    |

|--------------------------|--------------|----------|-------------|------|

| Dime                     | nsion Limits | MIN      | NOM         | MAX  |

| Number of Pins           | N            |          | 20          |      |

| Pitch                    | е            | 0.65 BSC |             |      |

| Overall Height           | Α            | -        | -           | 2.00 |

| Molded Package Thickness | A2           | 1.65     | 1.75        | 1.85 |

| Standoff                 | A1           | 0.05     | -           | -    |

| Overall Width            | E            | 7.40     | 7.80        | 8.20 |

| Molded Package Width     | E1           | 5.00     | 5.30        | 5.60 |

| Overall Length           | D            | 6.90     | 7.20        | 7.50 |

| Foot Length              | L            | 0.55     | 0.75        | 0.95 |

| Footprint                | L1           |          | 1.25 REF    |      |

| Lead Thickness           | С            | 0.09     | -           | 0.25 |

| Foot Angle               | φ            | 0°       | 4°          | 8°   |

| Lead Width               | b            | 0.22     | -           | 0.38 |

#### Notes:

Note:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B