#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 224 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 20-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15345-i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                                     | Function              | Input<br>Type | Output Type | Description                                                         |

|----------------------------------------------------------------------------------------------------------|-----------------------|---------------|-------------|---------------------------------------------------------------------|

| <u>RC3</u> /ANC3/C1IN3-/C2IN3-/CCP2 <sup>(1)</sup> /<br>SS1 <sup>(1)</sup> /CLCIN0 <sup>(1)</sup> /IOCC3 | RC3                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| 331 //CECINO //IOCC3                                                                                     | ANC3                  | AN            | _           | ADC Channel C3 input.                                               |

|                                                                                                          | C1IN3-                | AN            | _           | Comparator 1 positive input.                                        |

|                                                                                                          | C2IN3-                | AN            | _           | Comparator 2 positive input.                                        |

|                                                                                                          | CCP2 <sup>(1)</sup>   | TTL/ST        | CMOS/OD     | Capture/compare/PWM2 (default input location for capture function). |

|                                                                                                          | SS1 <sup>(1)</sup>    | TTL/ST        | _           | MSSP1 SPI slave select input.                                       |

|                                                                                                          | CLCIN0 <sup>(1)</sup> | TTL/ST        | _           | Configurable Logic Cell source input.                               |

|                                                                                                          | IOCC3                 | TTL/ST        | _           | Interrupt-on-change input.                                          |

| RC4/ANC4/TX1 <sup>(1)</sup> /CK1 <sup>(1)</sup> /CLCIN1 <sup>(1)</sup> /<br>IOCC4                        | RC4                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

|                                                                                                          | ANC4                  | AN            | _           | ADC Channel C4 input.                                               |

|                                                                                                          | TX1                   | -             | CMOS        | EUSART1 asynchronous transmit.                                      |

|                                                                                                          | CLCIN1 <sup>(1)</sup> | TTL/ST        | _           | Configurable Logic Cell source input.                               |

|                                                                                                          | CK1 <sup>(1)</sup>    | TTL/ST        | CMOS/OD     | EUSART1 synchronous mode clock input/output.                        |

|                                                                                                          | IOCC4                 | TTL/ST        | _           | Interrupt-on-change input.                                          |

| RC5/ANC5/CCP1 <sup>(1)</sup> /RX1 <sup>(1)</sup> /DT1 <sup>(1)</sup> /<br>IOCC5                          | RC5                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| 10005                                                                                                    | ANC5                  | AN            | _           | ADC Channel C5 input.                                               |

|                                                                                                          | CCP1 <sup>(1)</sup>   | TTL/ST        | CMOS/OD     | Capture/compare/PWM1 (default input location for capture function). |

|                                                                                                          | RX1 <sup>(1)</sup>    | TTL/ST        | _           | EUSART1 Asynchronous mode receiver data input.                      |

|                                                                                                          | DT1 <sup>(1)</sup>    | TTL/ST        | CMOS/OD     | EUSART1 Synchronous mode data input/output.                         |

|                                                                                                          | IOCC5                 | TTL/ST        | _           | Interrupt-on-change input.                                          |

| Vdd                                                                                                      | Vdd                   | Power         | _           | Positive supply voltage input.                                      |

| Vss                                                                                                      | Vss                   | Power         | _           | Ground reference.                                                   |

TABLE 1-2: PIC16(L)F15325 PINOUT DESCRIPTION (CONTINUED)

Legend:

AN

= Analog input or output TTL

CMOS

= CMOS compatible input or output

OD

= Open-Drain

TTL

= TTL compatible input HV

= High Voltage

ST

= Schmitt Trigger input with CMOS levels

I<sup>2</sup>C

= Schmitt Trigger input with I<sup>2</sup>C

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-3 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

#### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address                                         | Name             | Bit 7                | Bit 6             | Bit 5             | Bit 4              | Bit 3            | Bit 2            | Bit 1            | Bit 0       | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-------------------------------------------------|------------------|----------------------|-------------------|-------------------|--------------------|------------------|------------------|------------------|-------------|-----------------------|----------------------------|

| Bank 21-59                                      |                  |                      |                   |                   |                    |                  |                  |                  |             |                       |                            |

| CPU CORE REGISTERS; see Table 4-3 for specifics |                  |                      |                   |                   |                    |                  |                  |                  |             |                       |                            |

| x0Ch/<br>x8Ch<br>                               |                  |                      |                   |                   |                    |                  |                  | _                |             |                       |                            |

| Legend:                                         | x = unknown, u : | = unchanged, q = dep | ends on conditior | ı, - = unimplemer | nted, read as '0', | r = reserved. Sh | aded locations u | inimplemented, r | ead as '0'. |                       |                            |

#### 9.2.2.2 Internal Oscillator Frequency Adjustment

The internal oscillator is factory-calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 9-7).

The default value of the OSCTUNE register is 00h. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

#### 9.2.2.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a factory calibrated 31 kHz internal clock source.

The LFINTOSC is the frequency for the Power-up Timer (PWRT), Windowed Watchdog Timer (WWDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits of Configuration Word 1 to enable LFINTOSC.

- Write to the NOSC<2:0> bits of the OSCCON1 register.

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Windowed Watchdog Timer (WWDT)

- Timer1

- Timer0

- Timer2

- Fail-Safe Clock Monitor (FSCM)

- CLKR

- CLC

#### 9.2.2.4 Oscillator Status and Manual Enable

The 'ready' status of each oscillator is displayed in the OSCSTAT register (Register 9-4). The oscillators can also be manually enabled through the OSCEN register (Register 9-7). Manual enabling makes it possible to verify the operation of the EXTOSC or SOSC crystal oscillators. This can be achieved by enabling the selected oscillator, then watching the corresponding 'ready' state of the oscillator in the OSCSTAT register.

#### 9.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the New Oscillator Source (NOSC) and New Divider selection request (NDIV) bits of the OSCCON1 register.

#### 9.3.1 NEW OSCILLATOR SOURCE (NOSC) AND NEW DIVIDER SELECTION REQUEST (NDIV) BITS

The New Oscillator Source (NOSC) and New Divider selection request (NDIV) bits of the OSCCON1 register select the system clock source and the frequency that are used for the CPU and peripherals.

When new values of NOSC and NDIV are written to OSCCON1, the current oscillator selection will continue to operate while waiting for the new clock source to indicate that it is stable and ready. In some cases, the newly requested source may already be in use, and is ready immediately. In the case of a divider-only change, the new and old sources are the same, and will be immediately ready. The device may enter Sleep while waiting for the switch as described in **Section 9.3.3 "Clock Switch and Sleep"**.

When the new oscillator is ready, the New Oscillator is Ready (NOSCR) bit of OSCCON3 and the Clock Switch Interrupt Flag (CSWIF) bit of PIR1 become set (CSWIF = 1). If Clock Switch Interrupts are enabled (CSWIE = 1), an interrupt will be generated at that time. The Oscillator Ready (ORDY) bit of OSCCON3 can also be polled to determine when the oscillator is ready in lieu of an interrupt.

If the Clock Switch Hold (CSWHOLD) bit of OSCCON3 is clear, the oscillator switch will occur when the new Oscillator's READY bit (NOSCR) is set, and the interrupt (if enabled) will be serviced at the new oscillator setting.

If CSWHOLD is set, the oscillator switch is suspended, while execution continues using the current (old) clock source. When the NOSCR bit is set, software should:

- set CSWHOLD = 0 so the switch can complete, or

- · copy COSC into NOSC to abandon the switch.

If DOZE is in effect, the switch occurs on the next clock cycle, whether or not the CPU is operating during that cycle.

| FIGURE 10-2: | INTERRUPT LA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TENCY  |         |             |                |                              |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|-------------|----------------|------------------------------|--|--|

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |         |             |                | Rev. 10-000289E<br>8/31/2016 |  |  |

|              | $ \begin{array}{c} \begin{array}{c} \begin{array}{c} \begin{array}{c} \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{c} \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{c} \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{c} \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{c} \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \end{array} \\ \begin{array}{c} \end{array} \\ \begin{array} \\ \end{array} \\ \end{array}$ |        |         |             |                |                              |  |  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |         |             |                |                              |  |  |

| INT<br>pin   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |         |             |                |                              |  |  |

| Fetch P      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PC + 1 |         | PC = 0x0004 | PC = 0x0005    | PC = 0x0006                  |  |  |

| Execute PC   | C - 21 PC - 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PC     | NOP     | NOP         | PC = 0x0004    | PC = 0x0005                  |  |  |

|              | Indeterminate<br>Laten cy <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | Latency |             |                |                              |  |  |

|              | errupt may occur at any ti<br>an interrupt may occur a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |         |             | ency can vary. |                              |  |  |

|                           | Q1   Q2   Q3   Q4                               | Q1   Q2   Q3   Q4       | Q1   Q2   Q3   Q4       | Q1   Q2   Q3   Q4    | Q1   Q2   Q3   Q4       |

|---------------------------|-------------------------------------------------|-------------------------|-------------------------|----------------------|-------------------------|

| OSC1                      |                                                 |                         |                         |                      |                         |

|                           | (4)                                             |                         |                         | -<br>                |                         |

| INT pin                   |                                                 | , (1)                   | 1                       | 1<br>1<br>1          | <u> </u>                |

| INTF                      | , (1) (5)                                       | , ·                     | Interrupt Latency (2)   | ,<br>,<br>,<br>,     |                         |

| GIE                       |                                                 |                         |                         | 1                    |                         |

| INSTRUCTION               |                                                 |                         |                         |                      |                         |

| PC                        | ( PC                                            | PC + 1                  | PC + 1                  | X 0004h              | X0005h                  |

| Instruction (<br>Fetched  | Inst (PC)                                       | Inst (PC + 1)           | —                       | Inst (0004h)         | Inst (0005h)            |

| Instruction (<br>Executed | Inst (PC – 1)                                   | Inst (PC)               | Forced NOP              | Forced NOP           | Inst (0004h)            |

| Note 1: IN                | NTF flag is sampled here                        | e (every Q1).           |                         |                      |                         |

|                           | synchronous interrupt la atency is the same whe |                         |                         |                      | instruction cycle time. |

| 3: F                      | or minimum width of INT                         | f pulse, refer to AC sp | ecifications in Section | 37.0 "Electrical Spe | cifications".           |

4: INTF may be set any time during the Q4-Q1 cycles.

| U-0                             | U-0                             | R/W/HS-0/0                       | R/W/HS-0/0        | U-0             | U-0              | U-0              | R/W/HS-0/0   |  |

|---------------------------------|---------------------------------|----------------------------------|-------------------|-----------------|------------------|------------------|--------------|--|

| _                               | _                               | NVMIF                            | NCO1IF            | _               | —                | _                | CWG1IF       |  |

| bit 7                           |                                 |                                  |                   |                 | ·                |                  | bit 0        |  |

|                                 |                                 |                                  |                   |                 |                  |                  |              |  |

| Legend:                         |                                 |                                  |                   |                 |                  |                  |              |  |

| R = Readable                    | e bit                           | W = Writable                     | bit               | U = Unimpler    | mented bit, read | as '0'           |              |  |

| u = Bit is unc                  | hanged                          | x = Bit is unkr                  | nown              | -n/n = Value a  | at POR and BO    | R/Value at all o | other Resets |  |

| '1' = Bit is set                | t                               | '0' = Bit is cle                 | ared              | HS = Hardwa     | are set          |                  |              |  |

|                                 |                                 |                                  |                   |                 |                  |                  |              |  |

| bit 7-6                         | Unimplemen                      | ted: Read as '                   | 0'                |                 |                  |                  |              |  |

| bit 5                           | NVMIF: Nonv                     | olatile Memory                   | (NVM) Interru     | upt Flag bit    |                  |                  |              |  |

|                                 |                                 | ested NVM ope<br>rrupt not asser |                   | npleted         |                  |                  |              |  |

| bit 4                           | NCO1IF: Nun                     | nerically Contro                 | olled Oscillator  | r (NCO) Interru | upt Flag bit     |                  |              |  |

|                                 | 1 = The NCO                     | has rolled ove                   | r                 |                 |                  |                  |              |  |

|                                 | 0 <b>= No NCO i</b>             | nterrupt event                   | has occurred      |                 |                  |                  |              |  |

| bit 3-1                         | Unimplemen                      | ted: Read as '                   | 0'                |                 |                  |                  |              |  |

| bit 0                           | CWG1IF: CWG1 Interrupt Flag bit |                                  |                   |                 |                  |                  |              |  |

| 1 = CWG1 has gone into shutdown |                                 |                                  |                   |                 |                  |                  |              |  |

|                                 | 0 = CWG1 is                     | operating norn                   | hally, or interru | ipt cleared     |                  |                  |              |  |

|                                 |                                 |                                  |                   |                 |                  |                  |              |  |

#### REGISTER 10-17: PIR7: PERIPHERAL INTERRUPT REQUEST REGISTER 7

| Note: | Interrupt flag bits are set when an interrupt |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |  |  |

|       | its corresponding enable bit or the Global    |  |  |  |  |  |  |  |

|       | Enable bit, GIE, of the INTCON register.      |  |  |  |  |  |  |  |

|       | User software should ensure the               |  |  |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear     |  |  |  |  |  |  |  |

|       | prior to enabling an interrupt.               |  |  |  |  |  |  |  |

#### 23.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 23-1) contains Control and Status bits for the following:

- Enable

- Output

- Output polarity

- · Hysteresis enable

- · Timer1 output synchronization

The CMxCON1 register (see Register 23-2) contains Control bits for the following:

- · Interrupt on positive/negative edge enables

- The CMxNSEL and CMxPSEL (Register 23-3 and Register 23-4) contain control bits for the following:

- Positive input channel selection

- Negative input channel selection

#### 23.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 23.2.2 COMPARATOR OUTPUT

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register.

The comparator output can also be routed to an external pin through the RxyPPS register (Register 15-2). The corresponding TRIS bit must be clear to enable the pin as an output.

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 23.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 23-2 shows the output state versus input conditions, including polarity control.

#### TABLE 23-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

#### 23.10 CWG1 Auto-shutdown Source

The output of the comparator module can be used as an auto-shutdown source for the CWG1 module. When the output of the comparator is active and the corresponding ASxE is enabled, the CWG operation will be suspended immediately (see **Section 30.10 "Auto-Shutdown"**).

#### 23.11 Operation in Sleep Mode

The comparator module can operate during Sleep. The comparator clock source is based on the Timer1 clock source. If the Timer1 clock source is either the system clock (FOSC) or the instruction clock (FOSC/4), Timer1 will not operate during Sleep, and synchronized comparator outputs will not operate.

A comparator interrupt will wake the device from Sleep. The CxIE bits of the PIE2 register must be set to enable comparator interrupts.

#### 26.1 Timer1 Operation

The Timer1 modules are 16-bit incrementing counters which are accessed through the TMR1H:TMR1L register pairs. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

The timer is enabled by configuring the TMR1ON and GE bits in the T1CON and T1GCON registers, respectively. Table 26-1 displays the Timer1 enable selections.

TABLE 26-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 1      | 1      | Count Enabled       |

| 1      | 0      | Always On           |

| 0      | 1      | Off                 |

| 0      | 0      | Off                 |

#### 26.2 Clock Source Selection

The T1CLK register is used to select the clock source for the timer. Register 26-3 shows the possible clock sources that may be selected to make the timer increment.

#### 26.2.1 INTERNAL CLOCK SOURCE

When the internal clock source Fosc is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the respective Timer1 prescaler.

When the Fosc internal clock source is selected, the timer register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the TMR1H:TMR1L value. To utilize the full resolution of the timer in this mode, an asynchronous input signal must be used to gate the timer clock input.

Out of the total timer gate signal sources, the following subset of sources can be asynchronous and may be useful for this purpose:

- CLC4 output

- CLC3 output

- CLC2 output

- CLC1 output

- · Zero-Cross Detect output

- · Comparator2 output

- Comparator1 output

- TxG PPS remappable input pin

#### 26.2.2 EXTERNAL CLOCK SOURCE

When the timer is enabled and the external clock input source (ex: T1CKI PPS remappable input) is selected as the clock source, the timer will increment on the rising edge of the external clock input.

When using an external clock source, the timer can be configured to run synchronously or asynchronously, as described in Section 26.5 "Timer Operation in Asynchronous Counter Mode".

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used connected to the SOSCI/SOSCO pins.

- **Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- · The timer is first enabled after POR

- Firmware writes to TMR1H or TMR1L

- · The timer is disabled

- The timer is re-enabled (e.g., TMR1ON-->1) when the T1CKI signal is currently logic low.

#### 26.6.2 TIMER GATE SOURCE SELECTION

One of the several different external or internal signal sources may be chosen to gate the timer and allow the timer to increment. The gate input signal source can be selected based on the T1GATE register setting. See the T1GATE register (Register 26-4) description for a complete list of the available gate sources. The polarity for each available source is also selectable. Polarity selection is controlled by the GPOL bit of the T1GCON register.

#### 26.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for the timer gate control. It can be used to supply an external source to the time gate circuitry.

#### 26.6.2.2 Timer0 Overflow Gate Operation

When Timer0 overflows, or a period register match condition occurs (in 8-bit mode), a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 26.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for the timer gate control. The Comparator 1 output can be synchronized to the timer clock or left asynchronous. For more information see **Section 23.4.1 "Comparator Output Synchronization**".

#### 26.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for the timer gate control. The Comparator 2 output can be synchronized to the timer clock or left asynchronous. For more information see Section 23.4.1 "Comparator Output Synchronization".

#### 26.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a timer gate signal, as opposed to the duration of a single level pulse.

The timer gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 26-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the GTM bit of the T1GCON register. When the GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

## 26.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single-pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the GSPM bit in the T1GCON register. Next, the GGO/DONE bit in the T1GCON register must be set. The timer will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment the timer until the GGO/DONE bit is once again set in software. See Figure 26-5 for timing details.

If the Single-Pulse Gate mode is disabled by clearing the GSPM bit in the T1GCON register, the GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the timer gate source to be measured. See Figure 26-6 for timing details.

#### 26.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the GVAL bit in the T1GCON register. The GVAL bit is valid even when the timer gate is not enabled (GE bit is cleared).

#### 26.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of GVAL occurs, the TMR1GIF flag bit in the PIR5 register will be set. If the TMR1GIE bit in the PIE5 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the timer gate is not enabled (TMR1GE bit is cleared).

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 28-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 28.3.8 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 28.3.9 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 28.3.10 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 29.1 Standard PWM Mode

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the PWMx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- TMR2 register

- PR2 register

- PWMxCON registers

- PWMxDCH registers

- PWMxDCL registers

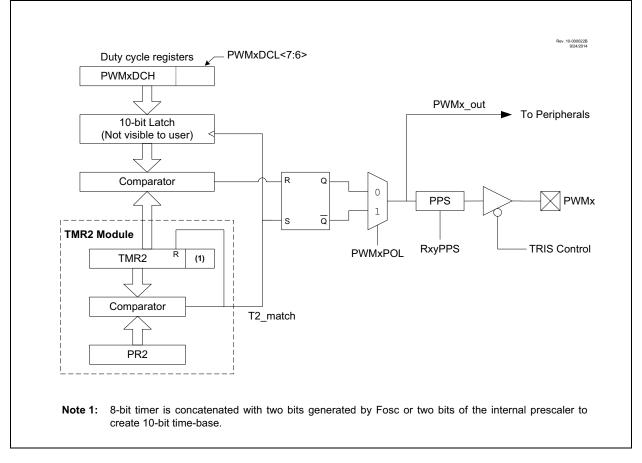

Figure 29-2 shows a simplified block diagram of PWM operation.

If PWMPOL = 0, the default state of the output is '0'. If PWMPOL = 1, the default state is '1'. If PWMEN = 0, the output will be the default state.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the PWMx pin

#### FIGURE 29-2: SIMPLIFIED PWM BLOCK DIAGRAM

| R/W-0/0                                                                                                                                                         | R/W-0/0                                                                                                                                                         | R/W-0/0                         | R/W-0/0          | R/W-0/0             | R/W-0/0             | R/W-0/0             | R/W-0/0             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|---------------------|---------------------|---------------------|---------------------|

| OVRD                                                                                                                                                            | OVRC                                                                                                                                                            | OVRB                            | OVRA             | STRD <sup>(2)</sup> | STRC <sup>(2)</sup> | STRB <sup>(2)</sup> | STRA <sup>(2)</sup> |

| bit 7                                                                                                                                                           |                                                                                                                                                                 |                                 |                  |                     |                     |                     | bit 0               |

| Legend:                                                                                                                                                         |                                                                                                                                                                 |                                 |                  |                     |                     |                     |                     |

| R = Readable                                                                                                                                                    | bit                                                                                                                                                             | W = Writable                    | bit              | U = Unimpler        | mented bit, read    | as '0'              |                     |

| u = Bit is unch                                                                                                                                                 |                                                                                                                                                                 | x = Bit is unkr                 |                  |                     | at POR and BO       |                     | ther Resets         |

| '1' = Bit is set                                                                                                                                                |                                                                                                                                                                 | '0' = Bit is clea               |                  |                     | pends on condit     |                     |                     |

|                                                                                                                                                                 |                                                                                                                                                                 |                                 |                  | 1                   |                     | -                   |                     |

| bit 7                                                                                                                                                           | OVRD: Steer                                                                                                                                                     | ing Data D bit                  |                  |                     |                     |                     |                     |

| bit 6                                                                                                                                                           | OVRC: Steer                                                                                                                                                     | ing Data C bit                  |                  |                     |                     |                     |                     |

| bit 5                                                                                                                                                           | OVRB: Steer                                                                                                                                                     | ing Data B bit                  |                  |                     |                     |                     |                     |

| bit 4                                                                                                                                                           | OVRA: Steer                                                                                                                                                     | ing Data A bit                  |                  |                     |                     |                     |                     |

| bit 3                                                                                                                                                           | STRD: Steeri                                                                                                                                                    | ng Enable D bi                  | t <sup>(2)</sup> |                     |                     |                     |                     |

| <ul> <li>1 = CWG1D output has the CWG1_data waveform with polarity control from POLD bit</li> <li>0 = CWG1D output is assigned the value of OVRD bit</li> </ul> |                                                                                                                                                                 |                                 |                  |                     |                     |                     |                     |

| bit 2                                                                                                                                                           | STRC: Steering Enable C bit <sup>(2)</sup>                                                                                                                      |                                 |                  |                     |                     |                     |                     |

| <ul> <li>1 = CWG1C output has the CWG1_data waveform with polarity control from POLC bit</li> <li>0 = CWG1C output is assigned the value of OVRC bit</li> </ul> |                                                                                                                                                                 |                                 |                  |                     |                     |                     |                     |

| bit 1                                                                                                                                                           | STRB: Steering Enable B bit <sup>(2)</sup>                                                                                                                      |                                 |                  |                     |                     |                     |                     |

|                                                                                                                                                                 | <ul> <li>1 = CWG1B output has the CWG1_data waveform with polarity control from POLB bit</li> <li>0 = CWG1B output is assigned the value of OVRB bit</li> </ul> |                                 |                  |                     |                     |                     |                     |

| bit 0                                                                                                                                                           | STRA: Steering Enable A bit <sup>(2)</sup>                                                                                                                      |                                 |                  |                     |                     |                     |                     |

|                                                                                                                                                                 |                                                                                                                                                                 | output has the output is assign |                  |                     | polarity control    | from POLA bit       |                     |

| Note 1: Th                                                                                                                                                      | e bits in this re                                                                                                                                               | gister apply onl                | y when MOD       | E<2:0> = 00x.       |                     |                     |                     |

### REGISTER 30-7: CWG1STR: CWG1 STEERING CONTROL REGISTER<sup>(1)</sup>

**2:** This bit is effectively double-buffered when MODE<2:0> = 001.

| R/W-x/u          | R/W-x/u      | R/W-x/u                                                                   | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |

|------------------|--------------|---------------------------------------------------------------------------|-----------------|----------------|------------------|------------------|-------------|--|

| LCxG2D4T         | LCxG2D4N     | LCxG2D3T                                                                  | LCxG2D3N        | LCxG2D2T       | LCxG2D2N         | LCxG2D1T         | LCxG2D1N    |  |

| bit 7            | •            |                                                                           | •               |                |                  | •                | bit (       |  |

|                  |              |                                                                           |                 |                |                  |                  |             |  |

| Legend:          |              |                                                                           |                 |                |                  |                  |             |  |

| R = Readable     |              | W = Writable                                                              | bit             | -              | nented bit, read |                  |             |  |

| u = Bit is uncha | anged        | x = Bit is unkr                                                           | nown            | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |  |

| '1' = Bit is set |              | '0' = Bit is clea                                                         | ared            |                |                  |                  |             |  |

|                  |              |                                                                           | - <i>,</i> .    |                |                  |                  |             |  |

| bit 7            |              | Sate 1 Data 4 T                                                           |                 | ,              |                  |                  |             |  |

|                  |              | true) is gated i<br>true) is not gat                                      |                 |                |                  |                  |             |  |

| bit 6            |              | · · ·                                                                     |                 |                |                  |                  |             |  |

|                  |              | Gate 1 Data 4 I<br>inverted) is ga                                        | •               | ,              |                  |                  |             |  |

|                  |              | inverted) is ga                                                           |                 |                |                  |                  |             |  |

| bit 5            |              | , ,                                                                       | •               |                |                  |                  |             |  |

|                  |              | Gate 1 Data 3 True (non-inverted) bit<br>(true) is gated into CLCx Gate 1 |                 |                |                  |                  |             |  |

|                  |              | (true) is not gat                                                         |                 |                |                  |                  |             |  |

| bit 4            | LCxG2D3N: (  | Gate 1 Data 3 I                                                           | Negated (inver  | rted) bit      |                  |                  |             |  |

|                  | 1 = CLCIN2 ( | inverted) is gated into CLCx Gate 1                                       |                 |                |                  |                  |             |  |

|                  | 0 = CLCIN2 ( | inverted) is no                                                           | t gated into CL | Cx Gate 1      |                  |                  |             |  |

| bit 3            | LCxG2D2T: O  | Gate 1 Data 2 T                                                           | rue (non-inve   | rted) bit      |                  |                  |             |  |

|                  |              | true) is gated i                                                          |                 |                |                  |                  |             |  |

|                  | 0 = CLCIN1 ( | true) is not gat                                                          | ted into CLCx   | Gate 1         |                  |                  |             |  |

| bit 2            |              | Gate 1 Data 2 I                                                           | •               |                |                  |                  |             |  |

|                  |              | inverted) is ga                                                           |                 |                |                  |                  |             |  |

|                  |              | inverted) is no                                                           | •               |                |                  |                  |             |  |

| bit 1            |              | Gate 1 Data 1 T                                                           | •               | ,              |                  |                  |             |  |

|                  |              | true) is gated i                                                          |                 |                |                  |                  |             |  |

| hit 0            |              | (true) is not gat                                                         |                 |                |                  |                  |             |  |

| bit 0            |              | Gate 1 Data 1 I                                                           | •               | ,              |                  |                  |             |  |

|                  |              | inverted) is ga<br>inverted) is no                                        |                 |                |                  |                  |             |  |

#### REGISTER 31-8: CLCxGLS1: GATE 1 LOGIC SELECT REGISTER

|                                                        |   |    |                  |                      |                            |                  | H CKE =          |                                                                                             |                       |                           | ,                     |

|--------------------------------------------------------|---|----|------------------|----------------------|----------------------------|------------------|------------------|---------------------------------------------------------------------------------------------|-----------------------|---------------------------|-----------------------|

|                                                        | S |    |                  |                      |                            |                  |                  |                                                                                             |                       |                           |                       |

| 80X<br>(CXF = 0<br>CXE = 0)                            |   |    |                  |                      |                            |                  |                  |                                                                                             |                       |                           | :<br>:<br>:           |

| 80%<br>80%<br>(0%8 = 3<br>(0%8 = 3)                    |   |    | :<br>:<br>       | ·<br>·               |                            |                  | :<br>:<br>       | :<br>;<br>;                                                                                 | ;<br>;                | 1                         | :<br>:<br>:<br>:<br>: |

| Verito to<br>SSP (804<br>Verito to<br>SSP (804<br>Veto |   |    | •<br>•<br>•<br>• | ><br>;<br>;<br>;     | *<br>*<br>5<br>5<br>5      | •<br>•<br>•<br>• | •<br>•<br>•      | c<br>c<br>c<br>c<br>c<br>c<br>c<br>c<br>c<br>c<br>c<br>c<br>c<br>c<br>c<br>c<br>c<br>c<br>c | *<br>*<br>:<br>:      | •<br>•<br>•<br>•          | •<br>•<br>•<br>•      |

| 300                                                    |   | ¥( | X 68 6           | X 22. 8              | X 888.4                    | X 38.3           | X_346.2          | X 22.3                                                                                      | X                     | :<br>                     | <br>                  |

| -<br>                                                  |   |    |                  |                      |                            | ;<br>,           |                  |                                                                                             |                       | \$ <i>\\\\\\</i><br>\$. 3 |                       |

| inersei<br>Semple                                      |   |    |                  | ,<br>, ///,<br>,     | :<br>:<br>:<br>:<br>:<br>: | . //p            |                  | ,<br>, <i>1</i> 10,<br>,                                                                    | :<br>: 2<br>:         | ><br>%<br>%<br>           |                       |

| ssprin<br>kierupi<br>Hisg                              |   |    | :                | 5<br>6<br>5<br>6<br> | •<br>•<br>•<br>•           | :<br>:<br>:<br>: | :<br>:<br>:      |                                                                                             | ,<br>,<br>,<br>,<br>, | •<br>•<br>•<br>•          |                       |