Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                          |

|----------------------------|----------------------------------------------------------|

| Product Status             | Obsolete                                                 |

| Core Processor             | ARM® Cortex®-M3                                          |

| Core Size                  | 32-Bit Single-Core                                       |

| Speed                      | 48MHz                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT               |

| Number of I/O              | 47                                                       |

| Program Memory Size        | 64KB (64K x 8)                                           |

| Program Memory Type        | FLASH                                                    |

| EEPROM Size                | -                                                        |

| RAM Size                   | 8K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                             |

| Data Converters            | A/D 10x10b; D/A 1x10b                                    |

| Oscillator Type            | Internal                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                        |

| Mounting Type              | Surface Mount                                            |

| Package / Case             | 64-LQFP                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atsam3n1ba-au |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 11.13.3.5 Examples

```

ASR R7, R8, #9 ; Arithmetic shift right by 9 bits

LSLS R1, R2, #3 ; Logical shift left by 3 bits with flag update

LSR R4, R5, #6 ; Logical shift right by 6 bits

ROR R4, R5, R6 ; Rotate right by the value in the bottom byte of R6

RRX R4, R5 ; Rotate right with extend

```

# 11.14 Multiply and divide instructions

Table 11-21 shows the multiply and divide instructions:

Table 11-21. Multiply and divide instructions

| Mnemonic | Brief description                                           | See                                          |

|----------|-------------------------------------------------------------|----------------------------------------------|

| MLA      | Multiply with Accumulate, 32-bit result                     | "MUL, MLA, and MLS" on page 114              |

| MLS      | Multiply and Subtract, 32-bit result                        | "MUL, MLA, and MLS" on page 114              |

| MUL      | Multiply, 32-bit result                                     | "MUL, MLA, and MLS" on page 114              |

| SDIV     | Signed Divide                                               | "SDIV and UDIV" on page 116                  |

| SMLAL    | Signed Multiply with Accumulate (32x32+64), 64-bit result   | "UMULL, UMLAL, SMULL, and SMLAL" on page 115 |

| SMULL    | Signed Multiply (32x32), 64-bit result                      | "UMULL, UMLAL, SMULL, and SMLAL" on page 115 |

| UDIV     | Unsigned Divide                                             | "SDIV and UDIV" on page 116                  |

| UMLAL    | Unsigned Multiply with Accumulate (32x32+64), 64-bit result | "UMULL, UMLAL, SMULL, and SMLAL" on page 115 |

| UMULL    | Unsigned Multiply (32x32), 64-bit result                    | "UMULL, UMLAL, SMULL, and SMLAL" on page 115 |

# 13.4 Functional Description

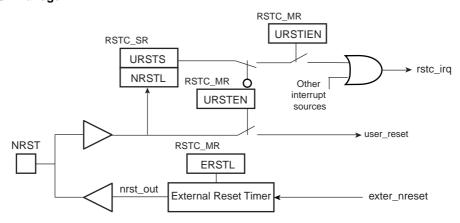

#### 13.4.1 Reset Controller Overview

The Reset Controller is made up of an NRST Manager and a Reset State Manager. It runs at Slow Clock and generates the following reset signals:

- proc\_nreset: Processor reset line. It also resets the Watchdog Timer.

- periph\_nreset: Affects the whole set of embedded peripherals.

- nrst\_out: Drives the NRST pin.

These reset signals are asserted by the Reset Controller, either on external events or on software action. The Reset State Manager controls the generation of reset signals and provides a signal to the NRST Manager when an assertion of the NRST pin is required.

The NRST Manager shapes the NRST assertion during a programmable time, thus controlling external device resets.

The Reset Controller Mode Register (RSTC\_MR), allowing the configuration of the Reset Controller, is powered with VDDIO, so that its configuration is saved as long as VDDIO is on.

### 13.4.2 NRST Manager

After power-up, NRST is an output during the ERSTL time period defined in the RSTC\_MR. When ERSTL has elapsed, the pin behaves as an input and all the system is held in reset if NRST is tied to GND by an external signal.

The NRST Manager samples the NRST input pin and drives this pin low when required by the Reset State Manager. Figure 13-2 shows the block diagram of the NRST Manager.

Figure 13-2. NRST Manager

#### 13.4.2.1 NRST Signal or Interrupt

The NRST Manager samples the NRST pin at Slow Clock speed. When the line is detected low, a User Reset is reported to the Reset State Manager.

However, the NRST Manager can be programmed to not trigger a reset when an assertion of NRST occurs. Writing the bit URSTEN at 0 in RSTC\_MR disables the User Reset trigger.

The level of the pin NRST can be read at any time in the bit NRSTL (NRST level) in RSTC\_SR. As soon as the pin NRST is asserted, the bit URSTS in RSTC\_SR is set. This bit clears only when RSTC\_SR is read.

The Reset Controller can also be programmed to generate an interrupt instead of generating a reset. To do so, the bit URSTIEN in RSTC MR must be written at 1.

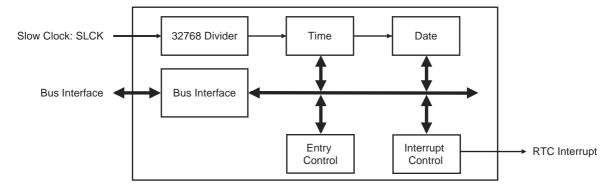

# 15. Real Time Clock (RTC)

# 15.1 Description

The Real-time Clock (RTC) peripheral is designed for very low power consumption.

It combines a complete time-of-day clock with alarm and a two-hundred-year Gregorian calendar, complemented by a programmable periodic interrupt. The alarm and calendar registers are accessed by a 32-bit data bus.

The time and calendar values are coded in binary-coded decimal (BCD) format. The time format can be 24-hour mode or 12-hour mode with an AM/PM indicator.

Updating time and calendar fields and configuring the alarm fields are performed by a parallel capture on the 32-bit data bus. An entry control is performed to avoid loading registers with incompatible BCD format data or with an incompatible date according to the current month/year/century.

### 15.2 Embedded Characteristics

- Low Power Consumption

- Full asynchronous design

- Two hundred year calendar

- Programmable Periodic Interrupt

- Alarm and update parallel load

- Control of alarm and update Time/Calendar Data In

# 15.3 Block Diagram

Figure 15-1. RTC Block Diagram

# 23.4 Functional Description

### 23.4.1 Configuration

The PDC channel user interface enables the user to configure and control data transfers for each channel. The user interface of each PDC channel is integrated into the associated peripheral user interface.

The user interface of a serial peripheral, whether it is full or half duplex, contains four 32-bit pointers (RPR, RNPR, TPR, TNPR) and four 16-bit counter registers (RCR, RNCR, TCR, TNCR). However, the transmit and receive parts of each type are programmed differently: the transmit and receive parts of a full duplex peripheral can be programmed at the same time, whereas only one part (transmit or receive) of a half duplex peripheral can be programmed at a time.

32-bit pointers define the access location in memory for current and next transfer, whether it is for read (transmit) or write (receive). 16-bit counters define the size of current and next transfers. It is possible, at any moment, to read the number of transfers left for each channel.

The PDC has dedicated status registers which indicate if the transfer is enabled or disabled for each channel. The status for each channel is located in the associated peripheral status register. Transfers can be enabled and/or disabled by setting TXTEN/TXTDIS and RXTEN/RXTDIS in the peripheral's Transfer Control Register.

At the end of a transfer, the PDC channel sends status flags to its associated peripheral. These flags are visible in the peripheral status register (ENDRX, ENDTX, RXBUFF, and TXBUFE). Refer to Section 23.4.3 and to the associated peripheral user interface.

### 23.4.2 Memory Pointers

Each full duplex peripheral is connected to the PDC by a receive channel and a transmit channel. Both channels have 32-bit memory pointers that point respectively to a receive area and to a transmit area in on- and/or off-chip memory.

Each half duplex peripheral is connected to the PDC by a bidirectional channel. This channel has two 32-bit memory pointers, one for current transfer and the other for next transfer. These pointers point to transmit or receive data depending on the operating mode of the peripheral.

Depending on the type of transfer (byte, half-word or word), the memory pointer is incremented respectively by 1, 2 or 4 bytes.

If a memory pointer address changes in the middle of a transfer, the PDC channel continues operating using the new address.

### 23.4.3 Transfer Counters

Each channel has two 16-bit counters, one for current transfer and the other one for next transfer. These counters define the size of data to be transferred by the channel. The current transfer counter is decremented first as the data addressed by current memory pointer starts to be transferred. When the current transfer counter reaches zero, the channel checks its next transfer counter. If the value of next counter is zero, the channel stops transferring data and sets the appropriate flag. But if the next counter value is greater then zero, the values of the next pointer/next counter are copied into the current pointer/current counter and the channel resumes the transfer whereas next pointer/next counter get zero/zero as values. At the end of this transfer the PDC channel sets the appropriate flags in the Peripheral Status Register.

The following list gives an overview of how status register flags behave depending on the counters' values:

- ENDRX flag is set when the PERIPH\_RCR register reaches zero.

- RXBUFF flag is set when both PERIPH RCR and PERIPH RNCR reach zero.

- ENDTX flag is set when the PERIPH\_TCR register reaches zero.

- TXBUFE flag is set when both PERIPH TCR and PERIPH TNCR reach zero.

# 23.5.2 Receive Counter Register

Name: PERIPH\_RCR

Access: Read-write

| 31 | 30    | 29 | 28 | 27 | 26 | 25 | 24 |

|----|-------|----|----|----|----|----|----|

| _  | _     | _  | _  | _  | _  | _  | _  |

| 23 | 22    | 21 | 20 | 19 | 18 | 17 | 16 |

| _  | _     | _  | _  | _  | _  | -  | _  |

| 15 | 14    | 13 | 12 | 11 | 10 | 9  | 8  |

|    | RXCTR |    |    |    |    |    |    |

| 7  | 6     | 5  | 4  | 3  | 2  | 1  | 0  |

|    | RXCTR |    |    |    |    |    |    |

### • RXCTR: Receive Counter Register

RXCTR must be set to receive buffer size.

When a half duplex peripheral is connected to the PDC, RXCTR = TXCTR.

0 = Stops peripheral data transfer to the receiver

1 - 65535 = Starts peripheral data transfer if corresponding channel is active

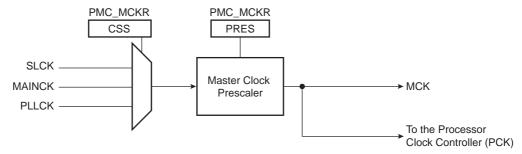

Figure 25-2. Master Clock Controller

#### 25.5 Processor Clock Controller

The PMC features a Processor Clock Controller (HCLK) that implements the Processor Sleep Mode. The Processor Clock can be disabled by executing the WFI (WaitForInterrupt) or the WFE (WaitForEvent) processor instruction once the LPM bit is at 0 in the PMC Fast Startup Mode Register (PMC FSMR).

The Processor Clock HCLK is enabled after a reset and is automatically re-enabled by any enabled interrupt. The Processor Sleep Mode is achieved by disabling the Processor Clock, which is automatically re-enabled by any enabled fast or normal interrupt, or by the reset of the product.

When Processor Sleep Mode is entered, the current instruction is finished before the clock is stopped, but this does not prevent data transfers from other masters of the system bus.

### 25.6 SysTick Clock

The SysTick calibration value is fixed at 6000 which allows the generation of a time base of 1 ms with SysTick clock at 6 MHz (max MCK/8).

# 25.7 Peripheral Clock Controller

The Power Management Controller controls the clocks of each embedded peripheral by means of the Peripheral Clock Controller. The user can individually enable and disable the Clock on the peripherals.

The user can also enable and disable these clocks by writing Peripheral Clock Enable (PMC\_PCER) and Peripheral Clock Disable (PMC\_PCDR) registers. The status of the peripheral clock activity can be read in the Peripheral Clock Status Register (PMC\_PCSR).

When a peripheral clock is disabled, the clock is immediately stopped. The peripheral clocks are automatically disabled after a reset.

In order to stop a peripheral, it is recommended that the system software wait until the peripheral has executed its last programmed operation before disabling the clock. This is to avoid data corruption or erroneous behavior of the system.

The bit number within the Peripheral Clock Control registers (PMC\_PCER, PMC\_PCDR and PMC\_PCSR) is the Peripheral Identifier defined at the product level. The bit number corresponds to the interrupt source number assigned to the peripheral.

# 25.8 Free Running Processor Clock

The Free running processor clock (FCLK) used for sampling interrupts and clocking debug blocks ensures that interrupts can be sampled, and sleep events can be traced, while the processor is sleeping. It is connected to Master Clock (MCK).

# 25.9 Programmable Clock Output Controller

The PMC controls 3 signals to be output on external pins, PCKx. Each signal can be independently programmed via the PMC\_PCKx registers.

PCKx can be independently selected between the Slow Clock (SLCK), the Main Clock (MAINCK), the PLL Clock (PLLCK) and the Master Clock (MCK) by writing the CSS field in PMC\_PCKx. Each output signal can also be divided by a power of 2 between 1 and 64 by writing the PRES (Prescaler) field in PMC\_PCKx.

Each output signal can be enabled and disabled by writing 1 in the corresponding bit, PCKx of PMC\_SCER and PMC\_SCDR, respectively. Status of the active programmable output clocks are given in the PCKx bits of PMC\_SCSR (System Clock Status Register).

Moreover, like the PCK, a status bit in PMC\_SR indicates that the Programmable Clock is actually what has been programmed in the Programmable Clock registers.

As the Programmable Clock Controller does not manage with glitch prevention when switching clocks, it is strongly recommended to disable the Programmable Clock before any configuration change and to re-enable it after the change is actually performed.

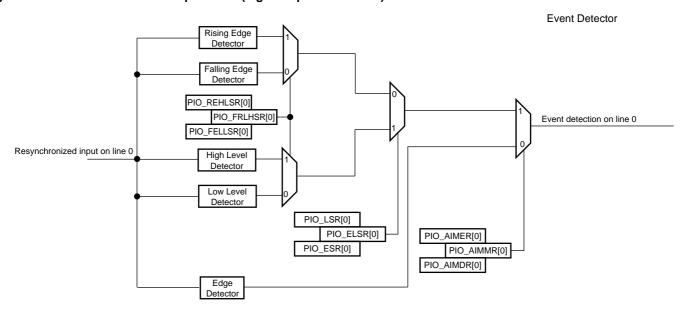

These Additional Modes are:

- Rising Edge Detection

- Falling Edge Detection

- Low Level Detection

- High Level Detection

In order to select an Additional Interrupt Mode:

- The type of event detection (Edge or Level) must be selected by writing in the set of registers; PIO\_ESR (Edge Select Register) and PIO\_LSR (Level Select Register) which enable respectively, the Edge and Level Detection. The current status of this selection is accessible through the PIO\_ELSR (Edge/Level Status Register).

- The Polarity of the event detection (Rising/Falling Edge or High/Low Level) must be selected by writing in the set of registers; PIO\_FELLSR (Falling Edge /Low Level Select Register) and PIO\_REHLSR (Rising Edge/High Level Select Register) which allow to select Falling or Rising Edge (if Edge is selected in the PIO\_ELSR) Edge or High or Low Level Detection (if Level is selected in the PIO\_ELSR). The current status of this selection is accessible through the PIO\_FRLHSR (Fall/Rise - Low/High Status Register).

When an input Edge or Level is detected on an I/O line, the corresponding bit in PIO\_ISR (Interrupt Status Register) is set. If the corresponding bit in PIO\_IMR is set, the PIO Controller interrupt line is asserted. The interrupt signals of the thirty-two channels are ORed-wired together to generate a single interrupt signal to the . Nested Vector Interrupt Controller (NVIC).

When the software reads PIO\_ISR, all the interrupts are automatically cleared. This signifies that all the interrupts that are pending when PIO\_ISR is read must be handled. When an Interrupt is enabled on a "Level", the interrupt is generated as long as the interrupt source is not cleared, even if some read accesses in PIO\_ISR are performed.

Figure 27-7. Event Detector on Input Lines (Figure represents line 0)

# 27.7.16 PIO Interrupt Mask Register

Name: PIO\_IMR

**Addresses:** 0x400E0E48 (PIOA), 0x400E1048 (PIOB), 0x400E1248 (PIOC)

Access: Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

# • P0-P31: Input Change Interrupt Mask

0 = Input Change Interrupt is disabled on the I/O line.

1 = Input Change Interrupt is enabled on the I/O line.

# 27.7.45 PIO Lock Status Register

Name: PIO\_LOCKSR

**Addresses:** 0x400E0EE0 (PIOA), 0x400E10E0 (PIOB), 0x400E12E0 (PIOC)

Access: Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

### • P0-P31: Lock Status.

0 =The I/O line is not locked.

1 = The I/O line is locked.

• ACPC: RC Compare Effect on TIOA

| Value | Name   | Description |

|-------|--------|-------------|

| 0     | NONE   | None        |

| 1     | SET    | Set         |

| 2     | CLEAR  | Clear       |

| 3     | TOGGLE | Toggle      |

### • AEEVT: External Event Effect on TIOA

| Value | Name   | Description |

|-------|--------|-------------|

| 0     | NONE   | None        |

| 1     | SET    | Set         |

| 2     | CLEAR  | Clear       |

| 3     | TOGGLE | Toggle      |

ASWTRG: Software Trigger Effect on TIOA

| Value | Name   | Description |

|-------|--------|-------------|

| 0     | NONE   | None        |

| 1     | SET    | Set         |

| 2     | CLEAR  | Clear       |

| 3     | TOGGLE | Toggle      |

• BCPB: RB Compare Effect on TIOB

| Value | Name   | Description |  |  |

|-------|--------|-------------|--|--|

| 0     | NONE   | None        |  |  |

| 1     | SET    | Set         |  |  |

| 2     | CLEAR  | Clear       |  |  |

| 3     | TOGGLE | Toggle      |  |  |

• BCPC: RC Compare Effect on TIOB

| Value | Name   | Description |

|-------|--------|-------------|

| 0     | NONE   | None        |

| 1     | SET    | Set         |

| 2     | CLEAR  | Clear       |

| 3     | TOGGLE | Toggle      |

# • BEEVT: External Event Effect on TIOB

| Value | Name   | Description |

|-------|--------|-------------|

| 0     | NONE   | None        |

| 1     | SET    | Set         |

| 2     | CLEAR  | Clear       |

| 3     | TOGGLE | Toggle      |

# 32.7.4 TC Stepper Motor Mode Register

Name:  $TC_SMMRx[x=0..2]$

**Address:** 0x40010008 (0)[0], 0x40010048 (0)[1], 0x40010088 (0)[2], 0x40014008 (1)[0], 0x40014048 (1)[1],

0x40014088 (1)[2]

Access: Read/Write

| 31 | 30 | 29 | 28 | 27 | 26 | 25   | 24   |

|----|----|----|----|----|----|------|------|

| _  | -  | _  | _  | -  | -  | -    | -    |

| 23 | 22 | 21 | 20 | 19 | 18 | 17   | 16   |

| _  | _  | -  | -  | 1  | _  | _    | _    |

|    |    |    |    |    |    |      |      |

| 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8    |

| _  | _  | -  | -  | -  | _  | _    | _    |

|    |    |    |    |    |    |      |      |

| 7  | 6  | 5  | 4  | 3  | 2  | 1    | 0    |

| _  | -  | _  | _  | _  | -  | DOWN | GCEN |

This register can only be written if the WPEN bit is cleared in the TC Write Protection Mode Register.

### • GCEN: Gray Count Enable

0: TIOAx [x=0..2] and TIOBx [x=0..2] are driven by internal counter of channel x.

1: TIOAx [x=0..2] and TIOBx [x=0..2] are driven by a 2-bit gray counter.

### • DOWN: Down Count

0: Up counter.

1: Down counter.

# 32.7.8 TC Register C

Name:  $TC_RCx[x=0..2]$

Address: 0x4001001C (0)[0], 0x4001005C (0)[1], 0x4001009C (0)[2], 0x4001401C (1)[0], 0x4001405C (1)[1],

0x4001409C (1)[2]

Access: Read/Write

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |  |

|----|----|----|----|----|----|----|----|--|

|    | RC |    |    |    |    |    |    |  |

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |  |

|    | RC |    |    |    |    |    |    |  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |  |

| RC |    |    |    |    |    |    |    |  |

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |

| RC |    |    |    |    |    |    |    |  |

This register can only be written if the WPEN bit is cleared in the TC Write Protection Mode Register.

# • RC: Register C

RC contains the Register C value in real time.

IMPORTANT: For 16-bit channels, RC field size is limited to register bits 15:0.

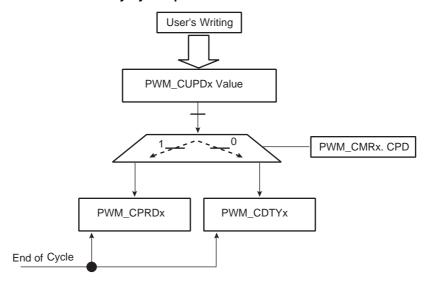

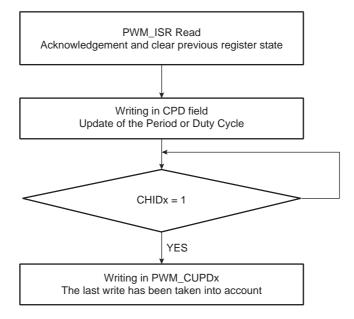

Figure 33-6. Synchronized Period or Duty Cycle Update

To prevent overwriting the PWM\_CUPDx by software, the user can use status events in order to synchronize his software. Two methods are possible. In both, the user must enable the dedicated interrupt in PWM\_IER at PWM Controller level.

The first method (polling method) consists of reading the relevant status bit in PWM\_ISR Register according to the enabled channel(s). See Figure 33-7.

The second method uses an Interrupt Service Routine associated with the PWM channel.

Note: Reading the PWM\_ISR register automatically clears CHIDx flags.

Figure 33-7. Polling Method

Note: Polarity and alignment can be modified only when the channel is disabled.

# 34.7.8 ADC Last Converted Data Register

Name: ADC\_LCDR

Address: 0x40038020

Access: Read-only

|       | -  |     |    |       |    |    |    |

|-------|----|-----|----|-------|----|----|----|

| 31    | 30 | 29  | 28 | 27    | 26 | 25 | 24 |

| _     | _  | _   | _  | _     | _  | _  | _  |

| 23    | 22 | 21  | 20 | 19    | 18 | 17 | 16 |

| _     | _  | _   | _  | _     | _  | -  | _  |

| 15    | 14 | 13  | 12 | 11    | 10 | 9  | 8  |

|       | CH | INB |    | LDATA |    |    |    |

| 7     | 6  | 5   | 4  | 3     | 2  | 1  | 0  |

| LDATA |    |     |    |       |    |    |    |

### • LDATA: Last Data Converted

The analog-to-digital conversion data is placed into this register at the end of a conversion and remains until a new conversion is completed.

#### • CHNB: Channel Number

Indicates the last converted channel when the TAG option is set to 1 in ADC\_EMR register. If TAG option is not set, CHNB = 0.

# 35. Digital to Analog Converter Controller (DACC)

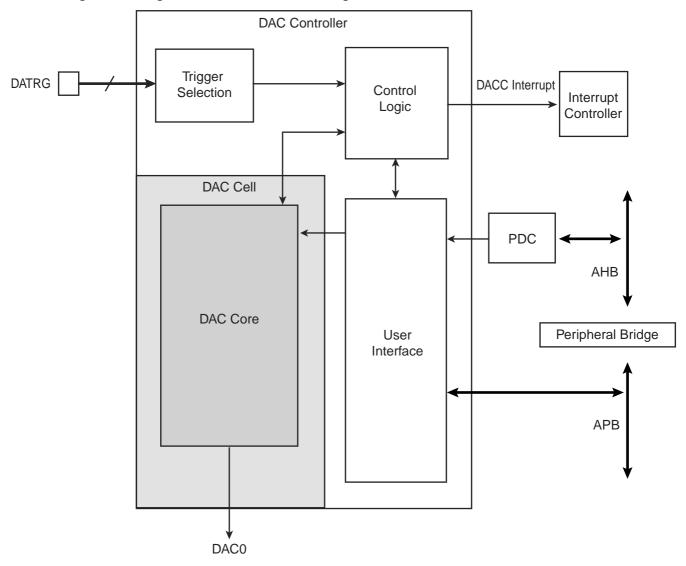

# 35.1 Description

The Digital-to-Analog Converter Controller (DACC) has one analog output, making it possible for the digital-to-analog conversion to drive one analog line.

The DACC supports 10-bit resolution and data to be converted are sent in a common register. External triggers, through the ext\_trig pins, or internal triggers are configurable.

The DACC Controller connects with a PDC channel. This feature reduces processor intervention.

Finally, the user can configure DACC timings such as Startup Time and the Internal Trigger Period.

### 35.2 Embedded Characteristics

- 1 channel 10-bit DAC

- Up to 500 ksamples/s conversion rate

- Flexible conversion range

- Multiple trigger sources

- One PDC channel

# 35.3 Block Diagram

Figure 35-1. Digital-to-Analog Converter Controller Block Diagram

# 35.4 Signal Description

Table 35-1. DAC Pin Description

| Pin Name | Description           |

|----------|-----------------------|

| DAC0     | Analog output channel |

| DATRG    | External triggers     |

# 35.7.8 DACC Write Protect Mode Register

Name: DACC\_WPMR

Address: 0x4003C0E4

Access: Read-write

| 31 | 30    | 29 | 28 | 27 | 26 | 25 | 24   |  |

|----|-------|----|----|----|----|----|------|--|

|    | WPKEY |    |    |    |    |    |      |  |

| 23 | 22    | 21 | 20 | 19 | 18 | 17 | 16   |  |

|    | WPKEY |    |    |    |    |    |      |  |

| 15 | 14    | 13 | 12 | 11 | 10 | 9  | 8    |  |

|    | WPKEY |    |    |    |    |    |      |  |

| 7  | 6     | 5  | 4  | 3  | 2  | 1  | 0    |  |

| _  | _     | _  | _  | _  | _  | _  | WPEN |  |

### • WPEN: Write Protect Enable

0 = Disables the Write Protect if WPKEY corresponds to 0x444143 ("DAC" in ASCII).

1 = Enables the Write Protect if WPKEY corresponds to 0x444143 ("DAC" in ASCII).

Protects the DACC Mode Register.

### • WPKEY: Write Protect KEY

This security code is needed to set/reset the WPROT bit value (see Section 35.6.7 "Write Protection Registers" for details). Must be filled with "DAC" ASCII code.

| 35. | Digit | al to Analog Converter Controller (DACC)                     | 693 |  |  |  |  |  |

|-----|-------|--------------------------------------------------------------|-----|--|--|--|--|--|

|     | 35.1  | Description                                                  | 693 |  |  |  |  |  |

|     | 35.2  | Embedded Characteristics                                     | 693 |  |  |  |  |  |

|     | 35.3  | Block Diagram                                                | 694 |  |  |  |  |  |

|     | 35.4  | Signal Description                                           | 694 |  |  |  |  |  |

|     | 35.5  | Product Dependencies                                         | 695 |  |  |  |  |  |

|     | 35.6  | Functional Description                                       | 696 |  |  |  |  |  |

|     | 35.7  | Digital-to-Analog Converter Controller (DACC) User Interface | 698 |  |  |  |  |  |

| 36. | Elec  | trical Characteristics                                       | 708 |  |  |  |  |  |

|     | 36.1  | Absolute Maximum Ratings                                     | 708 |  |  |  |  |  |

|     | 36.2  | DC Characteristics                                           | 709 |  |  |  |  |  |

|     | 36.3  | Power Consumption                                            | 714 |  |  |  |  |  |

|     | 36.4  | Crystal Oscillators Characteristics                          | 722 |  |  |  |  |  |

|     | 36.5  | PLL Characteristics                                          | 728 |  |  |  |  |  |

|     | 36.6  | 10-bit ADC Characteristics                                   | 729 |  |  |  |  |  |

|     | 36.7  | 10-bit DAC Characteristics                                   | 731 |  |  |  |  |  |

|     | 36.8  | AC Characteristics                                           | 732 |  |  |  |  |  |

| 37. | Mecl  | hanical Characteristics                                      | 741 |  |  |  |  |  |

|     | 37.1  | Soldering Profile                                            | 749 |  |  |  |  |  |

|     | 37.2  | Packaging Resources                                          | 749 |  |  |  |  |  |

| 38. | Mark  | king                                                         | 750 |  |  |  |  |  |

| 39. | Orde  | ering Information                                            | 751 |  |  |  |  |  |

| 40. | SAM   | SAM3N Series Errata                                          |     |  |  |  |  |  |

|     | 40.1  | SAM3N4/2/1 Errata - Rev. A Parts                             | 753 |  |  |  |  |  |

|     | 40.2  | Flash Memory                                                 | 753 |  |  |  |  |  |

|     | 40.3  | SAM3N1 Errata - Rev. B Parts / SAM3N0/00 - Rev. A Parts      | 754 |  |  |  |  |  |

| 41. | Revi  | sion History                                                 | 755 |  |  |  |  |  |

| Tab | le of | Contents                                                     | 760 |  |  |  |  |  |