# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                   |

|----------------------------|------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                       |

| Speed                      | 216MHz                                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                             |

| Number of I/O              | 114                                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 256K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                              |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                    |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 144-LQFP                                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f722zct6                    |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 2. STM32F722xx and STM32F723xx features and peripheral counts (continued)

| Peripherals            | STM32F72xRx                           | STM32F72xVx                                        | STM32F72xZx                         | STM32F72xlx         |  |  |  |  |

|------------------------|---------------------------------------|----------------------------------------------------|-------------------------------------|---------------------|--|--|--|--|

| Operating voltage      |                                       | 1.7 to 3                                           | 3.6 V <sup>(8)</sup>                |                     |  |  |  |  |

| Operating temperatures | An                                    | nbient temperatures: -40                           | ) to +85 °C /-40 to +105            | °C                  |  |  |  |  |

|                        | Junction temperature: -40 to + 125 °C |                                                    |                                     |                     |  |  |  |  |

| Package                | LQFP64 <sup>(9)</sup>                 | LQFP100 <sup>(9)</sup><br>WLCSP100 <sup>(10)</sup> | LQFP144<br>UFBGA144 <sup>(10)</sup> | UFBGA176<br>LQFP176 |  |  |  |  |

1. For the LQFP100 package, only FMC Bank1 is available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select.

2. On the STM32F723xx device packages, except the 176-pin ones, the TIM12 is not available, so there are 9 generalpurpose timers.

3. The SPI1, SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I<sup>2</sup>S audio mode.

4. USB OTG HS with the ULPI on the STM32F722xx devices and with integrated HS PHY on the STM32F723xx devices.

5. The SDMMC2 supports a dedicated power rail for clock, command and data 0..4 lines, feature available starting from 144 pin package.

6. The SDMMC2 is not available on the STM32F723Vx devices.

216 MHz maximum frequency for - 40°C to + 85°C ambient temperature range (200 MHz maximum frequency for - 40°C to + 105°C ambient temperature range).

8. V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the internal reset is OFF (refer to Section 2.15.2: Internal reset OFF).

9. Available only on the STM32F722xx devices.

10. Available only on the STM32F723xx devices.

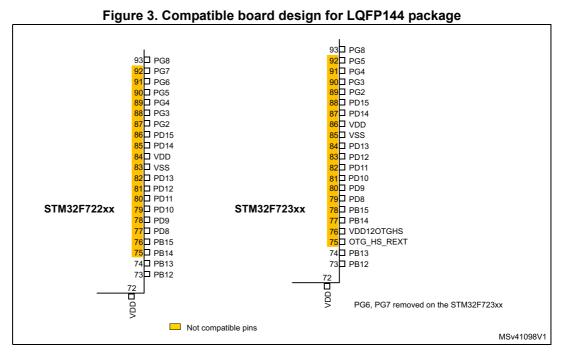

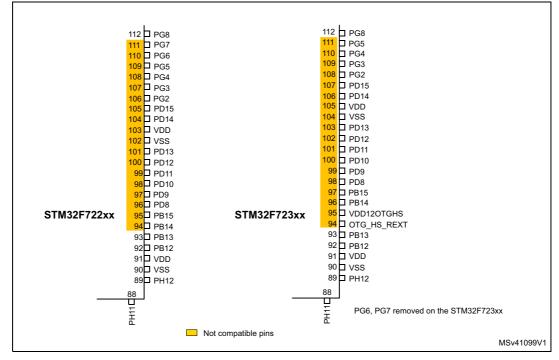

# 1.2 STM32F723xx versus STM32F722xx LQFP144/LQFP176 packages:

Figure 4. Compatible board design for LQFP176 package

DocID029808 Rev 2

2. Available only on the STM32F723xx devices.

## 2 Functional overview

## 2.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M7 with FPU

The ARM<sup>®</sup> Cortex<sup>®</sup>-M7 with FPU processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and low interrupt latency.

The Cortex<sup>®</sup>-M7 processor is a highly efficient high-performance featuring:

- Six-stage dual-issue pipeline

- Dynamic branch prediction

- Harvard caches (8 Kbytes of I-cache and 8 Kbytes of D-cache)

- 64-bit AXI4 interface

- 64-bit ITCM interface

- 2x32-bit DTCM interfaces

The processor supports the following memory interfaces:

- Tightly Coupled Memory (TCM) interface.

- Harvard instruction and data caches and AXI master (AXIM) interface.

- Dedicated low-latency AHB-Lite peripheral (AHBP) interface.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

It supports single precision FPU (floating point unit), speeds up software development by using metalanguage development tools, while avoiding saturation.

Figure 5 shows the general block diagram of the STM32F722xx and STM32F723xx family.

Note: Cortex<sup>®</sup>-M7 with FPU core is binary compatible with the Cortex<sup>®</sup>-M4 core.

## 2.2 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

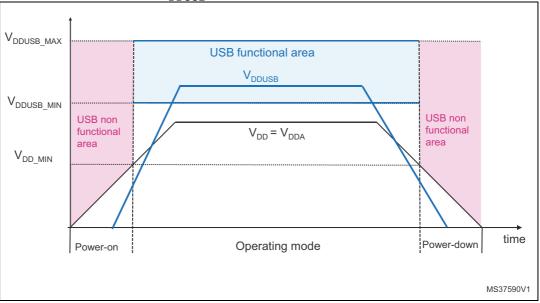

- The V<sub>DDUSB</sub> rising and falling time rate specifications must be respected

- In the operating mode phase, V<sub>DDUSB</sub> could be lower or higher than V<sub>DD</sub>.

- If the USB (USB OTG\_HS/OTG\_FS) is used, the associated GPIOs powered by  $V_{DDUSB}$  are operating between  $V_{DDUSB\ MIN}$  and  $V_{DDUSB\ MAX}.$

- The V<sub>DDUSB</sub> supplies both USB transceiver (USB OTG\_HS and USB OTG\_FS). If only one USB transceiver is used in the application, the GPIOs associated to the other USB transceiver are still supplied by V<sub>DDUSB</sub>.

- If the USB (USB OTG\_HS/OTG\_FS) is not used, the associated GPIOs powered by  $V_{DDUSB}$  are operating between  $V_{DD\_MIN}$  and  $V_{DD\_MAX}.$

### Figure 7. V<sub>DDUSB</sub> connected to V<sub>DD</sub> power supply

### Figure 8. $V_{DDUSB}$ connected to external power supply

On the STM32F7x3xx devices, the USB OTG HS sub-system uses an additional power supply pin:

The VDD12OTGHS pin is the output of PHY HS regulator (1.2V). An external capacitor of 2.2 µF must be connected on the VDD12OTGHS pin.

### 2.15 **Power supply supervisor**

### 2.15.1 Internal reset ON

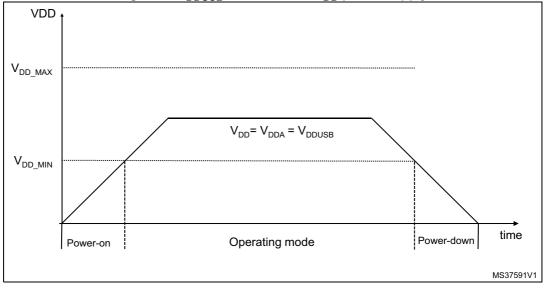

On packages embedding the PDR\_ON pin, the power supply supervisor is enabled by holding PDR\_ON high. On the other packages, the power supply supervisor is always enabled.

The device has an integrated power-on reset (POR)/ power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is reached, the option byte loading process starts, either to confirm or modify default BOR thresholds, or to disable BOR permanently. Three BOR thresholds are available through option bytes. The device remains in reset mode when V<sub>DD</sub> is below a specified threshold, V<sub>POR/PDR</sub> or V<sub>BOR</sub>, without the need for an external reset circuit.

The device also features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

### 2.15.2 Internal reset OFF

This feature is available only on packages featuring the PDR\_ON pin. The internal power-on reset (POR) / power-down reset (PDR) circuitry is disabled through the PDR\_ON pin.

An external power supply supervisor should monitor  $V_{DD}$  and NRST and should maintain the device in reset mode as long as  $V_{DD}$  is below a specified threshold. PDR\_ON should be connected to  $V_{SS}$ . Refer to *Figure 9: Power supply supervisor interconnection with internal reset OFF*.

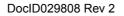

Figure 12. Startup in regulator OFF: slow  $V_{DD}$  slope - power-down reset risen after  $V_{CAP}$   $_1/V_{CAP}$   $_2$  stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

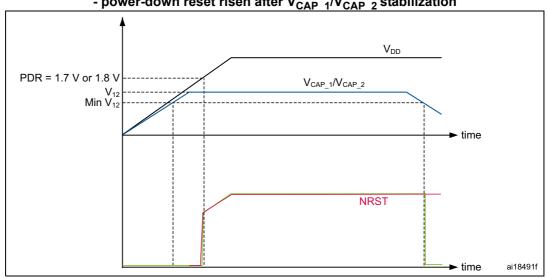

Figure 13. Startup in regulator OFF mode: fast  $V_{DD}$  slope - power-down reset risen before  $V_{CAP_1}/V_{CAP_2}$  stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

### Table 10. STM32F722xx and STM32F723xx pin and ball definition (continued)

|        |         |         |          | Pin N   | lumbe    | r        |          |         |         |                                                      |          |               |            |                                                                                          |                                              |

|--------|---------|---------|----------|---------|----------|----------|----------|---------|---------|------------------------------------------------------|----------|---------------|------------|------------------------------------------------------------------------------------------|----------------------------------------------|

|        | STN     | 132F7   | 22xx     | _       |          | STM      | 32F72    | 3xx     |         |                                                      |          | Ċ,            |            |                                                                                          |                                              |

| LQFP64 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | WLCSP100 | UFBGA176 | UFBGA144 | LQFP144 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes      | Alternate functions                                                                      | Additional<br>functions                      |

| 15     | 23      | 35      | N2       | 41      | J8       | N2       | K2       | 35      | 41      | PA1                                                  | I/O      | FT            | (5)        | TIM2_CH2, TIM5_CH2,<br>USART2_RTS, UART4_RX,<br>QUADSPI_BK1_IO3,<br>SAI2_MCK_B, EVENTOUT | ADC1_IN1,<br>ADC2_IN1,<br>ADC3_IN1           |

| 16     | 24      | 36      | P2       | 42      | H8       | P2       | L2       | 36      | 42      | PA2                                                  | I/O      | FT            | (5)        | TIM2_CH3, TIM5_CH3,<br>TIM9_CH1, USART2_TX,<br>SAI2_SCK_B, EVENTOUT                      | ADC1_IN2,<br>ADC2_IN2,<br>ADC3_IN2,<br>WKUP2 |

| -      | -       | -       | F4       | 43      | -        | F4       | -        | -       | 43      | PH2                                                  | I/O      | FT            |            | LPTIM1_IN2,<br>QUADSPI_BK2_IO0,<br>SAI2_SCK_B, FMC_SDCKE0,<br>EVENTOUT                   | -                                            |

| -      | -       | -       | G4       | 44      | -        | G4       | -        | -       | 44      | PH3                                                  | I/O      | FT            | -          | QUADSPI_BK2_IO1,<br>SAI2_MCK_B, FMC_SDNE0,<br>EVENTOUT                                   | -                                            |

| -      | -       | -       | H4       | 45      | -        | H4       | -        | -       | 45      | PH4                                                  | I/O      | FTf           | (4)        | I2C2_SCL, OTG_HS_ULPI_NXT,<br>EVENTOUT                                                   | -                                            |

| -      | -       | -       | J4       | 46      | -        | J4       | -        | -       | 46      | PH5                                                  | I/O      | FTf           | -          | I2C2_SDA, SPI5_NSS,<br>FMC_SDNWE, EVENTOUT                                               | -                                            |

| 17     | 25      | 37      | R2       | 47      | H7       | R2       | M2       | 37      | 47      | PA3                                                  | I/O      | FT            | (4)<br>(5) | TIM2_CH4, TIM5_CH4,<br>TIM9_CH2, USART2_RX,<br>OTG_HS_ULPI_D0, EVENTOUT                  | ADC1_IN3,<br>ADC2_IN3,<br>ADC3_IN3           |

| 18     | 26      | 38      | -        | -       | K8       | -        | G4       | 38      | -       | VSS                                                  | S        | -             | -          | -                                                                                        | -                                            |

| -      | -       | -       | L4       | 48      | -        | L4       | H5       | -       | 48      | BYPASS_REG                                           | I        | FT            | -          | -                                                                                        | -                                            |

|        |         |         |          |         | Table<br>lumbe |          | rm32f    | -722x   | x and   | I STM32F723xx                                        | pin a    | nd b          | all d | efinition (continued)                                                                     |                        |

|--------|---------|---------|----------|---------|----------------|----------|----------|---------|---------|------------------------------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------|------------------------|

|        | STN     | 132F7   | 22xx     |         |                |          | 32F72    | 3xx     |         |                                                      |          |               |       |                                                                                           |                        |

| LQFP64 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | WLCSP100       | UFBGA176 | UFBGA144 | LQFP144 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                       | Additiona<br>functions |

| -      | -       | -       | C9       | 136     | -              | C9       | -        | -       | 136     | VDD                                                  | S        | -             | -     | -                                                                                         | -                      |

| 49     | 76      | 109     | A14      | 137     | C4             | A14      | A11      | 109     | 137     | PA14(JTCK-<br>SWCLK)                                 | I/O      | FT            | -     | JTCK-SWCLK, EVENTOUT                                                                      | -                      |

| 50     | 77      | 110     | A13      | 138     | B4             | A13      | A10      | 110     | 138     | PA15(JTDI)                                           | I/O      | FT            | -     | JTDI, TIM2_CH1/TIM2_ETR,<br>SPI1_NSS/I2S1_WS,<br>SPI3_NSS/I2S3_WS,<br>UART4_RTS, EVENTOUT | -                      |

| 51     | 78      | 111     | B14      | 139     | A3             | B14      | B11      | 111     | 139     | PC10                                                 | I/O      | FT            | -     | SPI3_SCK/I2S3_CK,<br>USART3_TX, UART4_TX,<br>QUADSPI_BK1_IO1,<br>SDMMC1_D2, EVENTOUT      | -                      |

| 52     | 79      | 112     | B13      | 140     | C5             | B13      | B10      | 112     | 140     | PC11                                                 | I/O      | FT            | -     | SPI3_MISO, USART3_RX,<br>UART4_RX,<br>QUADSPI_BK2_NCS,<br>SDMMC1_D3, EVENTOUT             | -                      |

| 53     | 80      | 113     | A12      | 141     | D5             | A12      | C10      | 113     | 141     | PC12                                                 | I/O      | FT            | -     | TRACED3,<br>SPI3_MOSI/I2S3_SD,<br>USART3_CK, UART5_TX,<br>SDMMC1_CK, EVENTOUT             | -                      |

| -      | 81      | 114     | B12      | 142     | B5             | B12      | E10      | 114     | 142     | PD0                                                  | I/O      | FT            | -     | CAN1_RX, FMC_D2,<br>EVENTOUT                                                              | -                      |

| -      | 82      | 115     | C12      | 143     | A4             | C12      | D10      | 115     | 143     | PD1                                                  | I/O      | FT            | -     | CAN1_TX, FMC_D3,<br>EVENTOUT                                                              | -                      |

DocID029808 Rev 2

5

75/229

STM32F722xx STM32F723xx

Pinouts and pin description

96/229

DocID029808 Rev 2

|        |      |     | Iu     |          | 5110152172              |                     |                                                  | 2000 010                                                 |                                                  | ction mapp                              |                                                      |                                                     |        |                                      |              |

|--------|------|-----|--------|----------|-------------------------|---------------------|--------------------------------------------------|----------------------------------------------------------|--------------------------------------------------|-----------------------------------------|------------------------------------------------------|-----------------------------------------------------|--------|--------------------------------------|--------------|

|        |      | AF0 | AF1    | AF2      | AF3                     | AF4                 | AF5                                              | AF6                                                      | AF7                                              | AF8                                     | AF9                                                  | AF10                                                | AF11   | AF12                                 | AF15         |

| Po     | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10/1<br>1/LPTIM1 | I2C1/2/3/U<br>SART1 | SPI1/I2S1/<br>SPI2/I2S2/<br>SPI3/I2S3/<br>SPI4/5 | SPI2/I2S2/<br>SPI3/I2S3/<br>SPI3/I2S3/<br>SAI1/<br>UART4 | SPI2/I2S2/S<br>PI3/I2S3/US<br>ART1/2/3/UA<br>RT5 | SAI2/USART<br>6/UART4/5/7/<br>8/OTG1_FS | CAN1/TIM1<br>2/13/14/QU<br>ADSPI/<br>FMC/<br>OTG2_HS | SAI2/QUAD<br>SPI/SDMM<br>C2/OTG2_<br>HS/OTG1_<br>FS | SDMMC2 | UART7/F<br>MC/SDM<br>MC1/<br>OTG2_FS | SYS          |

|        | PI7  | -   | -      | -        | TIM8_CH3                | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | SAI2_FS_A                                           | -      | FMC_D29                              | EVEN<br>TOUT |

|        | PI8  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -      | -                                    | EVEN<br>TOUT |

|        | PI9  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | UART4_RX                                | CAN1_RX                                              | -                                                   | -      | FMC_D30                              | EVEN<br>TOUT |

|        | PI10 | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -      | FMC_D31                              | EVEN<br>TOUT |

| Port I | PI11 | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | OTG_HS_U<br>LPI_DIR                                 | -      | -                                    | EVEN<br>TOUT |

|        | PI12 | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -      | -                                    | EVEN<br>TOUT |

|        | PI13 | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -      | -                                    | EVEN<br>TOUT |

|        | PI14 | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -      | -                                    | EVEN<br>TOUT |

|        | PI15 | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -      | -                                    | EVEN<br>TOUT |

### Table 12. STM32F722xx and STM32F723xx alternate function mapping (continued)

### 5.3.13 USB OTG HS PHY PLLs characteristics (on STM32F723xx devices)

The parameters given in *Table 49* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Symbol                 | Parameter                        | Conditions | Min    | Тур                  | Max  | Unit |  |

|------------------------|----------------------------------|------------|--------|----------------------|------|------|--|

| f <sub>PLL1_IN</sub>   | PLL1 input clock                 | -          | 12, 12 | 12, 12.5, 16, 24, 25 |      |      |  |

| f <sub>PLL1_OUT</sub>  | PLL1 output clock <sup>(2)</sup> | -          | -      | 60                   | -    | MHz  |  |

| f <sub>VCO_OUT</sub>   | PLL1 VCO output                  | -          | 600    | -                    | 720  |      |  |

| t <sub>LOCK</sub>      | PLL1 lock time <sup>(2)</sup>    | -          | -      | -                    | 22   | μs   |  |

| I <sub>DD(PLL1)</sub>  | PLL1 digital power consumption   | -          | -      | -                    | 1.8  | mA   |  |

| I <sub>DDA(PLL1)</sub> | PLL1 analog power consumption    | -          | -      | -                    | 2.75 |      |  |

1. Guaranteed by design.

2. Based on test during characterization.

| Table 50. USB OTG HS | PLL2 characteris | tics <sup>(1)</sup> |  |

|----------------------|------------------|---------------------|--|

|                      |                  |                     |  |

| Symbol                 | Parameter                        | Conditions | Min | Тур | Max | Unit |

|------------------------|----------------------------------|------------|-----|-----|-----|------|

| f <sub>PLL2_IN</sub>   | PLL2 input clock                 | -          | -   | 60  | -   |      |

| f <sub>PLL2_OUT</sub>  | PLL2 output clock <sup>(2)</sup> | -          | -   | 480 | -   | MHz  |

| f <sub>VCO_OUT</sub>   | PLL2 VCO output                  | -          | -   | 480 | -   |      |

| t <sub>LOCK</sub>      | PLL2 lock time <sup>(2)</sup>    | -          | -   | -   | 91  | μs   |

| I <sub>DD(PLL2)</sub>  | PLL2 digital power consumption   | -          | -   | -   | 2.1 | mA   |

| I <sub>DDA(PLL2)</sub> | PLL2 analog power consumption    | _          | -   | -   | 1.5 | ША   |

1. Guaranteed by design.

2. Based on test during characterization.

# 5.3.14 USB OTG HS PHY regulator characteristics (on STM32F723xx devices)

The parameters given in *Table 51* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

|                        | Table 91. 00D 010 110 1111 legula                |            | 1131103 |     |      |      |

|------------------------|--------------------------------------------------|------------|---------|-----|------|------|

| Symbol                 | Parameter                                        | Conditions | Min     | Тур | Max  | Unit |

| V <sub>DD12OTGHS</sub> | 1.2 V internal voltage on V <sub>DD12OTGHS</sub> | -          | 1.18    | 1.2 | 1.24 | V    |

| CEXT                   | External capacitor on V <sub>DD12OTGHS</sub>     | -          | 1.1     | 2.2 | 3.3  | μF   |

| IDDPHYHSREG            | Regulator power consumption                      | -          | 100     | 120 | 125  | μA   |

Table 51. USB OTG HS PHY regulator characteristics<sup>(1)</sup>

1. Based on test during characterization.

# 5.3.15 USB HS PHY external resistor characteristics (on STM32F723xx devices)

### Table 52. USB HS PHY external resistor characteristics (on STM32F723xx devices)

| Symbol | Parameter                                                         | Conditions                      | Min  | Тур  | Max  | Unit |

|--------|-------------------------------------------------------------------|---------------------------------|------|------|------|------|

| REXT   | External calibration resistor connected (to GND) from OTG_HS_REXT | Required if using<br>USB HS PHY | 2.97 | 3.00 | 3.03 | kΩ   |

### 5.3.16 Memory characteristics

### **Flash memory**

The characteristics are given at TA = -40 to 105 °C unless otherwise specified.

The devices are shipped to customers with the Flash memory erased.

Table 53. Flash memory characteristics

| Symbol                       | Parameter | Conditions                                  |   | Тур  | Max | Unit |

|------------------------------|-----------|---------------------------------------------|---|------|-----|------|

| I <sub>DD</sub> Supply curre |           | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V  | - | 6.7  | -   |      |

|                              |           | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V | - | 9.2  | -   | mA   |

|                              |           | Write / Erase 32-bit mode, $V_{DD}$ = 3.3 V | - | 12.6 | -   |      |

Table 54. Flash memory programming

| Symbol                  | Parameter Conditions       |                                                  | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 346  | 418                |      |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 252  | 312                | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 208  | 265                |      |

|                         | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1953 | 2500               |      |

| t <sub>ERASE128KB</sub> |                            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 1252 | 1639               | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 927  | 1322               |      |

| terase64kb              | Sector (64 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1027 | 1298               |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 675  | 840                | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 505  | 682                |      |

### Static latchup

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

### 5.3.19 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibilty to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of – 5  $\mu$ A/+0  $\mu$ A range), or other functional failure (for example reset, oscillator frequency deviation).

Negative induced leakage current is caused by negative injection and positive induced leakage current by positive injection.

The test results are given in Table 61.

|                  |                                                                                                                        | Functional s |                    |      |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--------------|--------------------|------|--|

| Symbol           | Description                                                                                                            |              | Positive injection | Unit |  |

|                  | Injected current on BOOT0, PDR_ON, BYPASS_REG,<br>OTG_HS_REXT                                                          | -0           | 0                  |      |  |

|                  | Injected current on NRST                                                                                               | -0           | NA                 |      |  |

| I <sub>INJ</sub> | Injected current on PF9, PF10, PH0_OSCIN, PH1_OSCOUT, PC0,<br>PC1, PC2, PC3, PB14 <sup>(2)</sup> , PB15 <sup>(2)</sup> | -0           | NA                 | mA   |  |

|                  | Injected current on any other FT or FTf pins                                                                           | -5           | NA                 |      |  |

|                  | Injected current on any other pins                                                                                     | -5           | +5                 |      |  |

### Table 61. I/O current injection susceptibility<sup>(1)</sup>

1. NA = not applicable.

| Symbol                         | Parameter                                                                                                                           | Conditions                                                                                             | Min                                 | Max                | Unit |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin                                                                                             | CMOS port <sup>(2)</sup><br>I <sub>IO</sub> = +8 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V                   | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin except PC14                                                                                | CMOS port <sup>(2)</sup><br>I <sub>IO</sub> = -8 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V                   | V <sub>DD</sub> - 0.4               | -                  | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for PC14                                                                                                  | CMOS port <sup>(2)</sup><br>$I_{IO} = -2 \text{ mA}$<br>$2.7 \text{ V} \leq V_{DD} \leq 3.6 \text{ V}$ | V <sub>DD</sub> - 0.4               | -                  |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin                                                                                             | TTL port <sup>(2)</sup><br>I <sub>IO</sub> =+8mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V                      | -                                   | 0.4                | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin except PC14                                                                                | TTL port <sup>(2)</sup><br>I <sub>IO</sub> =-8mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V                      | 2.4                                 | -                  |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin                                                                                             | I <sub>IO</sub> = +20 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V                                              | -                                   | 1.3 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin<br>except PC14                                                                             | I <sub>IO</sub> = -20 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V                                              | V <sub>DD</sub> -1.3 <sup>(4)</sup> | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin                                                                                             | I <sub>IO</sub> = +6 mA<br>1.8 V ≤V <sub>DD</sub> ≤3.6 V                                               | -                                   | 0.4 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin $I_{IO} = -6 \text{ mA}$ $V_{DD} = -0.4$ except PC141.8 V $\leq V_{DD} \leq 3.6 \text{ V}$ |                                                                                                        | V <sub>DD</sub> -0.4 <sup>(4)</sup> | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin                                                                                             | I <sub>IO</sub> = +4 mA<br>1.7 V ≤V <sub>DD</sub> ≤3.6V                                                | -                                   | 0.4 <sup>(5)</sup> |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin except PC14                                                                                | I <sub>IO</sub> = -4 mA<br>1.7 V ≤V <sub>DD</sub> ≤3.6V                                                | V <sub>DD</sub> -0.4 <sup>(5)</sup> | -                  | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for PC14                                                                                                  | I <sub>IO</sub> = -1 mA<br>1.7 V ≤V <sub>DD</sub> ≤3.6V                                                | V <sub>DD</sub> -0.4 <sup>(5)</sup> | -                  |      |

| Table 63. | Output voltage characteristics |

|-----------|--------------------------------|

|-----------|--------------------------------|

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 15*. and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 15 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

- 4. Based on characterization data.

- 5. Guaranteed by design.

### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 45* and *Table 64*, respectively.

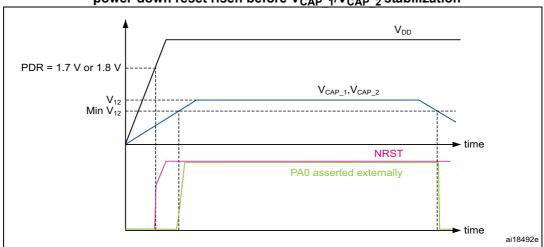

Figure 47. ADC accuracy characteristics

- 1. See also Table 70.

- 2. Example of an actual transfer curve.

- 3. Ideal transfer curve.

- 4 End point correlation line.

$E_T$  = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. 5.

EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

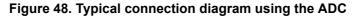

- Refer to Table 68 for the values of  $\mathsf{R}_{AIN},\,\mathsf{R}_{ADC}$  and  $\mathsf{C}_{ADC}.$ 1.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 5 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced. 2.

| Symbol                    | Parameter                                                 | Min        | Max        | Unit |

|---------------------------|-----------------------------------------------------------|------------|------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                           | 2Thclk -1  | 2Thclk +1  |      |

| t <sub>v(NOE_NE)</sub>    | FMC_NEx low to FMC_NOE low                                | 0          | 0.5        |      |

| t <sub>w(NOE)</sub>       | FMC_NOE low time                                          | 2Thclk -1  | 2Thclk +1  |      |

| t <sub>h(NE_NOE)</sub>    | FMC_NOE high to FMC_NE high hold time                     | 0          | -          |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                                | -          | 0.5        | 1    |

| t <sub>h(A_NOE)</sub>     | NOE) Address hold time after FMC_NOE high                 |            | -          |      |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid                               | -          | 0.5        | ns   |

| t <sub>h(BL_NOE)</sub>    | FMC_BL hold time after FMC_NOE high                       | 0          | -          | 115  |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time                           | Thclk -1.5 | -          |      |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOEx high setup time                          | Thclk -1.5 | -          |      |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FMC_NOE high                         | 0          | -          |      |

| t <sub>h(Data_NE)</sub>   | t <sub>h(Data_NE)</sub> Data hold time after FMC_NEx high |            | -          |      |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low                               | -          | 0          | ]    |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                                         | -          | Thclk -0.5 |      |

Table 94. Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings<sup>(1)</sup>

1. C<sub>L</sub> = 30 pF.

| Table 95. Asynchronous non-multiplexed SRAM/PSRAM/NOR read - NWAIT | <sup>·</sup> timings <sup>(1)</sup> |

|--------------------------------------------------------------------|-------------------------------------|

|--------------------------------------------------------------------|-------------------------------------|

| Symbol                    | Parameter                                    | Min        | Max       | Unit |

|---------------------------|----------------------------------------------|------------|-----------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                              | 7Thclk +1  | 7Thclk +1 |      |

| t <sub>w(NOE)</sub>       | FMC_NWE low time                             | 5Thclk -1  | 5Thclk +1 | ns   |

| t <sub>w(NWAIT)</sub>     | FMC_NWAIT low time                           | Thclk -0.5 | -         | 110  |

| t <sub>su(NWAIT_NE)</sub> | WAIT_NE) FMC_NWAIT valid before FMC_NEx high |            | -         |      |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid    | 4Thclk +1  | -         |      |

1. Guaranteed by characterization results.

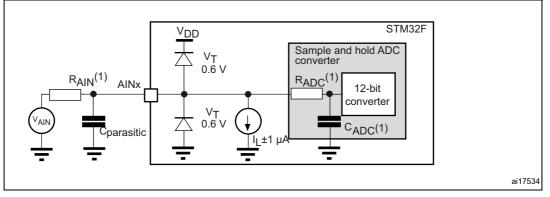

Figure 65. Synchronous multiplexed NOR/PSRAM read timings

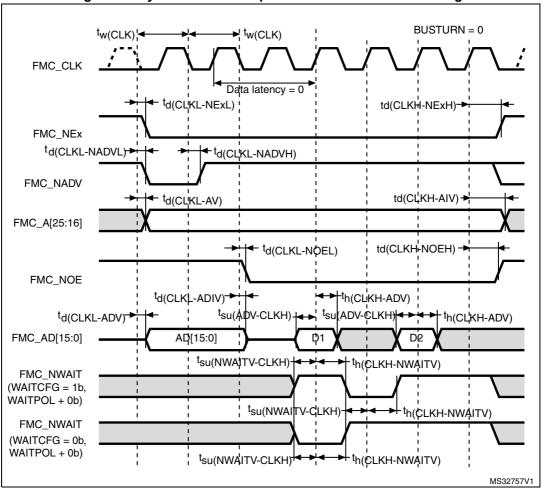

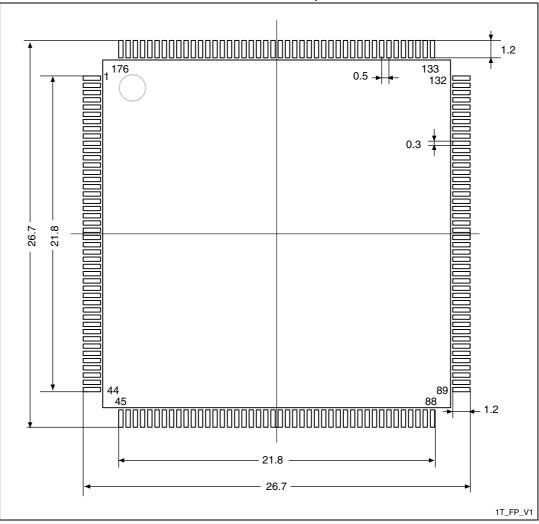

## 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 6.1 LQFP64 – 10 x 10 mm, low-profile quad flat package information

Figure 79. LQFP64 – 10 x 10 mm, low-profile quad flat package outline

1. Drawing is not to scale.

| Symbol |       | millimeters |      |        | inches <sup>(1)</sup> |        |  |

|--------|-------|-------------|------|--------|-----------------------|--------|--|

| Symbol | Min   | Тур         | Мах  | Min    | Тур                   | Max    |  |

| А      | -     | -           | 1.60 | -      | -                     | 0.0630 |  |

| A1     | 0.05  | -           | 0.15 | 0.0020 | -                     | 0.0059 |  |

| A2     | 1.350 | 1.40        | 1.45 | 0.0531 | 0.0551                | 0.0571 |  |

| b      | 0.17  | 0.22        | 0.27 | 0.0067 | 0.0087                | 0.0106 |  |

Figure 89. LQFP176, 24 x 24 mm, 176-pin low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

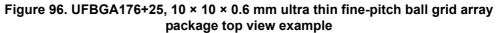

### UFBGA176+25 device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

## **Revision history**

| Date        | Revision | Changes                                                                                                         |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------|

| 03-Feb-2017 | 1        | Initial release.                                                                                                |

| 30-Mar-2017 | 2        | Updated cover with the maximum SPI speed at 54 Mbit/s.<br>Updated <i>Figure 14: STM32F722xx LQFP64 pinout</i> . |

### Table 129. Document revision history