#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                   |

|----------------------------|------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                       |

| Speed                      | 216MHz                                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                             |

| Number of I/O              | 112                                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 256K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                              |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                    |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 144-LQFP                                                                                 |

| Supplier Device Package    | 144-LQFP (20x20)                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f723zet6                    |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 2. STM32F722xx and STM32F723xx features and peripheral counts (continued)

| Peripherals            | STM32F72xRx                                         | STM32F72xlx                                        |                                     |                     |  |  |  |  |  |  |  |

|------------------------|-----------------------------------------------------|----------------------------------------------------|-------------------------------------|---------------------|--|--|--|--|--|--|--|

| Operating voltage      | 1.7 to 3.6 V <sup>(8)</sup>                         |                                                    |                                     |                     |  |  |  |  |  |  |  |

| Operating temperatures | Ambient temperatures: -40 to +85 °C /-40 to +105 °C |                                                    |                                     |                     |  |  |  |  |  |  |  |

|                        | Junction temperature: -40 to + 125 °C               |                                                    |                                     |                     |  |  |  |  |  |  |  |

| Package                | LQFP64 <sup>(9)</sup>                               | LQFP100 <sup>(9)</sup><br>WLCSP100 <sup>(10)</sup> | LQFP144<br>UFBGA144 <sup>(10)</sup> | UFBGA176<br>LQFP176 |  |  |  |  |  |  |  |

1. For the LQFP100 package, only FMC Bank1 is available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select.

2. On the STM32F723xx device packages, except the 176-pin ones, the TIM12 is not available, so there are 9 generalpurpose timers.

3. The SPI1, SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I<sup>2</sup>S audio mode.

4. USB OTG HS with the ULPI on the STM32F722xx devices and with integrated HS PHY on the STM32F723xx devices.

5. The SDMMC2 supports a dedicated power rail for clock, command and data 0..4 lines, feature available starting from 144 pin package.

6. The SDMMC2 is not available on the STM32F723Vx devices.

216 MHz maximum frequency for - 40°C to + 85°C ambient temperature range (200 MHz maximum frequency for - 40°C to + 105°C ambient temperature range).

8. V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the internal reset is OFF (refer to Section 2.15.2: Internal reset OFF).

9. Available only on the STM32F722xx devices.

10. Available only on the STM32F723xx devices.

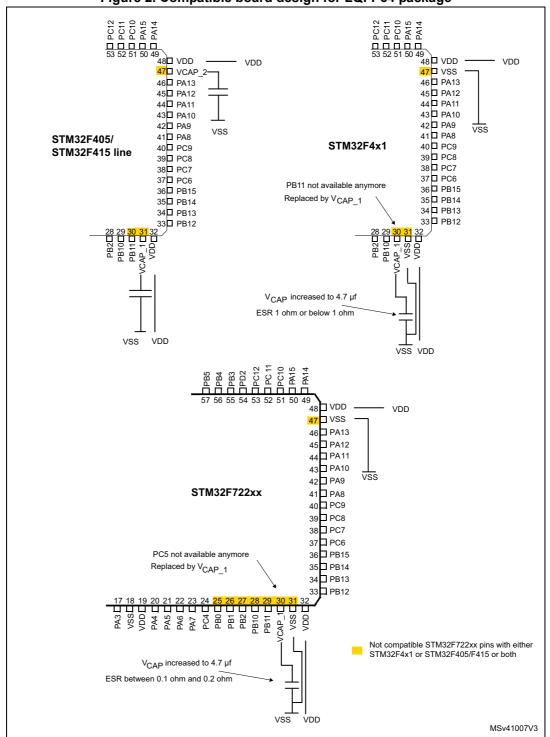

Figure 2. Compatible board design for LQFP64 package

The STM32F722xx LQFP144, UFBGA176 and LQFP176 packages are fully pin to pin compatible with the STM32F4xx devices.

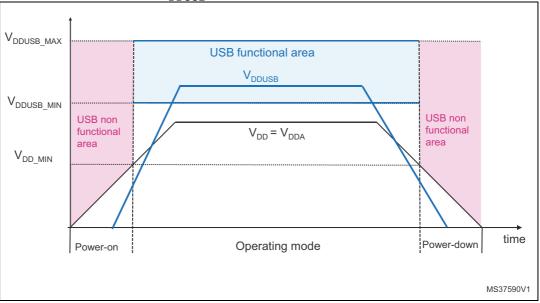

- The V<sub>DDUSB</sub> rising and falling time rate specifications must be respected

- In the operating mode phase, V<sub>DDUSB</sub> could be lower or higher than V<sub>DD</sub>.

- If the USB (USB OTG\_HS/OTG\_FS) is used, the associated GPIOs powered by  $V_{DDUSB}$  are operating between  $V_{DDUSB\ MIN}$  and  $V_{DDUSB\ MAX}.$

- The V<sub>DDUSB</sub> supplies both USB transceiver (USB OTG\_HS and USB OTG\_FS). If only one USB transceiver is used in the application, the GPIOs associated to the other USB transceiver are still supplied by V<sub>DDUSB</sub>.

- If the USB (USB OTG\_HS/OTG\_FS) is not used, the associated GPIOs powered by  $V_{DDUSB}$  are operating between  $V_{DD\_MIN}$  and  $V_{DD\_MAX}.$

#### Figure 7. V<sub>DDUSB</sub> connected to V<sub>DD</sub> power supply

#### Figure 8. $V_{DDUSB}$ connected to external power supply

On the STM32F7x3xx devices, the USB OTG HS sub-system uses an additional power supply pin:

The VDD12OTGHS pin is the output of PHY HS regulator (1.2V). An external capacitor of 2.2 µF must be connected on the VDD12OTGHS pin.

### 2.15 **Power supply supervisor**

#### 2.15.1 Internal reset ON

On packages embedding the PDR\_ON pin, the power supply supervisor is enabled by holding PDR\_ON high. On the other packages, the power supply supervisor is always enabled.

The device has an integrated power-on reset (POR)/ power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is reached, the option byte loading process starts, either to confirm or modify default BOR thresholds, or to disable BOR permanently. Three BOR thresholds are available through option bytes. The device remains in reset mode when V<sub>DD</sub> is below a specified threshold, V<sub>POR/PDR</sub> or V<sub>BOR</sub>, without the need for an external reset circuit.

The device also features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

#### 2.15.2 Internal reset OFF

This feature is available only on packages featuring the PDR\_ON pin. The internal power-on reset (POR) / power-down reset (PDR) circuitry is disabled through the PDR\_ON pin.

An external power supply supervisor should monitor  $V_{DD}$  and NRST and should maintain the device in reset mode as long as  $V_{DD}$  is below a specified threshold. PDR\_ON should be connected to  $V_{SS}$ . Refer to *Figure 9: Power supply supervisor interconnection with internal reset OFF*.

All the RTC events (Alarm, WakeUp Timer, Timestamp or Tamper) can generate an interrupt and wakeup the device from the low-power modes.

#### 2.18 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The voltage regulator can be put either in main regulator mode (MR) or in low-power mode (LPR). Both modes can be configured as follows (see *Table 5: Voltage regulator modes in stop mode*):

- Normal mode (default mode when MR or LPR is enabled)

- Under-drive mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup and the LPTIM1 asynchronous interrupt).

| Voltage regulator<br>configuration | Main regulator (MR)    | Low-power regulator (LPR) |

|------------------------------------|------------------------|---------------------------|

| Normal mode                        | MR ON                  | LPR ON                    |

| Under-drive mode                   | MR in under-drive mode | LPR in under-drive mode   |

#### Table 5. Voltage regulator modes in stop mode

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising or falling edge on one of the 6 WKUP pins (PA0, PA2, PC1, PC13, PI8, PI11), or an RTC alarm / wakeup / tamper /time stamp event occurs.

The Standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

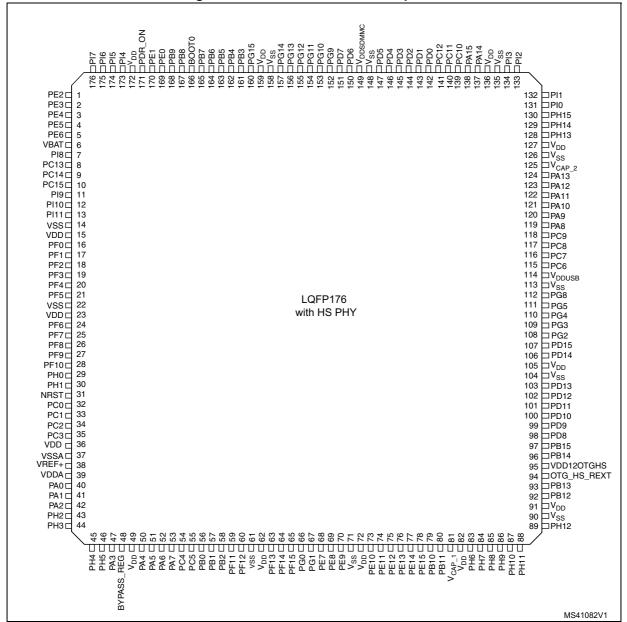

#### Figure 21. STM32F723xx LQFP176 pinout

1. The above figure shows the package top view.

DocID029808 Rev 2

|        |         |         |          |         | Table '  | 10. S <sup>-</sup> | ГМ32     | =722x   | x and   | d STM32F723xx                                                                               | pin a                                                                | and b         | all d            | efinition (continued)                                                           |                                                               |  |

|--------|---------|---------|----------|---------|----------|--------------------|----------|---------|---------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------|------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------|--|

|        |         |         |          | Pin N   | lumbei   | r                  |          |         |         |                                                                                             |                                                                      |               |                  |                                                                                 |                                                               |  |

|        | STN     | 132F7   | 22xx     |         |          | STM                | 32F72    | 3xx     |         |                                                                                             |                                                                      | <i>a</i>      |                  |                                                                                 |                                                               |  |

| LQFP64 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | WLCSP100 | UFBGA176           | UFBGA144 | LQFP144 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup>                                        | Pin type                                                             | I/O structure | Notes            | Alternate functions                                                             | Additional<br>functions                                       |  |

| -      | -       | 20      | L3       | 26      | -        | L3                 | G3       | 20      | 26      | PF8                                                                                         | I/O                                                                  | FT            | -                | SPI5_MISO, SAI1_SCK_B,<br>UART7_RTS, TIM13_CH1,<br>QUADSPI_BK1_IO0,<br>EVENTOUT | ADC3_IN6                                                      |  |

| -      | -       | 21      | L2       | 27      | -        | L2                 | G2       | 21      | 27      | PF9 I/O FT - SPI5_MOSI, SAI1_FS_B,<br>UART7_CTS, TIM14_CH1,<br>QUADSPI_BK1_IO1,<br>EVENTOUT |                                                                      | ADC3_IN7      |                  |                                                                                 |                                                               |  |

| -      | -       | 22      | L1       | 28      | -        | L1                 | G1       | 22      | 28      | PF10                                                                                        | I/O                                                                  | FT            | -                | EVENTOUT                                                                        | ADC3_IN8                                                      |  |

| 5      | 12      | 23      | G1       | 29      | G10      | G1                 | D1       | 23      | 29      | PH0-OSC_IN                                                                                  | I/O                                                                  | FT            | -                | EVENTOUT                                                                        | OSC_IN <sup>(5)</sup>                                         |  |

| 6      | 13      | 24      | H1       | 30      | H10      | H1                 | E1       | 24      | 30      | PH1-OSC_OUT                                                                                 | I/O                                                                  | FT            | -                | EVENTOUT                                                                        | OSC_OUT <sup>(5)</sup>                                        |  |

| 7      | 14      | 25      | J1       | 31      | G9       | J1                 | F1       | 25      | 31      | NRST                                                                                        | I/O                                                                  | RS<br>T       | -                | -                                                                               | -                                                             |  |

| 8      | 15      | 26      | M2       | 32      | F8       | M2                 | H1       | 26      | 32      | PC0                                                                                         | I/O FT (4) SAI2_FS_B,<br>(5) OTG_HS_ULPI_STP,<br>FMC_SDNWE, EVENTOUT |               | OTG_HS_ULPI_STP, | ADC1_IN10,<br>ADC2_IN10,<br>ADC3_IN10                                           |                                                               |  |

| 9      | 16      | 27      | М3       | 33      | H9       | М3                 | H2       | 27      | 33      | PC1                                                                                         | I/O                                                                  | FT            | (5)              | TRACED0,<br>SPI2_MOSI/I2S2_SD,<br>SAI1_SD_A, EVENTOUT                           | ADC1_IN11,<br>ADC2_IN11,<br>ADC3_IN11,<br>RTC_TAMP3,<br>WKUP3 |  |

62/229

5

66/229

DocID029808 Rev 2

|       | Table 10. STM32F722xx and STM32F723xx pin and ball definition (continued)         Pin Number |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin N | lumber                                                                                       |  |  |  |  |  |  |

| ~~    | 0714005300                                                                                   |  |  |  |  |  |  |

|        | STM32F722xx |         |          |         | STM      | 32F72    | 3xx      |         |         |                                                      |                                                                                              |               |                       |                                                                |                         |  |

|--------|-------------|---------|----------|---------|----------|----------|----------|---------|---------|------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------|-----------------------|----------------------------------------------------------------|-------------------------|--|

| LQFP64 | LQFP100     | LQFP144 | UFBGA176 | LQFP176 | WLCSP100 | UFBGA176 | UFBGA144 | LQFP144 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type                                                                                     | I/O structure | Notes                 | Alternate functions                                            | Additional<br>functions |  |

| 25     | 34          | 46      | R5       | 56      | F5       | R5       | L4       | 46      | 56      | PB0                                                  | PB0 I/O FT (4) TIM1_CH2N, TIM3_CH3,<br>(5) TIM8_CH2N, UART4_CTS,<br>OTG_HS_ULPI_D1, EVENTOUT |               | ADC1_IN8,<br>ADC2_IN8 |                                                                |                         |  |

| 26     | 35          | 47      | R4       | 57      | G5       | R4       | M4       | 47      | 57      | PB1                                                  | I/O                                                                                          | FT            | (4)<br>(5)            | TIM1_CH3N, TIM3_CH4,<br>TIM8_CH3N,<br>OTG_HS_ULPI_D2, EVENTOUT | ADC1_IN9,<br>ADC2_IN9   |  |

| 27     | 36          | 48      | M6       | 58      | K6       | M6       | J5       | 48      | 58      | PB2                                                  | I/O                                                                                          | FT            | -                     | SAI1_SD_A,<br>SPI3_MOSI/I2S3_SD,<br>QUADSPI_CLK, EVENTOUT      | -                       |  |

| -      | -           | 49      | R6       | 59      | -        | R6       | M5       | 49      | 59      | PF11                                                 | I/O                                                                                          | FT            | -                     | SPI5_MOSI, SAI2_SD_B,<br>FMC_SDNRAS, EVENTOUT                  | -                       |  |

| -      | -           | 50      | P6       | 60      | -        | P6       | L5       | 50      | 60      | PF12                                                 | I/O                                                                                          | FT            | -                     | FMC_A6, EVENTOUT                                               | -                       |  |

| -      | -           | 51      | M8       | 61      | -        | M8       | -        | 51      | 61      | VSS                                                  | S                                                                                            | -             | -                     | -                                                              | -                       |  |

| -      | -           | 52      | N8       | 62      | -        | N8       | G5       | 52      | 62      | VDD                                                  | S                                                                                            | -             | -                     | -                                                              | -                       |  |

| -      | -           | 53      | N6       | 63      | -        | N6       | K5       | 53      | 63      | PF13                                                 | I/O                                                                                          | FT            | -                     | FMC_A7, EVENTOUT                                               | -                       |  |

| -      | -           | 54      | R7       | 64      | -        | R7       | M6       | 54      | 64      | PF14                                                 | I/O                                                                                          | FT            | -                     | FMC_A8, EVENTOUT                                               | -                       |  |

| -      | -           | 55      | P7       | 65      | -        | P7       | L6       | 55      | 65      | PF15                                                 | I/O                                                                                          | FT            | -                     | FMC_A9, EVENTOUT                                               | -                       |  |

| -      | -           | 56      | N7       | 66      | -        | N7       | K6       | 56      | 66      | PG0                                                  | I/O                                                                                          | FT            | -                     | FMC_A10, EVENTOUT                                              | -                       |  |

| -      | -           | 57      | M7       | 67      | -        | M7       | J6       | 57      | 67      | PG1                                                  | I/O                                                                                          | FT            | -                     | FMC_A11, EVENTOUT                                              | -                       |  |

68/229

DocID029808 Rev 2

|        |         |         |          | •       | Table    | 10. ST   | ГМЗ2Р    | 722x    | x and   | STM32F723xx                                          | pin a                                                  | nd b          | all d | lefinition (continued)                                                             |                         |  |

|--------|---------|---------|----------|---------|----------|----------|----------|---------|---------|------------------------------------------------------|--------------------------------------------------------|---------------|-------|------------------------------------------------------------------------------------|-------------------------|--|

|        |         |         |          | Pin N   | lumbe    | r        |          |         |         |                                                      |                                                        |               |       |                                                                                    |                         |  |

|        | STN     | 132F7   | 22xx     | 1       |          | STM      | 32F72    | 3xx     | 1       |                                                      |                                                        | ø             |       |                                                                                    |                         |  |

| LQFP64 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | WLCSP100 | UFBGA176 | UFBGA144 | LQFP144 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type                                               | I/O structure | Notes | Alternate functions                                                                | Additional<br>functions |  |

| -      | 44      | 67      | P11      | 77      | K4       | P11      | L8       | 67      | 77      | PE14                                                 | I/O                                                    | FT            | -     | TIM1_CH4, SPI4_MOSI,<br>SAI2_MCK_B, FMC_D11,,<br>EVENTOUT                          | -                       |  |

| -      | 45      | 68      | R11      | 78      | F4       | R11      | M8       | 68      | 78      | PE15                                                 | I/O                                                    | FT            | -     | TIM1_BKIN, FMC_D12,<br>EVENTOUT                                                    | -                       |  |

| 28     | 46      | 69      | R12      | 79      | G3       | R12      | M9       | 69      | 79      | PB10                                                 | I/O                                                    | FTf           | (4)   | TIM2_CH3, I2C2_SCL,<br>SPI2_SCK/I2S2_CK,<br>USART3_TX,<br>OTG_HS_ULPI_D3, EVENTOUT | -                       |  |

| 29     | 47      | 70      | R13      | 80      | H3       | R13      | M10      | 70      | 80      | PB11                                                 | I/O                                                    | FTf           | (4)   | TIM2_CH4, I2C2_SDA,<br>USART3_RX,<br>OTG_HS_ULPI_D4, EVENTOUT                      | -                       |  |

| 30     | 48      | 71      | M10      | 81      | J3       | M10      | H7       | 71      | 81      | VCAP_1                                               | S                                                      | -             | -     | -                                                                                  | -                       |  |

| 31     | 49      | -       | -        | -       | K3       | -        | -        | -       | -       | VSS                                                  | S                                                      | -             | -     | -                                                                                  | -                       |  |

| 32     | 50      | 72      | N10      | 82      | K2       | N10      | G7       | 72      | 82      | VDD                                                  | S                                                      | -             | -     | -                                                                                  | -                       |  |

| -      | -       | -       | M11      | 83      | -        | M11      | -        | -       | 83      | PH6                                                  | I/O                                                    | FT            | -     | I2C2_SMBA, SPI5_SCK,<br>TIM12_CH1, FMC_SDNE1,<br>EVENTOUT                          | -                       |  |

| -      | -       | -       | N12      | 84      | -        | N12      | -        | -       | 84      | PH7                                                  | I/O FTF - I2C3_SCL, SPI5_MISO,<br>FMC_SDCKE1, EVENTOUT |               | -     |                                                                                    |                         |  |

| -      | -       | -       | M12      | 85      | -        | M12      | -        | -       | 85      | PH8                                                  | I/O                                                    | FTf           | -     | I2C3_SDA, FMC_D16,<br>EVENTOUT                                                     | -                       |  |

#### STM32F722xx STM32F723xx

| Pin name | NOR/PSRAM/SR<br>AM | NOR/PSRAM<br>Mux | NAND16 | SDRAM  |  |  |  |  |  |  |  |  |  |

|----------|--------------------|------------------|--------|--------|--|--|--|--|--|--|--|--|--|

| PB7      | NADV               | NADV             | -      | -      |  |  |  |  |  |  |  |  |  |

| PF6      | -                  | -                | -      | -      |  |  |  |  |  |  |  |  |  |

| PF7      | -                  | -                | -      | -      |  |  |  |  |  |  |  |  |  |

| PF8      | -                  | -                | -      | -      |  |  |  |  |  |  |  |  |  |

| PF9      | -                  | -                | -      | -      |  |  |  |  |  |  |  |  |  |

| PF10     | -                  | -                | -      | -      |  |  |  |  |  |  |  |  |  |

| PG6      | -                  | -                | -      | -      |  |  |  |  |  |  |  |  |  |

| PG7      | -                  | -                | INT    | -      |  |  |  |  |  |  |  |  |  |

| PE0      | NBL0               | NBL0             | -      | NBL0   |  |  |  |  |  |  |  |  |  |

| PE1      | NBL1               | NBL1             | -      | NBL1   |  |  |  |  |  |  |  |  |  |

| PI4      | NBL2               | -                | -      | NBL2   |  |  |  |  |  |  |  |  |  |

| PI5      | NBL3               | -                | -      | NBL3   |  |  |  |  |  |  |  |  |  |

| PG8      | -                  | -                | -      | SDCLK  |  |  |  |  |  |  |  |  |  |

| PC0      | -                  | -                | -      | SDNWE  |  |  |  |  |  |  |  |  |  |

| PF11     | -                  | -                | -      | SDNRAS |  |  |  |  |  |  |  |  |  |

| PG15     | -                  | -                | -      | SDNCAS |  |  |  |  |  |  |  |  |  |

| PH2      | -                  | -                | -      | SDCKE0 |  |  |  |  |  |  |  |  |  |

| PH3      | -                  | -                | -      | SDNE0  |  |  |  |  |  |  |  |  |  |

| PH6      | -                  | -                | -      | SDNE1  |  |  |  |  |  |  |  |  |  |

| PH7      | -                  | -                | -      | SDCKE1 |  |  |  |  |  |  |  |  |  |

| PH5      | -                  | -                | -      | SDNWE  |  |  |  |  |  |  |  |  |  |

| PC2      | -                  | -                | -      | SDNE0  |  |  |  |  |  |  |  |  |  |

| PC3      | -                  | -                | -      | SDCKE0 |  |  |  |  |  |  |  |  |  |

| PB5      | -                  | -                | -      | SDCKE1 |  |  |  |  |  |  |  |  |  |

| PB6      | -                  | -                | -      | SDNE1  |  |  |  |  |  |  |  |  |  |

Table 11. FMC pin definition (continued)

| 5 |

|---|

|   |

.

# DocID029808 Rev 2

87/229

|        |      |                   | Та                        | ble 12. S | 6TM32F72                | 2xx and             | STM32F7                                          | 23xx alt                                                 | ernate fun                                       | ction mapp                              | oing (cont                                           | inued)                                              |        |                                      |              |

|--------|------|-------------------|---------------------------|-----------|-------------------------|---------------------|--------------------------------------------------|----------------------------------------------------------|--------------------------------------------------|-----------------------------------------|------------------------------------------------------|-----------------------------------------------------|--------|--------------------------------------|--------------|

|        |      | AF0               | AF1                       | AF2       | AF3                     | AF4                 | AF5                                              | AF6                                                      | AF7                                              | AF8                                     | AF9                                                  | AF10                                                | AF11   | AF12                                 | AF15         |

| Po     | ort  | SYS               | TIM1/2                    | TIM3/4/5  | TIM8/9/10/1<br>1/LPTIM1 | I2C1/2/3/U<br>SART1 | SPI1/I2S1/<br>SPI2/I2S2/<br>SPI3/I2S3/<br>SPI4/5 | SPI2/I2S2/<br>SPI3/I2S3/<br>SPI3/I2S3/<br>SAI1/<br>UART4 | SPI2/I2S2/S<br>PI3/I2S3/US<br>ART1/2/3/UA<br>RT5 | SAI2/USART<br>6/UART4/5/7/<br>8/OTG1_FS | CAN1/TIM1<br>2/13/14/QU<br>ADSPI/<br>FMC/<br>OTG2_HS | SAI2/QUAD<br>SPI/SDMM<br>C2/OTG2_<br>HS/OTG1_<br>FS | SDMMC2 | UART7/F<br>MC/SDM<br>MC1/<br>OTG2_FS | SYS          |

|        | PA12 | -                 | TIM1_ETR                  | -         | -                       | -                   | -                                                | -                                                        | USART1_RT<br>S                                   | SAI2_FS_B                               | CAN1_TX                                              | OTG_FS_D<br>P                                       | -      | -                                    | EVEN<br>TOUT |

|        | PA13 | JTMS-<br>SWDIO    | -                         | -         | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -      | -                                    | EVEN<br>TOUT |

| Port A | PA14 | JTCK-<br>SWCLK    | -                         | -         | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -      | -                                    | EVEN<br>TOUT |

|        | PA15 | JTDI              | TIM2_CH1<br>/TIM2_ET<br>R | -         | -                       | -                   | SPI1_NSS<br>/I2S1_WS                             | SPI3_NSS<br>/I2S3_WS                                     | -                                                | UART4_RTS                               | -                                                    | -                                                   | -      | -                                    | EVEN<br>TOUT |

|        | PB0  | -                 | TIM1_CH2<br>N             | TIM3_CH3  | TIM8_CH2<br>N           | -                   | -                                                | -                                                        | -                                                | UART4_CTS                               |                                                      | OTG_HS_U<br>LPI_D1                                  | -      | -                                    | EVEN<br>TOUT |

|        | PB1  | -                 | TIM1_CH3<br>N             | TIM3_CH4  | TIM8_CH3<br>N           | -                   | -                                                | -                                                        | -                                                | -                                       |                                                      | OTG_HS_U<br>LPI_D2                                  | -      | -                                    | EVEN<br>TOUT |

|        | PB2  | -                 | -                         | -         | -                       | -                   | -                                                | SAI1_SD_<br>A                                            | SPI3_MOSI/I<br>2S3_SD                            |                                         | QUADSPI_<br>CLK                                      | -                                                   | -      | -                                    | EVEN<br>TOUT |

|        | PB3  | JTDO/TR<br>ACESWO | TIM2_CH2                  | -         | -                       | -                   | SPI1_SCK<br>/I2S1_CK                             | SPI3_SCK<br>/I2S3_CK                                     | -                                                | -                                       | -                                                    | SDMMC2_<br>D2                                       | -      | -                                    | EVEN<br>TOUT |

| Port B | PB4  | NJTRST            | -                         | TIM3_CH1  | -                       | -                   | SPI1_MIS<br>O                                    | SPI3_MIS<br>O                                            | SPI2_NSS/I2<br>S2_WS                             | -                                       | -                                                    | SDMMC2_<br>D3                                       | -      | -                                    | EVEN<br>TOUT |

|        | PB5  | -                 | -                         | TIM3_CH2  | -                       | I2C1_SMB<br>A       | SPI1_MO<br>SI/I2S1_S<br>D                        | SPI3_MO<br>SI/I2S3_S<br>D                                | -                                                | -                                       | -                                                    | OTG_HS_U<br>LPI_D7                                  | -      | FMC_SDC<br>KE1                       | EVEN<br>TOUT |

|        | PB6  | -                 | -                         | TIM4_CH1  | -                       | I2C1_SCL            | -                                                | -                                                        | USART1_TX                                        | -                                       | -                                                    | QUADSPI_<br>BK1_NCS                                 | -      | FMC_SDN<br>E1                        | EVEN<br>TOUT |

|        | PB7  | -                 | -                         | TIM4_CH2  | -                       | I2C1_SDA            | -                                                | -                                                        | USART1_RX                                        | -                                       | -                                                    | -                                                   | -      | FMC_NL                               | EVEN<br>TOUT |

|        | PB8  | -                 | -                         | TIM4_CH3  | TIM10_CH<br>1           | I2C1_SCL            | -                                                | -                                                        | -                                                | -                                       | CAN1_RX                                              | SDMMC2_<br>D4                                       | -      | SDMMC1<br>_D4                        | EVEN<br>TOUT |

DocID029808 Rev 2

93/229

| Table 12. STM32F722xx and STM32F723xx alternate function mappi | ng (continued) |

|----------------------------------------------------------------|----------------|

|----------------------------------------------------------------|----------------|

|        |      | AF0 | AF1    | AF2      | AF3                     | AF4                 | AF5                                              | AF6                                                      | AF7                                              | AF8                                     | AF9                                                  | AF10                                                | AF11          | AF12                                 | AF1        |

|--------|------|-----|--------|----------|-------------------------|---------------------|--------------------------------------------------|----------------------------------------------------------|--------------------------------------------------|-----------------------------------------|------------------------------------------------------|-----------------------------------------------------|---------------|--------------------------------------|------------|

| Po     | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10/1<br>1/LPTIM1 | I2C1/2/3/U<br>SART1 | SPI1/I2S1/<br>SPI2/I2S2/<br>SPI3/I2S3/<br>SPI4/5 | SPI2/I2S2/<br>SPI3/I2S3/<br>SPI3/I2S3/<br>SAI1/<br>UART4 | SPI2/I2S2/S<br>PI3/I2S3/US<br>ART1/2/3/UA<br>RT5 | SAI2/USART<br>6/UART4/5/7/<br>8/OTG1_FS | CAN1/TIM1<br>2/13/14/QU<br>ADSPI/<br>FMC/<br>OTG2_HS | SAI2/QUAD<br>SPI/SDMM<br>C2/OTG2_<br>HS/OTG1_<br>FS | SDMMC2        | UART7/F<br>MC/SDM<br>MC1/<br>OTG2_FS | SYS        |

|        | PG0  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | FMC_A10                              | EVE<br>TOL |

|        | PG1  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | FMC_A11                              | EVE<br>TOL |

|        | PG2  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | FMC_A12                              | EVE<br>TOL |

|        | PG3  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | FMC_A13                              | EVE<br>TOL |

|        | PG4  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | FMC_A14/<br>FMC_BA0                  | EVE<br>TOL |

| Port G | PG5  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | FMC_A15/<br>FMC_BA1                  | EVE<br>TOL |

|        | PG6  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | -                                                   | -             | -                                    | EVE<br>TOL |

|        | PG7  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | USART6_CK                               | -                                                    | -                                                   | -             | FMC_INT                              | EVE<br>TOU |

|        | PG8  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | USART6_RT<br>S                          | -                                                    | -                                                   | -             | FMC_SDC<br>LK                        | EVE<br>TOU |

|        | PG9  | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | USART6_RX                               | QUADSPI_<br>BK2_IO2                                  | SAI2_FS_B                                           | SDMMC2<br>_D0 | FMC_NE2<br>/FMC_NC<br>E              | EVE<br>TOI |

|        | PG10 | -   | -      | -        | -                       | -                   | -                                                | -                                                        | -                                                | -                                       | -                                                    | SAI2_SD_B                                           | SDMMC2<br>_D1 | FMC_NE3                              | EVI<br>TO  |

Pinouts and pin description

- 7. The over-drive mode is not supported when the internal regulator is OFF.

- 8. To sustain a voltage higher than VDD+0.3, the internal Pull-up and Pull-Down resistors must be disabled

- 9. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

- 10. In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub>.

| Operating<br>power supply<br>range                | ADC operation                     | Maximum Flash<br>memory access<br>frequency with<br>no wait states<br>(f <sub>Flashmax</sub> ) | Maximum HCLK<br>frequency vs Flash<br>memory wait states<br>(1)(2) | I/O operation          | Possible Flash<br>memory<br>operations        |

|---------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------|-----------------------------------------------|

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(3)</sup>   | Conversion time<br>up to 1.2 Msps | 20 MHz                                                                                         | 180 MHz with 8 wait<br>states and over-drive<br>OFF                | No I/O<br>compensation | 8-bit erase and<br>program<br>operations only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                 | Conversion time<br>up to 1.2 Msps | 22 MHz                                                                                         | 216 MHz with 9 wait<br>states and over-drive<br>ON                 | No I/O<br>compensation | 16-bit erase and<br>program<br>operations     |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                 | Conversion time<br>up to 2.4 Msps | 24 MHz                                                                                         | 216 MHz with 8 wait<br>states and over-drive<br>ON                 | I/O compensation works | 16-bit erase and<br>program<br>operations     |

| $V_{DD} = 2.7 \text{ to}$<br>3.6 V <sup>(4)</sup> | Conversion time<br>up to 2.4 Msps | 30 MHz                                                                                         | 216 MHz with 7 wait<br>states and over-drive<br>ON                 | I/O compensation works | 32-bit erase and<br>program<br>operations     |

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

Thanks to the ART accelerator on ITCM interface and L1-cache on AXI interface, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator or L1-cache allows to achieve a performance equivalent to 0-wait state program execution.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 2.17.2: Internal reset OFF).

4. The voltage range for USB full speed PHYs can drop down to 2.7 V. However the electrical characteristics of D- and D+ pins will be degraded between 2.7 and 3 V.

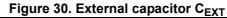

#### 5.3.2 VCAP1/VCAP2 external capacitor

Stabilization for the main regulator is achieved by connecting an external capacitor  $C_{EXT}$  to the VCAP1/VCAP2 pins.  $C_{EXT}$  is specified in *Table 19*.

*Note:* The VCAP2 pin is not available on the LQFP64 package.

1. Legend: ESR is the equivalent series resistance.

| Symbol                            | Parameter                                                            | Conditions | Min | Тур | Max | Unit |

|-----------------------------------|----------------------------------------------------------------------|------------|-----|-----|-----|------|

| I <sub>VREF+</sub> <sup>(2)</sup> | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode | -          | -   | 300 | 500 | μA   |

| I <sub>VDDA</sub> <sup>(2)</sup>  | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode | -          | -   | 1.6 | 1.8 | mA   |

Table 68. ADC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 2.17.2: Internal reset OFF).

2. Guaranteed by characterization results.

3.  $V_{\mathsf{REF}^+}$  is internally connected to  $V_{\mathsf{DDA}}$  and  $V_{\mathsf{REF}^-}$  is internally connected to  $V_{\mathsf{SSA}}.$

4.  $R_{ADC}$  maximum value is given for V<sub>DD</sub>=1.7 V, and minimum value for V<sub>DD</sub>=3.3 V.

5. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in *Table 68*.

#### Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} = \frac{(k - 0.5)}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. N = 12 (from 12-bit resolution) and k is the number of sampling periods defined in the ADC\_SMPR1 register.

| Symbol | Parameter                    | Test conditions                                             | Тур | Max <sup>(1)</sup> | Unit |  |

|--------|------------------------------|-------------------------------------------------------------|-----|--------------------|------|--|

| ET     | Total unadjusted error       |                                                             | ±3  | ±4                 |      |  |

| EO     | Offset error                 | f <sub>ADC</sub> =18 MHz<br>V <sub>DDA</sub> = 1.7 to 3.6 V | ±2  | ±3                 | Ī    |  |

| EG     | Gain error                   | $V_{\text{REF}}$ = 1.7 to 3.6 V                             | ±1  | ±3                 | LSB  |  |

| ED     | Differential linearity error | V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V                  | ±1  | ±2                 | Ī    |  |

| EL     | Integral linearity error     |                                                             | ±2  | ±3                 |      |  |

Table 69. ADC static accuracy at f<sub>ADC</sub> = 18 MHz

1. Guaranteed by characterization results.

| Symbol | Parameter                    | Test conditions                                                                | Тур  | Max <sup>(1)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                | ±2   | ±5                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 30 MHz,<br>R <sub>AIN</sub> < 10 kΩ                         | ±1.5 | ±2.5               |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,                                               | ±1.5 | ±4                 | LSB  |

| ED     | Differential linearity error | V <sub>REF</sub> = 1.7 to 3.6 V,<br>V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                                                                | ±1.5 | ±3                 |      |

1. Guaranteed by characterization results.

1. Guaranteed by characterization results.

| Symbol                    | Parameter                                 | Min         | Max          | Unit |  |  |  |

|---------------------------|-------------------------------------------|-------------|--------------|------|--|--|--|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 9Thclk - 1  | 9Thclk + 1   |      |  |  |  |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 7Thclk -0.5 | 7Thclk + 0.5 | ns   |  |  |  |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6Thclk + 2  | -            |      |  |  |  |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4Thclk - 1  | -            |      |  |  |  |

1. Guaranteed by characterization results.

#### Synchronous waveforms and timings

*Figure 65* through *Figure 68* represent synchronous waveforms and *Table 102* through *Table 105* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- BurstAccessMode = FMC\_BurstAccessMode\_Enable;

- MemoryType = FMC\_MemoryType\_CRAM;

- WriteBurst = FMC\_WriteBurst\_Enable;

- CLKDivision = 1;

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

- CL = 30 pF on data and address lines. CL = 10 pF on FMC\_CLK unless otherwise specified.

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

- For 2.7 V≤V<sub>DD</sub>≤3.6 V, maximum FMC\_CLK = 108 MHz at CL=20 pF or 90 MHz at CL=30 pF (on FMC\_CLK).

- For 1.71 V $\leq$ V<sub>DD</sub><2.7 V, maximum FMC\_CLK = 70 MHz at CL=10 pF (on FMC\_CLK).

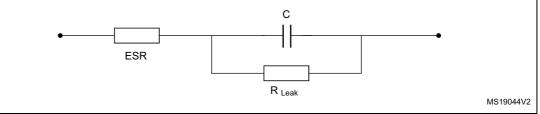

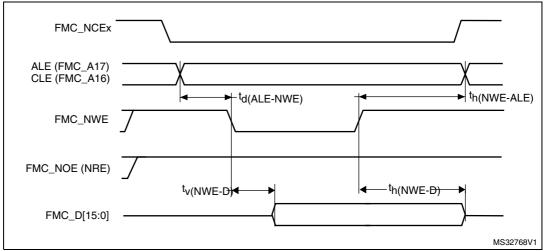

Figure 69. NAND controller waveforms for read access

Figure 70. NAND controller waveforms for write access

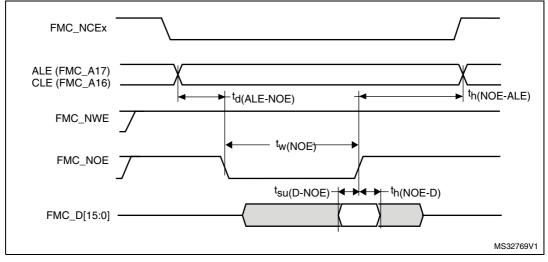

Figure 71. NAND controller waveforms for common memory read access

| Symbol                        | Parameter              | Min         | Max         | Unit |

|-------------------------------|------------------------|-------------|-------------|------|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2Thclk -0.5 | 2Thclk +0.5 |      |

| t <sub>su(SDCLKH _Data)</sub> | Data input setup time  | 1.5         | -           |      |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 2           | -           |      |

| t <sub>d(SDCLKL_Add)</sub>    | Address valid time     | -           | 1.5         |      |

| t <sub>d(SDCLKL</sub> - SDNE) | Chip select valid time | -           | 1.5         | ns   |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 0.5         | -           | 113  |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -           | 1           |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0.5         | -           |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -           | 1.5         |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0           | -           |      |

# Table 108. SDRAM read timings<sup>(1)</sup>

1. Guaranteed by characterization results.

# Table 109. LPSDR SDRAM read timings<sup>(1)</sup>

| Symbol                        | Parameter              | Min         | Мах         | Unit |

|-------------------------------|------------------------|-------------|-------------|------|

| t <sub>W(SDCLK)</sub>         | FMC_SDCLK period       | 2Thclk -0.5 | 2Thclk +0.5 |      |

| t <sub>su(SDCLKH_Data)</sub>  | Data input setup time  | 0           | -           |      |

| t <sub>h(SDCLKH_Data)</sub>   | Data input hold time   | 4.5         | -           |      |

| t <sub>d(SDCLKL_Add)</sub>    | Address valid time     | -           | 1.5         |      |

| t <sub>d(SDCLKL_SDNE)</sub>   | Chip select valid time | -           | 1.5         | ns   |

| t <sub>h(SDCLKL_SDNE)</sub>   | Chip select hold time  | 0           | -           | 115  |

| t <sub>d(SDCLKL_SDNRAS</sub>  | SDNRAS valid time      | -           | 0.5         |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0           | -           |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -           | 1.5         |      |

| t <sub>h(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0           | -           |      |

1. Guaranteed by characterization results.

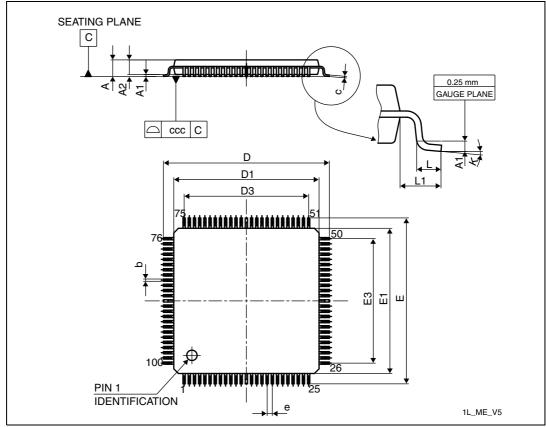

# 6.2 LQFP100, 14 x 14 mm low-profile quad flat package information

Figure 82. LQFP100, 14 x 14 mm 100-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |  |  |

|--------|-------------|--------|--------|-----------------------|--------|--------|--|--|--|

|        | Min         | Тур    | Max    | Min                   | Тур    | Мах    |  |  |  |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |  |  |  |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |  |  |  |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |  |  |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |  |  |

| с      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |  |  |  |

| D      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |  |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |  |

| D3     | -           | 12.000 | -      | -                     | 0.4724 | -      |  |  |  |

| E      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |  |

| Figure 95. UFBGA176+25, 10 x 10 mm x 0.65 mm, ultra fine-pitch ball grid array |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| package recommended footprint                                                  |  |  |  |  |  |  |  |

#### Table 123. UFBGA176+25 recommended PCB design rules (0.65 mm pitch BGA)

| Dimension         | Recommended values                                                    |

|-------------------|-----------------------------------------------------------------------|

| Pitch             | 0.65 mm                                                               |

| Dpad              | 0.300 mm                                                              |

| Dsm               | 0.400 mm typ. (depends on the soldermask reg-<br>istration tolerance) |

| Stencil opening   | 0.300 mm                                                              |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                         |

| Pad trace width   | 0.100 mm                                                              |

## Appendix A Recommendations when using internal reset OFF

When the internal reset is OFF, the following integrated features are no longer supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled.

- The brownout reset (BOR) circuitry must be disabled.

- The embedded programmable voltage detector (PVD) is disabled.

- V<sub>BAT</sub> functionality is no more available and VBAT pin should be connected to V<sub>DD</sub>.

- The over-drive mode is not supported.

# A.1 Operating conditions

# Table 128. Limitations depending on the operating power supply range

| Operating<br>power<br>supply<br>range           | ADC<br>operation                     | Maximum<br>Flash<br>memory<br>access<br>frequency<br>with no wait<br>states<br>(f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency with<br>wait states <sup>(1)(2)</sup> | I/O operation                           | Possible Flash<br>memory<br>operations        |

|-------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------|

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(3)</sup> | Conversion<br>time up to<br>1.2 Msps | 20 MHz                                                                                                  | 180 MHz with 8<br>wait states and<br>over-drive OFF                               | <ul> <li>No I/O compensation</li> </ul> | 8-bit erase and<br>program<br>operations only |

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

2. Thanks to the ART accelerator on ITCM interface and L1-cache on AXI interface, the number of wait states given here does not impact the execution speed from the Flash memory since the ART accelerator or L1-cache allows to achieve a performance equivalent to 0-wait state program execution.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V, with the use of an external power supply supervisor (refer to Section 2.15.1: Internal reset ON).