Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | H8S/2000                                                                     |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 13MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SCI, SmartCard                                             |

| Peripherals                | LCD, POR, PWM, WDT                                                           |

| Number of I/O              | 67                                                                           |

| Program Memory Size        | 256KB (256K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 16K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 10x10b; D/A 2x8b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-BFQFP                                                                    |

| Supplier Device Package    | 100-QFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2268fa13v |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item                                               | Page | Page Revision (See Manual for Details)                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|----------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 9.7.1 Port H Data 165                              |      | Description added                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Direction Register<br>(PHDDR)                      |      | PHDDR specifies input or output the port H pins using the individual bits. PHDDR cannot be read; if it is, an undefined value will be read.                                                                                                                                                              |  |  |  |  |  |

|                                                    |      | The value of this register when read is undefined after a bit<br>manipulation instruction is executed. To prevent undefined read<br>values, do not use bit manipulation instructions to write to this<br>register. For details, see section 2.9.4, Access Methods for<br>Registers with Write-Only Bits. |  |  |  |  |  |

| 9.8.1 Port J Data                                  | 170  | Description added                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Direction Register<br>(PJDDR)                      |      | PJDDR specifies input or output the port J pins using the individual bits. PJDDR cannot be read; if it is, an undefined value will be read.                                                                                                                                                              |  |  |  |  |  |

|                                                    |      | The value of this register when read is undefined after a bit<br>manipulation instruction is executed. To prevent undefined read<br>values, do not use bit manipulation instructions to write to this<br>register. For details, see section 2.9.4, Access Methods for<br>Registers with Write-Only Bits. |  |  |  |  |  |

| 9.9.1 Port K Data<br>Direction Register<br>(PKDDR) | 174  | Description added                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                                                    |      | PKDDR specifies input or output the port K pins using the individual bits. PKDDR cannot be read; if it is, an undefined value will be read.                                                                                                                                                              |  |  |  |  |  |

|                                                    |      | The value of this register when read is undefined after a bit<br>manipulation instruction is executed. To prevent undefined read<br>values, do not use bit manipulation instructions to write to this<br>register. For details, see section 2.9.4, Access Methods for<br>Registers with Write-Only Bits. |  |  |  |  |  |

| 9.10.1 Port L Data                                 | 176  | Description added                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Direction Register<br>(PLDDR)                      |      | PLDDR specifies input or output of the port L pins using the individual bits. PLDDR cannot be read; if it is, an undefined value will be read.                                                                                                                                                           |  |  |  |  |  |

|                                                    |      | The value of this register when read is undefined after a bit<br>manipulation instruction is executed. To prevent undefined read<br>values, do not use bit manipulation instructions to write to this<br>register. For details, see section 2.9.4, Access Methods for<br>Registers with Write-Only Bits. |  |  |  |  |  |

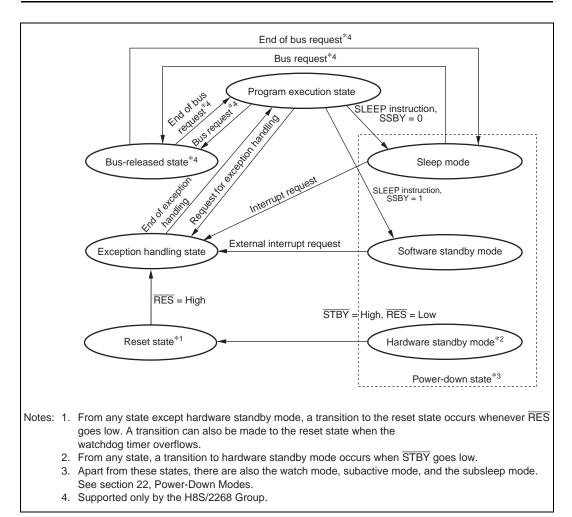

Figure 2.13 State Transitions

Section 2 CPU

|       | P17    | P16    | P15    | P14    | P13   | P12   | P11   | P10   |

|-------|--------|--------|--------|--------|-------|-------|-------|-------|

| I/O   | Output | Output | Output | Output | Input | Input | Input | Input |

| P1DDR | 1      | 1      | 1      | 1      | 0     | 0     | 0     | 0     |

|  | RAM0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

|--|------|---|---|---|---|---|---|---|---|

|--|------|---|---|---|---|---|---|---|---|

RAM locations are readable and writable, so there is no possibility of a problem if a bitmanipulation instruction is used to clear only bit 4 of RAM0. Read the value from RAM0 and then write it back to P1DDR.

| MOV.B | @RAM0, | ROL    |

|-------|--------|--------|

| MOV.B | ROL,   | @P1DDR |

|       | P17    | P16    | P15    | P14   | P13   | P12   | P11   | P10   |

|-------|--------|--------|--------|-------|-------|-------|-------|-------|

| I/O   | Output | Output | Output | Input | Input | Input | Input | Input |

| P1DDR | 1      | 1      | 1      | 0     | 0     | 0     | 0     | 0     |

|       |        |        |        |       |       |       |       |       |

| RAM0  | 1      | 1      | 1      | 0     | 0     | 0     | 0     | 0     |

Following this procedure in access to registers that include write-only bits makes the behavior of the program independent of the type of instruction.

| Table 10.14 TIORL | _0 (Channel 0) | (H8S/2268 | Group Only) |

|-------------------|----------------|-----------|-------------|

|-------------------|----------------|-----------|-------------|

|               |               |               |               | Descriptio             | n                                  |

|---------------|---------------|---------------|---------------|------------------------|------------------------------------|

| Bit 3<br>IOC3 | Bit 2<br>IOC2 | Bit 1<br>IOC1 | Bit 0<br>IOC0 | TGRC_0<br>Function     | TIOCC0 Pin Function                |

| 0             | 0             | 0             | 0             | Output                 | Output disabled                    |

|               |               |               | 1             | compare<br>register*   | Initial output is 0                |

|               |               |               |               | register               | 0 output at compare match          |

|               |               | 1             | 0             | _                      | Initial output is 0                |

|               |               |               |               |                        | 1 output at compare match          |

|               |               |               | 1             |                        | Initial output is 0                |

|               |               |               |               |                        | Toggle output at compare match     |

|               | 1             | 0             | 0             |                        | Output disabled                    |

|               |               |               | 1             |                        | Initial output is 1                |

|               |               |               |               |                        | 0 output at compare match          |

|               |               | 1             | 0             |                        | Initial output is 1                |

|               |               |               |               |                        | 1 output at compare match          |

|               |               |               | 1             |                        | Initial output is 1                |

|               |               |               |               |                        | Toggle output at compare match     |

| 1             | 0             | 0             | 0             | Input                  | Capture input source is TIOCC0 pin |

|               |               |               | _             | capture<br>– register* | Input capture at rising edge       |

|               |               |               | 1             |                        | Capture input source is TIOCC0 pin |

|               |               | _             |               |                        | Input capture at falling edge      |

|               |               | 1             | Х             |                        | Capture input source is TIOCC0 pin |

|               |               |               |               |                        | Input capture at both edges        |

|               | 1             | Х             | Х             |                        | Setting disabled                   |

Legend:

X: Don't care

Note: \* When the BFA bit in TMDR\_0 is set to 1 and TGRC\_0 is used as a buffer register, this setting is invalid and input capture/output compare is not generated.

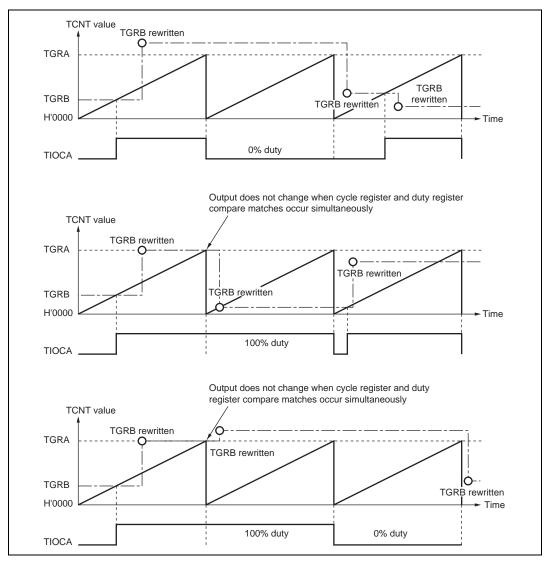

Figure 10.25 shows examples of PWM waveform output with 0% duty and 100% duty in PWM mode.

Figure 10.25 Example of PWM Mode Operation (3)

## RENESAS

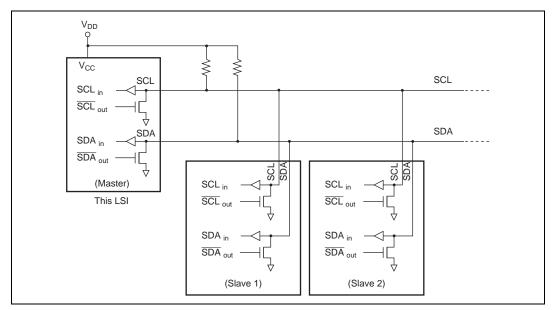

Figure 14.2 I<sup>2</sup>C Bus Interface Connections (Example: This LSI as Master)

# 14.2 Input/Output Pins

Table 14.1 shows the pin configuration for the I<sup>2</sup>C bus interface.

## Table 14.1 Pin Configuration

| Name                       | Abbreviation <sup>*1</sup> | I/O | Function                        |

|----------------------------|----------------------------|-----|---------------------------------|

| Serial clock               | SCL0                       | I/O | IIC_0 serial clock input/output |

| Serial data                | SDA0                       | I/O | IIC_0 serial data input/output  |

| Serial clock <sup>*2</sup> | SCL1                       | I/O | IIC_1 serial clock input/output |

| Serial data <sup>*2</sup>  | SDA1                       | I/O | IIC_1 serial data input/output  |

Notes: 1. In the text, the channel subscript is omitted, and only SCL and SDA are used.

2. Supported only by the H8S/2268 Group.

# 14.3.5 Serial Control Register X (SCRX)

SCRX controls the IIC operating modes.

|        |          | Initial |     |                                                                                                           |

|--------|----------|---------|-----|-----------------------------------------------------------------------------------------------------------|

| Bit    | Bit Name | Value   | R/W | Description                                                                                               |

| 7      | -        | 0       | R/W | Reserved                                                                                                  |

|        |          |         |     | The initial value should not be changed.                                                                  |

| 6      | IICX1*   | 0       | R/W | I <sup>2</sup> C Transfer Rate Select 1 and 0                                                             |

| 5      | IICX0    | 0       | R/W | Selects the transfer rate in master mode, together with bits CKS2 to CKS0 in ICMR. Refer to table 14.3.   |

|        |          |         |     | IICX1 controls IIC_1 and IICX0 controls IIC_0.                                                            |

|        |          |         |     | Note: * In the H8S/2264 Group, this bit is reserved.                                                      |

|        |          |         |     | The initial value should not be changed.                                                                  |

| 4      | IICE     | 0       | R/W | I <sup>2</sup> C Master Enable                                                                            |

|        |          |         |     | Controls CPU access to the IIC data register and control registers (ICCR, ICSR, ICDR/SARX, and ICMR/SAR). |

|        |          |         |     | <ol> <li>CPU access to the IIC data register and control<br/>registers is disabled.</li> </ol>            |

|        |          |         |     | <ol> <li>CPU access to the IIC data register and control<br/>registers is enabled.</li> </ol>             |

| 3      | FLSHE    | 0       | R/W | For details on this bit, refer to section 20.5.7, Serial Control Register X (SCRX).                       |

| 2 to 0 | -        | All 0   | R/W | Reserved                                                                                                  |

|        |          |         |     | The initial value should not be changed.                                                                  |

| Figure 22.3  | Software Standby Mode Application Example                                |

|--------------|--------------------------------------------------------------------------|

| Figure 22.4  | Hardware Standby Mode Timing                                             |

|              |                                                                          |

|              | Power Supply Circuit                                                     |

| Figure 23.1  | Power Supply Connections When Internal Power Supply Step-Down Circuit Is |

|              | Used                                                                     |

| Section 25   | Electrical Characteristics                                               |

| Figure 25.1  | Power Supply Voltage and Operating Ranges (1)                            |

| Figure 25.1  | Power Supply Voltage and Operating Ranges (2)                            |

| Figure 25.2  | Output Load Circuit                                                      |

| Figure 25.3  | Output Load Circuit                                                      |

| Figure 25.4  | Oscillator Settling Timing                                               |

| Figure 25.5  | Reset Input Timing                                                       |

| Figure 25.6  | Interrupt Input Timing                                                   |

| Figure 25.7  | TPU Clock Input Timing                                                   |

| Figure 25.8  | 8-Bit Timer Clock Input Timing                                           |

| Figure 25.9  | SCK Clock Input Timing                                                   |

| Figure 25.10 | SCI Input/Output Timing (Clock Synchronous Mode)                         |

| Figure 25.11 | I <sup>2</sup> C Bus Interface Input/Output Timing (Option)              |

| Figure 25.12 | TONED Load Circuit (Supported Only by the H8S/2268 Group)641             |

|              |                                                                          |

| Appendix     | C Package Dimensions650                                                  |

| Figure C.1   | TFP-100B and TFP-100BV Package Dimensions (H8S/2268 Group Only)650       |

| Figure C.2   | TFP-100G and TFP-100GV Package Dimensions                                |

| Figure C.3   | FP-100B and FP-100BV Package Dimensions                                  |

Rev. 5.00 Sep. 01, 2009 Page xlv of I REJ09B0071-0500