Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                     |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SCI, SmartCard                                             |

| Peripherals                | LCD, POR, PWM, WDT                                                           |

| Number of I/O              | 67                                                                           |

| Program Memory Size        | 256KB (256K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | ·                                                                            |

| RAM Size                   | 16K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                    |

| Data Converters            | A/D 10x10b; D/A 2x8b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-TQFP                                                                     |

| Supplier Device Package    | 100-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2268tf20v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item                                                          | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                         |                                                                    |                          |                                             |                   |                                 |                   |                                                             |  |

|---------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------|---------------------------------------------|-------------------|---------------------------------|-------------------|-------------------------------------------------------------|--|

| 25.2.2 DC<br>Characteristics                                  | 602  | Table am                                                                                                                                                                                                                                                                                                                                                  | ended                                                              |                          |                                             |                   |                                 |                   |                                                             |  |

| Table 25.2 DC                                                 |      | Item<br>Input high                                                                                                                                                                                                                                                                                                                                        | RES, STBY,NMI,                                                     | Symbol<br>V <sub>⊪</sub> | Min.<br>V <sub>cc</sub> × 0.9               | Тур               | •. Max.<br>V <sub>cc</sub> +0.3 | Unit<br>3 V       | Test Conditions                                             |  |

| Characteristics (2)                                           |      | voltage                                                                                                                                                                                                                                                                                                                                                   | FWE, MD2, MD1<br>EXTAL, Ports 1, 3,<br>7, F, J to N, PH0 to<br>PH3 | -                        | $V_{cc} 	imes 0.8$                          |                   | V <sub>cc</sub> +0.3            | 3 V               |                                                             |  |

|                                                               |      |                                                                                                                                                                                                                                                                                                                                                           | Ports 4 <sup>*4</sup> , 9, PH7                                     |                          | $V_{cc} 	imes 0.8$                          |                   | V <sub>cc</sub> + 0.3           | 3 <sup>*4</sup> V |                                                             |  |

|                                                               | 603  | Note adde                                                                                                                                                                                                                                                                                                                                                 | ed                                                                 |                          |                                             |                   |                                 |                   |                                                             |  |

|                                                               |      | Notes: 4.                                                                                                                                                                                                                                                                                                                                                 | When Vcc<br>P41 is Vcc                                             |                          |                                             | maxir             | num va                          | alue fo           | or P40 and                                                  |  |

| 25.2.4 A/D                                                    | 615  | Table con                                                                                                                                                                                                                                                                                                                                                 | dition amen                                                        | ded                      |                                             |                   |                                 |                   |                                                             |  |

| Conversion<br>Characteristics<br>Table 25.9 A/D<br>Conversion |      | V to 5.5 V<br>MHz, T <sub>a</sub> =                                                                                                                                                                                                                                                                                                                       | ′*, V <sub>ref</sub> = 2.7                                         | V to A<br>75°C (         | V <sub>cc</sub> , V <sub>s</sub><br>(regula | <sub>ss</sub> = A | $V_{ss} = 0$                    | ) V,              | , $AV_{cc} = 2.7$<br>= 2 to 13.5<br>$T_a = -40^{\circ}C$ to |  |

| Characteristics                                               |      | Condition C (F-ZTAT version): $V_{cc} = 4.0 \text{ V}$ to 5.5 V <sup>*</sup> , $AV_{cc} = 4.0 \text{ V}$ to 5.5 V <sup>*</sup> , $V_{rel} = 4.0 \text{ V}$ to $AV_{cc}$ , $V_{ss} = AV_{ss} = 0 \text{ V}$ , $\phi = 10$ to 20.5 MHz, $T_a = -20^{\circ}$ C to +75°C (regular specifications), $T_a = -40^{\circ}$ C to +85°C (wide-range specifications) |                                                                    |                          |                                             |                   |                                 |                   |                                                             |  |

|                                                               |      | Note added                                                                                                                                                                                                                                                                                                                                                |                                                                    |                          |                                             |                   |                                 |                   |                                                             |  |

|                                                               |      | Note: * AN0 and AN1 can be used only when Vcc = AVcc.                                                                                                                                                                                                                                                                                                     |                                                                    |                          |                                             |                   |                                 |                   |                                                             |  |

| 25.3.2 DC                                                     | 622  | Table amended                                                                                                                                                                                                                                                                                                                                             |                                                                    |                          |                                             |                   |                                 |                   |                                                             |  |

| Characteristics                                               |      | Item                                                                                                                                                                                                                                                                                                                                                      |                                                                    | Symbol                   |                                             | Тур.              |                                 |                   | est Conditions                                              |  |

| Table 25.15 DC<br>Characteristics (1)                         |      | Input high<br>voltage                                                                                                                                                                                                                                                                                                                                     | RES, STBY, NMI,<br>FWE, MD2, MD1                                   | V <sub>IH</sub>          | V <sub>cc</sub> 0.9                         |                   | V <sub>cc</sub> + 0.3           | V                 |                                                             |  |

| Unaracteristics (1)                                           |      |                                                                                                                                                                                                                                                                                                                                                           | EXTAL, Ports 1, 3,<br>7, F, H, J to L                              | _                        | V <sub>cc</sub> 0.8                         |                   | V <sub>cc</sub> + 0.3           | V                 |                                                             |  |

|                                                               |      |                                                                                                                                                                                                                                                                                                                                                           | Ports 4 <sup>*4</sup> , 9                                          |                          | V <sub>cc</sub> 0.8                         |                   | AV <sub>cc</sub> +0.3*          | 4 V               |                                                             |  |

|                                                               | 623  | Note adde                                                                                                                                                                                                                                                                                                                                                 | ed                                                                 |                          |                                             |                   |                                 |                   |                                                             |  |

|                                                               |      | Notes: 4.                                                                                                                                                                                                                                                                                                                                                 | When Vcc<br>P41 is Vcc                                             |                          |                                             | naxir             | num va                          | alue fo           | or P40 and                                                  |  |

| 25.3.2 DC<br>Characteristics                                  | 624  | Table am                                                                                                                                                                                                                                                                                                                                                  | ended                                                              | Symbol                   | Min.                                        | Тур.              | Max.                            | Unit T            | est Conditions                                              |  |

| Table 25.15 DC                                                |      | Input high<br>voltage                                                                                                                                                                                                                                                                                                                                     | RES, STBY, NMI,<br>FWE, MD2, MD1                                   | V <sub>IH</sub>          | V <sub>cc</sub> 0.9                         |                   | V <sub>cc</sub> + 0.3           | V                 |                                                             |  |

| Characteristics (2)                                           |      | vollage                                                                                                                                                                                                                                                                                                                                                   | EXTAL, Ports 1, 3,                                                 |                          | V <sub>cc</sub> 0.8                         |                   | V <sub>cc</sub> + 0.3           | V                 |                                                             |  |

|                                                               |      |                                                                                                                                                                                                                                                                                                                                                           | 7, F, H, J to L<br>Ports 4 <sup>*4</sup> , 9                       |                          | V <sub>cc</sub> 0.8                         |                   | $AV_{cc} + 0.3^*$               | 4 V               |                                                             |  |

|                                                               | 625  | Note adde                                                                                                                                                                                                                                                                                                                                                 | ed                                                                 |                          |                                             |                   |                                 |                   |                                                             |  |

|                                                               | 320  |                                                                                                                                                                                                                                                                                                                                                           | When Vcc<br>P41 is Vcc                                             |                          |                                             | maxir             | num va                          | alue fo           | or P40 and                                                  |  |

Rev. 5.00 Sep. 01, 2009 Page xviii of I REJ09B0071-0500

# RENESAS

|       | 13.6.1  | Clock                                                                    | 355   |

|-------|---------|--------------------------------------------------------------------------|-------|

|       | 13.6.2  | SCI Initialization (Clocked Synchronous Mode)                            | 355   |

|       | 13.6.3  | Serial Data Transmission (Clocked Synchronous Mode)                      | 356   |

|       | 13.6.4  | Serial Data Reception (Clocked Synchronous Mode)                         | 359   |

|       | 13.6.5  | Simultaneous Serial Data Transmission and Reception (Clocked Synchronous | S     |

|       |         | Mode)                                                                    | 361   |

| 13.7  | Operati | ion in Smart Card Interface                                              | 363   |

|       | 13.7.1  | Pin Connection Example                                                   | 363   |

|       |         | Data Format (Except for Block Transfer Mode)                             |       |

|       |         | Block Transfer Mode                                                      |       |

|       | 13.7.4  | Receive Data Sampling Timing and Reception Margin                        | 366   |

|       | 13.7.5  | Initialization                                                           | 367   |

|       | 13.7.6  | Serial Data Transmission (Except for Block Transfer Mode)                | 367   |

|       | 13.7.7  | Serial Data Reception (Except for Block Transfer Mode)                   | 371   |

|       | 13.7.8  | Clock Output Control                                                     | 372   |

| 13.8  | Interru | pt Sources                                                               | 374   |

|       | 13.8.1  | Interrupts in Normal Serial Communication Interface Mode                 | 374   |

|       | 13.8.2  | Interrupts in Smart Card Interface Mode                                  | 375   |

| 13.9  | Usage 1 | Notes                                                                    | 376   |

|       | 13.9.1  | Module Stop Mode Setting                                                 | 376   |

|       | 13.9.2  | Break Detection and Processing (Asynchronous Mode Only)                  | 376   |

|       | 13.9.3  | Mark State and Break Detection (Asynchronous Mode Only)                  | 376   |

|       | 13.9.4  | Receive Error Flags and Transmit Operations (Clocked Synchronous         |       |

|       |         | Mode Only)                                                               | 377   |

|       | 13.9.5  | Restrictions on Use of DTC (H8S/2268 Group Only)                         | 377   |

|       | 13.9.6  | Operation in Case of Mode Transition                                     | 378   |

|       | 13.9.7  | Switching from SCK Pin Function to Port Pin Function:                    | 381   |

|       | 13.9.8  | Assignment and Selection of Registers                                    | 382   |

| ~ .   |         |                                                                          |       |

| Secti | on 14   | I <sup>2</sup> C Bus Interface (IIC)                                     | • • • |

|       |         | (Supported as an Option by H8S/2264 Group)                               |       |

| 14.1  |         | 28                                                                       |       |

| 14.2  | 1       | Dutput Pins                                                              |       |

| 14.3  |         | r Descriptions                                                           |       |

|       | 14.3.1  | I <sup>2</sup> C Bus Data Register (ICDR)                                |       |

|       | 14.3.2  | Slave Address Register (SAR)                                             |       |

|       | 14.3.3  | Second Slave Address Register (SARX)                                     |       |

|       | 14.3.4  | e v ,                                                                    |       |

|       |         | Serial Control Register X (SCRX)                                         |       |

|       |         | I <sup>2</sup> C Bus Control Register (ICCR)                             |       |

|       | 14.3.7  | I <sup>2</sup> C Bus Status Register (ICSR)                              | 401   |

|       |         |                                                                          |       |

Rev. 5.00 Sep. 01, 2009 Page xxx of I REJ09B0071-0500

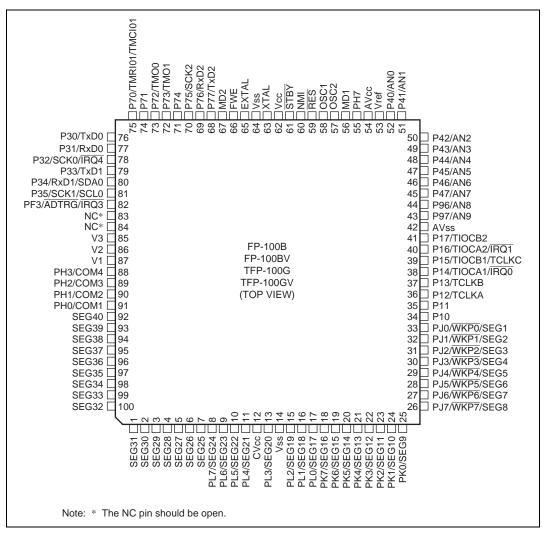

Figure 1.4 Pin Arrangement of H8S/2264 Group

## RENESAS

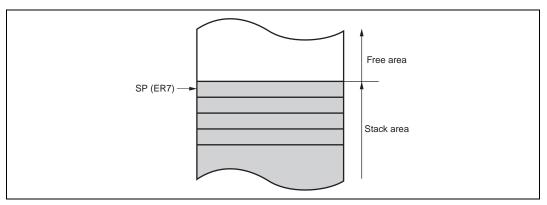

Figure 2.8 Stack Status

#### 2.4.2 Program Counter (PC)

This 24-bit counter indicates the address of the next instruction the CPU will execute. The length of all CPU instructions is 2 bytes (one word), so the least significant PC bit is ignored. (When an instruction is fetched, the least significant PC bit is regarded as 0.)

#### 2.4.3 Extended Control Register (EXR) (H8S/2268 Group Only)

EXR is an 8-bit register that manipulates the LDC, STC, ANDC, ORC, and XORC instructions. When these instructions except for the STC instruction is executed, all interrupts including NMI will be masked for three states after execution is completed.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                 |  |  |  |

|--------|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7      | Т        | 0                | R/W | Trace Bit                                                                                                                                                                   |  |  |  |

|        |          |                  |     | When this bit is set to 1, a trace exception is generated<br>each time an instruction is executed. When this bit is<br>cleared to 0, instructions are executed in sequence. |  |  |  |

| 6 to 3 |          | 1                |     | Reserved                                                                                                                                                                    |  |  |  |

|        |          |                  |     | These bits are always read as 1.                                                                                                                                            |  |  |  |

| 2      | 12       | 1                | R/W | These bits designate the interrupt mask level (0 to 7). For                                                                                                                 |  |  |  |

| 1      | 11       | 1                | R/W | details, refer to section 5, Interrupt Controller.                                                                                                                          |  |  |  |

| 0      | 10       | 1                | R/W |                                                                                                                                                                             |  |  |  |

# 2.5 Data Formats

The H8S/2000 CPU can process 1-bit, 4-bit (BCD), 8-bit (byte), 16-bit (word), and 32-bit (longword) data. Bit-manipulation instructions operate on 1-bit data by accessing bit n (n = 0, 1, 2, ..., 7) of byte operand data. The DAA and DAS decimal-adjust instructions treat byte data as two digits of 4-bit BCD data.

#### 2.5.1 General Register Data Formats

| Data Type<br>1-bit data | Register Number | Data Format<br>7 0<br>7 6 5 4 3 2 1 0 Don't care                                                                 |

|-------------------------|-----------------|------------------------------------------------------------------------------------------------------------------|

| 1-bit data              | RnL             | 7         0           Don't care         7         6         5         4         3         2         1         0 |

| 4-bit BCD o             | lata RnH        | 7     4     3     0       Upper     Lower     Don't care                                                         |

| 4-bit BCD c             | lata RnL        | 7     4     3     0       Don't care     Upper     Lower                                                         |

| Byte data               | RnH             | 7 0<br>Don't care<br>MSB LSB                                                                                     |

| Byte data               | RnL             | 7     0       Don't care     MSB     LSB                                                                         |

Figure 2.9 shows the data formats in general registers.

Figure 2.9 General Register Data Formats (1)

| Exception Source                | Vector Number | Vector Address Advanced Mode <sup>*1</sup> |

|---------------------------------|---------------|--------------------------------------------|

| Internal interrupt*2            | 24            | H'0060 to H'0063                           |

|                                 | 107           | H'01AC to H'01AF                           |

| External interrupt WKP0 to WKP7 | 108           | H'01B0 to H'01B3                           |

| Internal interrupt              | 120<br>       | H'01E0 to H'01E3                           |

|                                 | 123           | H'01EC to H'01EF                           |

Notes: 1. Lower 16 bits of the address.

- 2. For details of internal interrupt vectors, see section 5.4.3, Interrupt Exception Handling Vector Table.

- 3. For details on direct transitions, see section 22.10, Direct Transitions.

- 4. Supported only by the H8S/2268 Group.

# 4.3 Reset

A reset has the highest exception priority.

When the  $\overline{\text{RES}}$  pin goes low, all processing halts and this LSI enters the reset. A reset initializes the internal state of the CPU and the registers of on-chip peripheral modules. The interrupt control mode is 0 immediately after reset.

When the  $\overline{\text{RES}}$  pin goes high from the low state, this LSI starts reset exception handling.

The chip can also be reset by overflow of the watchdog timer. For details see section 12, Watchdog Timer (WDT).

#### 4.3.1 Reset Exception Handling

When the  $\overline{\text{RES}}$  pin goes low, this LSI enters the reset. To ensure that this LSI is reset, hold the  $\overline{\text{RES}}$  pin low for at least 20 ms at power-up. To reset the chip during operation, hold the  $\overline{\text{RES}}$  pin low for at least 20 states. When the  $\overline{\text{RES}}$  pin goes high after being held low for the necessary time, this LSI starts reset exception handling as follows.

- 1. The internal state of the CPU and the registers of the on-chip peripheral modules are initialized, the T bit in EXR<sup>\*</sup> is cleared to 0, and the I bits in EXR<sup>\*</sup> and CCR is set to 1.

- 2. The reset exception handling vector address is read and transferred to the PC, and program execution starts from the address indicated by the PC.

Note: \* Supported only by the H8S/2268 Group.

the corresponding DDR to 0; and use the pin as an I/O pin for another function. IRQnF interrupt request flag is set to 1 when the setting condition is satisfied, regardless of IER settings. Accordingly, refer to only necessary flags.

### 5.4.2 Internal Interrupts

For each on-chip peripheral module, there are flags that indicate the interrupt request status, and enable bits that select enabling or disabling of these interrupts. If both of these are set to 1 for a particular interrupt source, an interrupt request is issued to the interrupt controller.

## 5.4.3 Interrupt Exception Handling Vector Table

Table 5.2 shows interrupt exception handling sources, vector addresses, and interrupt priorities. For default priorities, the lower the vector number, the higher the priority.

Priorities among modules can be set by means of the IPR. (H8S/2268 Group only)

Modules set at the same priority will conform to their default priorities. Priorities within a module are fixed.

| Port   | Description                               | Port and<br>Other Functions Name | Input/Output and<br>Output Type |

|--------|-------------------------------------------|----------------------------------|---------------------------------|

| Port L | General I/O port also                     | PL7/SEG24                        |                                 |

|        | functioning as LCD<br>segment output pins | PL6/SEG23                        |                                 |

|        | segment output pins                       | PL5/SEG22                        |                                 |

|        |                                           | PL4/SEG21                        |                                 |

|        |                                           | PL3/SEG20                        |                                 |

|        |                                           | PL2/SEG19                        |                                 |

|        |                                           | PL1/SEG18                        |                                 |

|        |                                           | PL0/SEG17                        |                                 |

## 9.1 Port 1

Port 1 is an 8-bit I/O port and has the following registers.

- Port 1 data direction register (P1DDR)

- Port 1 data register (P1DR)

- Port 1 register (PORT1)

#### 9.1.1 Port 1 Data Direction Register (P1DDR)

P1DDR specifies input or output of the port 1 pins using the individual bits. P1DDR cannot be read; if it is, an undefined value will be read.

The value of this register when read is undefined after a bit manipulation instruction is executed. To prevent undefined read values, do not use bit manipulation instructions to write to this register. For details, see section 2.9.4, Access Methods for Registers with Write-Only Bits.

| Port Name | Pin Handling Example                                                      |

|-----------|---------------------------------------------------------------------------|

| Port 1    | Connect each pin to Vcc (pull-up) or to Vss (pull-down) via a resistor.   |

| Port 3    | _                                                                         |

| Port 4    | Connect each pin to AVcc (pull-up) or to AVss (pull-down) via a resistor. |

| Port 7    | Connect each pin to Vcc (pull-up) or to Vss (pull-down) via a resistor.   |

| Port 9    | Connect each pin to AVcc (pull-up) or to AVss (pull-down) via a resistor. |

| Port F    | Connect each pin to Vcc (pull-up) or to Vss (pull-down) via a resistor.   |

| Port H    | * Ports M and N apply to the H8S/2268 Group only.                         |

| Port J    | _                                                                         |

| Port K    | _                                                                         |

| Port L    | _                                                                         |

| Port M*   | —                                                                         |

| Port N*   | —                                                                         |

#### Table 9.3 Examples of Ways to Handle Unused Input Pins

For pins set as LCD SEG pins (see 17.3.1, LED Port Control Register (LPCR)), add extra capacitance as appropriate to accommodate the LCD drive power supply capacity and the LCD used.

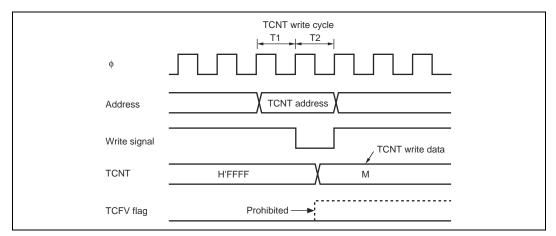

#### 10.10.12 Contention between TCNT Write and Overflow/Underflow

In the H8S/2268 Group, if there is an up-count or down-count in the T2 state of a TCNT write cycle and overflow/underflow occurs, the TCNT write takes precedence and the TCFV/TCFU flag in TSR is not set.

In the H8S/2264 Group, if there is an up-count in the T2 state of a TCNT write cycle and overflow occurs, the TCNT write takes precedence and the TCFV flag in TSR is not set.

Figure 10.54 shows the operation timing when there is contention between TCNT write and overflow.

Figure 10.54 Contention between TCNT Write and Overflow

#### 10.10.13 Multiplexing of I/O Pins

In the H8S/2268 Group, the TCLKA input pin is multiplexed with the TIOCC0 I/O pin, the TCLKB input pin with the TIOCD0 I/O pin, the TCLKC input pin with the TIOCD1 I/O pin, and the TCLKD input pin with the TIOCB2 I/O pin. In the H8S/2264 Group, the TCLKC input pin is multiplexed with the TIOCB1 I/O pin. When an external clock is input, compare match output should not be performed from a multiplexed pin.

## 10.10.14 Interrupts in Module Stop Mode

If module stop mode is entered when an interrupt has been requested, it will not be possible to clear the CPU interrupt source, or the DTC activation source (the H8S/2268 Group only). Interrupts should therefore be disabled before entering module stop mode.

TCORB is continually compared with the value in TCNT. When a match is detected, the corresponding compare-match flag B (CMFB) in TCSR is set. Note, however, that comparison is disabled during the T2 state of a TCORB write cycle.

The timer output from the TMO pin can be freely controlled by the compare-match signal B and the settings of output select bits OS1 and OS0 in TCSR.

The initial value of TCORB is H'FF.

#### **11.3.4** Timer Control Register (TCR)

TCR selects the TCNT clock source and the time at which TCNT is cleared, and controls interrupt requests.

| Bit | Bit Name | Initial<br>Value | R/W  | Description                                                                                                            |

|-----|----------|------------------|------|------------------------------------------------------------------------------------------------------------------------|

| 7   | CMIEB    | 0                | R/W  | Compare-Match Interrupt Enable B                                                                                       |

| 7   | CIMIED   | 0                | R/VV | Selects whether the CMFB interrupt request (CMIB) is<br>enabled or disabled when the CMFB flag in TCSR is set<br>to 1. |

|     |          |                  |      | 0: CMFB interrupt request (CMIB) is disabled                                                                           |

|     |          |                  |      | 1: CMFB interrupt request (CMIB) is enabled                                                                            |

| 6   | CMIEA    | 0                | R/W  | Compare-Match Interrupt Enable A                                                                                       |

|     |          |                  |      | Selects whether the CMFA interrupt request (CMIA) is<br>enabled or disabled when the CMFA flag in TCSR is set<br>to 1. |

|     |          |                  |      | 0: CMFA interrupt request (CMIA) is disabled                                                                           |

|     |          |                  |      | 1: CMFA interrupt request (CMIA) is enabled                                                                            |

| 5   | OVIE     | 0                | R/W  | Timer Overflow Interrupt Enable                                                                                        |

|     |          |                  |      | Selects whether the OVF interrupt request (OVI) is enabled or disabled when the OVF flag in TCSR is set to 1.          |

|     |          |                  |      | 0: OVF interrupt request (OVI) is disabled                                                                             |

|     |          |                  |      | 1: OVF interrupt request (OVI) is enabled                                                                              |

| 4   | CCLR1    | 0                | R/W  | Counter Clear 1 and 0                                                                                                  |

| 3   | CCLR0    | 0                | R/W  | These bits select the method by which TCNT is cleared                                                                  |

|     |          |                  |      | 00: Clearing is disabled                                                                                               |

|     |          |                  |      | 01: Cleared on compare-match A                                                                                         |

|     |          |                  |      | 10: Cleared on compare-match B                                                                                         |

|     |          |                  |      | 11: Cleared on rising edge of external reset input                                                                     |

|     |          |                  |      |                                                                                                                        |

|          | Operating Frequency $\phi$ (MHz) |     |           |   |      |           |   |     |           |  |

|----------|----------------------------------|-----|-----------|---|------|-----------|---|-----|-----------|--|

| Bit Rate |                                  | 18  |           |   | 19.0 | 6608      |   | 20  |           |  |

| (bps)    | n                                | Ν   | Error (%) | n | Ν    | Error (%) | n | Ν   | Error (%) |  |

| 110      | 3                                | 79  | -0.12     | 3 | 86   | 0.31      | 3 | 88  | -0.25     |  |

| 150      | 2                                | 233 | 0.16      | 2 | 255  | 0.00      | 2 | 64  | 0.16      |  |

| 300      | 2                                | 116 | 0.16      | 2 | 127  | 0.00      | 2 | 129 | 0.16      |  |

| 600      | 1                                | 233 | 0.16      | 1 | 255  | 0.00      | 1 | 64  | 0.16      |  |

| 1200     | 1                                | 116 | 0.16      | 1 | 127  | 0.00      | 1 | 129 | 0.16      |  |

| 2400     | 0                                | 233 | 0.16      | 0 | 255  | 0.00      | 0 | 64  | 0.16      |  |

| 4800     | 0                                | 116 | 0.16      | 0 | 127  | 0.00      | 0 | 129 | 0.16      |  |

| 9600     | 0                                | 58  | -0.69     | 0 | 63   | 0.00      | 0 | 64  | 0.16      |  |

| 19200    | 0                                | 28  | 1.02      | 0 | 31   | 0.00      | 0 | 32  | -1.36     |  |

| 31250    | 0                                | 17  | 0.00      | 0 | 19   | -1.70     | 0 | 19  | 0.00      |  |

| 38400    | 0                                | 14  | -2.34     | 0 | 15   | 0.00      | 0 | 15  | 1.73      |  |

Table 13.3

BRR Settings for Various Bit Rates (Asynchronous Mode) (4)

Table 13.4

Maximum Bit Rate for Each Frequency (Asynchronous Mode)

| φ (MHz)  | Maximum Bit<br>Rate (kbps) | n | N | φ (MHz) | Maximum Bit<br>Rate (kbps) | n | N |

|----------|----------------------------|---|---|---------|----------------------------|---|---|

| 2        | 62.5                       | 0 | 0 | 9.8304  | 307.2                      | 0 | 0 |

| 2.097152 | 65.536                     | 0 | 0 | 10      | 312.5                      | 0 | 0 |

| 2.4576   | 76.8                       | 0 | 0 | 12      | 375.0                      | 0 | 0 |

| 3        | 93.75                      | 0 | 0 | 12.288  | 384.0                      | 0 | 0 |

| 3.6864   | 115.2                      | 0 | 0 | 14      | 437.5                      | 0 | 0 |

| 4        | 125.0                      | 0 | 0 | 14.7456 | 460.8                      | 0 | 0 |

| 4.9152   | 153.6                      | 0 | 0 | 16      | 500.0                      | 0 | 0 |

| 5        | 156.25                     | 0 | 0 | 17.2032 | 537.6                      | 0 | 0 |

| 6        | 187.5                      | 0 | 0 | 18      | 562.5                      | 0 | 0 |

| 6.144    | 192.0                      | 0 | 0 | 19.6608 | 614.4                      | 0 | 0 |

| 7.3728   | 230.4                      | 0 | 0 | 20      | 625.0                      | 0 | 0 |

| 8        | 250.0                      | 0 | 0 |         |                            |   |   |

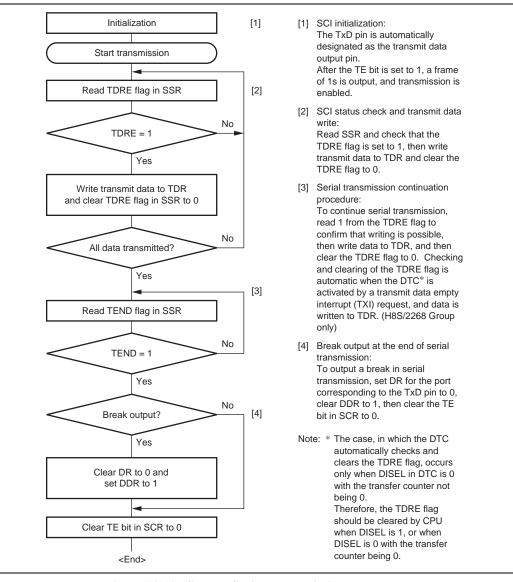

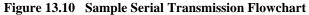

Figure 13.10 shows a sample flowchart for data transmission.

#### 14.4.7 IRIC Setting Timing and SCL Control

The interrupt request flag (IRIC) is set at different times depending on the WAIT bit in ICMR, the FS bit in SAR, and the FSX bit in SARX. If the TDRE or RDRF internal flag is set to 1, SCL is automatically held low after one frame has been transferred; this timing is synchronized with the internal clock. Figure 14.19 shows the IRIC set timing and SCL control.

Figure 14.19 IRIC Setting Timing and SCL Control

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                           |  |  |  |  |

|-----|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 4   | SUPS     | 0                | R/W | (H8S/2268 Group)                                                                                                                                                                                                      |  |  |  |  |

|     |          |                  |     | Drive Power Select                                                                                                                                                                                                    |  |  |  |  |

|     |          |                  |     | Triple Step-up Voltage Circuit Control                                                                                                                                                                                |  |  |  |  |

|     |          |                  |     | The triple step-up voltage circuit stops operation when Vcc is selected as drive power. The triple step-up voltage circuit starts operation when LCD input reference voltage $(V_{LCD3})$ is selected as drive power. |  |  |  |  |

|     |          |                  |     | 0: Drive power is Vcc, triple step-up voltage circuit halts                                                                                                                                                           |  |  |  |  |

|     |          |                  |     | 1: Drive power is triple step-up voltage of the LCD input reference voltage (V <sub>LCD3</sub> ), triple step-up voltage circuit operates                                                                             |  |  |  |  |

|     |          |                  |     | (H8S/2264 Group)                                                                                                                                                                                                      |  |  |  |  |

|     |          |                  |     | Reserved                                                                                                                                                                                                              |  |  |  |  |

|     |          |                  |     | 0 should be written to this bit.                                                                                                                                                                                      |  |  |  |  |

| 3   | CDS3     | 0                | R/W | Selection of Duty Ratio for Charge/Discharge Pulse                                                                                                                                                                    |  |  |  |  |

| 2   | CDS2     | 0                | R/W | Duty ratio is selected during the power supply divider                                                                                                                                                                |  |  |  |  |

| 1   | CDS1     | 0                | R/W | resistance is connected to power supply circuit. When the duty ratio of 0 is selected, the power supply divider                                                                                                       |  |  |  |  |

| 0   | CDS0     | 0                | R/W | resistance is fixed to the state that the resistance is<br>separated from the power supply circuit. Therefore,<br>supply the power to pins $V_1$ , $V_2$ , and $V_3$ from the external<br>circuit.                    |  |  |  |  |

|     |          |                  |     | The charge/discharge pulses have the waveform shown in figure 17.2. The duty ratio is represented by $T_c/T_w$ .                                                                                                      |  |  |  |  |

|     |          |                  |     | 0000: duty ratio = 1 (stack at high)                                                                                                                                                                                  |  |  |  |  |

|     |          |                  |     | 0001: duty ratio = 1/8                                                                                                                                                                                                |  |  |  |  |

|     |          |                  |     | 0010: duty ratio = 2/8                                                                                                                                                                                                |  |  |  |  |

|     |          |                  |     | 0011: duty ratio = 3/8                                                                                                                                                                                                |  |  |  |  |

|     |          |                  |     | 0100: duty ratio = 4/8                                                                                                                                                                                                |  |  |  |  |

|     |          |                  |     | 0101: duty ratio = 5/8                                                                                                                                                                                                |  |  |  |  |

|     |          |                  |     | 0110: duty ratio = 6/8                                                                                                                                                                                                |  |  |  |  |

|     |          |                  |     | 0111: duty ratio = 0 (stack at low)                                                                                                                                                                                   |  |  |  |  |

|     |          |                  |     | 10XX: duty ratio = 1/16                                                                                                                                                                                               |  |  |  |  |

|     |          |                  |     | 11XX: duty ratio = 1/32                                                                                                                                                                                               |  |  |  |  |

Legend: X: Don't care

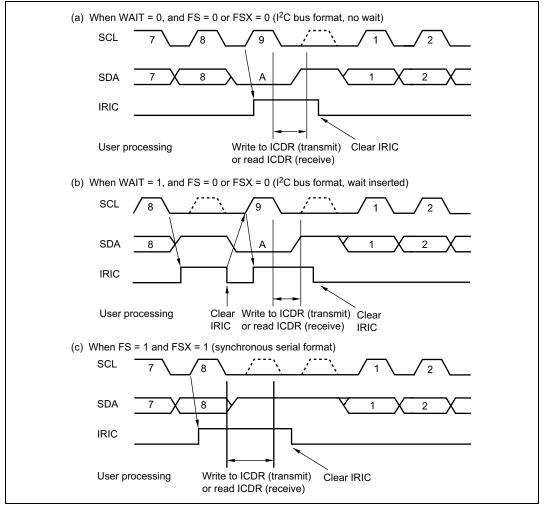

The differences between boot mode and user program mode are shown in table 20.1.

Figure 20.3 shows the operation flow for boot mode and figure 20.4 shows that for user program mode.

#### Figure 20.2 Flash Memory State Transitions

#### Table 20.1 Differences between Boot Mode and User Program Mode

| Boot Mode              | User Program Mode                                       |

|------------------------|---------------------------------------------------------|

| Yes                    | Yes                                                     |

| No                     | Yes                                                     |

| Program/program-verify | Program/program-verify/erase/<br>erase-verify/emulation |

|                        | Yes<br>No                                               |

Note: \* To be provided by the user, in accordance with the recommended algorithm.

# Section 24 List of Registers

This section gives information on the on-chip I/O registers and is configured as described below.

- 1. Register Addresses (by functional module, in address order)

- Descriptions by functional module, in ascending order of addresses

- When registers consist of 16 bits, the addresses of the MSBs are given.

- Data bus width is given.

- The number of access states are given.

- 2. Register Bits

- Bit configurations of the registers are described in the same order as the Register Addresses (by functional module, in ascending order of addresses).

- Reserved bits are indicated by in the bit name.

- When registers consist of 16 or 32 bits, bits are described from the MSB side.

- 3. Register States in Each Operating Mode

- Register states are described in the same order as the Register Addresses (by functional module, in ascending order of addresses).

- The register states described are for the basic operating modes. If there is a specific reset for an on-chip module, refer to the section on that on-chip module.

#### Table 25.2DC Characteristics (4)

Condition C (F-ZTAT version):  $V_{cc} = 4.0 \text{ V}$  to 5.5 V,  $AV_{cc} = 4.0 \text{ V}$  to 5.5 V,  $V_{ref} = 4.0 \text{ V}$  to  $AV_{cc}$ ,  $V_{ss} = AV_{ss} = 0 \text{ V}$ ,  $T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$  (regular specifications),  $T_a = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ (wide-range specifications)<sup>\*1</sup>

| Item                                 |                                                  | Symbol          | Min. | Тур.                          | Max.                          | Unit | Test Conditions                                                                                     |

|--------------------------------------|--------------------------------------------------|-----------------|------|-------------------------------|-------------------------------|------|-----------------------------------------------------------------------------------------------------|

| Input<br>capacitance                 | RES                                              | C <sub>in</sub> | _    | _                             | 30                            | pF   | $V_{in} = 0 V, f = 1 MHz, Ta$                                                                       |

|                                      | NMI                                              |                 | _    | _                             | 30                            | pF   | — = 25°C<br>                                                                                        |

|                                      | P32 to P35                                       |                 | _    | _                             | 20                            | pF   |                                                                                                     |

|                                      | All input pins<br>except RES,<br>NMI, P32 to P35 |                 |      | _                             | 15                            | pF   |                                                                                                     |

| Current<br>consumption <sup>*2</sup> | Normal operation                                 |                 |      | 30<br>V <sub>cc</sub> = 5.0 V | 40<br>V <sub>cc</sub> = 5.5 V | mA   | f = 20.5 MHz                                                                                        |

|                                      | Sleep mode                                       |                 | _    | 22<br>V <sub>cc</sub> = 5.0 V | 30<br>V <sub>cc</sub> = 5.5 V | mA   | f = 20.5 MHz                                                                                        |

|                                      | All modules<br>stopped                           |                 | _    | 15                            | _                             | mA   | $      f = 20.5 \text{ MHz}, \\ V_{cc} = 5.0 \text{ V} \\ (reference values) $                      |

|                                      | Medium-speed<br>mode (\phi/32)                   |                 | _    | 19                            | _                             | mA   | f = 20.5  MHz,<br>$V_{cc} = 5.0 \text{ V}$<br>(reference values)                                    |

|                                      | Subactive mode                                   |                 |      | 70                            | 120                           | μΑ   | Using 32.768 kHz<br>crystal resonator, Vcc =<br>5.0 V (LCD lighting)                                |

|                                      | Subsleep mode                                    |                 |      | 60                            | 100                           | μA   | Using 32.768 kHz<br>crystal resonator, Vcc =<br>5.0 V (LCD lighting)                                |

|                                      | Watch mode                                       |                 |      | 5                             | 30                            | μΑ   | Using 32.768 kHz<br>crystal resonator, Vcc =<br>5.0 V (LCD and TMR4<br>not used, WDT_1<br>operates) |

|                                      | Standby mode <sup>*3</sup>                       | -               |      | 1.0<br>Vcc = 5.0 V            | 10<br>Vcc = 5.5 V             | μA   | $T_a \le 50^{\circ}$ C, 32.768 kHz not used                                                         |

|                                      |                                                  |                 | —    |                               | 50<br>Vcc = 5.5 V             | _    | 50°C < T₄, 32.768 kHz<br>not used                                                                   |

| ltem                                 |                                  | Symbol           | Min. | Тур.               | Max.              | Unit | Test Conditions                                                                                                                                                                                                                |

|--------------------------------------|----------------------------------|------------------|------|--------------------|-------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Current<br>consumption <sup>*2</sup> | Watch mode                       | <sub>CC</sub> *4 |      | 2.5                | 8                 | μΑ   | $\label{eq:transform} \begin{array}{l} T_{\rm a} \leq 50^{\circ}\text{C}, \text{ Using} \\ 32.768 \text{ kHz crystal} \\ \text{resonator, Vcc} = 3.0 \text{ V} \\ (\text{LCD not used, WDT_1} \\ \text{operates}) \end{array}$ |

|                                      |                                  |                  |      | _                  | 10                | -    | 50°C < Ta, using<br>32.768 kHz crystal<br>resonator, Vcc = 3.0 V<br>(LCD not used, WDT_1<br>operates)                                                                                                                          |

|                                      | Standby mode <sup>*3</sup>       | _                | _    | 0.5<br>Vcc = 3.0 V | 5<br>Vcc = 5.5 V  | μA   | $T_a \le 50^{\circ}C$ , 32.768 kHz not used                                                                                                                                                                                    |

|                                      |                                  |                  | _    | _                  | 20<br>Vcc = 5.5 V | _    | 50°C < T <sub>a</sub> , 32.768 kHz<br>not used                                                                                                                                                                                 |

| Analog<br>power supply<br>current    | During A/D conversion            | $AI_{cc}$        | —    | 0.3                | 1.5               | mA   |                                                                                                                                                                                                                                |

|                                      | Waiting for<br>A/D<br>conversion | _                | _    | 0.01               | 5.0               | μΑ   |                                                                                                                                                                                                                                |

| Reference<br>current                 | During A/D conversion            | $AI_{cc}$        | —    | 0.4                | 1.0               | mA   |                                                                                                                                                                                                                                |

|                                      | Waiting for<br>A/D<br>conversion | _                | _    | 0.01               | 5.0               | μA   |                                                                                                                                                                                                                                |

| RAM standby                          | voltage                          | $V_{RAM}$        | 2.0  | _                  | _                 | V    |                                                                                                                                                                                                                                |

Section 25 Electrical Characteristics

Notes: 1. If the A/D converter is not used, do not leave the AVCC, Vref, and AVSS pins open. Apply a voltage 2.0 to 5.5 V to the AVCC and Vref pins by connecting them to  $V_{cc}$ , for instance. Set  $V_{ref} \leq AV_{cc}$ .

- 2. Current consumption values are for V<sub>IH</sub> min. = V<sub>cc</sub> 0.2 V, V<sub>IL</sub> max. = 0.2 V with all output pins unloaded and the on-chip pull-up resistors in the off state.

- 3. The values are for V\_{\_{RAM}} \le V\_{\_{CC}} < 2.7 V, V\_{\_{IH}} min. = V\_{\_{CC}} 0.2, and V\_{\_{IL}} max. = 0.2 V.

- 4.  $I_{cc}$  depends on  $V_{cc}$  and f as follows (reference):  $I_{cc}$  max. = 3.0 (mA) + 1.24 (mA/V) × (Vcc - 2.7 (V)) + 1.00 (mA/MHz) × (f - 2.0 (MHz)) (normal operation)  $I_{cc}$  max. = 2.0 (mA) + 1.12 (mA/V) × (Vcc - 2.7 (V)) + 0.64 (mA/MHz) × (f - 2.0 (MHz)) (sleep mode)

# RENESAS