Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 32MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART                                           |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 84                                                                                   |

| Program Memory Size        | 384KB (384K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 32K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x10b; D/A 2x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 100-LQFP                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3739gc-ueu-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

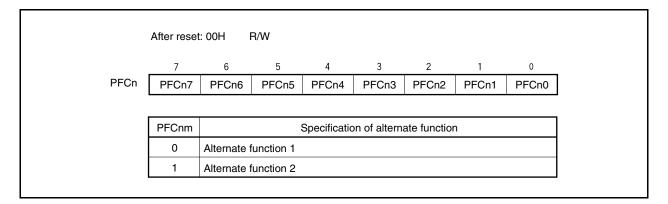

# (4) Port n function control register (PFCn)

The PFCn register specifies the alternate function of a port pin to be used if the pin has two alternate functions. Each bit of this register corresponds to one pin of port n, and the alternate function of a port pin can be specified in 1-bit units.

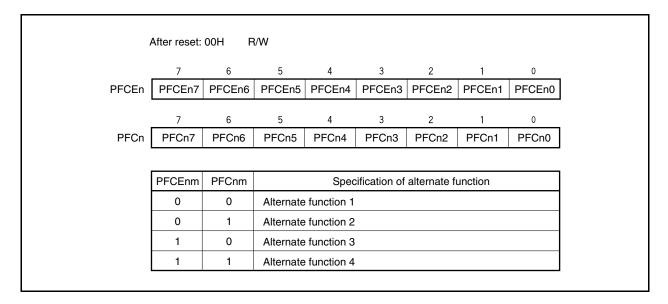

### (5) Port n function control expansion register (PFCEn)

The PFCEn register specifies the alternate function of a port pin to be used if the pin has three or more alternate functions.

Each bit of this register corresponds to one pin of port n, and the alternate function of a port pin can be specified in 1-bit units.

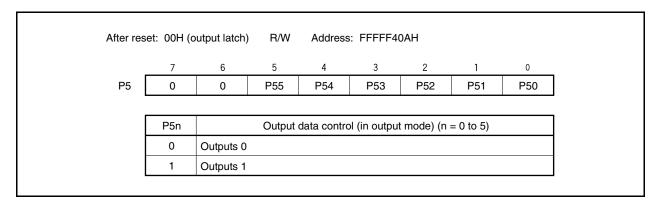

# 4.3.5 Port 5

Port 5 is a 6-bit port that controls I/O in 1-bit units. Port 5 includes the following alternate-function pins.

| Pin Name | Pin No. | Alternate-Function Pin Name                    | I/O | Remark                               | Block Type |

|----------|---------|------------------------------------------------|-----|--------------------------------------|------------|

| P50      | 37      | TIQ01/KR0/TOQ01/RTP00                          | I/O | Selectable as N-ch open-drain output | U-5        |

| P51      | 38      | TIQ02/KR1/TOQ02/RTP01                          | I/O |                                      | U-5        |

| P52      | 39      | TIQ03/KR2/TOQ03/RTP02/DDI <sup>Note</sup>      | I/O |                                      | U-6        |

| P53      | 40      | SIB2/KR3/TIQ00/TOQ00/RTP03/DDO <sup>Note</sup> | I/O |                                      | U-7        |

| P54      | 41      | SOB2/KR4/RTP04/DCK <sup>Note</sup>             | I/O |                                      | U-8        |

| P55      | 42      | SCKB2/KR5/RTP05/DMS <sup>Note</sup>            | I/O |                                      | U-9        |

# Table 4-8. Port 5 Alternate-Function Pins

Note

The DDI, DDO, DCK, and DMS pins are for on-chip debugging.

If on-chip debugging is not used, fix the P05/INTP2/DRST pin to low level between when the reset signal of the RESET pin is released and when the OCDM.OCDM0 bit is cleared (0).

For details, see 4.6.3 Cautions on on-chip debug pins.

- Cautions 1. When the power is turned on, the P53 pin may output undefined level temporarily even during reset.

- 2. The P50 to P55 pins have hysteresis characteristics in the input mode of the alternate function, but do not have hysteresis characteristics in the port mode.

- (1) Port 5 register (P5)

| PFCE52 | PFC52 | Specification of P52 pin alternate function |

|--------|-------|---------------------------------------------|

| 0      | 0     | Setting prohibited                          |

| 0      | 1     | TIQ03 input/KR2 <sup>№te</sup> input        |

| 1      | 0     | TOQ03 input                                 |

| 1      | 1     | RTP02 output                                |

| PFCE51 | PFC51 | Specification of P51 pin alternate function |

|--------|-------|---------------------------------------------|

| 0      | 0     | Setting prohibited                          |

| 0      | 1     | TIQ02 input/KR1 <sup>Note</sup> input       |

| 1      | 0     | TOQ02 output                                |

| 1      | 1     | RTP01 output                                |

| PFCE50 | PFC50 | Specification of P50 pin alternate function |

|--------|-------|---------------------------------------------|

| 0      | 0     | Setting prohibited                          |

| 0      | 1     | TIQ01 input/KR0 <sup>Note</sup> input       |

| 1      | 0     | TOQ01 output                                |

| 1      | 1     | RTP00 output                                |

**Note** The KRn pin and TIQ0m pin are alternate-function pins. When using the pin as the TIQ0m pin, disable KRn pin key return detection, which is the alternate function. (Clear the KRM.KRMn bit to 0.) Also, when using the pin as the KRn pin, disable TIQ0m pin edge detection, which is the alternate function (n = 0 to 3, m = 0 to 3).

| Pin Name  | Use as TIQ0m Pin | Use as KRn Pin                                                                         |

|-----------|------------------|----------------------------------------------------------------------------------------|

| KR0/TIQ01 | KRM.KRM0 bit = 0 | TQ0IOC1. TQ0TIG2, TQ0IOC1. TQ0TIG3 bits = 0                                            |

| KR1/TIQ02 | KRM.KRM1 bit = 0 | TQ0IOC1.TQ0TIG4, TQ0IOC1.TQ0TIG5 bits = 0                                              |

| KR2/TIQ03 | KRM.KRM2 bit = 0 | TQ0IOC1.TQ0TIG6, TQ0IOC1.TQ0TIG7 bits = 0                                              |

| KR3/TIQ00 | KRM.KRM3 bit = 0 | TQ0IOC1.TQ0TIG0, TQ0IOC1.TQ0TIG1 bits = 0<br>TQ0IOC2.TQ0EES0, TQ0IOC2.TQ0EES1 bits = 0 |

|           |                  | TQ0IOC2.TQ0ETS0, TQ0IOC2.TQ0ETS1 bits = 0                                              |

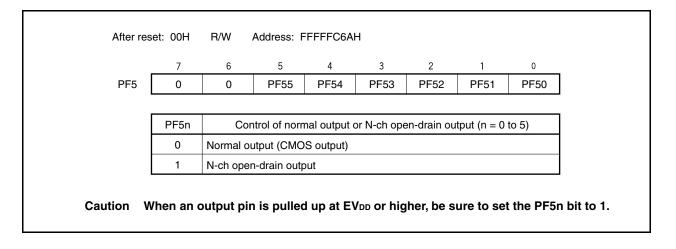

#### (7) Port 5 function register (PF5)

# (1) Port 9 register (P9)

| After res | set: 0000H                         | l (output late           | ch) R/V                               | V Addre                  |                        | FFF412H,<br>FFFF412H     |             | FF413H       |                                      |

|-----------|------------------------------------|--------------------------|---------------------------------------|--------------------------|------------------------|--------------------------|-------------|--------------|--------------------------------------|

|           | 15                                 | 14                       | 13                                    | 12                       | 11                     | 10                       | 9           | 8            | _                                    |

| P9 (P9H)  | P915                               | P914                     | P913                                  | P912                     | P911                   | P910                     | P99         | P98          |                                      |

|           | 7                                  | 6                        | 5                                     | 4                        | 3                      | 2                        | 1           | 0            |                                      |

| (P9L)     | P97                                | P96                      | P95                                   | P94                      | P93                    | P92                      | P91         | P90          |                                      |

|           | P9n<br>0<br>1                      | Outputs 0<br>Outputs 1   |                                       | data contro              | (in output             | mode) (n =               | = 0 to 15)  |              |                                      |

| 2.        | However,<br>lower 8 b<br>To read/w | when usi<br>its as the f | ng the hi<br>P9L regist<br>to 15 of t | gher 8 bi<br>ter, P9 car | ts of the<br>h be read | P9 registe<br>or written | in 8-bit or | r 1-bit unit | ster and the<br>s.<br>n as bits 0 to |

# (2) Port 9 mode register (PM9)

| After res    | et: FFFFH                 | R/W   | Address | : PM9 FFI<br>PM9L FF |              | PM9H FF    | FFF433H      |            |  |

|--------------|---------------------------|-------|---------|----------------------|--------------|------------|--------------|------------|--|

|              | 15                        | 14    | 13      | 12                   | 11           | 10         | 9            | 8          |  |

| PM9 (PM9H)   | PM915                     | PM914 | PM913   | PM912                | PM911        | PM910      | PM99         | PM98       |  |

|              | 7                         | 6     | 5       | 4                    | 3            | 2          | 1            | 0          |  |

| (PM9L)       | PM97                      | PM96  | PM95    | PM94                 | PM93         | PM92       | PM91         | PM90       |  |

|              | 0                         |       |         |                      |              |            |              |            |  |

| Remarks 1. ⊤ |                           |       |         | or written           | in 16-bit ı  | units.     |              |            |  |

|              | owever, w<br>wer 8 bits   |       | Ŭ       |                      |              | 0          |              | Ŭ          |  |

|              | o read/writ<br>7 of the F |       |         | e PM9 reg            | jister in 8∙ | bit or 1-b | it units, sp | pecify the |  |

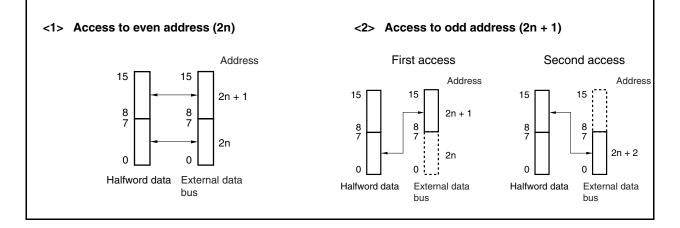

### (3) Halfword access (16 bits)

### (a) With 16-bit data bus width

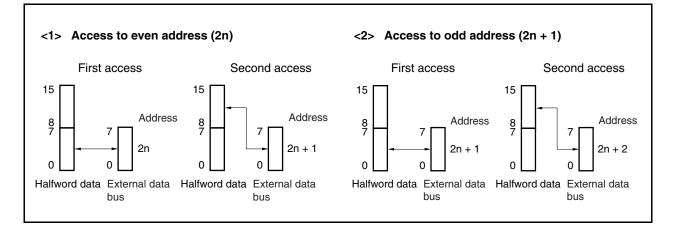

(b) 8-bit data bus width

### (3) Lock register (LOCKR)

Phase lock occurs at a given frequency following power application or immediately after the STOP mode is released, and the time required for stabilization is the lockup time (frequency stabilization time). This state until stabilization is called the lockup status, and the stabilized state is called the locked status.

The LOCKR register includes a LOCK bit that reflects the PLL frequency stabilization status.

This register is read-only, in 8-bit or 1-bit units.

Reset sets this register to 00H.

| After res                                                                                                                                                                                                | set: 00H                                           | R A                                                   | ddress: FF                                          | FFF824H                                               |                                            |                       |                     |              |                         |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------|--------------------------------------------|-----------------------|---------------------|--------------|-------------------------|--|--|

|                                                                                                                                                                                                          | 7                                                  | 6                                                     | 5                                                   | 4                                                     | 3                                          | 2                     | 1                   | <0>          |                         |  |  |

| LOCKR                                                                                                                                                                                                    | 0                                                  | 0                                                     | 0                                                   | 0                                                     | 0                                          | 0                     | 0                   | LOCK         |                         |  |  |

|                                                                                                                                                                                                          |                                                    | ·                                                     |                                                     |                                                       |                                            |                       |                     |              |                         |  |  |

|                                                                                                                                                                                                          | LOCK                                               |                                                       |                                                     | PLL k                                                 | ock status c                               | check                 |                     |              |                         |  |  |

|                                                                                                                                                                                                          | 0                                                  | Locked st                                             | _ocked status                                       |                                                       |                                            |                       |                     |              |                         |  |  |

|                                                                                                                                                                                                          | 1                                                  | Unlocked                                              | status                                              |                                                       |                                            |                       |                     |              |                         |  |  |

| <b>Conditions</b><br>[Set conditions]<br>• Upon system rese<br>• In IDLE2 or STOF<br>• Upon setting of P                                                                                                 | et <sup>Note</sup><br>2 mode                       |                                                       | PLLCTL.I                                            | PLLON bit                                             | to 0)                                      |                       |                     |              |                         |  |  |

| Upon stopping n<br>PCC.MCK bit to 1<br>Note This regist<br>oscillation                                                                                                                                   | )<br>er is set                                     | to 01H by                                             | v reset and                                         | d cleared                                             | ·                                          | -                     |                     |              | C .                     |  |  |

| <ul> <li>[Clear conditions]</li> <li>Upon overflow of <ul> <li>(3) Oscillation s</li> <li>Upon oscillation</li> <li>when the STOP r</li> <li>Upon PLL lockup</li> <li>from 0 to 1</li> </ul> </li> </ul> | tabilizati<br>stabilizati<br>node was<br>time time | on time so<br>on timer o<br>set in the<br>er overflov | elect regis<br>overflow(<br>PLL oper<br>v (time set | ster (OST<br>time set to<br>tating statu<br>t by PLLS | <b>S)</b> ))<br>by OSTS<br>is<br>register) | register)<br>when the | following<br>PLLCTL | 3 STOP mod   | e release,<br>s changed |  |  |

| <ul> <li>After the setup tir<br/>when the IDLE2 r</li> </ul>                                                                                                                                             |                                                    | -                                                     |                                                     |                                                       | mode is                                    | released              | (time set           | t by the OST | S register)             |  |  |

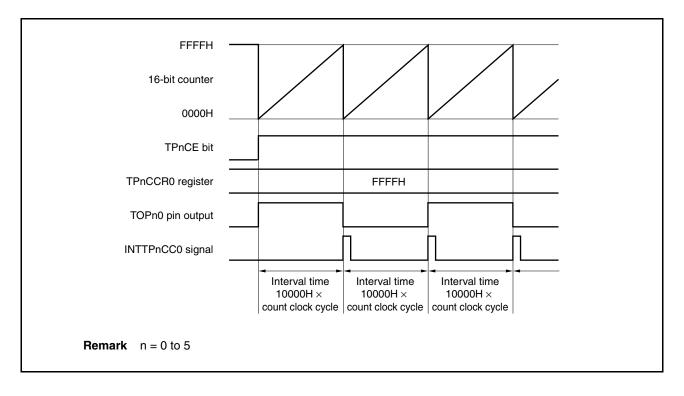

### (b) Operation if TPnCCR0 register is set to FFFFH

If the TPnCCR0 register is set to FFFFH, the 16-bit counter counts up to FFFFH. The counter is cleared to 0000H in synchronization with the next count-up timing. The INTTPnCC0 signal is generated and the output of the TOPn0 pin is inverted. At this time, an overflow interrupt request signal (INTTPnOV) is not generated, nor is the overflow flag (TPnOPT0.TPnOVF bit) set to 1.

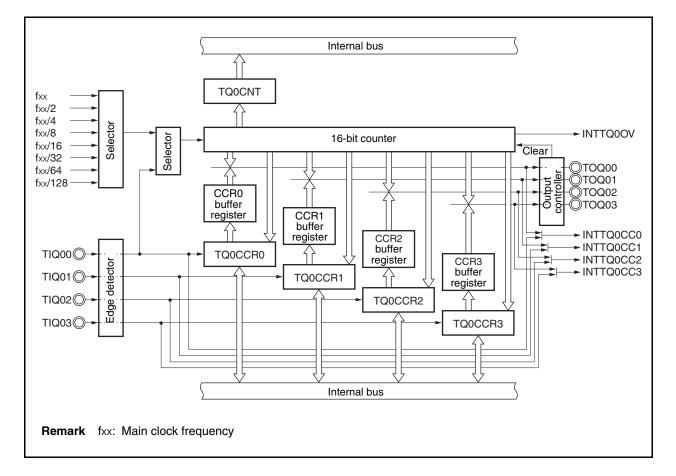

# 8.3 Configuration

TMQ0 includes the following hardware.

| Item                                | Configuration                                                                                                                                |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Timer register                      | 16-bit counter                                                                                                                               |

| Registers                           | TMQ0 capture/compare registers 0 to 3 (TQ0CCR0 to TQ0CCR3)<br>TMQ0 counter read buffer register (TQ0CNT)<br>CCR0 to CCR3 buffer registers    |

| Timer inputs                        | 4 (TIQ00 <sup>Note 1</sup> to TIQ03 pins)                                                                                                    |

| Timer outputs                       | 4 (TOQ00 to TOQ03 pins)                                                                                                                      |

| Control registers <sup>Note 2</sup> | TMQ0 control registers 0, 1 (TQ0CTL0, TQ0CTL1)<br>TMQ0 I/O control registers 0 to 2 (TQ0IOC0 to TQ0IOC2)<br>TMQ0 option register 0 (TQ0OPT0) |

### Table 8-1. Configuration of TMQ0

- **Notes 1.** The TIQ00 pin functions alternately as a capture trigger input signal, external event count input signal, and external trigger input signal.

- 2. When using the functions of the TIQ00 to TIQ03 and TOQ00 to TOQ03 pins, see Table 4-15 Using Port Pin as Alternate-Function Pin.

| Figure 8-1. | Block Diagram | of TMQ0 |

|-------------|---------------|---------|

|             | Bioon Biagian |         |

# (6) TMQ0 option register 0 (TQ0OPT0)

The TQ0OPT0 register is an 8-bit register used to set the capture/compare operation and detect an overflow. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00H.

| After reset: 00H                                                |                                                                            | Address:                                                               | FFFFF545                                                                                                |                                                          | _                                                    |                                                |                                                      |

|-----------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------|------------------------------------------------|------------------------------------------------------|

|                                                                 | 6<br>3 TQ0CCS2                                                             | 5<br>TQ0CCS1                                                           | 4<br>TQ0CCS0                                                                                            | 3<br>0                                                   | 2                                                    | 1                                              | <0><br>TQ0OVF                                        |

|                                                                 | 1                                                                          | 1                                                                      |                                                                                                         | -                                                        |                                                      |                                                |                                                      |

| TQ0CCSm                                                         | ı                                                                          | TQ0C0                                                                  | CRm register                                                                                            | capture/                                                 | compare se                                           | election                                       |                                                      |

| 0                                                               | 0     Compare register selected       1     Capture register selected      |                                                                        |                                                                                                         |                                                          |                                                      |                                                |                                                      |

| 1                                                               |                                                                            |                                                                        |                                                                                                         |                                                          |                                                      |                                                |                                                      |

| The TQ                                                          | OCCSm bit                                                                  | setting is v                                                           | alid only in th                                                                                         | e free-ru                                                | nning timer                                          | r mode.                                        |                                                      |

|                                                                 |                                                                            |                                                                        |                                                                                                         |                                                          |                                                      |                                                |                                                      |

| та                                                              | 00VF                                                                       |                                                                        | TMQ0 ov                                                                                                 | verflow de                                               | etection                                             |                                                |                                                      |

| Set (1)                                                         |                                                                            | Overflow                                                               | occurred                                                                                                |                                                          |                                                      |                                                |                                                      |

| Reset (0                                                        | Reset (0) TQ0OVF bit 0 written or TQ0CTL0.TQ0CE bit = 0                    |                                                                        |                                                                                                         |                                                          |                                                      |                                                |                                                      |

| TQ0O <sup>V</sup><br>than th<br>• The TC<br>registe<br>• The TC | /F bit is set<br>e free-runn<br>200VF bit i<br>r are read v<br>200VF bit o | to 1. The<br>ing timer m<br>s not cleare<br>when the T(<br>can be both | NTTQ0OV) is<br>INTTQ0OV s<br>ode and the<br>ed even wher<br>Q0OVF bit =<br>read and wr<br>as no influen | ignal is n<br>pulse wic<br>1 the TQ(<br>1.<br>itten, but | ot generate<br>Ith measure<br>OVF bit or<br>the TQ0O | ed in moc<br>ement mo<br>the TQ0<br>VF bit car | les other<br>ode.<br>OPT0<br>nnot be set             |

| Cautions                                                        | TQ0<br>whe                                                                 | CTL0.TQ0<br>n the TG<br>ormed, cl                                      | DCE bit = 0<br>NOCE bit =                                                                               | . (The<br>1.) If                                         | same va<br>rewriting                                 | lue can<br>g was                               | when the<br>be written<br>mistakenly<br>set the bits |

### (1) Clock control

This block controls supplying and stopping the operating clock (fx) when the watch timer operates on the main clock.

### (2) 3-bit prescaler

This prescaler divides fx to generate fx/2, fx/4, or fx/8.

### (3) 8-bit counter

This 8-bit counter counts the source clock (fbgcs).

### (4) 11-bit prescaler

This prescaler divides fw to generate a clock of  $fw/2^4$  to  $fw/2^{11}$ .

#### (5) 5-bit counter

This counter counts fw or fw/2<sup>9</sup>, and generates a watch timer interrupt request signal at intervals of  $2^4$ /fw,  $2^5$ /fw,  $2^{12}$ /fw, or  $2^{14}$ /fw.

#### (6) Selector

The watch timer has the following five selectors.

- Selector that selects one of fx, fx/2, fx/4, or fx/8 as the source clock of the watch timer

- Selector that selects the main clock (fx) or subclock (fxr) as the clock of the watch timer

- Selector that selects fw or fw/29 as the count clock frequency of the 5-bit counter

- Selector that selects 2<sup>4</sup>/fw, 2<sup>13</sup>/fw, 2<sup>5</sup>/fw, or 2<sup>14</sup>/fw as the INTWT signal generation time interval

- Selector that selects 2<sup>4</sup>/fw to 2<sup>11</sup>/fw as the interval timer interrupt request signal (INTWTI) generation time interval

#### (7) PRSCM register

This is an 8-bit compare register that sets the interval time.

#### (8) PRSM register

This register controls clock supply to the watch timer.

#### (9) WTM register

This is an 8-bit register that controls the operation of the watch timer/interval timer, and sets the interrupt request signal generation interval.

### (2) Prescaler compare register 0 (PRSCM0)

The PRSCM0 register is an 8-bit compare register. This register can be read or written in 8-bit units. Reset sets this register to 00H.

| After res                                                                        | set: 00H          | R/W        | Address: F             | FFFF8B1H            | 4                     |          |         |           |           |

|----------------------------------------------------------------------------------|-------------------|------------|------------------------|---------------------|-----------------------|----------|---------|-----------|-----------|

|                                                                                  | 7                 | 6          | 5                      | 4                   | 3                     | 2        | 1       | 0         |           |

| PRSCM0                                                                           | PRSCM07           | PRSCM06    | PRSCM05                | PRSCM04             | PRSCM03               | PRSCM02  | PRSCM01 | PRSCM00   |           |

| <ol> <li>Do not i</li> <li>Set the</li> <li>Set the</li> <li>so as to</li> </ol> | PRSCM0<br>PRSM0 a | register b | pefore se<br>M0 regist | tting the lars acco | PRSM0.B<br>rding to t | GCE0 bit | to 1.   | quency th | at is use |

The calculation for fBRG is shown below.

$f_{BRG} = f_{BGCS}/2N$

Remark fBGCS: Watch timer source clock set by the PRSM0 register

N: Set value of PRSCM0 register = 1 to 256 However, N = 256 only when PRSCM0 register is set to 00H.

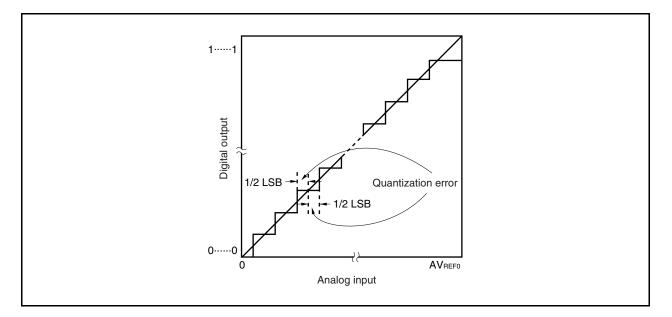

### (3) Quantization error

This is an error of  $\pm 1/2$  LSB that inevitably occurs when an analog value is converted into a digital value. Because the A/D converter converts analog input voltages in a range of  $\pm 1/2$  LSB into the same digital codes, a quantization error is unavoidable.

This error is not included in the overall error, zero-scale error, full-scale error, integral linearity error, or differential linearity error in the characteristics table.

Figure 13-17. Quantization Error

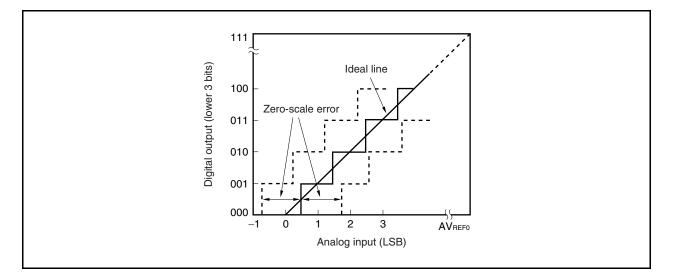

### (4) Zero-scale error

This is the difference between the actually measured analog input voltage and its theoretical value when the digital output changes from 0...000 to 0...001 (1/2 LSB).

Figure 13-18. Zero-Scale Error

### (2) CSIBn control register 1 (CBnCTL1)

CBnCTL1 is an 8-bit register that controls the CSIBn serial transfer operation. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00H.

#### Caution The CBnCTL1 register can be rewritten only when the CBnCTL0.CBnPWR bit = 0.

| After res    | et 00H R/               | W Ad    |                                          | OCTL1 FFF                                    |                                 |                                               |                             |                                               |

|--------------|-------------------------|---------|------------------------------------------|----------------------------------------------|---------------------------------|-----------------------------------------------|-----------------------------|-----------------------------------------------|

|              |                         |         |                                          | 2CTL1 FFF                                    |                                 | CB3CTL1 I                                     | FFFFD31                     | H,                                            |

|              |                         |         | CB                                       | 4CTL1 FFF                                    | FFD41H                          |                                               |                             |                                               |

|              | 7                       | 6       | 5                                        | 4                                            | 3                               | 2                                             | 1                           | 0                                             |

| CBnCTL1      | 0                       | 0       | 0                                        | CBnCKP                                       | CBnDAP                          | CBnCKS2                                       | CBnCKS1                     | CBnCKS0                                       |

| (n = 0 to 4) |                         |         | 1 1                                      |                                              | 0 10 11                         |                                               | ,                           |                                               |

|              |                         | CBnCKF  | CBnDAP                                   |                                              | Specification<br>reception time | on of data tra<br>ning in relatio             | nsmission/<br>n to SCKBn    |                                               |

|              | Communication<br>type 1 | n O     |                                          | SCKBn (I/O)<br>GOBn (output)<br>SIBn capture | <br>(7<br>↑                     | <u>□6 ( D5 ( D</u>                            | <u>4 X D3 X D2</u><br>↑ ↑   | <u>↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ </u> |

|              | Communication<br>type 2 | n O     | s                                        | SCKBn (I/O)<br>OBn (output)<br>SIBn capture  |                                 | <u>↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ </u> |                             |                                               |

|              | Communication<br>type 3 | n 1     |                                          | SCKBn (I/O)<br>GOBn (output)<br>SIBn capture | <br>( □7 )(<br>↑                | <u>D6 X D5 X D</u><br>↑ ↑ ↑                   | <u>↓ ↓ D3 ↓ D2</u>          | ∑<br>X_D1 X_D0<br>↑ ↑                         |

|              | Communication<br>type 4 | n 1     |                                          | SCKBn (I/O)<br>60Bn (output)<br>SIBn capture |                                 |                                               | <br><u>D3 ( D2 (</u><br>↑ ↑ | <b>Γ</b> _Γ<br><u>D1 X D0</u> ↑ ↑             |

|              | CBnCKS2 C               | BnCKS1  | CBnCKS0                                  | Commun                                       | ication cloc                    | ck (fcclк) <sup>Note</sup>                    | , N                         | lode                                          |

|              | 0                       | 0       | 0                                        | fxx/2                                        |                                 |                                               | Master                      | r mode                                        |

|              | 0                       | 0       | 1                                        | fxx/4                                        |                                 |                                               | Master                      | r mode                                        |

|              | 0                       | 1       | 0                                        | fxx/8                                        |                                 |                                               | Master                      | r mode                                        |

|              | 0                       | 1       | 1                                        | fxx/16                                       |                                 |                                               | Master                      | r mode                                        |

|              | 1                       | 0       | 0                                        | fxx/32                                       |                                 |                                               | Master                      | r mode                                        |

|              | 1                       | 0       | 1                                        | fxx/64                                       |                                 |                                               | Master                      | r mode                                        |

|              | 1                       | 1       | 0                                        | <b>f</b> BRGm                                |                                 |                                               | Master                      | r mode                                        |

|              | 1                       | 1       | 1                                        | External                                     | clock (SCK                      | Bn)                                           | Slave                       | mode                                          |

|              | Note Set                | the com | municatio                                | ication clock (fccLk) to 8 MHz or lower.     |                                 |                                               |                             |                                               |

|              |                         | When n  | = 0 or 1, r<br>= 2 or 3, r<br>= 4, m = 3 | m = 2                                        |                                 |                                               |                             |                                               |

|              |                         |         |                                          | m, see <b>16.</b> 8                          | 8 Baud F                        | Rate Gene                                     | erator.                     |                                               |

RENESAS

(6) When arbitration loss occurs due to low level of SDA0n pin when attempting to generate a restart condition

|                                     |                                                                                                         |                                                                                                 |                                                              |                                                | llCCr        | n.STTn bit = 1                                       |             |                |     |    |

|-------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------|--------------|------------------------------------------------------|-------------|----------------|-----|----|

| ST                                  | AD6 to AD0                                                                                              | R/W                                                                                             | ĀCK                                                          | D7 to D0                                       | ACK          | D7 to D0                                             | ACK         | D7 to D0       | ACK | SP |

|                                     | •                                                                                                       |                                                                                                 |                                                              | <b>1</b>                                       | <b>1</b> 2   | 3                                                    | ▲4          |                |     |    |

| ▲1                                  | : IICSn register                                                                                        | = 1000                                                                                          | X110B                                                        |                                                |              |                                                      |             |                |     |    |

| ▲2                                  | : IICSn register                                                                                        | = 1000                                                                                          | X000B (                                                      | WTIMn bit = 1                                  | )            |                                                      |             |                |     |    |

| ▲3                                  | : IICSn register                                                                                        | = 1000                                                                                          | XX00B (                                                      | WTIMn bit = 0                                  | )            |                                                      |             |                |     |    |

| ▲4                                  | : IICSn register                                                                                        | = 0100                                                                                          | 0000B (B                                                     | Example: Whe                                   | n ALDn       | bit is read duri                                     | ing interr  | upt servicing) |     |    |

| Δ 5                                 | IICSn register                                                                                          | = 00000                                                                                         | 0001B                                                        |                                                |              |                                                      |             |                |     |    |

|                                     |                                                                                                         | : Gen<br>: don'<br>= 0 to :                                                                     | erated<br>t care                                             | only when S                                    | PIEn bit     | = 1                                                  |             |                |     |    |

|                                     | ۵<br>۲<br><b>2.</b> n                                                                                   | : Gen<br>: don'<br>= 0 to :                                                                     | erated<br>t care                                             |                                                |              | = 1<br>n.STTn bit = 1                                | _           |                | _   |    |

|                                     | ۵<br>X<br><b>2.</b> n                                                                                   | : Gen<br>: don'<br>= 0 to :                                                                     | erated<br>t care                                             |                                                |              |                                                      | ĀCK         | D7 to D0       | ĀCK | SP |

| > Wh                                | ۵<br>۲<br>2. n<br>en WTIMn bi                                                                           | : Gen<br>: don'<br>= 0 to :<br>t = 1                                                            | erated<br>t care<br>2                                        | only when Sl                                   | IICCr<br>ACK | n.STTn bit = 1                                       |             | D7 to D0       | ACK | SP |

| > Wh                                | ۵<br>۲<br>2. n<br>en WTIMn bi                                                                           | : Gen<br>: don'<br>= 0 to :<br>t = 1<br>R/W                                                     | erated<br>t care<br>2<br>ACK                                 | only when Sl                                   | IICCr<br>ACK | n.STTn bit = 1                                       |             |                | ĀCK | SP |

| > Wh<br>ST<br>                      | ۵<br>۲<br>۲<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹        | : Gen<br>: don'<br>= 0 to :<br>t = 1<br>R/W<br>= 1000.                                          | ACK<br>ACK<br>X110B<br>XX00B                                 | only when Sl<br>D7 to D0<br>▲1                 |              | n.STTn bit = 1<br>D7 to D0<br>▲2                     | · · · · · · | 3              | ACK | SP |

| > Wh<br>ST<br>                      | A<br>X<br>2. n<br>en WTIMn bi<br>AD6 to AD0<br>: IICSn register<br>: IICSn register<br>: IICSn register | : Gen<br>: don'<br>= 0 to :<br>t = 1<br>$R/\overline{W}$<br>= 1000<br>= 1000<br>= 0100          | ACK<br>ACK<br>X110B<br>XX00B<br>0100B (f                     | only when Sl<br>D7 to D0<br>▲1                 |              | n.STTn bit = 1<br>D7 to D0<br>▲2                     | · · · · · · | 3              | ĀĊK | SP |

| > Wh<br>ST<br>                      | ۵<br>۲<br>۲<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹<br>۹        | : Gen<br>: don'<br>= 0 to :<br>t = 1<br>$R/\overline{W}$<br>= 1000<br>= 1000<br>= 0100          | ACK<br>ACK<br>X110B<br>XX00B<br>0100B (f                     | only when Sl<br>D7 to D0<br>▲1                 |              | n.STTn bit = 1<br>D7 to D0<br>▲2                     | · · · · · · | 3              | ĀĊĶ | SP |

| > Wh<br>ST<br>▲1<br>▲2<br>▲3<br>△ 4 | A<br>X<br>2. n<br>en WTIMn bi<br>AD6 to AD0<br>: IICSn register<br>: IICSn register<br>: IICSn register | : Gen<br>: don'<br>= 0 to :<br>t = 1<br>R/W<br>= 1000<br>= 1000<br>= 0100                       | ACK<br>ACK<br>X110B<br>XX00B<br>0100B (F<br>0001B            | only when Sl<br>D7 to D0<br>▲1<br>Example: Whe |              | n.STTn bit = 1<br>D7 to D0<br>▲2                     | · · · · · · | 3              | ĀĊK | SP |

| > Wh<br>ST<br>▲1<br>▲2<br>▲3<br>△ 4 | A<br>X<br>2. n<br>en WTIMn bi<br>AD6 to AD0<br>: IICSn register<br>: IICSn register<br>: IICSn register | : Gen<br>: don'<br>= 0 to :<br>t = 1<br>R/W<br>= 1000<br>= 1000<br>= 0100<br>= 00000<br>A: Alwa | ACK<br>ACK<br>X110B<br>XX00B<br>0100B (R<br>0001B<br>ays gen | only when Sl<br>D7 to D0<br>▲1<br>Example: Whe | IICCr<br>ACK | a.STTn bit = 1<br>D7 to D0<br>▲2<br>bit is read duri | · · · · · · | 3              | ĀĊK | SP |

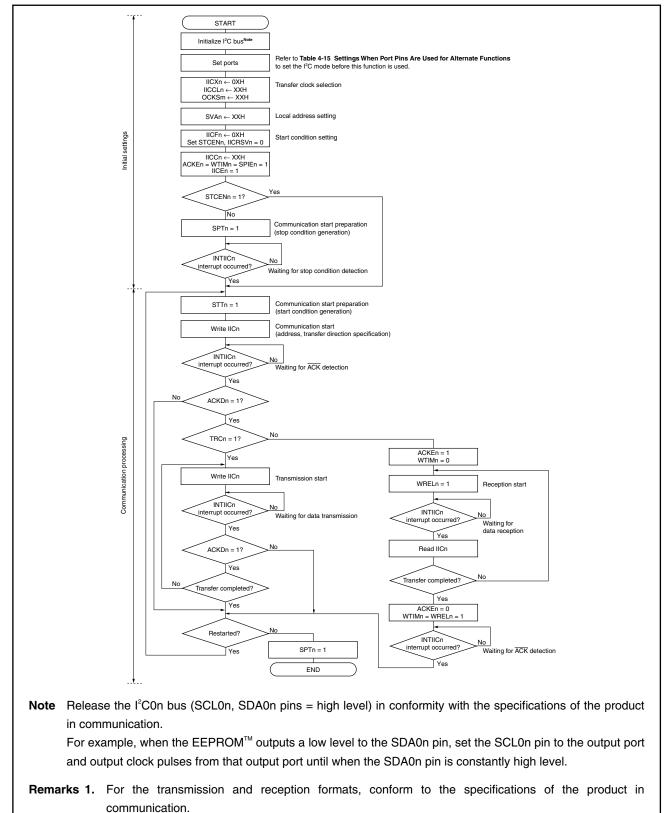

### 17.16.1 Master operation in single master system

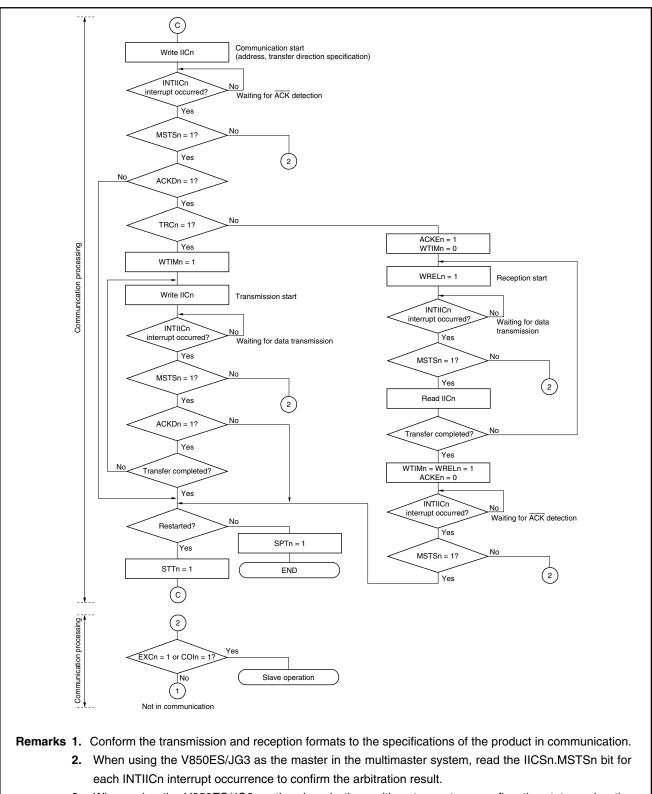

**2.** n = 0 to 2, m = 0, 1

RENESAS

Figure 17-19. Master Operation in Multimaster System (3/3)

- each INTITCh interrupt occurrence to confirm the arbitration result.

When using the V850ES/JG3 as the slave in the multimaster system, confirm the status using the IICSh and IICFh registers for each INTITCh interrupt occurrence to determine the next processing.

- **4.** n = 0 to 2

| IFCn5 | IFCn4 | IFCn3 | IFCn2 | IFCn1 | IFCn0 | Interrupt Source                  |

|-------|-------|-------|-------|-------|-------|-----------------------------------|

| 0     | 0     | 0     | 0     | 0     | 0     | DMA request by interrupt disabled |

| 0     | 0     | 0     | 0     | 0     | 1     | INTP0                             |

| 0     | 0     | 0     | 0     | 1     | 0     | INTP1                             |

| 0     | 0     | 0     | 0     | 1     | 1     | INTP2                             |

| 0     | 0     | 0     | 1     | 0     | 0     | INTP3                             |

| 0     | 0     | 0     | 1     | 0     | 1     | INTP4                             |

| 0     | 0     | 0     | 1     | 1     | 0     | INTP5                             |

| 0     | 0     | 0     | 1     | 1     | 1     | INTP6                             |

| 0     | 0     | 1     | 0     | 0     | 0     | INTP7                             |

| 0     | 0     | 1     | 0     | 0     | 1     | INTTQ0OV                          |

| 0     | 0     | 1     | 0     | 1     | 0     | INTTQ0CC0                         |

| 0     | 0     | 1     | 0     | 1     | 1     | INTTQ0CC1                         |

| 0     | 0     | 1     | 1     | 0     | 0     | INTTQ0CC2                         |

| 0     | 0     | 1     | 1     | 0     | 1     | INTTQ0CC3                         |

| 0     | 0     | 1     | 1     | 1     | 0     | INTTP0OV                          |

| 0     | 0     | 1     | 1     | 1     | 1     | INTTP0CC0                         |

| 0     | 1     | 0     | 0     | 0     | 0     | INTTP0CC1                         |

| 0     | 1     | 0     | 0     | 0     | 1     | INTTP1OV                          |

| 0     | 1     | 0     | 0     | 1     | 0     | INTTP1CC0                         |

| 0     | 1     | 0     | 0     | 1     | 1     | INTTP1CC1                         |

| 0     | 1     | 0     | 1     | 0     | 0     | INTTP2OV                          |

| 0     | 1     | 0     | 1     | 0     | 1     | INTTP2CC0                         |

| 0     | 1     | 0     | 1     | 1     | 0     | INTTP2CC1                         |

| 0     | 1     | 0     | 1     | 1     | 1     | INTTP3CC0                         |

| 0     | 1     | 1     | 0     | 0     | 0     | INTTP3CC1                         |

| 0     | 1     | 1     | 0     | 0     | 1     | INTTP4CC0                         |

| 0     | 1     | 1     | 0     | 1     | 0     | INTTP4CC1                         |

| 0     | 1     | 1     | 0     | 1     | 1     | INTTP5CC0                         |

| 0     | 1     | 1     | 1     | 0     | 0     | INTTP5CC1                         |

| 0     | 1     | 1     | 1     | 0     | 1     | INTTM0EQ0                         |

| 0     | 1     | 1     | 1     | 1     | 0     | INTCB0R/INTIIC1                   |

| 0     | 1     | 1     | 1     | 1     | 1     | INTCB0T                           |

| 1     | 0     | 0     | 0     | 0     | 0     | INTCB1R                           |

| 1     | 0     | 0     | 0     | 0     | 1     | INTCB1T                           |

| 1     | 0     | 0     | 0     | 1     | 0     | INTCB2R                           |

| 1     | 0     | 0     | 0     | 1     | 1     | INTCB2T                           |

| 1     | 0     | 0     | 1     | 0     | 0     | INTCB3R                           |

| 1     | 0     | 0     | 1     | 0     | 1     | INTCB3T                           |

| 1     | 0     | 0     | 1     | 1     | 0     | INTUA0R/INTCB4R                   |

| 1     | 0     | 0     | 1     | 1     | 1     | INTUA0T/INTCB4T                   |

| 1     | 0     | 1     | 0     | 0     | 0     | INTUA1R/INTIIC2                   |

| 1     | 0     | 1     | 0     | 0     | 1     | INTUA1T                           |

| 1     | 0     | 1     | 0     | 1     | 0     | INTUA2R/INTIIC0                   |

| Table 18-1. | DMA St | art Factors (1/2) |

|-------------|--------|-------------------|

|-------------|--------|-------------------|

**Remark** n = 0 to 3

# 21.4 IDLE1 Mode

#### 21.4.1 Setting and operation status

The IDLE1 mode is set by clearing the PSMR.PSM1 and PSMR.PSM0 bits to 00 and setting the PSC.STP bit to 1 in the normal operation mode.

In the IDLE1 mode, the clock oscillator, PLL, and flash memory continue operating but clock supply to the CPU and other on-chip peripheral functions stops.

As a result, program execution stops and the contents of the internal RAM before the IDLE1 mode was set are retained. The CPU and other on-chip peripheral functions stop operating. However, the on-chip peripheral functions that can operate with the subclock or an external clock continue operating.

Table 21-5 shows the operating status in the IDLE1 mode.

The IDLE1 mode can reduce the power consumption more than the HALT mode because it stops the operation of the on-chip peripheral functions. The main clock oscillator does not stop, so the normal operation mode can be restored without waiting for the oscillation stabilization time after the IDLE1 mode has been released, in the same manner as when the HALT mode is released.

- Cautions 1. Insert five or more NOP instructions after the instruction that stores data in the PSC register to set the IDLE1 mode.

- 2. If the IDLE1 mode is set while an unmasked interrupt request signal is being held pending, the IDLE1 mode is released immediately by the pending interrupt request.

#### 21.4.2 Releasing IDLE1 mode

The IDLE1 mode is released by a non-maskable interrupt request signal (NMI pin input, INTWDT2 signal), unmasked external interrupt request signal (INTP0 to INTP7 pin input), unmasked internal interrupt request signal from a peripheral function operable in the IDLE1 mode, or reset signal (reset by RESET pin input, WDT2RES signal, low-voltage detector (LVI), or clock monitor (CLM)).

After the IDLE1 mode has been released, the normal operation mode is restored.

(1) Releasing IDLE1 mode by non-maskable interrupt request signal or unmasked maskable interrupt request signal

The IDLE1 mode is released by a non-maskable interrupt request signal or an unmasked maskable interrupt request signal, regardless of the priority of the interrupt request signal. If the IDLE1 mode is set in an interrupt servicing routine, however, an interrupt request signal that is issued later is processed as follows.

- (a) If an interrupt request signal with a priority lower than that of the interrupt request currently being serviced is issued, the IDLE1 mode is released, but that interrupt request signal is not acknowledged. The interrupt request signal itself is retained.

- (b) If an interrupt request signal with a priority higher than that of the interrupt request currently being serviced is issued (including a non-maskable interrupt request signal), the IDLE1 mode is released and that interrupt request signal is acknowledged.

Caution An interrupt request signal that is disabled by setting the PSC.NMI1M, PSC.NMI0M, and PSC.INTM bits to 1 becomes invalid and IDLE1 mode is not released.

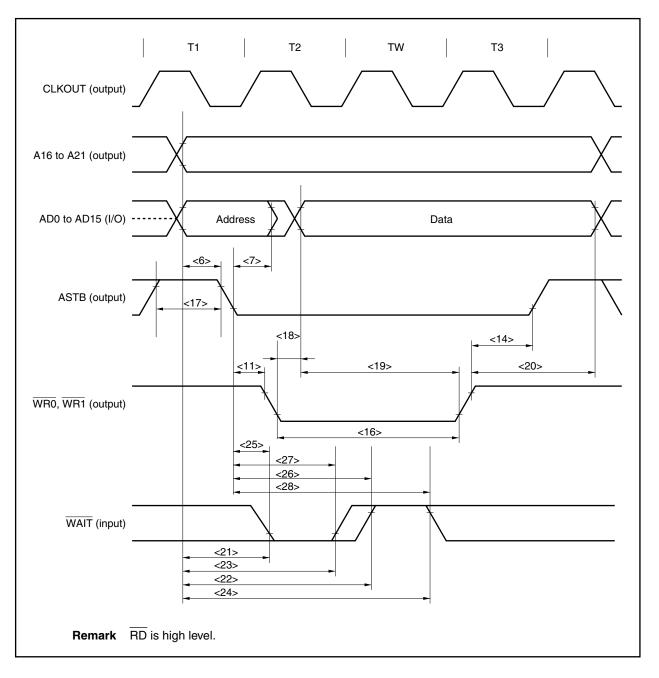

# Write Cycle (CLKOUT Asynchronous): In Multiplexed Bus Mode

<u>(19/3</u>6)

|            |                |                     |                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 19/3 |

|------------|----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| Chapter    | Classification | Function            | Details of<br>Function                                                                                                                                                                                                                                                                                                           | Cautions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pag    | e    |

| Chapter 15 | Asynchro-      |                     | UART<br>reception                                                                                                                                                                                                                                                                                                                | The operation during reception is performed assuming that there is only one stop bit. A second stop bit is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                     | p. 470 |      |

| Chap       | 5 (UARTA)      |                     | When reception is completed, read the UAnRX register after the reception complete interrupt request signal (INTUAnR) has been generated, and clear the UAnPWR or UAnRXE bit to 0. If the UAnPWR or UAnRXE bit is cleared to 0 before the INTUAnR signal is generated, the read value of the UAnRX register cannot be guaranteed. | p. 470                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |      |

|            |                |                     |                                                                                                                                                                                                                                                                                                                                  | If receive completion processing (INTUAR signal generation) of UARTAn and<br>the UAnPWR bit = 0 or UARRXE bit = 0 conflict, the INTUAR signal may be<br>generated in spite of these being no data stored in the UAnRX register.<br>To complete reception without waiting INTUARR signal generation, be sure to<br>clear (0) the interrupt request flag (UAnRIF) of the UAnRIC register, after setting<br>(1) the interrupt mask flag (UAnRMK) of the interrupt control register (UAnRIC)<br>and then set (1) the UAnPWR bit = 0 or UAnRXE bit = 0.                      | p. 470 |      |

|            |                |                     | Reception<br>errors                                                                                                                                                                                                                                                                                                              | When an INTUAnR signal is generated, the UAnSTR register must be read to check for errors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | p. 471 |      |

|            |                |                     |                                                                                                                                                                                                                                                                                                                                  | If a receive error interrupt occurs during continuous reception, read the contents of the UAnSTR register must be read before the next reception is completed, then perform error processing.                                                                                                                                                                                                                                                                                                                                                                           | p. 472 |      |

|            |                | LIN function        | When using the LIN function, fix the UAnPS1 and UAnPS0 bits of the UAnCTL0 register to 00.                                                                                                                                                                                                                                       | p. 473                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |      |

|            |                | UAnCTL1<br>register | Clear the UAnCTL0.UAnPWR bit to 0 before rewriting the UAnCTL1 register.                                                                                                                                                                                                                                                         | p. 476                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |      |

|            |                |                     | UAnCTL2<br>register                                                                                                                                                                                                                                                                                                              | Clear the UAnCTL0.UAnPWR bit to 0 or clear the UAnTXE and UAnRXE bits to 00 before rewriting the UAnCTL2 register.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | p. 477 |      |

|            |                |                     | Baud rate error                                                                                                                                                                                                                                                                                                                  | The baud rate error during transmission must be within the error tolerance on the receiving side.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | p. 478 |      |

|            |                |                     |                                                                                                                                                                                                                                                                                                                                  | The baud rate error during reception must satisfy the range indicated in (5)<br>Allowable baud rate range during reception.                                                                                                                                                                                                                                                                                                                                                                                                                                             | p. 478 |      |

|            |                |                     | Allowable baud<br>rate range<br>during<br>reception                                                                                                                                                                                                                                                                              | The baud rate error during reception must be set within the allowable error range using the following equation.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | p. 480 |      |

|            |                |                     | When the clock<br>supply to<br>UARTAn is<br>stopped                                                                                                                                                                                                                                                                              | When the clock supply to UARTAn is stopped (for example, in IDLE1, IDLE2, or STOP mode), the operation stops with each register retaining the value it had immediately before the clock supply was stopped. The TXDAn pin output also holds and outputs the value it had immediately before the clock supply was stopped. However, the operation is not guaranteed after the clock supply is resumed. Therefore, after the clock supply is resumed, the circuits should be initialized by setting the UAnCTL0.UAnPWR, UAnCTL0.UAnRXEn, and UAnCTL0.UAnTXEn bits to 000. | p. 483 |      |

|            |                |                     | RXDA1 pin<br>KR7 pin                                                                                                                                                                                                                                                                                                             | The RXDA1 and KR7 pins must not be used at the same time. To use the RXDA1 pin, do not use the KR7 pin. To use the KR7 pin, do not use the RXDA1 pin (it is recommended to set the PFC91 bit to 1 and clear PFCE91 bit to 0).                                                                                                                                                                                                                                                                                                                                           | p. 483 |      |

|            |                |                     | Performing the<br>transfer of<br>transmit data<br>and receive<br>data using<br>DMA transfer                                                                                                                                                                                                                                      | In UARTAn, the interrupt caused by a communication error does not occur. When performing the transfer of transmit data and receive data using DMA transfer, error processing cannot be performed even if errors (parity, overrun, framing) occur during transfer. Either read the UAnSTR register after DMA transfer has been completed to make sure that there are no errors, or read the UAnSTR register during communication to check for errors.                                                                                                                    | p. 483 |      |