# E. Renesas Electronics America Inc - UPD70F3740GC-UEU-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                  |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 32MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART                                           |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 84                                                                                   |

| Program Memory Size        | 512KB (512K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | <u>.</u>                                                                             |

| RAM Size                   | 40K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x10b; D/A 2x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 100-LQFP                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3740gc-ueu-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# (7) Port 3 function register (PF3)

| After res    | set: 0000H | I R/W       | Address      | : PF3 FFF<br>PF3L FFF | FFC66H,<br>FFFC66H, | PF3H FFF    | FFC67H      |                                            |

|--------------|------------|-------------|--------------|-----------------------|---------------------|-------------|-------------|--------------------------------------------|

|              | 15         | 14          | 13           | 12                    | 11                  | 10          | 9           | 8                                          |

| PF3 (PF3H)   | 0          | 0           | 0            | 0                     | 0                   | 0           | PF39        | PF38                                       |

|              | 7          | 6           | 5            | 4                     | 3                   | 2           | 1           | 0                                          |

| (PF3L)       | PF37       | PF36        | PF35         | PF34                  | PF33                | PF32        | PF31        | PF30                                       |

|              | PF3n       | Con         | trol of norm | nal output c          | or N-ch ope         | n-drain ou  | tput (n = 0 | to 9)                                      |

|              | 0          | Normal ou   | Itput (CMO   | S output)             |                     |             |             |                                            |

|              | 1          | N-ch oper   | n-drain outp | out                   |                     |             |             |                                            |

| Remarks 1. T | The PF3 r  | egister car | n be read    | or written            | in 16-bit ı         | units.      |             | <b>ie PF3n bit to 1</b><br>F3H register ar |

|              | ower 8 bit | s as the P  | F3L regist   | er, PF3 ca            | an be rea           | d or writte | n in 8-bit  | or 1-bit units.                            |

# (3) TMPn I/O control register 0 (TPnIOC0)

The TPnIOC0 register is an 8-bit register that controls the timer output (TOPn0, TOPn1 pins). This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00H.

| After res    | set: 00H   | R/W                                     | Address:                                                      | TP0IOC0                                                                                          | FFFFF592                                         | H, TP1IOC                                                   | 0 FFFF5                                      | 5A2H,                                         |   |

|--------------|------------|-----------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------|----------------------------------------------|-----------------------------------------------|---|

|              |            |                                         |                                                               |                                                                                                  | FFFF5B2                                          |                                                             |                                              | -                                             |   |

|              |            |                                         |                                                               |                                                                                                  | FFFFF5D2                                         |                                                             |                                              |                                               |   |

|              |            |                                         |                                                               |                                                                                                  |                                                  | ,                                                           |                                              |                                               |   |

|              | 7          | 6                                       | 5                                                             | 4                                                                                                | 3                                                | <2>                                                         | 1                                            | <0>                                           | I |

| TPnIOC0      | 0          | 0                                       | 0                                                             | 0                                                                                                | TPnOL1                                           | TPnOE1                                                      | TPnOL0                                       | TPnOE0                                        |   |

| (n = 0 to 5) | r          | 1                                       |                                                               |                                                                                                  |                                                  |                                                             |                                              |                                               | I |

|              | TPnOL1     |                                         |                                                               | TOPn1 pin                                                                                        | output leve                                      | el setting <sup>Not</sup>                                   | e                                            |                                               |   |

|              | 0          | TOPn1                                   | pin output                                                    | starts at hig                                                                                    | h level                                          |                                                             |                                              |                                               |   |

|              | 1          | TOPn1                                   | pin output :                                                  | starts at low                                                                                    | level                                            |                                                             |                                              |                                               |   |

|              |            |                                         |                                                               | TOD                                                                                              |                                                  |                                                             |                                              |                                               | 1 |

|              | TPnOE1     |                                         |                                                               |                                                                                                  | l pin output                                     | setting                                                     |                                              |                                               |   |

|              | 0          | • When <sup>-</sup>                     |                                                               | ed<br>t = 0: Low le<br>t = 1: High le                                                            |                                                  |                                                             |                                              |                                               |   |

|              | 1          |                                         |                                                               | ed (a square                                                                                     |                                                  |                                                             | -                                            |                                               |   |

|              |            |                                         | -                                                             |                                                                                                  |                                                  | -                                                           |                                              |                                               |   |

|              | TPnOL0     |                                         |                                                               | TOPn0 pin                                                                                        | output leve                                      | el setting <sup>Not</sup>                                   | e                                            |                                               |   |

|              | 0          | TOPn0                                   | pin output                                                    | starts at hig                                                                                    | h level                                          |                                                             |                                              |                                               |   |

|              | 1          | TOPn0                                   | pin output :                                                  | starts at low                                                                                    | level                                            |                                                             |                                              |                                               |   |

|              |            |                                         |                                                               |                                                                                                  |                                                  |                                                             |                                              |                                               |   |

|              | TPnOE0     |                                         |                                                               | TOPn                                                                                             | ) pin output                                     | setting                                                     |                                              |                                               |   |

|              | 0          | When <sup>-</sup>                       |                                                               | ed<br>t = 0: Low le<br>t = 1: High le                                                            |                                                  |                                                             |                                              |                                               |   |

|              | 1          | Timer ou                                | utput enable                                                  | ed (a square                                                                                     | e wave is o                                      | utput from                                                  | the TOPn0                                    | ) pin).                                       |   |

|              | TF<br>• Wh | PnOLm bi<br>en TPnOL<br>16-bit c<br>TPn | t is showr<br>.m bit = 0                                      | the timer                                                                                        | = 0, 1).<br>• When                               | n (TOPnn<br>TPnOLm b<br>16-bit coun<br>TPnCE<br>nm output ; | bit = 1<br>Iter                              | ed by the                                     |   |

|              | Cautions   | whe<br>writ<br>set<br>2. Eve<br>and     | n the TPr<br>ten whe<br>takenly p<br>the bits a<br>n if the 1 | TPnOL1, <sup>-</sup><br>nCTL0.TP<br>n the TF<br>performed,<br>gain.<br>rPnOLm to<br>n bits are ( | nCE bit =<br>PnCE bit<br>clear the<br>pit is mar | 0. (The s<br>= 1.)<br>e TPnCE                               | same valu<br>If rewri<br>bit to 0<br>when th | ue can be<br>ting was<br>and then<br>ne TPnCE |   |

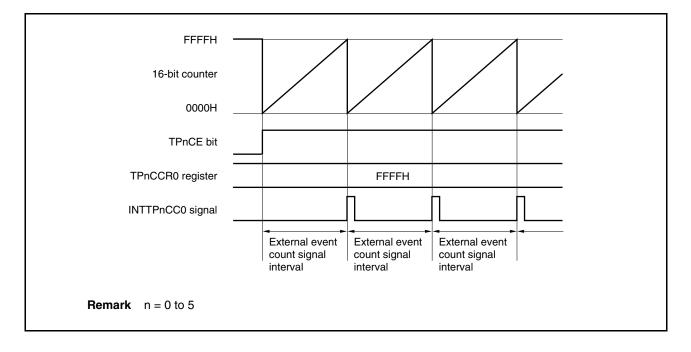

## (2) Operation timing in external event count mode

Cautions 1. In the external event count mode, do not set the TPnCCR0 register to 0000H.

In the external event count mode, use of the timer output is disabled. If performing timer output using external event count input, set the interval timer mode, and select the operation enabled by the external event count input for the count clock (TPnCTL1.TPnMD2 to TPnCTL1.TPnMD0 bits = 000, TPnCTL1.TPnEEE bit = 1).

#### (a) Operation if TPnCCR0 register is set to FFFFH

If the TPnCCR0 register is set to FFFFH, the 16-bit counter counts to FFFFH each time the valid edge of the external event count signal has been detected. The 16-bit counter is cleared to 0000H in synchronization with the next count-up timing, and the INTTPnCC0 signal is generated. At this time, the TPnOPT0.TPnOVF bit is not set.

#### (c) Generation timing of compare match interrupt request signal (INTTPnCC1)

The timing of generation of the INTTPnCC1 signal in the PWM output mode differs from the timing of other INTTPnCC1 signals; the INTTPnCC1 signal is generated when the count value of the 16-bit counter matches the value of the TPnCCR1 register.

| Count clock                |                                |

|----------------------------|--------------------------------|

| 16-bit counter             | D1 - 2 D1 - 1 D1 D1 + 1 D1 + 2 |

| TPnCCR1 register           | D1                             |

| TOPn1 pin output           |                                |

| INTTPnCC1 signal           |                                |

| <b>Remark</b> $n = 0$ to 5 | 5                              |

Usually, the INTTPnCC1 signal is generated in synchronization with the next counting up after the count value of the 16-bit counter matches the value of the TPnCCR1 register.

In the PWM output mode, however, it is generated one clock earlier. This is because the timing is changed to match the change timing of the output signal of the TOPn1 pin.

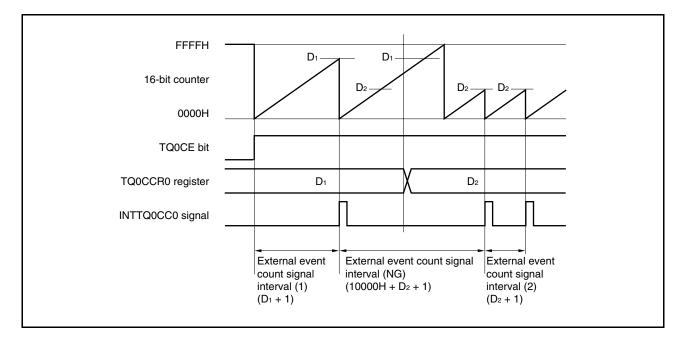

#### (b) Notes on rewriting the TQ0CCR0 register

To change the value of the TQ0CCR0 register to a smaller value, stop counting once and then change the set value.

If the value of the TQ0CCR0 register is rewritten to a smaller value during counting, the 16-bit counter may overflow.

If the value of the TQ0CCR0 register is changed from  $D_1$  to  $D_2$  while the count value is greater than  $D_2$  but less than  $D_1$ , the count value is transferred to the CCR0 buffer register as soon as the TQ0CCR0 register has been rewritten. Consequently, the value that is compared with the 16-bit counter is  $D_2$ .

Because the count value has already exceeded  $D_2$ , however, the 16-bit counter counts up to FFFFH, overflows, and then counts up again from 0000H. When the count value matches  $D_2$ , the INTTQ0CC0 signal is generated. Therefore, the INTTQ0CC0 signal may not be generated at the valid edge count of "( $D_1 + 1$ ) times" or "( $D_2 + 1$ ) times" originally expected, but may be generated at the valid edge count of "( $10000H + D_2 + 1$ ) times".

#### (b) 0%/100% output of PWM waveform

To output a 0% waveform, set the TQ0CCRk register to 0000H. If the set value of the TQ0CCR0 register is FFFFH, the INTTQ0CCk signal is generated periodically.

| Count clock      |          | $D_0 - 1$ $D_0$ 0000 |          | $\begin{array}{c c} & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & &$ | x 0000 x |

|------------------|----------|----------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| TQ0CE bit        |          |                      | <u> </u> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u>/</u> |

| TQ0CCR0 register | Do       | Do                   |          | Do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| TQ0CCRk register | 0000H    | 0000H                |          | 0000H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| INTTQ0CC0 signal | ,<br>    | ,                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| INTTQ0CCk signal |          | ,                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| TOQ0k pin output | <u> </u> | <u>}</u>             |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| Remark k =       | = 1 to 3 |                      |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

To output a 100% waveform, set a value of (set value of TQ0CCR0 register + 1) to the TQ0CCRk register. If the set value of the TQ0CCR0 register is FFFFH, 100% output cannot be produced.

| Count clock       |          |                                                                    |                                       |                                                            |          |

|-------------------|----------|--------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------|----------|

| 16-bit counter    |          | $\sum_{i=1}^{2^{n}} \sum_{i=1}^{n} D_{0} - 1 \sum_{i=1}^{n} D_{0}$ | X 0000 X 0001 X                       | $\sum_{i=1}^{n} \sum_{i=1}^{n} D_0 - 1 \sum_{i=1}^{n} D_0$ | X 0000 X |

| TQ0CE bit         |          | ))                                                                 |                                       | ) <del>)</del>                                             |          |

| TQ0CCR0 register  |          | »)                                                                 | Do                                    | Do                                                         |          |

| TQ0CCRk register  | Do + 1   | ;;                                                                 | Do + 1                                | Do + 1                                                     |          |

| INTTQ0CC0 signal  |          | 5                                                                  |                                       | · <del>·</del>                                             |          |

| INTTQ0CCk signal  |          | <u>ې</u>                                                           |                                       | · <del>/</del>                                             |          |

| TOQ0k pin output  |          | )                                                                  | · · · · · · · · · · · · · · · · · · · | <del>}</del>                                               |          |

| <b>Remark</b> k = | = 1 to 3 |                                                                    |                                       |                                                            |          |

#### (e) Generation timing of compare match interrupt request signal (INTTQ0CCk)

The timing of generation of the INTTQ0CCk signal in the external trigger pulse output mode differs from the timing of other INTTQ0CCk signals; the INTTQ0CCk signal is generated when the count value of the 16-bit counter matches the value of the CCRk buffer register.

| Count clock            |                                                                |

|------------------------|----------------------------------------------------------------|

| 16-bit counter         | Dk - 2         Dk - 1         Dk         Dk + 1         Dk + 2 |

| CCRk buffer register   | Dĸ                                                             |

| TOQ0k pin output       |                                                                |

| INTTQ0CCk signal       |                                                                |

| <b>Remark</b> k = 1 to | 3                                                              |

Usually, the INTTQ0CCk signal is generated in synchronization with the next count up after the count value of the 16-bit counter matches the value of the CCRk buffer register.

In the external trigger pulse output mode, however, it is generated one clock earlier. This is because the timing is changed to match the timing of changing the output signal of the TOQ0k pin.

#### (2) Real-time output port control register 0 (RTPC0)

The RTPC0 register is a register that sets the operation mode and output trigger of the real-time output port. The relationship between the operation mode and output trigger of the real-time output port is as shown in Tables 12-3 and 12-4.

This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00H.

| After res | et: 00H   | R/W               | Address: F            | TPC0 FFF            | FF6E5H      |              |              |            |                              |

|-----------|-----------|-------------------|-----------------------|---------------------|-------------|--------------|--------------|------------|------------------------------|

|           | <7>       | 6                 | 5                     | 4                   | 3           | 2            | 1            | 0          |                              |

| RTPC0     | RTPOE0    | RTPEG0            | BYTE0                 | EXTR0               | 0           | 0            | 0            | 0          |                              |

|           |           |                   |                       |                     |             |              |              |            | •                            |

|           | RTPOE0    |                   | С                     | ontrol of rea       | al-time out | out operati  | on           |            |                              |

|           | 0         | Disables o        | peration <sup>№</sup> | te 1                |             |              |              |            |                              |

|           | 1         | Enables o         | peration              |                     |             |              |              |            |                              |

|           |           |                   |                       |                     |             |              |              |            | 1                            |

|           | RTPEG0    |                   | Valid                 | edge of INT         | TPaCC0 (    | a = 0, 4, 5  | ) signal     |            |                              |

|           | 0         | Falling ed        | ge <sup>Note 2</sup>  |                     |             |              |              |            |                              |

|           | 1         | Rising edg        | je                    |                     |             |              |              |            |                              |

|           |           |                   |                       |                     |             |              |              |            | I                            |

|           | BYTE0     | S                 | pecificatio           | n of channe         | l configura | tion for rea | al-time outp | out        |                              |

|           | 0         | 4 bits $\times$ 1 | channel, 2            | bits $\times$ 1 cha | nnel        |              |              |            |                              |

|           | 1         | 6 bits $\times$ 1 | channel               |                     |             |              |              |            |                              |

|           | real-ti   | me output         | signals (             | RTP00 to            | RTP05) c    | output "0"   |              |            | ne bits of the<br>I by TMP0. |

| Caution   | n Set the | e RTPEG           | D, BYTEO              | , and EXT           | R0 bits o   | only whe     | n RTPOE      | 0 bit = 0. |                              |

Table 12-3. Operation Modes and Output Triggers of Real-Time Output Port

| BYTE0 | EXTR0 | Operation Mode             | RTBH0 (RTP04, RTP05) | RTBL0 (RTP00 to RTP03) |

|-------|-------|----------------------------|----------------------|------------------------|

| 0     | 0     | 4 bits $\times$ 1 channel, | INTTP5CC0            | INTTP4CC0              |

|       | 1     | 2 bits $\times$ 1 channel  | INTTP4CC0            | INTTP0CC0              |

| 1     | 0     | 6 bits $\times$ 1 channel  | INTTP4CC0            |                        |

|       | 1     |                            | INTTP0CC0            |                        |

## 14.4.3 Cautions

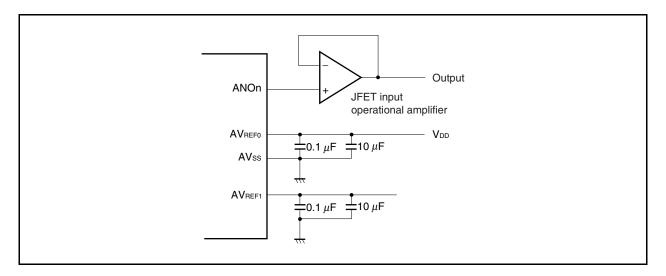

Observe the following cautions when using the D/A converter of the V850ES/JG3.

- (1) Do not change the set value of the DA0CSn register while the trigger signal is being issued in the real-time output mode.

- (2) Before changing the operation mode, be sure to clear the DA0M.DA0CEn bit to 0.

- (3) When using one of the P10/AN00 and P11/AN01 pins as an I/O port and the other as a D/A output pin, do so in an application where the port I/O level does not change during D/A output.

- (4) Make sure that AVREF0 = VDD = AVREF1 = 3.0 to 3.6 V. If this range is exceeded, the operation is not guaranteed.

- (5) Apply power to AVREF1 at the same timing as AVREF0.

- (6) No current can be output from the ANOn pin (n = 0, 1) because the output impedance of the D/A converter is high. When connecting a resistor of 2 M $\Omega$  or less, insert a JFET input operational amplifier between the resistor and the ANOn pin.

# Figure 14-2. External Pin Connection Example

(7) Because the D/A converter stops operation in the STOP mode, the ANO0 and ANO1 pins go into a high-impedance state, and the power consumption can be reduced.In the IDLE1, IDLE2, or subclock operation mode, however, the operation continues. To lower the power consumption, therefore, clear the DA0M.DA0CEn bit to 0.

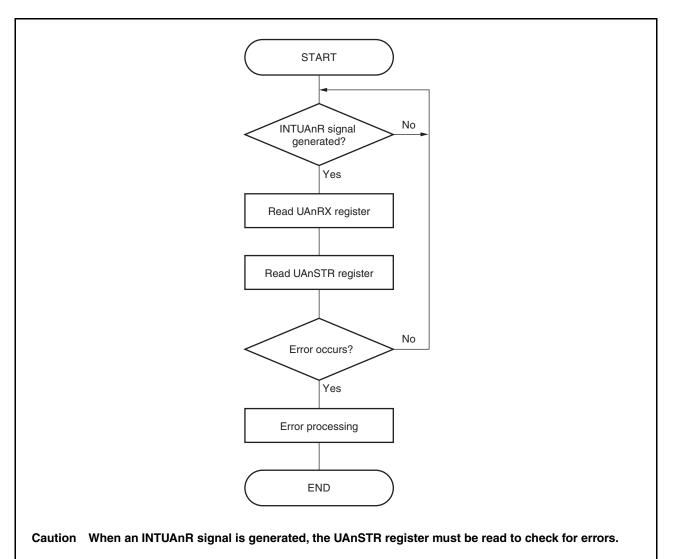

## 15.6.8 Reception errors

Errors during a receive operation are of three types: parity errors, framing errors, and overrun errors. Data reception result error flags are set in the UAnSTR register and a reception complete interrupt request signal (INTUAnR) is output when an error occurs.

It is possible to ascertain which error occurred during reception by reading the contents of the UAnSTR register. Clear the reception error flag by writing 0 to it after reading it.

· Receive data read flow

#### • Reception error causes

| Error Flag | Reception Error | Cause                                                                     |

|------------|-----------------|---------------------------------------------------------------------------|

| UAnPE      | Parity error    | Received parity bit does not match the setting                            |

| UAnFE      | Framing error   | Stop bit not detected                                                     |

| UAnOVE     | Overrun error   | Reception of next data completed before data was read from receive buffer |

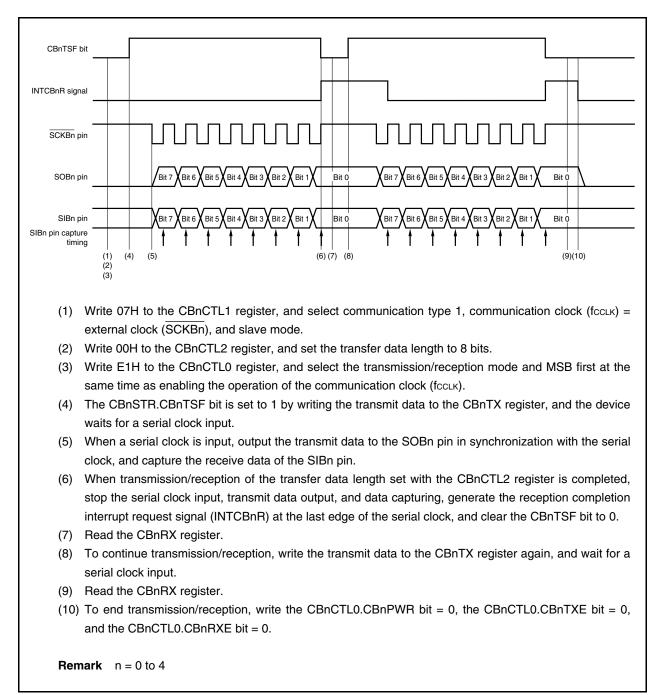

# (2) Operation timing

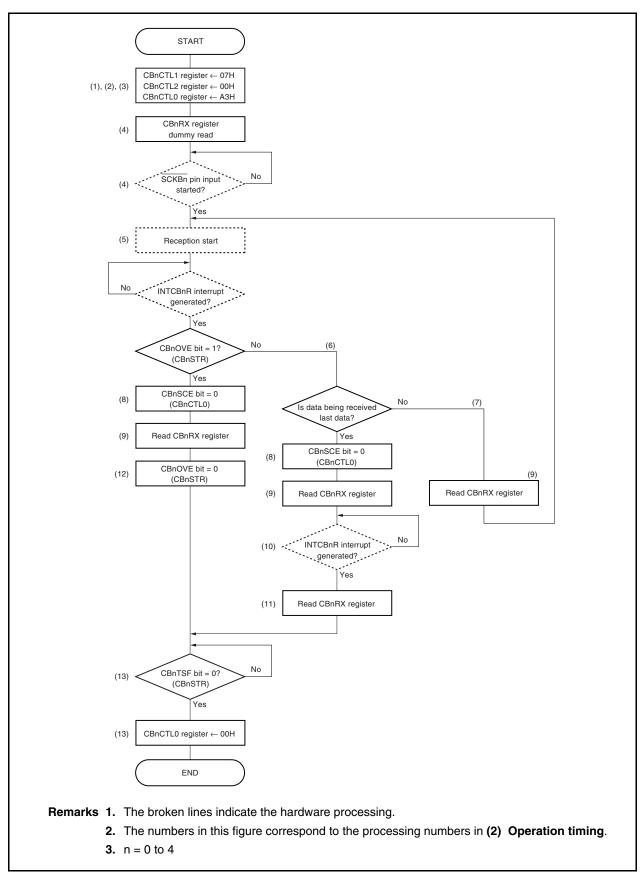

# (1) Operation flow

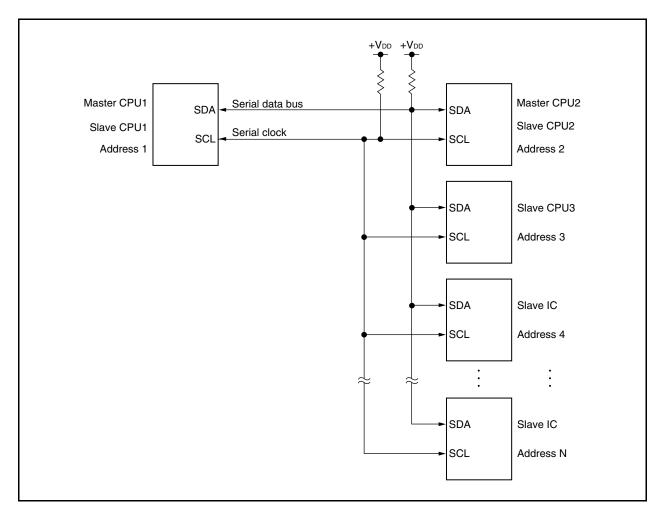

A serial bus configuration example is shown below.

Figure 17-5. Serial Bus Configuration Example Using I<sup>2</sup>C Bus

## (4) Start ~ Code ~ Data ~ Start ~ Address ~ Data ~ Stop

| <ul> <li>▲2: IICSn register = 0010X000B</li> <li>▲3: IICSn register = 00000X10B</li> <li>△ 4: IICSn register = 0000001B</li> <li>Remarks 1. ▲: Always generated</li> <li>△: Generated only when SPIEn bit = 1</li> <li>X: don't care</li> </ul> |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <ul> <li>▲3: IICSn register = 00000X10B</li> <li>△ 4: IICSn register = 0000001B</li> <li>Remarks 1. ▲: Always generated</li> <li>△: Generated only when SPIEn bit = 1</li> <li>X: don't care</li> </ul>                                         |    |

|                                                                                                                                                                                                                                                 |    |

| Remarks 1. ▲: Always generated ∆: Generated only when SPIEn bit = 1 X: don't care                                                                                                                                                               |    |

| $\Delta$ : Generated only when SPIEn bit = 1<br>X: don't care                                                                                                                                                                                   |    |

| $\Delta$ : Generated only when SPIEn bit = 1<br>X: don't care                                                                                                                                                                                   |    |

| X: don't care                                                                                                                                                                                                                                   |    |

|                                                                                                                                                                                                                                                 |    |

| <b>2.</b> $\Pi = 0.10.2$                                                                                                                                                                                                                        |    |

|                                                                                                                                                                                                                                                 |    |

| ST         AD6 to AD0         R/W         ACK         D7 to D0         ACK         ST         AD6 to AD0         R/W         ACK         D7 to D0         ACK                                                                                   | SP |

| <b>▲</b> 1 <b>▲</b> 2 <b>▲</b> 3 <b>▲</b> 4                                                                                                                                                                                                     |    |

| ▲1: IICSn register = 0010X010B                                                                                                                                                                                                                  |    |

|                                                                                                                                                                                                                                                 |    |

| ▲2: IICSn register = 0010X110B                                                                                                                                                                                                                  |    |

| <ul> <li>▲2: IICSn register = 0010X110B</li> <li>▲3: IICSn register = 0010XX00B</li> </ul>                                                                                                                                                      |    |

|                                                                                                                                                                                                                                                 |    |

| ▲3: IICSn register = 0010XX00B                                                                                                                                                                                                                  |    |

| ▲3: IICSn register = 0010XX00B<br>▲4: IICSn register = 00000X10B                                                                                                                                                                                |    |

| <ul> <li>▲3: IICSn register = 0010XX00B</li> <li>▲4: IICSn register = 00000X10B</li> <li>△ 5: IICSn register = 0000001B</li> <li>Remarks 1. ▲: Always generated</li> </ul>                                                                      |    |

| <ul> <li>▲3: IICSn register = 0010XX00B</li> <li>▲4: IICSn register = 00000X10B</li> <li>△ 5: IICSn register = 00000001B</li> </ul>                                                                                                             |    |

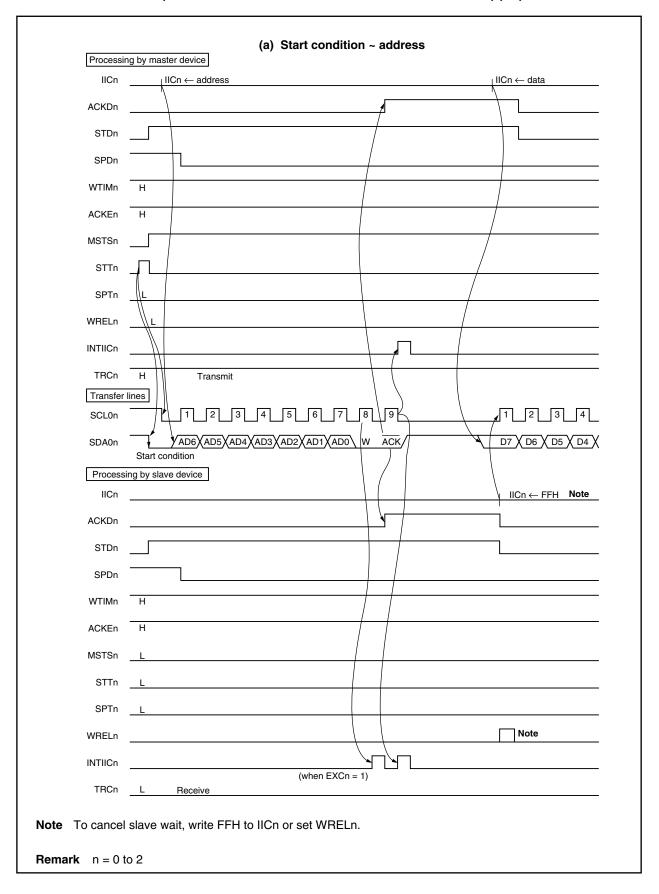

Figure 17-23. Example of Master to Slave Communication (When 9-Clock Wait Is Selected for Both Master and Slave) (1/3)

#### (5) DMA channel control registers 0 to 3 (DCHC0 to DCHC3)

The DCHC0 to DCHC3 registers are 8-bit registers that control the DMA transfer operating mode for DMA channel n.

These registers can be read or written in 8-bit or 1-bit units. (However, bit 7 is read-only and bits 1 and 2 are writeonly. If bit 1 or 2 is read, the read value is always 0.)

Reset sets these registers to 00H.

| Aller        | eset: 00H                                                     | R/W                                                           |                                             |                                            |                                       |                                              | FFFFF0E2H,<br>FFFFF0E6H                                            |                  |

|--------------|---------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------|--------------------------------------------|---------------------------------------|----------------------------------------------|--------------------------------------------------------------------|------------------|

|              | <7>                                                           | 6                                                             | 5                                           | 4                                          | 3                                     | <2>                                          | <1>                                                                | <0>              |

| DCHCn        | TCn <sup>Note 1</sup>                                         | 0                                                             | 0                                           | 0                                          | 0                                     | INITn <sup>Note</sup>                        | <sup>2</sup> STGn <sup>Note 2</sup>                                | Enn              |

| (n = 0 to 3) |                                                               |                                                               |                                             |                                            |                                       |                                              |                                                                    |                  |

|              | TCn <sup>Note 1</sup>                                         |                                                               |                                             | us flag indio<br>gh DMA ch                 |                                       |                                              |                                                                    |                  |

|              | 0                                                             | DMA tra                                                       | nsfer had no                                | ot complete                                | d.                                    |                                              |                                                                    |                  |

|              | 1                                                             | DMA tra                                                       | nsfer had co                                | ompleted.                                  |                                       |                                              |                                                                    |                  |

|              | It is set to                                                  | 1 on the                                                      | last DMA tr                                 | ansfer and                                 | cleared t                             | o 0 when it                                  | is read.                                                           |                  |

|              |                                                               | DSAnH,<br>complete<br>channel.<br>When in                     | DSAnL, DE<br>ed (before th                  | BCn, and D<br>ne TCn bit i<br>DMA contr    | ADCn reg<br>s set to 1<br>roller, how | jisters) befo<br>), be sure t<br>wever, be s | the DDAnH,<br>ore DMA trans<br>to initialize the<br>sure to observ | sfer is<br>e DMA |

|              | STGn <sup>Note 2</sup>                                        | If this bit                                                   | software st<br>is set to 1 i<br>DMA transfe | n the DMA                                  | transfer e                            |                                              | e (TCn bit = 0                                                     | , Enn            |

|              | Enn                                                           |                                                               |                                             | tting of whe<br>A channel n                |                                       |                                              | -                                                                  |                  |

|              | 0                                                             | DMA tra                                                       | nsfer disabl                                | ed                                         |                                       |                                              |                                                                    |                  |

|              | 1                                                             | DMA tra                                                       | nsfer enable                                | əd                                         |                                       |                                              |                                                                    |                  |

|              | When DM<br>automatic<br>To abort I<br>bit to 1 ag<br>When abo | IA transfe<br>ally clear<br>DMA trans<br>gain.<br>prting or r | ed to 0.<br>sfer, clear th                  | ted (when a<br>ne Enn bit t<br>MA transfer | terminal<br>0 0 by so                 | count is go<br>ftware. To                    | enerated), this<br>resume, set t<br>o observe the                  | he Enn           |

|              | nd STGn bi<br>to clear bi<br>MA transf<br>to 0 and th         | ts are w<br>ts 6 to 3<br>er is co<br>en the                   | of the D(<br>ompleted<br>FCn bit is         | (when a set to 1.                          | termir<br>If the I                    | al count<br>DCHCn re                         | t is genera<br>egister is re                                       | ead whil         |

= 0 and Enn bit = 0) may be read.

#### 19.3.3 Priorities of maskable interrupts

The INTC performs multiple interrupt servicing in which an interrupt is acknowledged while another interrupt is being serviced. Multiple interrupts can be controlled by priority levels.

There are two types of priority level control: control based on the default priority levels, and control based on the programmable priority levels that are specified by the interrupt priority level specification bit (xxPRn) of the interrupt control register (xxICn). When two or more interrupts having the same priority level specified by the xxPRn bit are generated at the same time, interrupt request signals are serviced in order depending on the priority level allocated to each interrupt request type (default priority level) beforehand. For more information, see **Table 19-1 Interrupt Source List**. The programmable priority control customizes interrupt request signals into eight levels by setting the priority level specification flag.

Note that when an interrupt request signal is acknowledged, the PSW.ID flag is automatically set to 1. Therefore, when multiple interrupts are to be used, clear the ID flag to 0 beforehand (for example, by placing the EI instruction in the interrupt service program) to set the interrupt enable mode.

# Remark xx: Identification name of each peripheral unit (see Table 19-2 Interrupt Control Register (xxICn))

n: Peripheral unit number (see Table 19-2 Interrupt Control Register (xxICn)).

| Address   | Register          | Bit               |                   |   |   |   |                     |                     |                     |  |  |

|-----------|-------------------|-------------------|-------------------|---|---|---|---------------------|---------------------|---------------------|--|--|

|           |                   | <7>               | <6>               | 5 | 4 | 3 | 2                   | 1                   | 0                   |  |  |

| FFFFF162H | UA0RIC/<br>CB4RIC | UA0RIF/<br>CB4RIF | UA0RMK/<br>CB4RMK | 0 | 0 | 0 | UA0RPR2/<br>CB4RPR2 | UA0RPR1/<br>CB4RPR1 | UA0RPR0/<br>CB4RPR0 |  |  |

| FFFF164H  | UA0TIC/<br>CB4TIC | UA0TIF/<br>CB4TIF | UA0TMK/<br>CB4TMK | 0 | 0 | 0 | UA0TPR2/<br>CB4TPR2 | UA0TPR1/<br>CB4TPR1 | UA0TPR0/<br>CB4TPR0 |  |  |

| FFFF166H  | UA1RIC/<br>IICIC2 | UA1RIF/<br>IICIF2 | UA1RMK/<br>IICMK2 | 0 | 0 | 0 | UA1RPR2/<br>IICPR22 | UA1RPR1/<br>IICPR21 | UA1RPR0/<br>IICPR20 |  |  |

| FFFFF168H | UA1TIC            | UA1TIF            | UA1TMK            | 0 | 0 | 0 | UA1TPR2             | UA1TPR1             | UA1TPR0             |  |  |

| FFFF16AH  | UA2RIC/<br>IICIC0 | UA2RIF/<br>IICIF0 | UA2RMK/<br>IICMK0 | 0 | 0 | 0 | UA2RPR2/<br>IICPR02 | UA2RPR1/<br>IICPR01 | UA2RPR0/<br>IICPR00 |  |  |

| FFFFF16CH | UA2TIC            | UA2TIF            | UA2TMK            | 0 | 0 | 0 | UA2TPR2             | UA2TPR1             | UA2TPR0             |  |  |

| FFFFF16EH | ADIC              | ADIF              | ADMK              | 0 | 0 | 0 | ADPR2               | ADPR1               | ADPR0               |  |  |

| FFFFF170H | DMAIC0            | DMAIF0            | DMAMK0            | 0 | 0 | 0 | DMAPR02             | DMAPR01             | DMAPR00             |  |  |

| FFFFF172H | DMAIC1            | DMAIF1            | DMAMK1            | 0 | 0 | 0 | DMAPR12             | DMAPR11             | DMAPR10             |  |  |

| FFFFF174H | DMAIC2            | DMAIF2            | DMAMK2            | 0 | 0 | 0 | DMAPR22             | DMAPR21             | DMAPR20             |  |  |

| FFFFF176H | DMAIC3            | DMAIF3            | DMAMK3            | 0 | 0 | 0 | DMAPR32             | DMAPR31             | DMAPR30             |  |  |

| FFFFF178H | KRIC              | KRIF              | KRMK              | 0 | 0 | 0 | KRPR2               | KRPR1               | KRPR0               |  |  |

| FFFFF17AH | WTIIC             | WTIIF             | WTIMK             | 0 | 0 | 0 | WTIPR2              | WTIPR1              | WTIPR0              |  |  |

| FFFFF17CH | WTIC              | WTIF              | WTMK              | 0 | 0 | 0 | WTPR2               | WTPR1               | WTPR0               |  |  |

Table 19-2. Interrupt Control Register (xxICn) (2/2)

# 19.3.5 Interrupt mask registers 0 to 3 (IMR0 to IMR3)

The IMR0 to IMR3 registers set the interrupt mask state for the maskable interrupts. The xxMKn bit of the IMR0 to IMR3 registers is equivalent to the xxICn.xxMKn bit.

The IMRm register can be read or written in 16-bit units (m = 0 to 3).

If the higher 8 bits of the IMRm register are used as an IMRmH register and the lower 8 bits as an IMRmL register, these registers can be read or written in 8-bit or 1-bit units (m = 0 to 3).

Reset sets these registers to FFFFH.

Caution The device file defines the xxICn.xxMKn bit as a reserved word. If a bit is manipulated using the name of xxMKn, the contents of the xxICn register, instead of the IMRm register, are rewritten (as a result, the contents of the IMRm register are also rewritten).

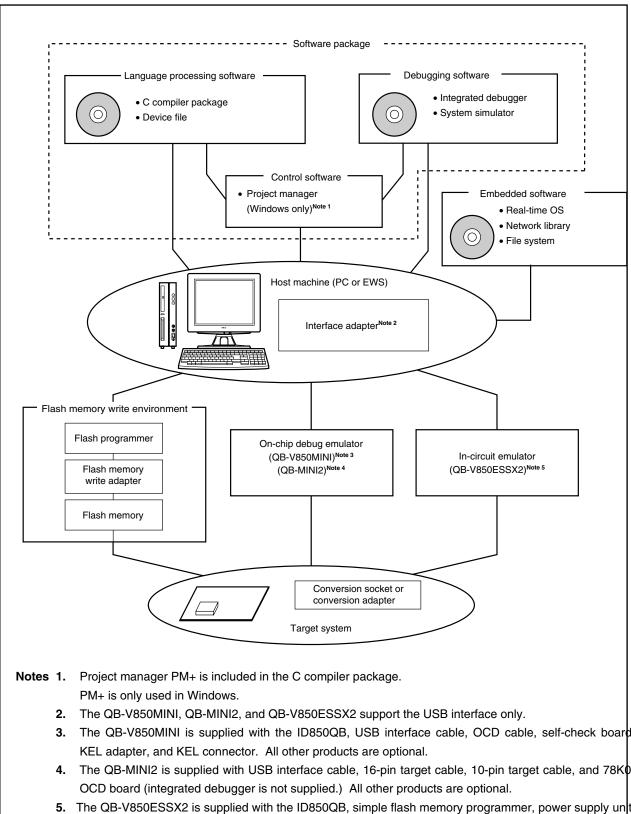

Figure A-1. Development Tool Configuration

- 3. The QB-V850MINI is supplied with the ID850QB, USB interface cable, OCD cable, self-check board,

- 4. The QB-MINI2 is supplied with USB interface cable, 16-pin target cable, 10-pin target cable, and 78K

- 5. The QB-V850ESSX2 is supplied with the ID850QB, simple flash memory programmer, power supply unit, and USB interface adapter. All other products are optional.

<u>(31/3</u>6)

| Chapter    | Classification     | Function                                | Details of<br>Function                                                                                                                                                                                                                                               | Cautions                                                                                                                                                                                                                                                                                                                                    |        |  |  |  |

|------------|--------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|

|            | Standby function   | Releasing<br>IDLE2 mode                 | The interrupt request signal that is disabled by setting the PSC.NMI1M, PSC.NMI0M, and PSC.INTM bits to 1 becomes invalid and IDLE2 mode is not released.                                                                                                            |                                                                                                                                                                                                                                                                                                                                             |        |  |  |  |

| Ö          | 0                  |                                         | STOP mode                                                                                                                                                                                                                                                            | Insert five or more NOP instructions after the instruction that stores data in the PSC register to set the STOP mode.                                                                                                                                                                                                                       |        |  |  |  |

|            |                    |                                         |                                                                                                                                                                                                                                                                      | If the STOP mode is set while an unmasked interrupt request signal is being held pending, the STOP mode is released immediately by the pending interrupt request.                                                                                                                                                                           |        |  |  |  |

|            |                    |                                         | Releasing<br>STOP mode                                                                                                                                                                                                                                               | The interrupt request that is disabled by setting the PSC.NMI1M, PSC.NMI0M, and PSC.INTM bits to 1 becomes invalid and STOP mode is not released.                                                                                                                                                                                           |        |  |  |  |

|            |                    | Subclock operation mode                 | When manipulating the CK3 bit, do not change the set values of the PCC.CK2 to PCC.CK0 bits (using a bit manipulation instruction to manipulate the bit is recommended). For details of the PCC register, see <b>6.3 (1) Processor clock control register (PCC)</b> . |                                                                                                                                                                                                                                                                                                                                             |        |  |  |  |

|            |                    |                                         | If the following conditions are not satisfied, change the CK2 to CK0 bits so that the conditions are satisfied and set the subclock operation mode.<br>Internal system clock ( $f_{CLK}$ ) > Subclock ( $f_{XT}$ = 32.768 kHz) × 4                                   | p. 689                                                                                                                                                                                                                                                                                                                                      |        |  |  |  |

|            |                    | Releasing<br>subclock<br>operation mode | When manipulating the CK3 bit, do not change the set values of the CK2 to CK0 bits (using a bit manipulation instruction to manipulate the bit is recommended). For details of the PCC register, see <b>6.3 (1) Processor clock control register (PCC)</b> .         |                                                                                                                                                                                                                                                                                                                                             |        |  |  |  |

|            |                    |                                         | Be sure to stop the PLL (PLLCTL.PLLON bit = 0) before stopping the main clock.                                                                                                                                                                                       | p. 690                                                                                                                                                                                                                                                                                                                                      |        |  |  |  |

|            |                    |                                         | When the CPU is operating on the subclock and main clock oscillation is stopped, accessing a register in which a wait occurs is disabled. If a wait is generated, it can be released only by reset (see <b>3.4.8 (2)</b> ).                                          | p. 690                                                                                                                                                                                                                                                                                                                                      |        |  |  |  |