# E. Renesas Electronics America Inc - UPD70F3742GC-UEU-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                  |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | V850ES                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 32MHz                                                                                |

| Connectivity               | CSI, EBI/EMI, I <sup>2</sup> C, UART/USART                                           |

| Peripherals                | DMA, LVD, PWM, WDT                                                                   |

| Number of I/O              | 84                                                                                   |

| Program Memory Size        | 1MB (1M x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 60K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x10b; D/A 2x8b                                                                 |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 100-LQFP                                                                             |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd70f3742gc-ueu-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

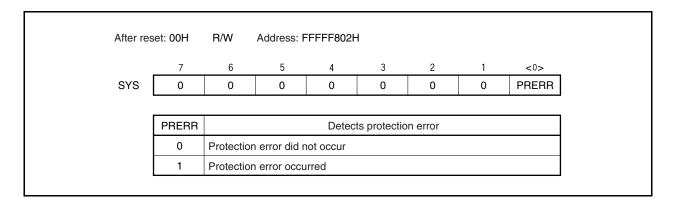

## (3) System status register (SYS)

Status flags that indicate the operation status of the overall system are allocated to this register. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00H.

The PRERR flag operates under the following conditions.

- (a) Set condition (PRERR flag = 1)

- (i) When data is written to a special register without writing anything to the PRCMD register (when <4> is executed without executing <3> in 3.4.7 (1) Setting data to special registers)

- (ii) When data is written to an on-chip peripheral I/O register other than a special register (including execution of a bit manipulation instruction) after writing data to the PRCMD register (if <4> in 3.4.7 (1) Setting data to special registers is not the setting of a special register)

- **Remark** Even if an on-chip peripheral I/O register is read (except by a bit manipulation instruction) between an operation to write the PRCMD register and an operation to write a special register, the PRERR flag is not set, and the set data can be written to the special register.

#### (b) Clear condition (PRERR flag = 0)

- (i) When 0 is written to the PRERR flag

- (ii) When the system is reset

- Cautions 1. If 0 is written to the PRERR bit of the SYS register, which is not a special register, immediately after a write access to the PRCMD register, the PRERR bit is cleared to 0 (the write access takes precedence).

- 2. If data is written to the PRCMD register, which is not a special register, immediately after a write access to the PRCMD register, the PRERR bit is set to 1.

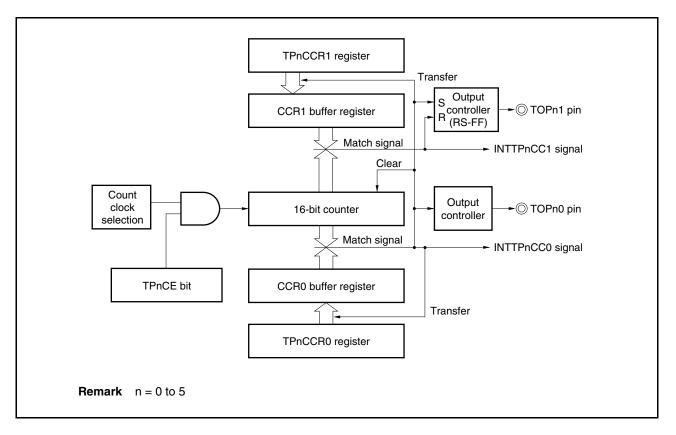

# 7.5.5 PWM output mode (TPnMD2 to TPnMD0 bits = 100)

In the PWM output mode, a PWM waveform is output from the TOPn1 pin when the TPnCTL0.TPnCE bit is set to 1. In addition, a pulse with one cycle of the PWM waveform as half its cycle is output from the TOPn0 pin.

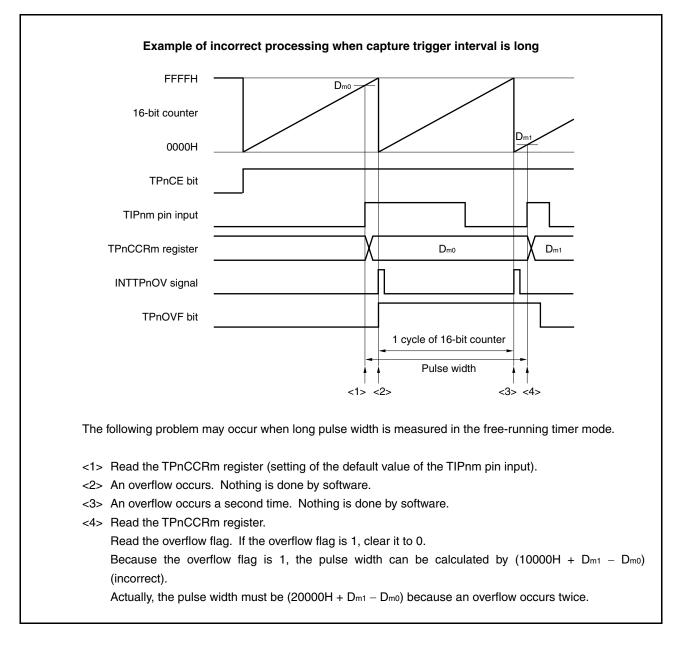

#### (d) Processing of overflow if capture trigger interval is long

If the pulse width is greater than one cycle of the 16-bit counter, care must be exercised because an overflow may occur more than once from the first capture trigger to the next. First, an example of incorrect processing is shown below.

If an overflow occurs twice or more when the capture trigger interval is long, the correct pulse width may not be obtained.

If the capture trigger interval is long, slow the count clock to lengthen one cycle of the 16-bit counter, or use software. An example of how to use software is shown next.

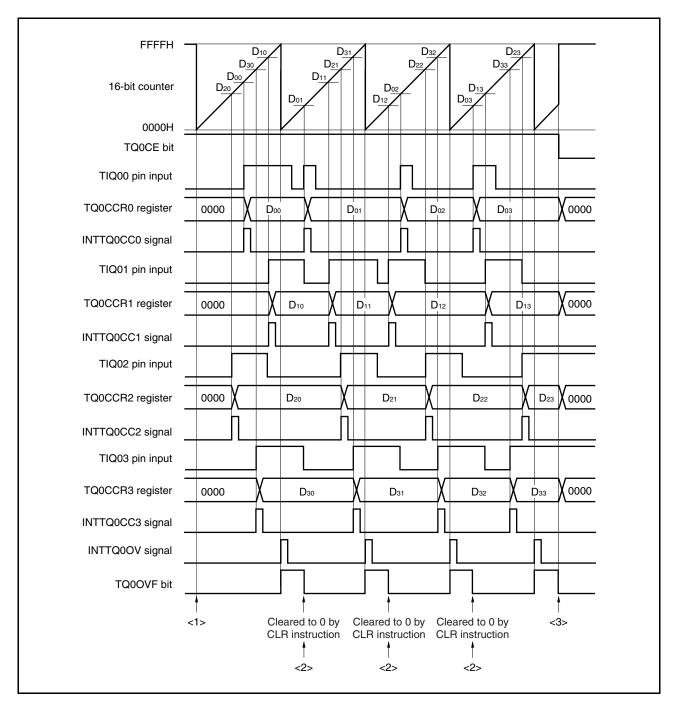

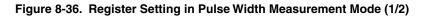

# (6) TMQ0 option register 0 (TQ0OPT0)

The TQ0OPT0 register is an 8-bit register used to set the capture/compare operation and detect an overflow. This register can be read or written in 8-bit or 1-bit units. Reset sets this register to 00H.

| After reset: 00H                                 |                                                                               | Address:                                                               | FFFFF545                                                                                                   |                                                        | _                                                     |                                                |                                                      |  |

|--------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|------------------------------------------------|------------------------------------------------------|--|

|                                                  | 6<br>3 TQ0CCS2                                                                | 5<br>TQ0CCS1                                                           | 4<br>TQ0CCS0                                                                                               | 3                                                      | 2                                                     | 1                                              | <0><br>TQ0OVF                                        |  |

|                                                  |                                                                               | 1                                                                      |                                                                                                            | -                                                      |                                                       |                                                |                                                      |  |

| TQ0CCSr                                          | TQ0CCSm TQ0CCRm register capture/compare selection                            |                                                                        |                                                                                                            |                                                        |                                                       |                                                |                                                      |  |

| 0                                                | Compare                                                                       | register se                                                            | elected                                                                                                    |                                                        |                                                       |                                                |                                                      |  |

| 1                                                | Capture                                                                       | register sel                                                           | ected                                                                                                      |                                                        |                                                       |                                                |                                                      |  |

| The TC                                           | 0CCSm bit                                                                     | setting is v                                                           | alid only in th                                                                                            | e free-ru                                              | nning timer                                           | r mode.                                        |                                                      |  |

|                                                  |                                                                               |                                                                        |                                                                                                            |                                                        |                                                       |                                                |                                                      |  |

| тс                                               | 00VF                                                                          |                                                                        | TMQ0 ov                                                                                                    | verflow d                                              | etection                                              |                                                |                                                      |  |

| Set (1)                                          | Set (1)                                                                       |                                                                        | Overflow occurred                                                                                          |                                                        |                                                       |                                                |                                                      |  |

| Reset (                                          | 0)<br>Q0OVF bit i                                                             | TQ00VF bit 0 written or TQ0CTL0.TQ0CE bit = 0                          |                                                                                                            |                                                        |                                                       |                                                |                                                      |  |

| TQ00<br>than th<br>• The T<br>registe<br>• The T | VF bit is set<br>the free-runn<br>QOOVF bit i<br>er are read v<br>QOOVF bit o | to 1. The<br>ing timer m<br>s not cleare<br>when the T(<br>can be both | NTTQ0OV) is<br>INTTQ0OV s<br>node and the<br>ed even wher<br>Q0OVF bit =<br>n read and wr<br>as no influen | ignal is r<br>pulse wid<br>the TQ(<br>1.<br>itten, but | ot generate<br>oth measure<br>OOVF bit or<br>the TQ0O | ed in moc<br>ement mo<br>the TQ0<br>VF bit car | les other<br>ode.<br>OPT0<br>nnot be set             |  |

| Caution                                          | TQ0<br>whe                                                                    | CTL0.TQ0<br>n the TG<br>ormed, cl                                      | DCE bit = 0<br>DCE bit =                                                                                   | . (The<br>1.) If                                       | same val                                              | lue can<br>g was                               | when the<br>be written<br>mistakenly<br>set the bits |  |

pin. If the trigger is generated again while the counter is operating, the counter is cleared to 0000H and restarted. (The output of the TOQ00 pin is inverted. The TOQ0k pin outputs a high-level regardless of the status (high/low) when a trigger is generated.)

The active level width, cycle, and duty factor of the PWM waveform can be calculated as follows.

Active level width = (Set value of TQ0CCRk register) × Count clock cycle Cycle = (Set value of TQ0CCR0 register + 1) × Count clock cycle Duty factor = (Set value of TQ0CCRk register)/(Set value of TQ0CCR0 register + 1)

The compare match request signal INTTQ0CC0 is generated when the 16-bit counter counts next time after its count value matches the value of the CCR0 buffer register, and the 16-bit counter is cleared to 0000H. The compare match interrupt request signal INTTQ0CCk is generated when the count value of the 16-bit counter matches the value of the CCRk buffer register.

The value set to the TQ0CCRm register is transferred to the CCRm buffer register when the count value of the 16-bit counter matches the value of the CCR0 buffer register and the 16-bit counter is cleared to 0000H.

The valid edge of an external trigger input signal, or setting the software trigger (TQ0CTL1.TQ0EST bit) to 1 is used as the trigger.

**Remark** k = 1 to 3, m = 0 to 3

#### Figure 8-18. Register Setting for Operation in External Trigger Pulse Output Mode (1/3)

| (a) T   | MQ0 con | trol regis | ster 0 (TQ | 0CTL0) |   |         |         |        |                                        |

|---------|---------|------------|------------|--------|---|---------|---------|--------|----------------------------------------|

|         | TQ0CE   |            |            |        |   | TQ0CKS2 | TQ0CKS1 | TQOCKS | 0                                      |

| TQ0CTL0 | 0/1     | 0          | 0          | 0      | 0 | 0/1     | 0/1     | 0/1    |                                        |

|         |         |            |            |        |   |         |         |        |                                        |

|         |         |            |            |        |   |         |         |        | - Select count clock                   |

|         |         |            |            |        |   |         |         |        | 0: Stop counting<br>1: Enable counting |

## (b) When using capture/compare register as capture register

#### Figure 8-33. Software Processing Flow in Free-Running Timer Mode (Capture Function) (1/2)

### (2) Prescaler compare register 0 (PRSCM0)

The PRSCM0 register is an 8-bit compare register. This register can be read or written in 8-bit units. Reset sets this register to 00H.

| After res                                                                        | set: 00H          | R/W        | Address: F             | FFFF8B1H       | 4                     |          |         |           |           |

|----------------------------------------------------------------------------------|-------------------|------------|------------------------|----------------|-----------------------|----------|---------|-----------|-----------|

|                                                                                  | 7                 | 6          | 5                      | 4              | 3                     | 2        | 1       | 0         |           |

| PRSCM0                                                                           | PRSCM07           | PRSCM06    | PRSCM05                | PRSCM04        | PRSCM03               | PRSCM02  | PRSCM01 | PRSCM00   |           |

| <ol> <li>Do not i</li> <li>Set the</li> <li>Set the</li> <li>so as to</li> </ol> | PRSCM0<br>PRSM0 a | register b | pefore se<br>M0 regist | tting the last | PRSM0.B<br>rding to t | GCE0 bit | to 1.   | quency th | at is use |

The calculation for fBRG is shown below.

$f_{BRG} = f_{BGCS}/2N$

Remark fBGCS: Watch timer source clock set by the PRSM0 register

N: Set value of PRSCM0 register = 1 to 256 However, N = 256 only when PRSCM0 register is set to 00H.

# 11.3 Registers

#### (1) Watchdog timer mode register 2 (WDTM2)

The WDTM2 register sets the overflow time and operation clock of watchdog timer 2.

This register can be read or written in 8-bit units. This register can be read any number of times, but it can be written only once following reset release.

Reset sets this register to 67H.

- Caution Accessing the WDTM2 register is prohibited in the following statuses. For details, see 3.4.8 (2) Accessing specific on-chip peripheral I/O registers.

- When the CPU operates with the subclock and the main clock oscillation is stopped

- When the CPU operates with the internal oscillation clock

|                                                                                              | set: 67H                                                                                      | R/W                                                                                             | Address: F                                                                            | FFFF6D0H                                                                                       | 4                                                                                     |                                                                               |                                                                  |                                                                                                                         |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|                                                                                              | 7                                                                                             | 6                                                                                               | 5                                                                                     | 4                                                                                              | 3                                                                                     | 2                                                                             | 1                                                                | 0                                                                                                                       |

| WDTM2                                                                                        | 0                                                                                             | WDM21                                                                                           | WDM20                                                                                 | WDCS24                                                                                         | WDCS23                                                                                | WDCS22                                                                        | WDCS21                                                           | WDCS20                                                                                                                  |

|                                                                                              |                                                                                               |                                                                                                 |                                                                                       |                                                                                                |                                                                                       |                                                                               |                                                                  |                                                                                                                         |

|                                                                                              | WDM21         WDM20         Selection of operation mode of watchdog timer 2                   |                                                                                                 |                                                                                       |                                                                                                |                                                                                       |                                                                               |                                                                  | r 2                                                                                                                     |

|                                                                                              | 0                                                                                             | 0                                                                                               | Stops ope                                                                             | eration                                                                                        |                                                                                       |                                                                               |                                                                  |                                                                                                                         |

|                                                                                              | 0 1 Non-maskable interrupt request mode<br>(generation of INTWDT2 signal)                     |                                                                                                 |                                                                                       |                                                                                                |                                                                                       |                                                                               |                                                                  |                                                                                                                         |

|                                                                                              | 1                                                                                             | _                                                                                               | Reset mo                                                                              | de (genera                                                                                     | tion of WD                                                                            | T2RES sig                                                                     | nal)                                                             |                                                                                                                         |

| oscillat<br>of the n<br>3. If the<br>generat<br>4. To inter<br>or write<br>Howeve<br>generat | or, clear<br>nain cloc<br>WDTM2<br>ted and th<br>ntionally<br>a value<br>er, when<br>ted even | the WDT<br>k or subc<br>register<br>ne counte<br>generate<br>other tha<br>watchdo<br>if data is | M2 regist<br>clock due<br>is rewrit<br>er is reset<br>an overf<br>n "ACH"<br>og timer | ter to 00H<br>to an erro<br>ten twice<br>t.<br>low signa<br>to the WE<br>2 is set<br>to the WE | I to secu<br>oneous v<br>e after r<br>al, write c<br>DTE regis<br>to stop<br>DTM2 reg | rely stop<br>write oper<br>reset, an<br>lata to th<br>ster only o<br>operatio | the time<br>ation).<br>overflow<br>e WDTM2<br>once.<br>n, an ove | ration of the inte<br>r (to avoid selec<br>v signal is for<br>Pregister only tw<br>erflow signal is<br>or a value other |

# 11.4 Operation

Watchdog timer 2 automatically starts in the reset mode following reset release.

The WDTM2 register can be written to only once following reset using byte access. To use watchdog timer 2, write the operation mode and the interval time to the WDTM2 register using an 8-bit memory manipulation instruction. After this, the operation of watchdog timer 2 cannot be stopped.

The WDCS24 to WDCS20 bits of the WDTM2 register are used to select the watchdog timer 2 loop detection time interval.

Writing ACH to the WDTE register clears the counter of watchdog timer 2 and starts the count operation again. After the count operation has started, write ACH to WDTE within the loop detection time interval.

If the time interval expires without ACH being written to the WDTE register, a reset signal (WDT2RES) or a nonmaskable interrupt request signal (INTWDT2) is generated, depending on the set values of the WDM21 and WDTM2.WDM20 bits.

When the WDTM2.WDM21 bit is set to 1 (reset mode), if a WDT overflow occurs during oscillation stabilization after a reset or standby is released, no internal reset will occur and the CPU clock will switch to the internal oscillation clock.

To not use watchdog timer 2, write 00H to the WDTM2 register.

For the non-maskable interrupt servicing while the non-maskable interrupt request mode is set, see **19.2.2 (2)** From **INTWDT2 signal**.

# CHAPTER 12 REAL-TIME OUTPUT FUNCTION (RTO)

#### 12.1 Function

The real-time output function transfers preset data to the RTBL0 and RTBH0 registers, and then transfers this data by hardware to an external device via the output latches, upon occurrence of a timer interrupt. The pins through which the data is output to an external device constitute a port called the real-time output function (RTO).

Because RTO can output signals without jitter, it is suitable for controlling a stepper motor.

In the V850ES/JG3, one 6-bit real-time output port channel is provided.

The real-time output port can be set to the port mode or real-time output port mode in 1-bit units.

# 13.5 Operation

#### 13.5.1 Basic operation

- <1> Set the operation mode, trigger mode, and conversion time for executing A/D conversion by using the ADA0M0, ADA0M1, ADA0M2, and ADA0S registers. When the ADA0CE bit of the ADA0M0 register is set, conversion is started in the software trigger mode and the A/D converter waits for a trigger in the external or timer trigger mode.

- <2> When A/D conversion is started, the voltage input to the selected analog input channel is sampled by the sample & hold circuit.

- <3> When the sample & hold circuit samples the input channel for a specific time, it enters the hold status, and holds the input analog voltage until A/D conversion is complete.

- <4> Set bit 9 of the successive approximation register (SAR) to set the compare voltage generation DAC to (1/2) AV<sub>REF0</sub>.

- <5> The voltage difference between the voltage of the compare voltage generation DAC and the analog input voltage is compared by the voltage comparator. If the analog input voltage is higher than (1/2) AVREF0, the MSB of the SAR register remains set. If it is lower than (1/2) AVREF0, the MSB is reset.

- <6> Next, bit 8 of the SAR register is automatically set and the next comparison is started. Depending on the value of bit 9, to which a result has been already set, the compare voltage generation DAC is selected as follows.

Bit 9 = 1: (3/4) AVREF0

• Bit 9 = 0: (1/4) AVREF0

This compare voltage and the analog input voltage are compared and, depending on the result, bit 8 is manipulated as follows.

Analog input voltage  $\geq$  Compare voltage: Bit 8 = 1 Analog input voltage  $\leq$  Compare voltage: Bit 8 = 0

- <7> This comparison is continued to bit 0 of the SAR register.

- <8> When comparison of the 10 bits is complete, the valid digital result is stored in the SAR register, which is then transferred to and stored in the ADA0CRn register. After that, an A/D conversion end interrupt request signal (INTAD) is generated.

- <9> In one-shot select mode, conversion is stopped<sup>Note</sup>. In one-shot scan mode, conversion is stopped after scanning once<sup>Note</sup>. In continuous select mode, repeat steps <2> to <8> until the ADA0M0.ADA0CE bit is cleared to 0. In continuous scan mode, repeat steps <2> to <8> for each channel.

- **Note** In the external trigger mode, timer trigger mode 0, or timer trigger mode 1, the trigger standby status is entered.

**Remark** The trigger standby status means the status after the stabilization time has passed.

# 15.2 Features

- Transfer rate: 300 bps to 625 kbps (using internal system clock of 32 MHz and dedicated baud rate generator)

- Full-duplex communication: Internal UARTAn receive data register (UAnRX)

Internal UARTAn transmit data register (UAnTX)

- $\bigcirc$  2-pin configuration: TXDAn: Transmit data output pin

- RXDAn: Receive data input pin

$\bigcirc$  Reception error output function

- Parity error

- Framing error

- Overrun error

- Interrupt sources: 2

- Reception complete interrupt (INTUAnR):

This interrupt occurs upon transfer of receive data from the receive shift register to receive data register after serial transfer completion, in the reception enabled status.

Transmission enable interrupt (INTUAnT):

This interrupt occurs upon transfer of transmit data from the transmit data register to the transmit shift register in the transmission enabled status.

- Character length: 7, 8 bits

- Parity function: Odd, even, 0, none

- Transmission stop bit: 1, 2 bits

- On-chip dedicated baud rate generator

- MSB-/LSB-first transfer selectable

- Transmit/receive data inverted input/output possible

- SBF (Sync Break Field) transmission/reception in the LIN (Local Interconnect Network) communication format possible

- 13 to 20 bits selectable for SBF transmission

- Recognition of 11 bits or more possible for SBF reception

- SBF reception flag provided

**Remark** n = 0 to 2

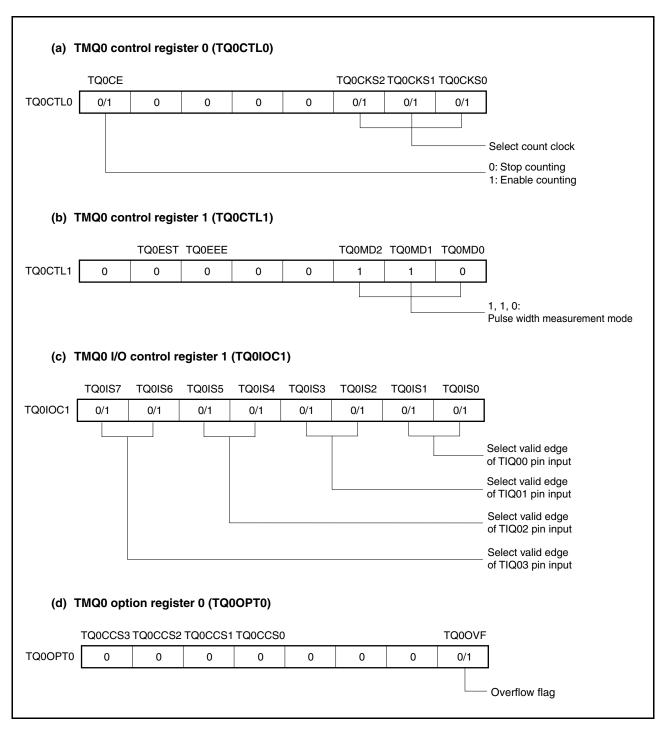

#### 15.6.7 UART reception

The reception wait status is set by setting the UAnCTL0.UAnPWR bit to 1 and then setting the UAnCTL0.UAnRXE bit to 1. In the reception wait status, the RXDAn pin is monitored and start bit detection is performed.

Start bit detection is performed using a two-step detection routine.

First the rising edge of the RXDAn pin is detected and sampling is started at the falling edge. The start bit is recognized if the RXDAn pin is low level at the start bit sampling point. After a start bit has been recognized, the receive operation starts, and serial data is saved to the UARTAn receive shift register according to the set baud rate.

When the reception complete interrupt request signal (INTUAnR) is output upon reception of the stop bit, the data of the UARTAn receive shift register is written to the UAnRX register. However, if an overrun error (UAnSTR.UAnOVE bit) occurs, the receive data at this time is not written to the UAnRX register and is discarded.

Even if a parity error (UAnSTR.UAnPE bit) or a framing error (UAnSTR.UAnFE bit) occurs during reception, reception continues until the reception position of the first stop bit, and INTUAnR is output following reception completion.

Figure 15-13. UART Reception

- Cautions 1. Be sure to read the UAnRX register even when a reception error occurs. If the UAnRX register is not read, an overrun error occurs during reception of the next data, and reception errors continue occurring indefinitely.

- 2. The operation during reception is performed assuming that there is only one stop bit. A second stop bit is ignored.

- 3. When reception is completed, read the UAnRX register after the reception complete interrupt request signal (INTUAnR) has been generated, and clear the UAnPWR or UAnRXE bit to 0. If the UAnPWR or UAnRXE bit is cleared to 0 before the INTUAnR signal is generated, the read value of the UAnRX register cannot be guaranteed.

- 4. If receive completion processing (INTUAnR signal generation) of UARTAn and the UAnPWR bit = 0 or UAnRXE bit = 0 conflict, the INTUAnR signal may be generated in spite of these being no data stored in the UAnRX register.

To complete reception without waiting INTUAnR signal generation, be sure to clear (0) the interrupt request flag (UAnRIF) of the UAnRIC register, after setting (1) the interrupt mask flag (UAnRMK) of the interrupt control register (UAnRIC) and then set (1) the UAnPWR bit = 0 or UAnRXE bit = 0.

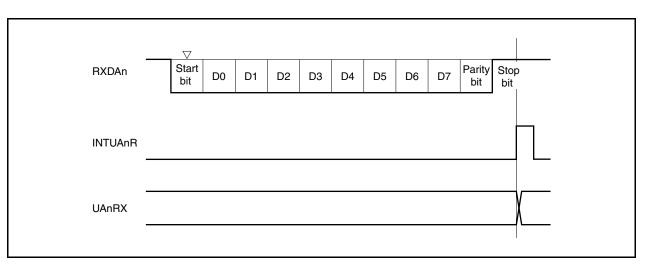

## (1) Operation flow

RENESAS

#### (5) IIC function expansion registers 0 to 2 (IICX0 to IICX2)

The IICXn register sets I<sup>2</sup>C0n function expansion (valid only in the high-speed mode).

This register can be read or written in 8-bit or 1-bit units.

Setting of the CLXn bit is performed in combination with the SMCn, CLn1, and CLn0 bits of the IICCLn register and the OCKSTHm, OCKSm1, and OCKSm0 bits of the OCKSm register (see **17.4 (6)**  $I^2$ **C0n transfer clock setting method**) (m = 0, 1).

Set the IICXn register when the IICCn.IICEn bit = 0.

Reset sets this register to 00H.

Address: IICX0 FFFFD85H, IICX1 FFFFD95H, IICX2 FFFFDA5H After reset: 00H R/W 6 5 4 3 <0> 2 1 IICXn 0 0 0 0 0 0 0 CLXn (n = 0 to 2)

#### (6) I<sup>2</sup>C0n transfer clock setting method

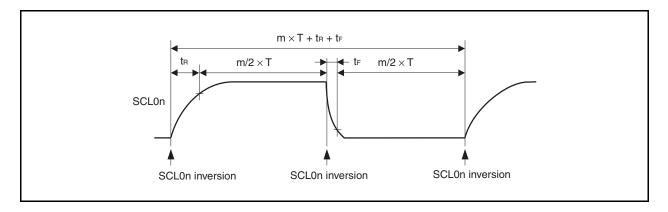

The  $l^2$ COn transfer clock frequency (fscl) is calculated using the following expression (n = 0 to 2).

$f_{SCL} = 1/(m \times T + t_R + t_F)$

m = 12, 18, 24, 36, 44, 48, 54, 60, 66, 72, 86, 88, 96, 132, 172, 176, 198, 220, 258, 344 (see Table 17-2 Clock Settings).

T: 1/fxx

- tR: SCL0n pin rise time

- tF: SCL0n pin fall time

For example, the l<sup>2</sup>C0n transfer clock frequency (fscL) when  $f_{XX} = 19.2$  MHz, m = 198,  $t_R = 200$  ns, and  $t_F = 50$  ns is calculated using following expression.

$f_{SCL} = 1/(198 \times 52 \text{ ns} + 200 \text{ ns} + 50 \text{ ns}) \cong 94.7 \text{ kHz}$

The clock to be selected can be set by the combination of the SMCn, CLn1, and CLn0 bits of the IICCLn register, the CLXn bit of the IICXn register, and the OCKSTHm, OCKSm1, and OCKSm0 bits of the OCKSm register (n = 0 to 2, m = 0, 1).

#### (b) Repeatedly execute setting INITn bit until transfer is forcibly terminated correctly

- <1> Suppress a request from the DMA request source of the channel to be forcibly terminated (stop operation of the on-chip peripheral I/O).

- <2> Check that the DMA transfer request of the channel to be forcibly terminated is not held pending, by using the DTFRn.DFn bit. If a DMA transfer request is held pending, wait until execution of the pending request is completed.

- <3> When it has been confirmed that the DMA request of the channel to be forcibly terminated is not held pending, clear the Enn bit to 0.

- <4> Again, clear the Enn bit of the channel to be forcibly terminated. If the target of transfer for the channel to be forcibly terminated (transfer source/destination) is the internal RAM, execute this operation once more.

- <5> Copy the initial number of transfers of the channel to be forcibly terminated to a general-purpose register.

- <6> Set the INITn bit of the channel to be forcibly terminated to 1.

- <7> Read the value of the DBCn register of the channel to be forcibly terminated, and compare it with the value copied in <5>. If the two values do not match, repeat operations <6> and <7>.

- Remarks 1. When the value of the DBCn register is read in <7>, the initial number of transfers is read if forced termination has been correctly completed. If not, the remaining number of transfers is read.

- **2.** Note that method (b) may take a long time if the application frequently uses DMA transfer for a channel other than the DMA channel to be forcibly terminated.

#### (5) Procedure of temporarily stopping DMA transfer (clearing Enn bit)

Stop and resume the DMA transfer under execution using the following procedure.

- <1> Suppress a transfer request from the DMA request source (stop the operation of the on-chip peripheral I/O).

- <2> Check the DMA transfer request is not held pending, by using the DFn bit (check if the DFn bit = 0). If a request is pending, wait until execution of the pending DMA transfer request is completed.

- <3> If it has been confirmed that no DMA transfer request is held pending, clear the Enn bit to 0 (this operation stops DMA transfer).

- <4> Set the Enn bit to 1 to resume DMA transfer.

- <5> Resume the operation of the DMA request source that has been stopped (start the operation of the on-chip peripheral I/O).

#### (6) Memory boundary

The operation is not guaranteed if the address of the transfer source or destination exceeds the area of the DMA target (external memory, internal RAM, or on-chip peripheral I/O) during DMA transfer.

#### (7) Transferring misaligned data

DMA transfer of misaligned data with a 16-bit bus width is not supported.

If an odd address is specified as the transfer source or destination, the least significant bit of the address is forcibly assumed to be 0.

| Pin         | Configura | ation of MINICUBE2 (QB-MINI2)                                  | With CSIB0- | -HS        | With CSIB3 | With CSIB3-HS |            | A0         |

|-------------|-----------|----------------------------------------------------------------|-------------|------------|------------|---------------|------------|------------|

| Signal Name | I/O       | Pin Function                                                   | Pin Name    | Pin<br>No. | Pin Name   | Pin<br>No.    | Pin Name   | Pin<br>No. |

| SI/RxD      | Input     | Pin to receive commands and data from V850ES/JG3               | P41/SOB0    | 23         | P911/SOB3  | 54            | P30/TXD0   | 25         |

| SO/TxD      | Output    | Pin to transmit commands and data to V850ES/JG3                | P40/SIB0    | 22         | P910/SIB3  | 53            | P31/RXD0   | 26         |

| SCK         | Output    | Clock output pin for 3-wire serial communication               | P42/SCKB0   | 24         | P912/SCKB3 | 55            | Not needed | -          |

| CLK         | Output    | Clock output pin                                               | Not needed  | -          | Not needed | _             | Not needed | -          |

| RESET_OUT   | Output    | Reset output pin to V850ES/JG3                                 | RESET       | 14         | RESET      | 14            | RESET      | 14         |

| FLMD0       | Output    | Output pin to set V850ES/JG3 to debug mode or programming mode | FLMD0       | 8          | FLMD0      | 8             | FLMD0      | 8          |

| FLMD1       | Output    | Output pin to set programming mode                             | PDL5/FLMD1  | 76         | PDL5/FLMD1 | 76            | PDL5/FLMD1 | 76         |

| HS          | Input     | Handshake signal for CSI0 + HS communication                   | PCM0/WAIT   | 61         | PCM0/WAIT  | 61            | Not needed | -          |

| GND         | -         | Ground                                                         | Vss         | 11         | Vss        | 11            | Vss        | 11         |

|             |           |                                                                | AVss        | 2          | AVss       | 2             | AVss       | 2          |

|             |           |                                                                | EVss        | 33,<br>69  | EVss       | 33,<br>69     | EVss       | 33,<br>69  |

| RESET_IN    | Input     | Reset input pin on the target system                           |             |            |            |               |            |            |

Table 28-3. Wiring Between V850ES/JG3 and MINICUBE2

## 28.2.2 Maskable functions

Only reset signals can be masked.

The maskable functions with the debugger (ID850QB) and the corresponding V850ES/JG3 functions are listed below.

| Maskable Functions with ID850QB | Corresponding V850ES/JG3 Functions         |

|---------------------------------|--------------------------------------------|

| NMIO                            | _                                          |

| NMI1                            | _                                          |

| NMI2                            | _                                          |

| STOP                            | _                                          |

| HOLD                            | _                                          |

| RESET                           | Reset signal generation by RESET pin input |

| WAIT                            | _                                          |

Table 28-4. Maskable Functions

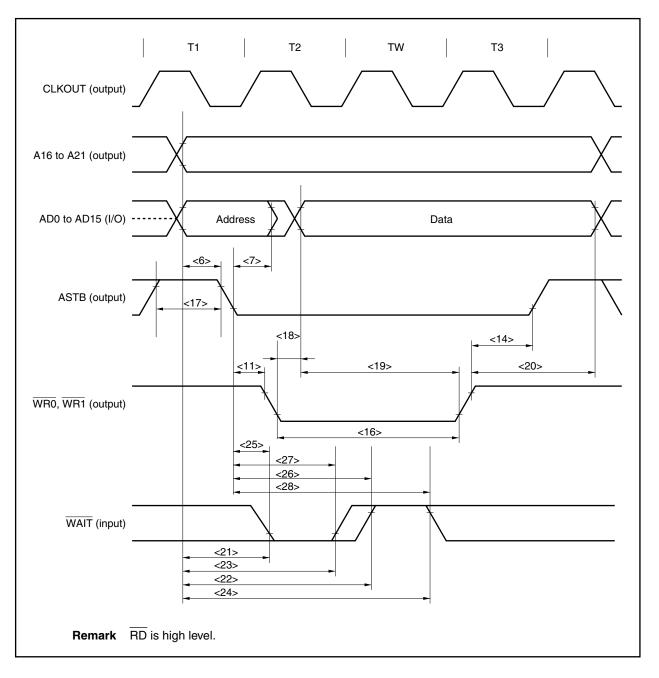

# Write Cycle (CLKOUT Asynchronous): In Multiplexed Bus Mode

### Figure A-2. System Configuration (When Using QB-V850ESSX2) (2/2)

- Notes 1. Download the device file from the Renesas Electronics website. http://www2.renesas.com/micro/ja/ods/index.html

- 2. Under development

- **3.** Supplied with the device depending on the ordering number.

- When QB-V850ESSX2-ZZZ is ordered The exchange adapter and the target connector are not supplied.

- When QB-V850ESSX2-S100GC is ordered The QB-100GC-EA-01S and QB-100GC-TC-01S are supplied.

- When QB-V850ESSX2-T100GC is ordered

- The QB-100GC-EA-01T, QB-100GC-YQ-01T, and QB-100GC-NQ-01T are supplied.

- 4. When using both <9> and <10>, the order between <9> and <10> is not cared.

| <5> QB-V850ESSX2 <sup>Note</sup><br>In-circuit emulator     | The in-circuit emulator serves to debug hardware and software when developing application systems using the V850ES/JG3. It supports to the integrated debugger ID850QB. This emulator should be used in combination with a power supply unit and emulation probe. Use the USB interface cable to connect this emulator to the host machine. |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <3> USB interface cable                                     | Cable to connect the host machine and the QB-V850ESSX2.                                                                                                                                                                                                                                                                                     |

| <4> AC adapter                                              | 100 to 240 V can be supported by replacing the AC plug.                                                                                                                                                                                                                                                                                     |

| <8> QB-100GC-EA-01S<br>QB-100GC-EA-01T<br>Exchange adapter  | Adapter to perform pin conversion.                                                                                                                                                                                                                                                                                                          |

| <9> QB-100-CA-01S<br>Check pin adapter                      | Adapter used in waveform monitoring using the oscilloscope, etc.                                                                                                                                                                                                                                                                            |

| <10> QB-100-SA-01S<br>QB-100GC-YS-01T<br>Space adapter      | Adapter to adjust the height.                                                                                                                                                                                                                                                                                                               |

| <11> QB-100GC-YQ-01T<br>YQ connector                        | Conversion adapter to connect the target connector and the exchange adapter.                                                                                                                                                                                                                                                                |

| <12> QB-100GC-MA-01S<br>QB-100GC-HQ-01T<br>Mount adapter    | Adapter to mount the V850ES/JG3 with socket.                                                                                                                                                                                                                                                                                                |

| <13> QB-100GC-TC-01S<br>QB-100GC-NQ-01T<br>Target connector | Connector to solder on the target system.                                                                                                                                                                                                                                                                                                   |

**Note** The QB-V850ESSX2 is supplied with a power supply unit, USB interface cable, and simple programmer. It is also supplied with integrated debugger ID850QB as control software.

Remark The numbers in the angle brackets correspond to the numbers in Figure A-2.