Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                   |

| Core Processor             | STM8                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 41                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 25x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8al3188tcx |

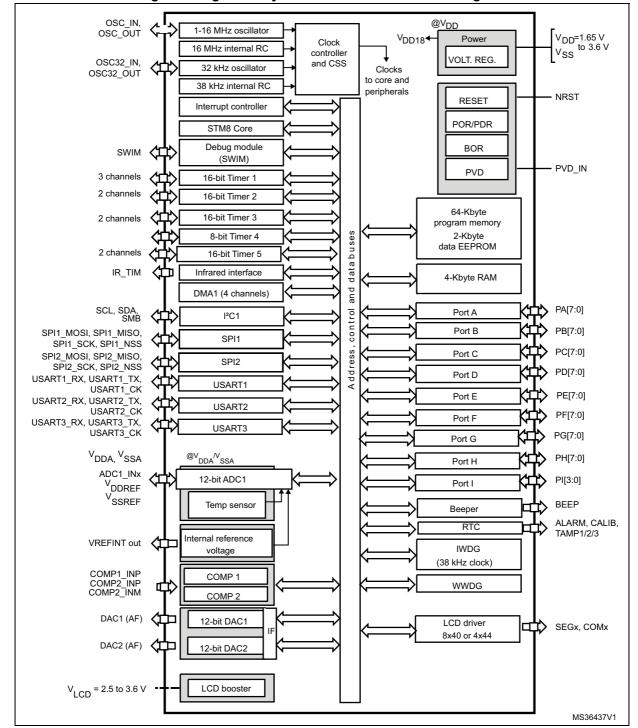

## 3 Functional overview

Figure 1. High-density STM8AL3x8x device block diagram

Legend: AF: alternate function ADC: Analog-to-digital converter

BOR: Brownout reset DMA: Direct memory access

## 3.12 System configuration controller and routing interface

The system configuration controller provides the capability to remap some alternate functions on different I/O ports. TIM4 and ADC1 DMA channels can also be remapped.

The highly flexible routing interface allows application software to control the routing of different I/Os to the TIM1 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1, COMP2, DAC1 and the internal reference voltage V<sub>REFINT</sub>. It also provides a set of registers for efficiently managing the charge transfer acquisition sequence.

## 3.13 Timers

The high-density STM8AL3x8x devices contain one advanced control timer (TIM1), three 16-bit general purpose timers (TIM2,TIM3 and TIM5) and one 8-bit basic timer (TIM4).

All the timers are served by DMA1.

*Table 3* compares the features of the advanced control, general-purpose and basic timers.

| Timer | Counter resolution | Counter<br>type | Prescaler factor               | DMA1<br>request<br>generation | Capture/compare channels | Complementary outputs |

|-------|--------------------|-----------------|--------------------------------|-------------------------------|--------------------------|-----------------------|

| TIM1  |                    |                 | Any integer<br>from 1 to 65536 |                               | 3 + 1                    | 3                     |

| TIM2  | 16-bit             | up/down         | Any power of 2 from 1 to 128   | Yes                           |                          |                       |

| TIM3  |                    |                 |                                |                               | 2                        |                       |

| TIM5  |                    |                 |                                |                               |                          | None                  |

| TIM4  | 8-bit              | up              | Any power of 2 from 1 to 32768 |                               | 0                        |                       |

Table 3. Timer feature comparison

#### 3.13.1 16-bit advanced control timer (TIM1)

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver.

- 16-bit up, down and up/down autoreload counter with 16-bit prescaler

- 3 independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- 1 additional capture/compare channel which is not connected to an external I/O

- Synchronization module to control the timer with external signals

- Break input to force timer outputs into a defined state

- 3 complementary outputs with adjustable dead time

- Encoder mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

#### 3.16 Communication interfaces

#### 3.16.1 SPI

The serial peripheral interfaces (SPI1 and SPI2) provide half/ full duplex synchronous serial communication with external devices.

- Maximum speed: 8 Mbit/s (f<sub>SYSCLK</sub>/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on 2 lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- Hardware CRC calculation

- Slave/master selection input pin

Note: SPI1 and SPI2 can be served by the DMA1 Controller.

#### 3.16.2 I<sup>2</sup>C

The I<sup>2</sup>C bus interface (I2C1) provides multi-master capability, and controls all I<sup>2</sup>C bus-specific sequencing, protocol, arbitration and timing.

- Master, slave and multi-master capability

- Standard mode up to 100 kHz and fast speed modes up to 400 kHz.

- 7-bit and 10-bit addressing modes.

- SMBus 2.0 and PMBus support

- Hardware CRC calculation

Note:  $I^2C1$  can be served by the DMA1 Controller.

#### 3.16.3 USART

The USART interfaces (USART1, USART2 and USART3) allow full duplex, asynchronous communications with external devices requiring an industry standard NRZ asynchronous serial data format. It offers a very wide range of baud rates.

- 1 Mbit/s full duplex SCI

- SPI1 emulation

- High precision baud rate generator

- Smartcard emulation

- IrDA SIR encoder decoder

- Single wire half duplex mode

Note: USART1, USART2 and USART3 can be served by the DMA1 Controller.

USART interfaces are used to implement LIN slave communication, with LIN Break detection on the framing error flag (FE in USART\_SR register) with a value of 0 in the USART data register (USART\_DR).

5//

Table 5. High-density STM8AL3x8x pin description (continued)

| n      | Pin<br>umb | er     |                                                                                                       |        |                   | ı        | npu | t              | 0                | utpu | ut | _                              |                                                                                                                                                                               |

|--------|------------|--------|-------------------------------------------------------------------------------------------------------|--------|-------------------|----------|-----|----------------|------------------|------|----|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP80 | LQFP64     | LQFP48 | Pin name                                                                                              | - Lype | I/O level         | floating | ndw | Ext. interrupt | High sink/source | ФО   | dd | Main function<br>(after reset) | Default alternate function                                                                                                                                                    |

| 58     | 46         | -      | PD5/TIM1_CH3<br>/LCD_SEG19 <sup>(3)</sup> /<br>ADC1_IN9/<br>COMP1_INP                                 | I/O    | FT <sup>(5)</sup> | x        | Х   | Х              | HS               | Х    | х  | Port D5                        | Timer 1 - channel 3 / LCD<br>segment 19 /<br>ADC1_IN9/Comparator 1<br>positive input                                                                                          |

| -      | 1          | 34     | PD5/TIM1_CH3<br>/LCD_SEG19 <sup>(3)</sup> /<br>ADC1_IN9/SPI2_MOSI/<br>COMP1_INP                       | I/O    | FT <sup>(5)</sup> | x        | X   | X              | HS               | x    | X  | Port D5                        | Timer 1 - channel 3 / LCD<br>segment 19 / ADC1_IN9/<br>SPI2 master out/slave<br>in/Comparator 1 positive<br>input                                                             |

| 59     | 47         |        | PD6/TIM1_BKIN<br>/LCD_SEG20 <sup>(3)</sup> /<br>ADC1_IN8/RTC_CALIB/<br>COMP1_INP/VREFINT              | I/O    | FT <sup>(5)</sup> | x        | x   | X              | HS               | X    | x  | Port D6                        | Timer 1 - break input / LCD segment 20 / ADC1_IN8 / RTC calibration/Comparator 1 positive input/Internal reference voltage output                                             |

| -      | -          |        | PD6/TIM1_BKIN<br>/LCD_SEG20 <sup>(3)</sup> /<br>ADC1_IN8/RTC_CALIB/<br>SPI2_SCK/COMP1_INP/<br>VREFINT | I/O    | FT <sup>(5)</sup> | x        | Х   | Х              | HS               | ×    | х  | Port D6                        | Timer 1 - break input / LCD segment 20 / ADC1_IN8 / RTC calibration/SPI2 clock/Comparator 1 positive input/Internal reference voltage output                                  |

| 60     | 48         | -      | PD7/TIM1_CH1N<br>/LCD_SEG21 <sup>(3)</sup> /<br>ADC1_IN7/RTC_ALARM/<br>COMP1_INP/VREFINT              | I/O    | FT <sup>(5)</sup> | x        | Х   | х              | HS               | х    | х  | Port D7                        | Timer 1 - inverted channel 1/<br>LCD segment 21 /<br>ADC1_IN7 / RTC<br>alarm/Comparator 1 positive<br>input/Internal reference<br>voltage output                              |

| -      | -          |        | PD7/TIM1_CH1N<br>/LCD_SEG21 <sup>(3)</sup> /<br>ADC1_IN7/RTC_ALARM/<br>SPI2_NSS/COMP1_INP/V<br>REFINT | I/O    | FT <sup>(5)</sup> | x        | X   | X              | HS               | x    | x  | Port D7                        | Timer 1 - inverted channel 1/<br>LCD segment 21 /<br>ADC1_IN7 / RTC alarm<br>/SPI2 master/slave<br>select/Comparator 1 positive<br>input/Internal reference<br>voltage output |

| 61     | 49         | -      | PG4/LCD_SEG32/<br>SPI2_NSS                                                                            | I/O    | FT <sup>(5)</sup> | X        | X   | X              | HS               | X    | Х  | Port G4                        | LCD segment 32 / SPI2<br>master/slave select                                                                                                                                  |

| 62     | 50         | -      | PG5/LCD_SEG33/<br>SPI2_SCK                                                                            | I/O    | FT <sup>(5)</sup> | X        | Х   | Х              | HS               | Х    | Х  | Port G5                        | LCD segment 33 / SPI2 clock                                                                                                                                                   |

| 63     | 51         | -      | PG6/LCD_SEG34/<br>SPI2_MOSI                                                                           | I/O    | FT <sup>(5)</sup> | X        | Х   | Х              | HS               | Х    | Х  | Port G6                        | LCD segment 34 / SPI2<br>master out- slave in                                                                                                                                 |

Table 9. General hardware register map (continued)

| Address   | Block    | Register label | Register name                          | Reset status |

|-----------|----------|----------------|----------------------------------------|--------------|

| 0x00 52B0 |          | TIM1_CR1       | TIM1 control register 1                | 0x00         |

| 0x00 52B1 |          | TIM1_CR2       | TIM1 control register 2                | 0x00         |

| 0x00 52B2 |          | TIM1_SMCR      | TIM1 Slave mode control register       | 0x00         |

| 0x00 52B3 |          | TIM1_ETR       | TIM1 external trigger register         | 0x00         |

| 0x00 52B4 |          | TIM1_DER       | TIM1 DMA1 request enable register      | 0x00         |

| 0x00 52B5 |          | TIM1_IER       | TIM1 Interrupt enable register         | 0x00         |

| 0x00 52B6 |          | TIM1_SR1       | TIM1 status register 1                 | 0x00         |

| 0x00 52B7 |          | TIM1_SR2       | TIM1 status register 2                 | 0x00         |

| 0x00 52B8 |          | TIM1_EGR       | TIM1 event generation register         | 0x00         |

| 0x00 52B9 |          | TIM1_CCMR1     | TIM1 Capture/Compare mode register 1   | 0x00         |

| 0x00 52BA |          | TIM1_CCMR2     | TIM1 Capture/Compare mode register 2   | 0x00         |

| 0x00 52BB |          | TIM1_CCMR3     | TIM1 Capture/Compare mode register 3   | 0x00         |

| 0x00 52BC |          | TIM1_CCMR4     | TIM1 Capture/Compare mode register 4   | 0x00         |

| 0x00 52BD |          | TIM1_CCER1     | TIM1 Capture/Compare enable register 1 | 0x00         |

| 0x00 52BE |          | TIM1_CCER2     | TIM1 Capture/Compare enable register 2 | 0x00         |

| 0x00 52BF |          | TIM1_CNTRH     | TIM1 counter high                      | 0x00         |

| 0x00 52C0 | TIM1     | TIM1_CNTRL     | TIM1 counter low                       | 0x00         |

| 0x00 52C1 | 1 IIVI I | TIM1_PSCRH     | TIM1 prescaler register high           | 0x00         |

| 0x00 52C2 |          | TIM1_PSCRL     | TIM1 prescaler register low            | 0x00         |

| 0x00 52C3 |          | TIM1_ARRH      | TIM1 Auto-reload register high         | 0xFF         |

| 0x00 52C4 |          | TIM1_ARRL      | TIM1 Auto-reload register low          | 0xFF         |

| 0x00 52C5 |          | TIM1_RCR       | TIM1 Repetition counter register       | 0x00         |

| 0x00 52C6 |          | TIM1_CCR1H     | TIM1 Capture/Compare register 1 high   | 0x00         |

| 0x00 52C7 |          | TIM1_CCR1L     | TIM1 Capture/Compare register 1 low    | 0x00         |

| 0x00 52C8 |          | TIM1_CCR2H     | TIM1 Capture/Compare register 2 high   | 0x00         |

| 0x00 52C9 |          | TIM1_CCR2L     | TIM1 Capture/Compare register 2 low    | 0x00         |

| 0x00 52CA |          | TIM1_CCR3H     | TIM1 Capture/Compare register 3 high   | 0x00         |

| 0x00 52CB |          | TIM1_CCR3L     | TIM1 Capture/Compare register 3 low    | 0x00         |

| 0x00 52CC |          | TIM1_CCR4H     | TIM1 Capture/Compare register 4 high   | 0x00         |

| 0x00 52CD |          | TIM1_CCR4L     | TIM1 Capture/Compare register 4 low    | 0x00         |

| 0x00 52CE |          | TIM1_BKR       | TIM1 break register                    | 0x00         |

| 0x00 52CF |          | TIM1_DTR       | TIM1 dead-time register                | 0x00         |

| 0x00 52D0 |          | TIM1_OISR      | TIM1 output idle state register        | 0x00         |

| 0x00 52D1 |          | TIM1_DCR1      | DMA1 control register 1                | 0x00         |

Table 9. General hardware register map (continued)

| Address                   | Block  | Register label | Register name               | Reset status                                   |

|---------------------------|--------|----------------|-----------------------------|------------------------------------------------|

| 0x00 53C8 to<br>0x00 53DF |        |                | Reserved area               |                                                |

| 0x00 53E0                 |        | USART2_SR      | USART2 status register      | 0xC0                                           |

| 0x00 53E1                 |        | USART2_DR      | USART2 data register        | 0xXX                                           |

| 0x00 53E2                 |        | USART2_BRR1    | USART2 baud rate register 1 | 0x00                                           |

| 0x00 53E3                 |        | USART2_BRR2    | USART2 baud rate register 2 | 0x00                                           |

| 0x00 53E4                 |        | USART2_CR1     | USART2 control register 1   | 0x00                                           |

| 0x00 53E5                 | USART2 | USART2_CR2     | USART2 control register 2   | 0x00                                           |

| 0x00 53E6                 |        | USART2_CR3     | USART2 control register 3   | 0x00                                           |

| 0x00 53E7                 |        | USART2_CR4     | USART2 control register 4   | 0x00                                           |

| 0x00 53E8                 |        | USART2_CR5     | USART2 control register 5   | 0x00                                           |

| 0x00 53E9                 |        | USART2_GTR     | USART2 guard time register  | 0x00                                           |

| 0x00 53EA                 |        | USART2_PSCR    | USART2 prescaler register   | 0x00                                           |

| 0x00 53EB to<br>0x00 53EF |        |                | Reserved area               |                                                |

| 0x00 53F0                 |        | USART3_SR      | USART3 status register      | 0xC0                                           |

| 0x00 53F1                 |        | USART3_DR      | USART3 data register        | 0xXX                                           |

| 0x00 53F2                 |        | USART3_BRR1    | USART3 baud rate register 1 | 0x00                                           |

| 0x00 53F3                 |        | USART3_BRR2    | USART3 baud rate register 2 | 0x00                                           |

| 0x00 53F4                 |        | USART3_CR1     | USART3 control register 1   | 0x00                                           |

| 0x00 53F5                 | USART3 | USART3_CR2     | USART3 control register 2   | 0x00                                           |

| 0x00 53F6                 |        | USART3_CR3     | USART3 control register 3   | 0x00                                           |

| 0x00 53F7                 |        | USART3_CR4     | USART3 control register 4   | 0x00                                           |

| 0x00 53F8                 |        | USART3_CR5     | USART3 control register 5   | 0x00                                           |

| 0x00 53F9                 |        | USART3_GTR     | USART3 guard time register  | 0x00                                           |

| 0x00 53FA                 | 7      | USART3_PSCR    | USART3 prescaler register   | 0x00                                           |

| 0x00 53FB to<br>0x00 53FF |        |                | Reserved area               | <u>,                                      </u> |

$14.0^{(2)}$

12.0

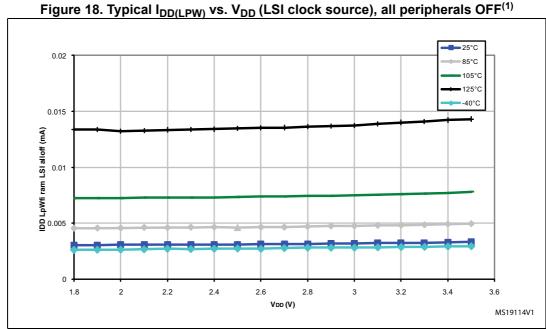

Symbol **Parameter** Conditions<sup>(1)</sup> Тур. Max. Unit  $T_A = -40 \,^{\circ}\text{C} \text{ to } 25 \,^{\circ}\text{C}$  $3.30^{(2)}$ 3.00 LSI RC osc.  $9.00^{(3)}$ T<sub>A</sub> = 85 °C 4.40 (at 38 kHz) Supply current in 18.00<sup>(3)</sup> T<sub>A</sub> = 125 °C 11.00 all peripherals OFF low-power wait I<sub>DD(LPW)</sub>  $T_A = -40 \,^{\circ}\text{C} \text{ to } 25 \,^{\circ}\text{C}$ 2.70<sup>(2)</sup> 2.35 mode LSE external clock<sup>(4)</sup>  $3.70^{(2)}$ T<sub>A</sub> = 85 °C 3.10 (32.768 kHz)

Table 24. Total current consumption in low-power wait mode at  $V_{DD}$  = 1.65 V to 3.6 V

T<sub>A</sub> = 125 °C

- 1. No floating I/Os.

- 2. Guaranteed by characterization results.

- Tested at 85°C for temperature range A or 125°C for temperature range C.

- Oscillator bypassed (LSEBYP = 1 in CLK\_ECKCR). When configured for external crystal, the LSE consumption (I<sub>DD LSE</sub>) must be added. Refer to Table 33.

1. Typical current consumption measured with code executed from RAM.

Table 25. Total current consumption and timing in Active-halt mode at  $V_{DD}$  = 1.65 V to 3.6 V (continued)

| Symbol                                     | Parameter                                                          | Conditions <sup>(1)</sup> |   |   | Тур.  | Max. <sup>(2)</sup> | Unit |

|--------------------------------------------|--------------------------------------------------------------------|---------------------------|---|---|-------|---------------------|------|

| t <sub>WU_HSI(AH)</sub> <sup>(9)(10)</sup> | Wakeup time from<br>Active-halt mode<br>to Run mode<br>(using HSI) | -                         | - | - | 4.70  | 7.00                | μs   |

| t <sub>WU_LSI(AH)</sub> <sup>(9)(10)</sup> | Wakeup time from<br>Active-halt mode<br>to Run mode<br>(using LSI) | -                         | - | - | 150.0 | -                   | μs   |

- 1. No floating I/O, unless otherwise specified.

- 2. Guaranteed by characterization results.

- 3. RTC enabled. Clock source = LSI

- 4. RTC enabled, LCD enabled with external V<sub>LCD</sub> = 3 V, static duty, division ratio = 256, all pixels active, no LCD connected.

- 5. RTC enabled, LCD enabled with external V<sub>LCD</sub>, 1/4 duty, 1/3 bias, division ratio = 64, all pixels active, no LCD connected.

- LCD enabled with internal LCD booster V<sub>LCD</sub> = 3 V, 1/4 duty, 1/3 bias, division ratio = 64, all pixels active, no LCD connected.

- 7. Oscillator bypassed (LSEBYP = 1 in CLK\_ECKCR). When configured for external crystal, the LSE consumption ( $I_{DD\ LSE}$ ) must be added. Refer to  $Table\ 33$

- 8. RTC enabled. Clock source = LSE

- Wakeup time until start of interrupt vector fetch.

The first word of interrupt routine is fetched 4 CPU cycles after t<sub>WU</sub>.

- 10. ULP=0 or ULP=1 and FWU=1 in the PWR\_CSR2 register.

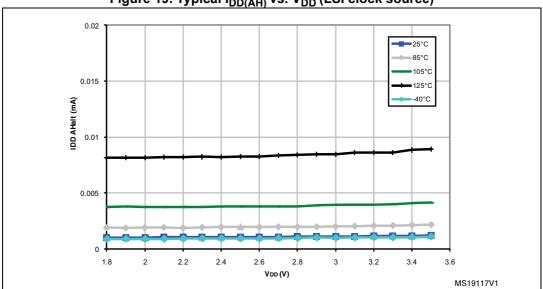

Table 26. Typical current consumption in Active-halt mode, RTC clocked by LSE external crystal

| Symbol                  | Parameter                          | Condition <sup>(1)</sup> |                       | Тур. | Unit |

|-------------------------|------------------------------------|--------------------------|-----------------------|------|------|

|                         | Supply current in Active-halt mode | \/ -19\/                 | LSE                   | 1.15 |      |

|                         |                                    | V <sub>DD</sub> = 1.8 V  | LSE/32 <sup>(3)</sup> | 1.05 | μΑ   |

| (2)                     |                                    | V <sub>DD</sub> = 3 V    | LSE                   | 1.30 |      |

| I <sub>DD(AH)</sub> (2) |                                    | v <sub>DD</sub> = 3 v    | LSE/32 <sup>(3)</sup> | 1.20 |      |

|                         |                                    | V 20V                    | LSE                   | 1.45 |      |

|                         |                                    | V <sub>DD</sub> = 3.6 V  | LSE/32 <sup>(3)</sup> | 1.35 |      |

- 1. No floating I/O, unless otherwise specified.

- 2. Based on measurements on bench with 32.768 kHz external crystal oscillator.

- 3. RTC clock is LSE divided by 32.

Figure 19. Typical  $I_{DD(AH)}$  vs.  $V_{DD}$  (LSI clock source)

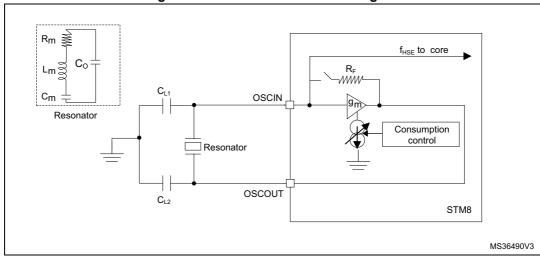

Figure 21. HSE oscillator circuit diagram

### HSE oscillator critical g<sub>m</sub> formula

$$g_{mcrit} = (2 \times \Pi \times f_{HSE})^2 \times R_m (2Co + C)^2$$

$R_{m} \hbox{:} \ Motional \ resistance \ (see \ crystal \ specification),} \ L_{m} \hbox{:} \ Motional \ inductance \ (see \ crystal \ specification),}$

C<sub>m</sub>: Motional capacitance (see crystal specification), Co: Shunt capacitance (see crystal specification),

$C_{L1}$ = $C_{L2}$ =C: Grounded external capacitance

g<sub>m</sub> >> g<sub>mcrit</sub>

#### LSE crystal/ceramic resonator oscillator

The LSE is available on STM8AL318x devices only.

The LSE clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

### 9.3.6 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error, out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation, LCD levels, etc.).

The test results are given in the following table.

**Functional susceptibility Symbol** Description Unit **Negative Positive** injection injection Injected current on true open-drain pins -5 +0 Injected current on all 5 V tolerant (FT) pins -5 +0  $I_{INJ}$ mΑ Injected current on any other pin -5 +5

Table 40. I/O current injection susceptibility

#### 9.3.7 I/O port pin characteristics

#### General characteristics

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

Table 42. Output driving current (high sink ports)

| I/O<br>Type | Symbol                         | Parameter                                                                         | Conditions                                           | Min.                  | Max. | Unit |

|-------------|--------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------|-----------------------|------|------|

|             | V <sub>OL</sub> <sup>(1)</sup> | Output low-level voltage for an I/O pin  Output high-level voltage for an I/O pin | $I_{IO}$ = +2 mA,<br>$V_{DD}$ = 3.0 V                | -                     | 0.45 | V    |

|             |                                |                                                                                   | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 1.8 V  | 1                     | 0.45 | V    |

| Standard    |                                |                                                                                   | I <sub>IO</sub> = +10 mA,<br>V <sub>DD</sub> = 3.0 V | -                     | 0.7  | ٧    |

| Stan        |                                |                                                                                   | I <sub>IO</sub> = -2 mA,<br>V <sub>DD</sub> = 3.0 V  | V <sub>DD</sub> -0.45 | -    | ٧    |

|             | V <sub>OH</sub> <sup>(2)</sup> |                                                                                   | I <sub>IO</sub> = -1 mA,<br>V <sub>DD</sub> = 1.8 V  | V <sub>DD</sub> -0.45 | -    | ٧    |

|             |                                |                                                                                   | I <sub>IO</sub> = -10 mA,<br>V <sub>DD</sub> = 3.0 V | V <sub>DD</sub> -0.7  | -    | V    |

<sup>1.</sup> The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

Table 43. Output driving current (true open drain ports)

| I/O<br>Type | Symbol                            | Parameter                               | Conditions                                          | Min. | Max. | Unit |

|-------------|-----------------------------------|-----------------------------------------|-----------------------------------------------------|------|------|------|

| drain       | Open drain A <sup>OP</sup> (1) On | Output low-level voltage for an I/O pin | $I_{IO}$ = +3 mA,<br>$V_{DD}$ = 3.0 V               | -    | 0.45 | ٧    |

| Open o      |                                   |                                         | I <sub>IO</sub> = +1 mA,<br>V <sub>DD</sub> = 1.8 V | -    | 0.45 | V    |

The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

Table 44. Output driving current (PA0 with high sink LED driver capability)

| I/O<br>Type | Symbol                         | Parameter                               | Conditions                             | Min. | Max. | Unit |

|-------------|--------------------------------|-----------------------------------------|----------------------------------------|------|------|------|

| 꼰           | V <sub>OL</sub> <sup>(1)</sup> | Output low-level voltage for an I/O pin | $I_{IO}$ = +20 mA,<br>$V_{DD}$ = 2.0 V | -    | 0.45 | V    |

<sup>1.</sup> The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

The I<sub>IQ</sub> current sourced must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IQ</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

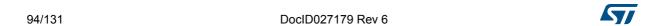

Figure 29. Typical V<sub>OL</sub> @ V<sub>DD</sub> = 3.0 V (high sink ports)

Figure 30. Typical V<sub>OL</sub> @ V<sub>DD</sub> = 1.8 V (high sink ports)

Figure 31. Typical V<sub>OL</sub> @ V<sub>DD</sub> = 3.0 V (true open drain ports)

Figure 32. Typical V<sub>OL</sub> @ V<sub>DD</sub> = 1.8 V (true open drain ports)

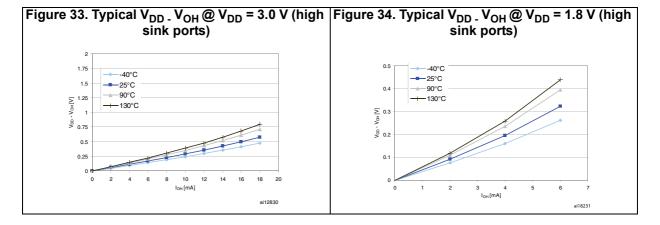

# **NRST** pin

Subject to general operating conditions for  $V_{DD}$  and  $T_{A}$  unless otherwise specified.

Table 45. NRST pin characteristics

| Symbol                | Parameter                          | Conditions                                                       | Min.                           | Тур. | Max.                           | Unit |

|-----------------------|------------------------------------|------------------------------------------------------------------|--------------------------------|------|--------------------------------|------|

| V <sub>IL(NRST)</sub> | NRST input low-level voltage       | -                                                                | V <sub>SS</sub> <sup>(1)</sup> | -    | 0.8 <sup>(1)</sup>             |      |

| V <sub>IH(NRST)</sub> | NRST input high-level voltage (1)  | -                                                                | 1.4 <sup>(1)</sup>             | -    | V <sub>DD</sub> <sup>(1)</sup> |      |

| V <sub>OL(NRST)</sub> | NDCT output love lovel voltage (1) | $I_{OL}$ = 2 mA<br>for 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V | -                              | -    | 0.4 <sup>(1)</sup>             | ٧    |

| VOL(NRST)             | NRST output low-level voltage (1)  | I <sub>OL</sub> = 1.5 mA<br>for V <sub>DD</sub> < 2.7 V          | -                              | -    | 0.4                            |      |

| V <sub>HYST</sub>     | NRST input hysteresis              | -                                                                | 10%V <sub>DD</sub> (2)(3)      | -    | -                              | mV   |

| R <sub>PU(NRST)</sub> | NRST pull-up equivalent resistor   | -                                                                | 30 <sup>(1)</sup>              | 45   | 60 <sup>(1)</sup>              | kΩ   |

| V <sub>F(NRST)</sub>  | NRST input filtered pulse          | -                                                                | -                              | -    | 50 <sup>(3)</sup>              | ns   |

| V <sub>NF(NRST)</sub> | NRST input not filtered pulse      | -                                                                | 300 <sup>(3)</sup>             | -    | -                              | 113  |

- 1. Guaranteed by characterization results.

- 2. 200 mV min.

- 3. Guaranteed by design.

#### 9.3.8 Communication interfaces

## SPI1 - Serial peripheral interface

Unless otherwise specified, the parameters given in *Table 46* are derived from tests performed under ambient temperature,  $f_{SYSCLK}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Section 9.3.1*. Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

Table 46. SPI1 characteristics

| Symbol                                               | Parameter                     | Conditions <sup>(1)</sup>                                             | Min.                      | Max.                     | Unit |  |

|------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------|---------------------------|--------------------------|------|--|

| f <sub>SCK</sub>                                     | SPI1 clock frequency          | Master mode                                                           | 0                         | 8                        |      |  |

| 1/t <sub>c(SCK)</sub>                                | SPTI Clock frequency          | Slave mode                                                            | 0                         | 8                        | MHz  |  |

| t <sub>r(SCK)</sub>                                  | SPI1 clock rise and fall time | Capacitive load: C = 30 pF                                            | -                         | 30                       |      |  |

| t <sub>su(NSS)</sub> <sup>(2)</sup>                  | NSS setup time                | Slave mode                                                            | 4 x 1/f <sub>SYSCLK</sub> | -                        |      |  |

| t <sub>h(NSS)</sub> <sup>(2)</sup>                   | NSS hold time                 | Slave mode                                                            | 80                        | -                        |      |  |

| t <sub>w(SCKH)</sub> (2)<br>t <sub>w(SCKL)</sub> (2) | SCK high and low time         | Master mode,<br>f <sub>MASTER</sub> = 8 MHz, f <sub>SCK</sub> = 4 MHz | 105                       | 145                      |      |  |

| t <sub>su(MI)</sub> (2)<br>t <sub>su(SI)</sub> (2)   | Data input setup time         | Master mode                                                           | 30                        | -                        |      |  |

| t <sub>su(SI)</sub> (2)                              | Data input setup time         | Slave mode                                                            | 3                         | -                        |      |  |

| t <sub>h(MI)</sub> (2)<br>t <sub>h(SI)</sub> (2)     | Data input hold time          | Master mode                                                           | 15                        | -                        | no   |  |

| $t_{h(SI)}^{(2)}$                                    | Data input noid time          | Slave mode                                                            | 0                         | -                        | ns   |  |

| t <sub>a(SO)</sub> (2)(3)                            | Data output access time       | Slave mode                                                            | -                         | 3x 1/f <sub>SYSCLK</sub> |      |  |

| t <sub>dis(SO)</sub> (2)(4)                          | Data output disable time      | Slave mode                                                            | 30                        | -                        |      |  |

| t <sub>v(SO)</sub> (2)                               | Data output valid time        | Slave mode (after enable edge)                                        | -                         | 60                       |      |  |

| t <sub>v(MO)</sub> <sup>(2)</sup>                    | Data output valid time        | Master mode (after enable edge)                                       | -                         | 20                       |      |  |

| t <sub>h(SO)</sub> (2)                               |                               | Slave mode (after enable edge)                                        | 15                        | -                        |      |  |

| t <sub>h(MO)</sub> <sup>(2)</sup>                    | Data output hold time         | Master mode (after enable edge)                                       | 1                         | -                        |      |  |

<sup>1.</sup> Parameters are given by selecting 10 MHz I/O output frequency.

<sup>2.</sup> Guaranteed by characterization results or by design.

<sup>3.</sup> Min. time is for the minimum time to drive the output and max. time is for the maximum time to validate the data.

<sup>4.</sup> Min. time is for the minimum time to invalidate the output and max. time is for the maximum time to put the data in Hi-Z.

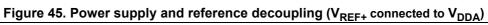

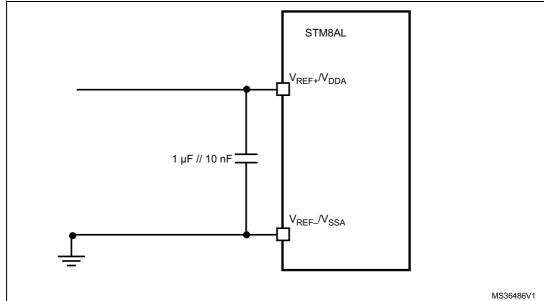

STM8AL V<sub>REF+</sub>  $1 \, \mu F \, / / \, 10 \, nF$ V<sub>DDA</sub> 1 μF // 10 nF VSSA/VREF-MS36485V1

Figure 44. Power supply and reference decoupling ( $V_{REF+}$  not connected to  $V_{DDA}$ )

millimeters inches<sup>(1)</sup> **Symbol** Min Тур Max Min Тур Max E3 7.500 0.2953 е 0.500 0.0197 Κ 0° 3.5° 7° 0°  $3.5^{\circ}$ 7° L 0.450 0.600 0.750 0.0177 0.0236 0.0295 L1 1.000 0.0394 0.080 0.0031 CCC

Table 66. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data (continued)

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

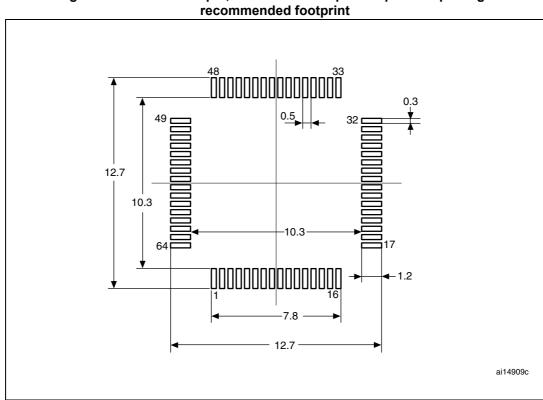

Figure 50. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

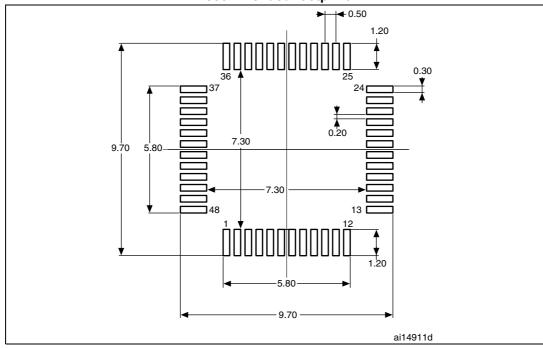

Figure 53. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

# 12 Revision history

Table 69. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03-Feb-2015 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22-Apr-2015 | 2        | Added:  - Figure 50: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package recommended footprint,  - Figure 48: LQFP80 marking example (package top view),  - Figure 51: LQFP64 marking example (package top view),  - Figure 54: LQFP48 marking example (package top view).  Corrected OPT0 default value in Table 12: Option byte addresses.                                                                                                                                                                                                                                                                                |

| 27-Jul-2015 | 3        | Updated  - the document confidentiality level to "Public",  - Table 1: Device summary, replacing STM8AL318AT with STM8AL318A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 19-Aug-2015 | 4        | Datasheet status changed to "production data".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1-Dec-2016  | 5        | <ul> <li>Updated Table 5: High-density STM8AL3x8x pin description: two pin names changed from PI0/RTC_TAMP1/[SPI2_NSS]/[TIM3_CH3 to PI0/RTC_TAMP1/[SPI2_NSS]/[TIM3_CH1 and from PF2/ADC1_IN26/[SPI2_SCK]/[USART3_SCK] to PF2/ADC1_IN26/[SPI1_SCK]/[USART3_SCK]</li> <li>Updated device marking part of Section 10.1: LQFP80 package information, Section 10.2: LQFP64 package information and Section 10.3: LQFP48 package information</li> <li>Updated Section 9.2: Absolute maximum ratings</li> <li>Updated table footnotes in Chapter 9: Electrical parameters</li> <li>Updated Figure 12: Power supply thresholds</li> </ul> |

| 5-Dec-2016  | 6        | <ul> <li>Updated Table 5: High-density STM8AL3x8x pin description: pin name changed from</li> <li>PC3/USART1_TX/LCD_SEG23(3)/ADC1_IN5/COMP_IN3M/COMP2_INM/COMP1_INP to</li> <li>PC3/USART1_TX/LCD_SEG23(3)/ADC1_IN5/COMP_2_INM/COMP1_INP.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                              |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics - All rights reserved