Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                   |

| Core Processor             | STM8                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                       |

| Number of I/O              | 54                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 28x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8al3189tcy |

# List of tables

| Table 1.  | Device summary                                                                       | . 2 |

|-----------|--------------------------------------------------------------------------------------|-----|

| Table 2.  | High-density STM8AL3x8x low-power device features and peripheral counts              | 13  |

| Table 3.  | Timer feature comparison                                                             | 22  |

| Table 4.  | Legend/abbreviation                                                                  |     |

| Table 5.  | High-density STM8AL3x8x pin description                                              | 29  |

| Table 6.  | Flash and RAM boundary addresses                                                     |     |

| Table 7.  | Factory conversion registers                                                         | 39  |

| Table 8.  | I/O port hardware register map                                                       | 39  |

| Table 9.  | General hardware register map                                                        | 41  |

| Table 10. | CPU/SWIM/debug module/interrupt controller registers                                 | 57  |

| Table 11. | Interrupt mapping                                                                    | 59  |

| Table 12. | Option byte addresses                                                                | 61  |

| Table 13. | Option byte description                                                              | 62  |

| Table 14. | Unique ID registers (96 bits)                                                        | 64  |

| Table 15. | Voltage characteristics                                                              | 66  |

| Table 16. | Current characteristics                                                              | 67  |

| Table 17. | Thermal characteristics                                                              | 67  |

| Table 18. | Operating lifetime (OLF)                                                             | 67  |

| Table 19. | General operating conditions                                                         | 68  |

| Table 20. | Embedded reset and power control block characteristics                               | 69  |

| Table 21. | Total current consumption in Run mode                                                | 71  |

| Table 22. | Total current consumption in Wait mode                                               | 74  |

| Table 23. | Total current consumption and timing in low-power run mode at VDD = 1.65 V to 3.6 V  | 76  |

| Table 24. | Total current consumption in low-power wait mode at VDD = 1.65 V to 3.6 V            |     |

| Table 25. | Total current consumption and timing in Active-halt mode                             | ' ' |

| Table 25. | at VDD = 1.65 V to 3.6 V                                                             | 78  |

| Table 26. | Typical current consumption in Active-halt mode, RTC clocked by LSE external crystal |     |

| Table 27. | Total current consumption and timing in Halt mode at VDD = 1.65 to 3.6 V             |     |

| Table 28. | Peripheral current consumption                                                       |     |

| Table 29. | Current consumption under external reset                                             |     |

| Table 30. | HSE external clock characteristics                                                   |     |

| Table 31. | LSE external clock characteristics                                                   |     |

| Table 32. | HSE oscillator characteristics                                                       |     |

| Table 33. | LSE oscillator characteristics                                                       |     |

| Table 34. | HSI oscillator characteristics.                                                      |     |

| Table 35. | LSI oscillator characteristics                                                       |     |

| Table 36. | RAM and hardware registers                                                           |     |

| Table 37. | Flash program memory/data EEPROM memory                                              |     |

| Table 38. | Flash program memory                                                                 |     |

| Table 39. | Data memory                                                                          |     |

| Table 40. | I/O current injection susceptibility                                                 |     |

| Table 41. | I/O static characteristics                                                           |     |

| Table 42. | Output driving current (high sink ports)                                             |     |

| Table 43. | Output driving current (true open drain ports)                                       |     |

| Table 44. | Output driving current (PA0 with high sink LED driver capability)                    |     |

| Table 45. | NRST pin characteristics                                                             |     |

| Table 46  | SPI1 characteristics                                                                 | 98  |

# List of figures

| Figure 1.  | High-density STM8AL3x8x device block diagram                                                            | 14  |

|------------|---------------------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Clock tree diagram                                                                                      |     |

| Figure 3.  | STM8AL318A 80-pin package pinout (without LCD)                                                          | 26  |

| Figure 4.  | STM8AL3L8A 80-pin package pinout (with LCD)                                                             |     |

| Figure 5.  | STM8AL3189 64-pin pinout (without LCD)                                                                  |     |

| Figure 6.  | STM8AL3L89 64-pin pinout (with LCD)                                                                     |     |

| Figure 7.  | STM8AL3188 48-pin pinout (without LCD)                                                                  |     |

| Figure 8.  | STM8AL3L88 48-pin pinout (with LCD)                                                                     |     |

| Figure 9.  | Memory map                                                                                              |     |

| Figure 10. | Pin loading conditions                                                                                  |     |

| Figure 11. | Pin input voltage                                                                                       |     |

| Figure 12. |                                                                                                         |     |

| Figure 13. | Power supply thresholds                                                                                 | 72  |

| Figure 14. | Typical $I_{DD(RUN)}$ from Flash vs. $V_{DD}$ (HSI clock source), $f_{CPU} = 16 \text{ MHz}^{(1)}$      | 73  |

| Figure 15. | Typical $I_{DD(Wait)}$ from RAM vs. $V_{DD}$ (HSI clock source), $f_{CPU} = 16 \text{ MHz}^{(1)}$       | 75  |

| Figure 16. | Typical I <sub>DD(Wait)</sub> from Flash (HSI clock source), f <sub>CPU</sub> = 16 MHz <sup>(1)</sup>   | 75  |

| Figure 17. | Typical I <sub>DD(LPR)</sub> vs. V <sub>DD</sub> (LSI clock source), all peripherals OFF                |     |

| Figure 18. | Typical I <sub>DD(LPW)</sub> vs. V <sub>DD</sub> (LSI clock source), all peripherals OFF <sup>(1)</sup> | 77  |

| Figure 19. | Typical IDD(AH) vs. V <sub>DD</sub> (LSI clock source)                                                  | 80  |

| Figure 20. | Typical IDD(Halt) vs. V <sub>DD</sub> (internal reference voltage OFF)                                  |     |

| Figure 21. | HSE oscillator circuit diagram                                                                          |     |

| Figure 22. | LSE oscillator circuit diagram                                                                          |     |

| Figure 23. | Typical HSI frequency vs. V <sub>DD</sub>                                                               |     |

| Figure 24. | Typical LSI clock source frequency vs. VDD                                                              |     |

| Figure 25. | Typical VIL and VIH vs. VDD (standard I/Os)                                                             |     |

| Figure 26. | Typical VIL and VIH vs. VDD (true open drain I/Os)                                                      |     |

| Figure 27. | Typical pull-up resistance R <sub>PU</sub> vs. V <sub>DD</sub> with VIN=VSS                             |     |

| Figure 28. | Typical pull-up current I <sub>pu</sub> vs. V <sub>DD</sub> with VIN=VSS                                |     |

| Figure 29. | Typical VOL @ VDD = 3.0 V (high sink ports)                                                             |     |

| Figure 30. | Typical VOL @ VDD = 1.8 V (high sink ports)                                                             |     |

| Figure 31. | Typical VOL @ VDD = 3.0 V (true open drain ports)                                                       |     |

| Figure 32. | Typical VOL @ VDD = 1.8 V (true open drain ports)                                                       |     |

| Figure 33. | Typical VDD - VOH @ VDD = 3.0 V (high sink ports)                                                       |     |

| Figure 34. | Typical VDD - VOH @ VDD = 1.8 V (high sink ports)                                                       |     |

| Figure 35. | Typical NRST pull-up resistance R <sub>PU</sub> vs. V <sub>DD</sub>                                     |     |

| Figure 36. | Typical NRST pull-up current I <sub>pu</sub> vs. V <sub>DD</sub>                                        |     |

| Figure 37. | Recommended NRST pin configuration                                                                      |     |

| Figure 38. | SPI1 timing diagram - slave mode and CPHA=0                                                             | 99  |

| Figure 39. | SPI1 timing diagram - slave mode and CPHA=1 <sup>(1)</sup>                                              | 99  |

| Figure 40. | SPI1 timing diagram - master mode <sup>(1)</sup>                                                        |     |

| Figure 41. | Typical application with I2C bus and timing diagram <sup>(1)</sup> )                                    | 102 |

| Figure 42. | ADC1 accuracy characteristics                                                                           |     |

| Figure 43. | Typical connection diagram using the ADC                                                                | 113 |

| Figure 44. | Power supply and reference decoupling ( $V_{REF+}$ not connected to $V_{DDA}$ )                         |     |

| Figure 45. | Power supply and reference decoupling (VREF+ connected to VDDA)                                         |     |

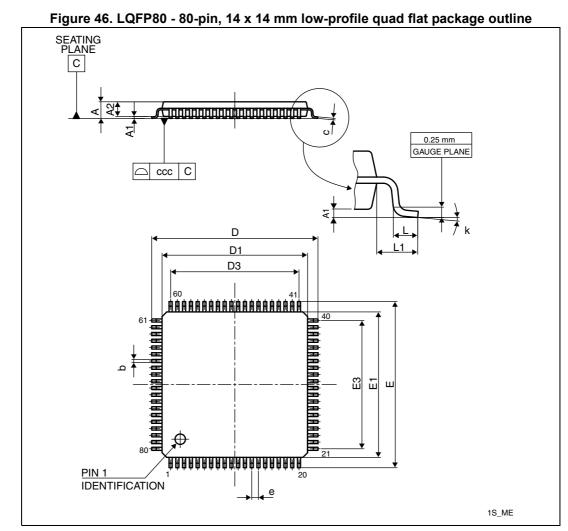

| Figure 46. | LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package outline                                       |     |

| Figure 47. | LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package                                               |     |

| 94.5       | recommended footnrint                                                                                   | 120 |

### 3.2 Central processing unit STM8

### 3.2.1 Advanced STM8 Core

The 8-bit STM8 core is designed for code efficiency and performance with an Harvard architecture and a 3-stage pipeline.

It contains 6 internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing, and 80 instructions.

#### Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus single cycle fetching most instructions

- X and Y 16-bit index registers enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter 16 Mbyte linear memory space

- 16-bit stack pointer access to a 64 Kbyte level stack

- 8-bit condition code register 7 condition flags for the result of the last instruction

#### Addressing

- 20 addressing modes

- Indexed indirect addressing mode for lookup tables located anywhere in the address space

- Stack pointer relative addressing mode for local variables and parameter passing

#### Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

### 3.2.2 Interrupt controller

The high-density STM8AL3x8x devices feature a nested vectored interrupt controller:

- Nested interrupts with 3 software priority levels

- 32 interrupt vectors with hardware priority

- Up to 40 external interrupt sources on 11 vectors

- Trap and reset interrupts

577

## 3.6 LCD (Liquid crystal display)

The LCD is only available on STM8AL3L8x devices.

The liquid crystal display drives up to 8 common terminals and up to 40 segment terminals to drive up to 320 pixels. This LCD is configurable to drive up to 4 common and 44 segments (up to 176 pixels).

- Internal step-up converter to guarantee contrast control whatever V<sub>DD</sub>.

- Static 1/2, 1/3, 1/4, 1/8 duty supported.

- Static 1/2, 1/3, 1/4 bias supported.

- Phase inversion to reduce power consumption and EMI.

- Up to 8 pixels programmable to blink.

- The LCD controller operating in Halt mode.

Note: Unnecessary segments and common pins can be used as general I/O pins.

### 3.7 Memories

The high-density STM8AL3x8x devices have the following main features:

- 4 Kbytes of RAM

- The non-volatile memory is divided into three arrays:

- 64 Kbytes of medium-density embedded Flash program memory

- 2 Kbytes of Data EEPROM

- Option byte.

The memory supports the read-while-write (RWW): it is possible to execute the code from the program matrix while programming/erasing the data matrix.

The option byte protects part of the Flash program memory from write and readout piracy.

### 3.8 DMA

A 4-channel direct memory access controller (DMA1) offers a memory-to-memory and peripherals-from/to-memory transfer capability. The 4 channels are shared between the following IPs with DMA capability: ADC1, DAC1, DAC2, I2C1, SPI1, SPI2, USART1, USART2, USART3, and the 5 Timers.

5//

### 3.12 System configuration controller and routing interface

The system configuration controller provides the capability to remap some alternate functions on different I/O ports. TIM4 and ADC1 DMA channels can also be remapped.

The highly flexible routing interface allows application software to control the routing of different I/Os to the TIM1 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1, COMP2, DAC1 and the internal reference voltage V<sub>REFINT</sub>. It also provides a set of registers for efficiently managing the charge transfer acquisition sequence.

### 3.13 Timers

The high-density STM8AL3x8x devices contain one advanced control timer (TIM1), three 16-bit general purpose timers (TIM2,TIM3 and TIM5) and one 8-bit basic timer (TIM4).

All the timers are served by DMA1.

*Table 3* compares the features of the advanced control, general-purpose and basic timers.

| Timer | Counter resolution | Counter<br>type | Prescaler factor               | DMA1<br>request<br>generation | Capture/compare channels | Complementary outputs |  |  |  |  |  |

|-------|--------------------|-----------------|--------------------------------|-------------------------------|--------------------------|-----------------------|--|--|--|--|--|

| TIM1  |                    |                 | Any integer<br>from 1 to 65536 |                               | 3 + 1                    | 3                     |  |  |  |  |  |

| TIM2  | 16-bit             | up/down         | up/down                        | up/down                       | up/down                  | up/down               |  |  |  |  |  |

| TIM3  |                    |                 | Any power of 2 from 1 to 128   | Yes                           | 2                        |                       |  |  |  |  |  |

| TIM5  |                    |                 |                                |                               |                          | None                  |  |  |  |  |  |

| TIM4  | 8-bit              | up              | Any power of 2 from 1 to 32768 |                               | 0                        |                       |  |  |  |  |  |

Table 3. Timer feature comparison

### 3.13.1 16-bit advanced control timer (TIM1)

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver.

- 16-bit up, down and up/down autoreload counter with 16-bit prescaler

- 3 independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- 1 additional capture/compare channel which is not connected to an external I/O

- Synchronization module to control the timer with external signals

- Break input to force timer outputs into a defined state

- 3 complementary outputs with adjustable dead time

- Encoder mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

22/131 DocID027179 Rev 6

Table 6. Flash and RAM boundary addresses

| Memory area          | Size    | Start address | End address |

|----------------------|---------|---------------|-------------|

| RAM                  | 4 Kbyte | 0x00 0000     | 0x00 0FFF   |

| Flash program memory | 64Kbyte | 0x00 8000     | 0x01 7FFF   |

## 5.2 Register map

Table 7. Factory conversion registers

| Address   | Block | Register label                      | Register name                                 | Reset<br>status |

|-----------|-------|-------------------------------------|-----------------------------------------------|-----------------|

| 0x00 4910 | -     | VREFINT_Factory_CONV <sup>(1)</sup> | Internal reference voltage factory conversion | 0xXX            |

| 0x00 4911 | -     | TS_Factory_CONV_V125 <sup>(2)</sup> | Temperature sensor output voltage             | 0xXX            |

<sup>1.</sup> The VREFINT Factory\_CONV byte represents the 8 LSB of the result of the VREFINT 12-bit ADC conversion performed in factory. The 2 MSB have a fixed value: 0x6.

Table 8. I/O port hardware register map

| Address   | Block    | Register label | Register name                     | Reset<br>status |

|-----------|----------|----------------|-----------------------------------|-----------------|

| 0x00 5000 |          | PA_ODR         | Port A data output latch register | 0x00            |

| 0x00 5001 |          | PA_IDR         | Port A input pin value register   | 0xXX            |

| 0x00 5002 | Port A   | PA_DDR         | Port A data direction register    | 0x00            |

| 0x00 5003 |          | PA_CR1         | Port A control register 1         | 0x01            |

| 0x00 5004 |          | PA_CR2         | Port A control register 2         | 0x00            |

| 0x00 5005 |          | PB_ODR         | Port B data output latch register | 0x00            |

| 0x00 5006 |          | PB_IDR         | Port B input pin value register   | 0xXX            |

| 0x00 5007 | Port B   | PB_DDR         | Port B data direction register    | 0x00            |

| 0x00 5008 |          | PB_CR1         | Port B control register 1         | 0x00            |

| 0x00 5009 |          | PB_CR2         | Port B control register 2         | 0x00            |

| 0x00 500A |          | PC_ODR         | Port C data output latch register | 0x00            |

| 0x00 500B |          | PB_IDR         | Port C input pin value register   | 0xXX            |

| 0x00 500C | Port C   | PC_DDR         | Port C data direction register    | 0x00            |

| 0x00 500D |          | PC_CR1         | Port C control register 1         | 0x00            |

| 0x00 500E | <u> </u> | PC_CR2         | Port C control register 2         | 0x00            |

<sup>2.</sup> The TS\_Factory\_CONV\_V125 byte represents the 8 LSB of the result of the V125 12-bit ADC conversion performed in factory. The 2 MSB have a fixed value: 0x3.

Table 9. General hardware register map (continued)

| Address                   | Block | Register label | Register label Register name     |      |

|---------------------------|-------|----------------|----------------------------------|------|

| 0x00 5400                 |       | LCD_CR1        | LCD control register 1           | 0x00 |

| 0x00 5401                 |       | LCD_CR2        | LCD control register 2           | 0x00 |

| 0x00 5402                 |       | LCD_CR3        | LCD control register 3           | 0x00 |

| 0x00 5403                 |       | LCD_FRQ        | LCD frequency selection register | 0x00 |

| 0x00 5404                 | LCD   | LCD_PM0        | LCD Port mask register 0         | 0x00 |

| 0x00 5405                 | LCD   | LCD_PM1        | LCD Port mask register 1         | 0x00 |

| 0x00 5406                 |       | LCD_PM2        | LCD Port mask register 2         | 0x00 |

| 0x00 5407                 |       | LCD_PM3        | LCD Port mask register 3         | 0x00 |

| 0x00 5408                 | 1     | LCD_PM4        | LCD Port mask register 4         | 0x00 |

| 0x00 5409                 | 1     | LCD_PM5        | LCD Port mask register 5         | 0x00 |

| 0x00 540A to<br>0x00 540B |       |                | Reserved area (2 byte)           |      |

| 0x00 540C                 |       | LCD_RAM0       | LCD display memory 0             | 0x00 |

| 0x00 540D                 |       | LCD_RAM1       | LCD display memory 1             | 0x00 |

| 0x00 540E                 | 1     | LCD_RAM2       | LCD display memory 2             | 0x00 |

| 0x00 540F                 | 1     | LCD_RAM3       | LCD display memory 3             | 0x00 |

| 0x00 5410                 | 1     | LCD_RAM4       | LCD display memory 4             | 0x00 |

| 0x00 5411                 | 1     | LCD_RAM5       | LCD display memory 5             | 0x00 |

| 0x00 5412                 |       | LCD_RAM6       | LCD display memory 6             | 0x00 |

| 0x00 5413                 |       | LCD_RAM7       | LCD display memory 7             | 0x00 |

| 0x00 5414                 | 1     | LCD_RAM8       | LCD display memory 8             | 0x00 |

| 0x00 5415                 |       | LCD_RAM9       | LCD display memory 9             | 0x00 |

| 0x00 5416                 | LCD   | LCD_RAM10      | LCD display memory 10            | 0x00 |

| 0x00 5417                 | LOD   | LCD_RAM11      | LCD display memory 11            | 0x00 |

| 0x00 5418                 |       | LCD_RAM12      | LCD display memory 12            | 0x00 |

| 0x00 5419                 |       | LCD_RAM13      | LCD display memory 13            | 0x00 |

| 0x00 541A                 |       | LCD_RAM14      | LCD display memory 14            | 0x00 |

| 0x00 541B                 |       | LCD_RAM15      | LCD display memory 15            | 0x00 |

| 0x00 541C                 |       | LCD_RAM16      | LCD display memory 16            | 0x00 |

| 0x00 541D                 |       | LCD_RAM17      | LCD display memory 17            | 0x00 |

| 0x00 541E                 |       | LCD_RAM18      | LCD display memory 18            | 0x00 |

| 0x00 541F                 |       | LCD_RAM19      | LCD display memory 19            | 0x00 |

| 0x00 5420                 |       | LCD_RAM20      | LCD display memory 20            | 0x00 |

| 0x00 5421                 |       | LCD_RAM21      | LCD display memory 21            | 0x00 |

# 6 Interrupt vector mapping

Note: Slope control of all GPIO pins can be programmed except true open drain pins and by

default is limited to 2 MHz.

Table 11. Interrupt mapping

|            | Table 11. Interrupt mapping    |                                                  |                             |                                       |                                      |                                                     |                   |  |  |

|------------|--------------------------------|--------------------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|-----------------------------------------------------|-------------------|--|--|

| IRQ<br>No. | Source<br>block                | Description                                      | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) <sup>(1)</sup> | Vector<br>address |  |  |

|            | RESET                          | Reset                                            | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8000         |  |  |

|            | TRAP                           | Software interrupt                               | -                           | -                                     | -                                    | -                                                   | 0x00 8004         |  |  |

| 0          | TLI <sup>(2)</sup>             | External Top level Interrupt                     | -                           | -                                     | -                                    | -                                                   | 0x00 8008         |  |  |

| 1          | FLASH                          | EOP/WR_PG_DIS                                    | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 800C         |  |  |

| 2          | DMA1 0/1                       | DMA1 channels 0/1                                | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8010         |  |  |

| 3          | DMA1 2/3                       | DMA1 channels 2/3                                | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8014         |  |  |

| 4          | RTC/LSE_<br>CSS                | RTC alarm interrupt/LSE<br>CSS interrupt         | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8018         |  |  |

| 5          | EXTI<br>E/F/PVD <sup>(4)</sup> | PortE/F interrupt/PVD interrupt                  | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 801C         |  |  |

| 6          | EXTIB/G                        | External interrupt port B/G                      | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8020         |  |  |

| 7          | EXTID/H                        | External interrupt port D/H                      | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8024         |  |  |

| 8          | EXTI0                          | External interrupt 0                             | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8028         |  |  |

| 9          | EXTI1                          | External interrupt 1                             | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 802C         |  |  |

| 10         | EXTI2                          | External interrupt 2                             | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8030         |  |  |

| 11         | EXTI3                          | External interrupt 3                             | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8034         |  |  |

| 12         | EXTI4                          | External interrupt 4                             | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8038         |  |  |

| 13         | EXTI5                          | External interrupt 5                             | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 803C         |  |  |

| 14         | EXTI6                          | External interrupt 6                             | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8040         |  |  |

| 15         | EXTI7                          | External interrupt 7                             | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8044         |  |  |

| 16         | LCD                            | LCD interrupt                                    | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8048         |  |  |

| 17         | CLK/<br>TIM1/<br>DAC           | System clock switch/CSS interrupt/TIM1 break/DAC | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 804C         |  |  |

| 18         | COMP1/<br>COMP2<br>ADC1        | Comparator 1 and 2 interrupt/ADC1                | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8050         |  |  |

Table 11. Interrupt mapping (continued)

| IRQ<br>No. | Source<br>block        | Description                                                                                                            | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) <sup>(1)</sup> | Vector<br>address |

|------------|------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|-----------------------------------------------------|-------------------|

| 19         | TIM2/<br>USART2        | TIM2 update /overflow/trigger/break/ USART2 transmission complete/transmit data register empty interrupt               | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8054         |

| 20         | TIM2/<br>USART2        | Capture/Compare/USART 2 interrupt                                                                                      | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8058         |

| 21         | TIM3/<br>USART3        | TIM3 Update /Overflow/Trigger/Break/ USART3 transmission complete/transmit data register empty interrupt               | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 805C         |

| 22         | TIM3/<br>USART3        | TIM3 Capture/Compare/<br>USART3 Receive register<br>data full/overrun/idle line<br>detected/parity error/<br>interrupt | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8060         |

| 23         | TIM1                   | Update /overflow/trigger/<br>COM                                                                                       | -                           | -                                     | -                                    | Yes <sup>(3)</sup>                                  | 0x00 8064         |

| 24         | TIM1                   | Capture/Compare                                                                                                        | -                           | -                                     | -                                    | Yes <sup>(3)</sup>                                  | 0x00 8068         |

| 25         | TIM4                   | Update/overflow/trigger                                                                                                | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 806C         |

| 26         | SPI1                   | End of Transfer                                                                                                        | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8070         |

| 27         | USART 1/<br>TIM5       | USART1 transmission<br>complete/transmit data<br>register empty/<br>TIM5 update/overflow/<br>trigger/break             | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8074         |

| 28         | USART 1/<br>TIM5       | USART1 Receive register<br>data full/overrun/idle line<br>detected/parity error/<br>TIM5 capture/compare               | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8078         |

| 29         | I <sup>2</sup> C1/SPI2 | I <sup>2</sup> C1 interrupt <sup>(5)</sup> /<br>SPI2                                                                   | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 807C         |

- 1. The Low-power wait mode is entered when executing a WFE instruction in Low-power run mode.

- 2. The TLI interrupt is the logic OR between TIM2 overflow interrupt, and TIM4 overflow interrupts.

- In WFE mode, this interrupt is served if it has been previously enabled. After processing the interrupt, the processor goes back to WFE mode. When this interrupt is configured as a wakeup event, the CPU wakes up and resumes processing.

- The interrupt from PVD is logically OR-ed with Port E and F interrupts. Register EXTI\_CONF allows to select between Port E and Port F interrupt. See more details about the external interrupt port select register (EXTI\_CONF) in the STM8L051/L052 Value Line, STM8L151/L152, STM8L162, STM8AL31, STM8AL3L MCU lines reference manual (RM0031).

- 5. The device is woken up from Halt or Active-halt mode only when the address received matches the interface address.

60/131 DocID027179 Rev 6

Table 13. Option byte description (continued)

| Option byte no. | Option description                                                                                                                                                                                                                                                           |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPT5            | BOR_ON: 0: Brownout reset off 1: Brownout reset on                                                                                                                                                                                                                           |

|                 | <b>BOR_TH[3:1]</b> : Brownout reset thresholds. Refer to <i>Table 20</i> for details on the thresholds according to the value of BOR_TH bits.                                                                                                                                |

| OPTBL           | OPTBL[15:0]: This option is checked by the boot ROM code after reset. Depending on the content of addresses 00 480B, 00 480C and 0x8000 (reset vector) the CPU jumps to the bootloader or to the reset vector.  Refer to the UM0560 bootloader user manual for more details. |

In the following table, data are based on characterization results, unless otherwise specified.

Table 22. Total current consumption in Wait mode

| Symbol                | Parameter               |                                                                   | Conditions <sup>(1)</sup>                                               |                                     |      | Max                                            | Unit                                |    |                   |

|-----------------------|-------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------|------|------------------------------------------------|-------------------------------------|----|-------------------|

|                       |                         |                                                                   |                                                                         | f <sub>CPU</sub> = 125 kHz          | 0.35 | 0.45 <sup>(4)</sup>                            |                                     |    |                   |

|                       |                         |                                                                   |                                                                         | f <sub>CPU</sub> = 1 MHz            | 0.35 | 0.50 <sup>(4)</sup>                            |                                     |    |                   |

|                       |                         |                                                                   | HSI                                                                     | f <sub>CPU</sub> = 4 MHz            | 0.40 | 0.60 <sup>(4)</sup>                            |                                     |    |                   |

|                       |                         | CPU not                                                           |                                                                         | f <sub>CPU</sub> = 8 MHz            | 0.50 | 0.60 <sup>(4)</sup>                            |                                     |    |                   |

|                       |                         | clocked, all peripherals                                          |                                                                         | f <sub>CPU</sub> = 16 MHz           | 0.70 | 0.85                                           | mA                                  |    |                   |

|                       | Supply                  | OFF, code executed from                                           |                                                                         | f <sub>CPU</sub> = 125 kHz          | 0.05 | 0.10 <sup>(4)</sup>                            | IIIA                                |    |                   |

| I <sub>DD(Wait)</sub> | current in<br>Wait mode | RAM with                                                          | LIGE - to a later                                                       | f <sub>CPU</sub> = 1 MHz            | 0.10 | 0.20 <sup>(4)</sup>                            |                                     |    |                   |

|                       | vvait mode              | Flash in I <sub>DDQ</sub><br>mode, <sup>(2)</sup> V <sub>DD</sub> | HSE external clock (f <sub>CPU</sub> =f <sub>HSE</sub> ) <sup>(3)</sup> | f <sub>CPU</sub> = 4 MHz            | 0.20 | 0.40 <sup>(4)</sup>                            |                                     |    |                   |

|                       |                         | from 1.65 V to                                                    | (GFO FIGE)                                                              | f <sub>CPU</sub> = 8 MHz            | 0.40 | 0.65 <sup>(4)</sup>                            |                                     |    |                   |

|                       |                         | 3.6 V                                                             |                                                                         | f <sub>CPU</sub> = 16 MHz           | 0.76 | 1.15 <sup>(4)</sup>                            |                                     |    |                   |

|                       |                         |                                                                   | LSI                                                                     | f <sub>CPU</sub> = f <sub>LSI</sub> | 60   | 80 <sup>(4)</sup>                              |                                     |    |                   |

|                       |                         |                                                                   |                                                                         |                                     |      | LSE <sup>(5)</sup> external clock (32.768 kHz) | f <sub>CPU</sub> = f <sub>LSE</sub> | 50 | 70 <sup>(4)</sup> |

|                       |                         |                                                                   | HSI                                                                     | f <sub>CPU</sub> = 125 kHz          | 0.38 | 0.55 <sup>(4)</sup>                            | -                                   |    |                   |

|                       |                         |                                                                   |                                                                         | f <sub>CPU</sub> = 1 MHz            | 0.40 | 0.60 <sup>(4)</sup>                            |                                     |    |                   |

|                       |                         |                                                                   |                                                                         | f <sub>CPU</sub> = 4 MHz            | 0.50 | 0.65 <sup>(4)</sup>                            |                                     |    |                   |

|                       |                         |                                                                   |                                                                         | f <sub>CPU</sub> = 8 MHz            | 0.60 | 0.75 <sup>(4)</sup>                            |                                     |    |                   |

|                       |                         | CPU not clocked, all                                              |                                                                         | f <sub>CPU</sub> = 16 MHz           | 0.80 | 0.90                                           |                                     |    |                   |

|                       | Supply                  | peripherals<br>OFF, code                                          |                                                                         | f <sub>CPU</sub> = 125 kHz          | 0.07 | 0.15 <sup>(4)</sup>                            | ⊢ mA                                |    |                   |

| I <sub>DD(Wait)</sub> | current in<br>Wait mode | executed from                                                     | (0)                                                                     | f <sub>CPU</sub> = 1 MHz            | 0.10 | 0.20 <sup>(4)</sup>                            |                                     |    |                   |

|                       | vvait mode              | Flash, V <sub>DD</sub><br>from 1.65 V to                          | HSE <sup>(3)</sup> external clock (f <sub>CPU</sub> = HSE)              | f <sub>CPU</sub> = 4 MHz            | 0.25 | 0.45 <sup>(4)</sup>                            |                                     |    |                   |

|                       |                         | 3.6 V                                                             | CFO - ,                                                                 | f <sub>CPU</sub> = 8 MHz            | 0.50 | 0.65 <sup>(4)</sup>                            | 1                                   |    |                   |

|                       |                         |                                                                   |                                                                         | f <sub>CPU</sub> = 16 MHz           | 1.00 | 1.20 <sup>(4)</sup>                            |                                     |    |                   |

|                       |                         |                                                                   | LSI                                                                     | f <sub>CPU</sub> = f <sub>LSI</sub> | 50   | 100 <sup>(4)</sup>                             |                                     |    |                   |

|                       |                         |                                                                   | LSE <sup>(5)</sup> external clock (32.768 kHz)                          | f <sub>CPU</sub> = f <sub>LSE</sub> | 50   | 80 <sup>(4)</sup>                              | μA                                  |    |                   |

<sup>1.</sup> All peripherals OFF,  $V_{DD}$  from 1.65 V to 3.6 V, HSI internal RC osc.,  $f_{CPU}$  =  $f_{SYSCLK}$

74/131 DocID027179 Rev 6

<sup>2.</sup> Flash is configured in  $I_{DDQ}$  mode in Wait mode by setting the EPM or WAITM bit in the Flash\_CR1 register.

Oscillator bypassed (HSEBYP = 1 in CLK\_ECKCR). When configured for external crystal, the HSE consumption (I<sub>DD HSE</sub>) must be added. Refer to Table 32.

<sup>4.</sup> Guaranteed by characterization results.

Oscillator bypassed (LSEBYP = 1 in CLK\_ECKCR). When configured for external crystal, the LSE consumption (I<sub>DD HSE</sub>) must be added. Refer to Table 33

In the following table, data are based on characterization results, unless otherwise specified.

Table 25. Total current consumption and timing in Active-halt mode at  $V_{DD}$  = 1.65 V to 3.6 V

| Symbol                 | Parameter                                                                        |                                                                                 | Conditions <sup>(1)</sup>                                                                    |                                                                |       | Max. <sup>(2)</sup> | Unit |

|------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------|---------------------|------|

|                        |                                                                                  |                                                                                 | LCD OFF <sup>(3)</sup>                                                                       | T <sub>A</sub> = -40 °C to 25 °C                               | 0.90  | 2.10                |      |

|                        |                                                                                  |                                                                                 |                                                                                              | T <sub>A</sub> = 85 °C                                         | 1.50  | 3.40                |      |

|                        |                                                                                  |                                                                                 |                                                                                              | T <sub>A</sub> = 125 °C                                        | 5.10  | 12.00               |      |

|                        |                                                                                  |                                                                                 | LCD ON                                                                                       | T <sub>A</sub> = -40 °C to 25 °C                               | 1.40  | 3.10                |      |

|                        |                                                                                  |                                                                                 | (static duty/<br>external                                                                    | T <sub>A</sub> = 85 °C                                         | 1.90  | 4.30                |      |

| ı                      | Supply current in                                                                | LSI RC                                                                          | V <sub>LCD</sub> ) <sup>(4)</sup>                                                            | T <sub>A</sub> = 125 °C                                        | 5.50  | 13.00               |      |

| I <sub>DD(AH)</sub>    | Active-halt mode                                                                 | (at 38 kHz)                                                                     | LCD ON                                                                                       | T <sub>A</sub> = -40 °C to 25 °C                               | 1.90  | 4.30                | μΑ   |

|                        |                                                                                  |                                                                                 | (1/4 duty/<br>external                                                                       | (1/4 duty/<br>external $T_A = 85 ^{\circ}\text{C}$             |       | 5.40                |      |

|                        |                                                                                  | $V_{LCD}$ ) (5) $T_A = 12$ $LCD ON$ $T_A = -4$ $(1/4 duty/internal)$ $T_A = 85$ | T <sub>A</sub> = 125 °C                                                                      | 6.00                                                           | 15.00 |                     |      |

|                        |                                                                                  |                                                                                 | $T_A = -40  ^{\circ}\text{C} \text{ to } 25  ^{\circ}\text{C}$                               | 3.90                                                           | 8.75  |                     |      |

|                        |                                                                                  |                                                                                 | T <sub>A</sub> = 85 °C                                                                       | 4.50                                                           | 10.20 |                     |      |

|                        |                                                                                  |                                                                                 |                                                                                              | T <sub>A</sub> = 125 °C                                        | 6.80  | 16.30               |      |

|                        |                                                                                  | LC<br>(st                                                                       |                                                                                              | T <sub>A</sub> = -40 °C to 25 °C                               | 0.50  | 1.20                | - μΑ |

|                        |                                                                                  |                                                                                 | LCD OFF <sup>(8)</sup>                                                                       | T <sub>A</sub> = 85 °C                                         | 0.90  | 2.10                |      |

|                        |                                                                                  |                                                                                 |                                                                                              | T <sub>A</sub> = 125 °C                                        | 4.80  | 11.00               |      |

|                        |                                                                                  |                                                                                 | external k (static duty/ external $V_{LCD}$ ) (4) $T_A = 85 ^{\circ}C$ $T_A = 125 ^{\circ}C$ | T <sub>A</sub> = -40 °C to 25 °C                               | 0.85  | 1.90                |      |

|                        |                                                                                  |                                                                                 |                                                                                              | T <sub>A</sub> = 85 °C                                         | 1.30  | 3.20                |      |

|                        |                                                                                  | clock                                                                           |                                                                                              | T <sub>A</sub> = 125 °C                                        | 5.00  | 12.00               |      |

| I <sub>DD(AH)</sub>    | Active-halt mode                                                                 | (32.768 kHz)                                                                    |                                                                                              | $T_A = -40  ^{\circ}\text{C} \text{ to } 25  ^{\circ}\text{C}$ | 1.50  | 2.50                |      |

|                        |                                                                                  | (,,                                                                             |                                                                                              | T <sub>A</sub> = 85 °C                                         | 1.80  | 4.20                |      |

|                        |                                                                                  |                                                                                 |                                                                                              | T <sub>A</sub> = 125 °C                                        | 5.70  | 14.00               |      |

|                        |                                                                                  |                                                                                 | LCD ON                                                                                       | $T_A = -40  ^{\circ}\text{C} \text{ to } 25  ^{\circ}\text{C}$ | 3.40  | 7.60                |      |

|                        |                                                                                  |                                                                                 | (1/4 duty/<br>internal                                                                       | T <sub>A</sub> = 85 °C                                         | 3.90  | 9.20                |      |

|                        |                                                                                  |                                                                                 | V <sub>LCD</sub> ) <sup>(6)</sup>                                                            | T <sub>A</sub> = 125 °C                                        | 6.30  | 15.20               |      |

| I <sub>DD(WUFAH)</sub> | Supply current<br>during wakeup<br>time from Active-<br>halt mode<br>(using HSI) | -                                                                               | -                                                                                            | -                                                              | 2.40  | -                   | mA   |

- Data based on a differential I<sub>DD</sub> measurement between DAC in reset configuration and continuous DAC conversion of V<sub>DD</sub> /2. Floating DAC output.

- Data based on a differential I<sub>DD</sub> measurement between COMP1 or COMP2 in reset configuration and COMP1 or COMP2 enabled with static inputs. Supply current of internal reference voltage excluded.

- 7. Including supply current of internal reference voltage.

Table 29. Current consumption under external reset

| Symbol        | Parameter      | Conditions                                              |                         | Тур. | Unit |

|---------------|----------------|---------------------------------------------------------|-------------------------|------|------|

|               |                | PB1/PB3/PA5 pins are externally tied to V <sub>DD</sub> | V <sub>DD</sub> = 1.8 V | 48   | _    |

| $I_{DD(RST)}$ |                |                                                         | V <sub>DD</sub> = 3 V   | 80   | μΑ   |

|               | Oxtornal redet | , 55                                                    | V <sub>DD</sub> = 3.6 V | 95   |      |

All pins except PA0, PB0 and PB4 are floating under reset. PA0, PB0 and PB4 are configured with pull-up under reset. PB1, PB3 and PA5 must be tied externally under reset to avoid the consumption due to their schmitt trigger.

### 9.3.4 Clock and timing characteristics

## HSE external clock (HSEBYP = 1 in CLK\_ECKCR)

Subject to general operating conditions for V<sub>DD</sub> and T<sub>A</sub>.

Table 30. HSE external clock characteristics

| Symbol                              | Parameter                               | Conditions                                          | Min.                  | Тур. | Max.                  | Unit |

|-------------------------------------|-----------------------------------------|-----------------------------------------------------|-----------------------|------|-----------------------|------|

| f <sub>HSE_ext</sub> <sup>(1)</sup> | External clock source frequency         |                                                     | 1                     | -    | 16                    | MHz  |

| V <sub>HSEH</sub>                   | OSC_IN input pin high-<br>level voltage | -                                                   | 0.7 x V <sub>DD</sub> | -    | V <sub>DD</sub>       | V    |

| V <sub>HSEL</sub>                   | OSC_IN input pin low-<br>level voltage  |                                                     | V <sub>SS</sub>       | -    | 0.3 x V <sub>DD</sub> | V    |

| C <sub>in(HSE)</sub> <sup>(1)</sup> | OSC_IN input capacitance                | -                                                   | -                     | 2.6  | -                     | pF   |

| I <sub>LEAK_HSE</sub>               | OSC_IN input leakage current            | V <sub>SS</sub> < V <sub>IN</sub> < V <sub>DD</sub> | -                     | -    | ±500                  | nA   |

<sup>1.</sup> Guaranteed by design.

Table 42. Output driving current (high sink ports)

| I/O<br>Type | Symbol                         | Parameter                                | Conditions                                           | Min.                  | Max. | Unit |

|-------------|--------------------------------|------------------------------------------|------------------------------------------------------|-----------------------|------|------|

| Standard    | V <sub>OL</sub> <sup>(1)</sup> | Output low-level voltage for an I/O pin  | $I_{IO}$ = +2 mA,<br>$V_{DD}$ = 3.0 V                | -                     | 0.45 | V    |

|             |                                |                                          | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 1.8 V  | 1                     | 0.45 | V    |

|             |                                |                                          | I <sub>IO</sub> = +10 mA,<br>V <sub>DD</sub> = 3.0 V | -                     | 0.7  | ٧    |

|             | V <sub>OH</sub> <sup>(2)</sup> | Output high-level voltage for an I/O pin | I <sub>IO</sub> = -2 mA,<br>V <sub>DD</sub> = 3.0 V  | V <sub>DD</sub> -0.45 | -    | ٧    |

|             |                                |                                          | I <sub>IO</sub> = -1 mA,<br>V <sub>DD</sub> = 1.8 V  | V <sub>DD</sub> -0.45 | -    | ٧    |

|             |                                |                                          | I <sub>IO</sub> = -10 mA,<br>V <sub>DD</sub> = 3.0 V | V <sub>DD</sub> -0.7  | -    | V    |

<sup>1.</sup> The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

Table 43. Output driving current (true open drain ports)

| I/O<br>Type               | Symbol                                          | Parameter                                           | Conditions                            | Min. | Max. | Unit |

|---------------------------|-------------------------------------------------|-----------------------------------------------------|---------------------------------------|------|------|------|

| Open drain $V_{OL}^{(1)}$ | V (1)                                           | Output law laws with an far an I/O nin              | $I_{IO}$ = +3 mA,<br>$V_{DD}$ = 3.0 V | -    | 0.45 | ٧    |

|                           | 1 VAL TOULDULION ICVCI VOILUGE IOI UIT I/O PIIT | I <sub>IO</sub> = +1 mA,<br>V <sub>DD</sub> = 1.8 V | -                                     | 0.45 | V    |      |

The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

Table 44. Output driving current (PA0 with high sink LED driver capability)

| I/O<br>Type | Symbol                         | Parameter                               | Conditions                             | Min. | Max. | Unit |

|-------------|--------------------------------|-----------------------------------------|----------------------------------------|------|------|------|

| 꼰           | V <sub>OL</sub> <sup>(1)</sup> | Output low-level voltage for an I/O pin | $I_{IO}$ = +20 mA,<br>$V_{DD}$ = 2.0 V | -    | 0.45 | V    |

<sup>1.</sup> The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

The I<sub>IQ</sub> current sourced must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IQ</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

400

pF

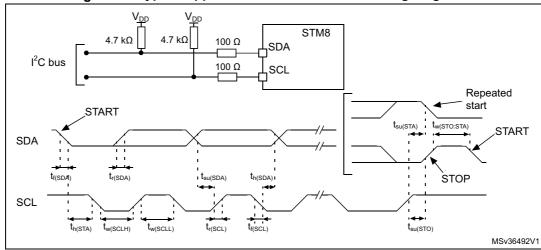

### I<sup>2</sup>C - Inter IC control interface

Subject to general operating conditions for  $V_{DD}$ ,  $f_{SYSCLK}$ , and  $T_A$  unless otherwise specified.

The STM8AL I<sup>2</sup>C interface (I2C1) meets the requirements of the Standard I<sup>2</sup>C communication protocol described in the following table with the restriction mentioned below:

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

Fast mode I<sup>2</sup>C<sup>(1)</sup> Standard mode I<sup>2</sup>C **Symbol Parameter** Unit Min. (2) Min.<sup>(2)</sup> Max. (2) Max. (2) SCL clock low time 4.7 1.3 tw(SCLL) μS SCL clock high time 4.0 0.6 tw(SCLH) 250 100 t<sub>su(SDA)</sub> SDA setup time SDA data hold time 0 0 900 t<sub>h(SDA)</sub>  $t_{r(SDA)}$ SDA and SCL rise time 1000 300 ns t<sub>r(SCL)</sub> t<sub>f(SDA)</sub> SDA and SCL fall time 300 300 t<sub>f(SCL)</sub> START condition hold time 4.0 0.6 t<sub>h(STA)</sub> Repeated START condition setup  $t_{su(STA)}$ 4.7 0.6 μS t<sub>su(STO)</sub> STOP condition setup time 4.0 0.6 STOP to START condition time (bus 4.7 1.3 tw(STO:STA) free)

400

Table 47. I2C characteristics

Capacitive load for each bus line

Note:

$C_b$

For speeds around 200 kHz, the achieved speed has a  $\pm 5\%$  tolerance. For other speed ranges, the achieved speed has a  $\pm 2\%$  tolerance. The above variations depend on the accuracy of the external components used.

<sup>1.</sup>  $f_{SYSCLK}$  must be at least equal to 8 MHz to achieve max fast  $I^2C$  speed (400 kHz).

<sup>2.</sup> Data based on standard I<sup>2</sup>C protocol requirement, not tested in production.

Figure 41. Typical application with I<sup>2</sup>C bus and timing diagram<sup>(1))</sup>

1. Measurement points are done at CMOS levels: 0.3 x  $\rm V_{DD}$  and 0.7 x  $\rm V_{DD}$

#### 9.3.15 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

### Functional EMS (electromagnetic susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms to the ANSI/ESDA/JEDEC JS-001, JESD22-A115 and ANSI/ESD S5.3.1.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

## Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### **Prequalification trials:**

Most of the common failures (unexpected reset and program counter corruption) are reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress is applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software is hardened to prevent unrecoverable errors occurring (see application note AN1015).

Table 60. EMS data

| Symbol            | Parameter                                                                      | Conditions                                                                      |           |    |

|-------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------|----|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance | $V_{DD}$ = 3.3 V, $T_A$ = +25 °C, $f_{CPU}$ = 16 MHz, conforms to IEC 61000     |           | 2B |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on            | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = +25 °C,<br>f <sub>CPU</sub> = 16 MHz, | Using HSI | 4A |

| *EF1B             | I VAN AITU VSS DIITS 10 ITTUUCE A                                              | conforms to IEC 61000                                                           | 2B        |    |

# 10 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

## 10.1 LQFP80 package information

1. Drawing is not to scale.

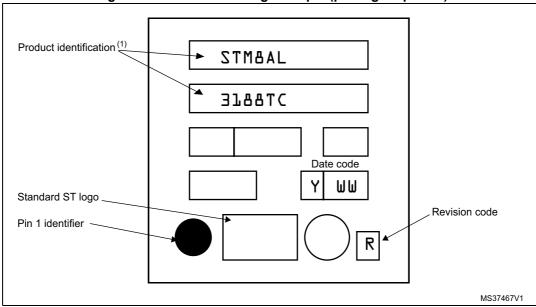

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 54. LQFP48 marking example (package top view)

I. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted to run a qualification activity prior to any decision to use these engineering samples.

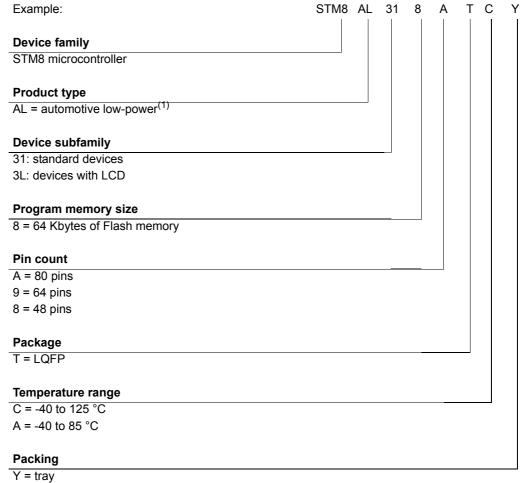

# 11 Ordering information

Table 68. Ordering information scheme

X = Tape and reel compliant with EIA 481-C

For a list of available options (e.g. memory size, package) and orderable part numbers or for further information on any aspect of this device, please go to <a href="https://www.st.com">www.st.com</a> or contact the nearest ST sales office.

Qualified and characterized according to AEC Q100 and Q003 or equivalent, advanced screening according to AEC Q001 and Q002 or equivalent.