Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 68                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 28x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 80-LQFP                                                               |

| Supplier Device Package    | 80-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8al318atcy |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 48. | LQFP80 marking example (package top view)                         | 121 |

|------------|-------------------------------------------------------------------|-----|

| Figure 49. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline | 122 |

| Figure 50. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package         |     |

| -          | recommended footprint                                             | 123 |

| Figure 51. | LQFP64 marking example (package top view)                         | 124 |

| Figure 52. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline   | 125 |

| Figure 53. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package           |     |

| -          | recommended footprint                                             | 127 |

| Figure 54. | LQFP48 marking example (package top view)                         | 128 |

# 1 Introduction

This document describes the features, pinout, mechanical data and ordering information of the high-density STM8AL318x and STM8AL3L8x devices (microcontrollers with 64 Kbyte Flash memory density). These devices are referred to as high-density devices in STM8L051/L052 Value Line, STM8L151/L152, STM8L162, STM8AL31, STM8AL3L MCU lines reference manual (RM0031) and in the STM8L and STM8AL Flash programming manual (PM0054).

For more details on the whole STMicroelectronics ultra-low-power family please refer to *Section 3: Functional overview on page 14.*

For information on the debug module and SWIM (single wire interface module), refer to the *STM8 SWIM communication protocol and debug module user manual* (UM0470).

For information on the STM8 core, please refer to the *STM8 CPU programming manual* (PM0044).

DAC: Digital-to-analog converter I<sup>2</sup>C: Inter-integrated circuit multimaster interface IWDG: Independent watchdog LCD: Liquid crystal display POR/PDR: Power on reset / power-down reset RTC: Real-time clock SPI: Serial peripheral interface SWIM: Single wire interface module USART: Universal synchronous asynchronous receiver transmitter WWDG: Window watchdog

## 3.1 Low-power modes

The high-density STM8AL3x8x devices support five low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

- Wait mode: CPU clock is stopped, but selected peripherals keep running. An internal or external interrupt or a Reset is used to exit the microcontroller from Wait mode (WFE or WFI mode).

- **Low-power run mode**: The CPU and the selected peripherals are running. Execution is done from RAM with a low speed oscillator (LSI or LSE). Flash memory and data EEPROM are stopped and the voltage regulator is configured in ultra-low-power mode. The microcontroller enters Low-power run mode by software and exits from this mode by software or by a reset.

All interrupts must be masked and are not used to exit the microcontroller from this mode.

- Low-power wait mode: This mode is entered when executing a Wait for event in Low-power run mode. It is similar to Low-power run mode except that the CPU clock is stopped. The wakeup from this mode is triggered by a Reset or by an internal or external event (peripheral event generated by the timers, serial interfaces, DMA controller (DMA1), comparators and I/O ports). When the wakeup is triggered by an event, the system goes back to Low-power run mode. All interrupts must be masked and arenot used to exit the microcontroller from this mode.

- Active-halt mode: CPU and peripheral clocks are stopped, except RTC. The wakeup is triggered by RTC interrupts, external interrupts or reset.

- Halt mode: CPU and peripheral clocks are stopped, the device remains powered on. The RAM content is preserved. The wakeup is triggered by an external interrupt or reset. A few peripherals have also a wakeup from Halt capability. Switching off the internal reference voltage reduces power consumption. Through software configuration it is also possible to wake up the device without waiting for the internal reference voltage wakeup time to have a fast wakeup time of 5 µs.

### 3.13.2 16-bit general purpose timers (TIM2, TIM3, TIM5)

- 16-bit autoreload (AR) up/down-counter

- 7-bit prescaler adjustable to fixed power of 2 ratios (1...128)

- 2 individually configurable capture/compare channels

- PWM mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

- Synchronization with other timers or external signals (external clock, reset, trigger and enable)

#### 3.13.3 8-bit basic timer (TIM4)

The 8-bit timer consists of an 8-bit up auto-reload counter driven by a programmable prescaler. This timer is used for timebase generation with interrupt generation on timer overflow or for DAC trigger generation.

### 3.14 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

#### 3.14.1 Window watchdog timer

The window watchdog (WWDG) is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

#### 3.14.2 Independent watchdog timer

The independent watchdog peripheral (IWDG) is used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the internal LSI RC clock source, and thus stays active even in case of a CPU clock failure.

### 3.15 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

| n      | Pin<br>umb | er     | Table 5. High-de                                                                                       |      |                   |          | npu |                |                  | utpu | -  |                                |                                                                                                                              |

|--------|------------|--------|--------------------------------------------------------------------------------------------------------|------|-------------------|----------|-----|----------------|------------------|------|----|--------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| LQFP80 | LQFP64     | LQFP48 | Pin name                                                                                               | Type | I/O level         | floating | ndw | Ext. interrupt | High sink/source | ОD   | ЬР | Main function<br>(after reset) | Default alternate function                                                                                                   |

| 73     | 61         | 45     | PC6/OSC32_OUT/<br>[SPI1_SCKJ <sup>[2)</sup> /<br>[USART1_RXJ <sup>(2)</sup>                            | I/O  | FT <sup>(5)</sup> | x        | х   | х              | HS               | х    | х  | Port C6                        | LSE oscillator output / [SPI1<br>clock] / [USART1 receive]                                                                   |

| 74     | 62         | -      | PC7/LCD_SEG25 <sup>(3)/</sup><br>ADC1_IN3/COMP2_INM/<br>COMP1_INP                                      | I/O  | FT <sup>(5)</sup> | x        | x   | х              | HS               | х    | x  | Port C7                        | LCD segment 25<br>/ADC1_IN3/ Comparator<br>negative input / Comparator<br>1 positive input                                   |

| -      | -          | 46     | PC7/LCD_SEG25 <sup>(3)</sup> /<br>ADC1_IN3/USART3_CK/<br>COMP2_INM/<br>COMP1_INP                       | I/O  | FT <sup>(5)</sup> | x        | x   | x              | HS               | x    | x  | Port C7                        | LCD segment 25<br>/ADC1_IN3/ USART3<br>synchronous clock/<br>Comparator 2 negative input<br>/ Comparator 1 positive<br>input |

| 29     | 25         | 20     | PD0/TIM3_CH2/<br><i>[ADC1_TRIG]<sup>(2)</sup>/</i><br>LCD_SEG7 <sup>(3)</sup> /<br>ADC1_IN22/COMP2_INP | I/O  | FT <sup>(5)</sup> | x        | x   | х              | HS               | х    | x  | Port D0                        | Timer 3 - channel 2 /<br>[ADC1_Trigger] / LCD<br>segment 7 / ADC1_IN22 /<br>Comparator 2 positive input<br>2                 |

| 30     | 26         | 21     | PD1/TIM3_ETR/<br>LCD_COM3 <sup>(3)</sup> /<br>ADC1_IN21/COMP1_INP/<br>COMP2_INP                        | I/O  | FT <sup>(5)</sup> | x        | x   | х              | HS               | х    | x  | Port D1                        | Timer 3 - trigger /<br>LCD_COM3 / ADC1_IN21 /<br>comparator 1 positive input/<br>comparator 2 positive input                 |

| 31     | 27         |        | PD2/TIM1_CH1<br>/LCD_SEG8 <sup>(3)</sup> /<br>ADC1_IN20/COMP1_INP                                      | I/O  | FT <sup>(5)</sup> | x        | x   | х              | HS               | х    | x  | Port D2                        | Timer 1 - channel 1 / LCD<br>segment 8 /<br>ADC1_IN20/Comparator 1<br>positive input                                         |

| 32     | 28         | 23     | PD3/ TIM1_ETR/<br>LCD_SEG9 <sup>(3)</sup> /<br>ADC1_IN19/<br>COMP1_INP                                 | I/O  | FT <sup>(5)</sup> | x        | x   | х              | HS               | х    | x  | Port D3                        | Timer 1 - trigger / LCD<br>segment 9 /<br>ADC1_IN19/Comparator 1<br>positive input                                           |

| 57     | 45         | -      | PD4/TIM1_CH2<br>/LCD_SEG18 <sup>(3)</sup> /<br>ADC1_IN10/<br>COMP1_INP                                 | I/O  | FT <sup>(5)</sup> | x        | x   | х              | HS               | х    | x  | Port D4                        | Timer 1 - channel 2 / LCD<br>segment 18 /<br>ADC1_IN10/Comparator 1<br>positive input                                        |

| -      | -          | 33     | PD4/TIM1_CH2<br>/LCD_SEG18 <sup>(3)</sup> /<br>ADC1_IN10/SPI2_MISO/<br>COMP1_INP                       | I/O  | FT <sup>(5)</sup> | x        | x   | х              | HS               | х    | x  | Port D4                        | Timer 1 - channel 2 / LCD<br>segment 18 /<br>ADC1_IN10/SPI2 master<br>in/slave out/Comparator 1<br>positive input            |

| Table 5. High-density STM8AL3x8x pin description (continued) |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

| n      | Pin<br>umb | er     |                                                                                             |      |           | I        | npu | t              | 0                | utpı | ıt | _                              |                                                                                                                     |  |

|--------|------------|--------|---------------------------------------------------------------------------------------------|------|-----------|----------|-----|----------------|------------------|------|----|--------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| LQFP80 | LQFP64     | LQFP48 | Pin name                                                                                    | Type | I/O level | floating | wpu | Ext. interrupt | High sink/source | OD   | dd | Main function<br>(after reset) | Default alternate function                                                                                          |  |

| 5      | 1          | 1      | PA0 <sup>(8)</sup> / <i>[USART1_CK]</i> <sup>(2)</sup> /<br>SWIM/BEEP/IR_TIM <sup>(9)</sup> | I/O  | -         | x        | x   | x              | HS               | x    | x  | Port A0                        | [USART1 synchronous<br>clock] <sup>(2)</sup> / SWIM input and<br>output /<br>Beep output / Infrared Timer<br>output |  |

| 68     | 56         | 40     | V <sub>SS2</sub>                                                                            | S    | -         | -        | -   | -              | -                | -    | -  | IOs ground voltage             |                                                                                                                     |  |

| 67     | 55         | 39     | V <sub>DD2</sub>                                                                            | S    | -         | -        | -   | -              | -                | -    | -  | IOs supply voltage             |                                                                                                                     |  |

| 48     | -          | -      | V <sub>SS4</sub>                                                                            | S    | -         | -        | -   | -              | -                | -    | -  | IOs ground voltage             |                                                                                                                     |  |

| 47     | -          | -      | V <sub>DD4</sub>                                                                            | S    | -         | -        | -   | -              | -                | -    | -  | IOs supply voltage             |                                                                                                                     |  |

Table 5. High-density STM8AL3x8x pin description (continued)

1. At power-up, the PA1/NRST pin is a reset input pin with pull-up. To be used as a general purpose pin (PA1), it can be configured only as output open-drain or push-pull, not as a general purpose input. Refer to Section *Configuring NRST/PA1 pin as general purpose output* in STM8L051/L052 Value Line, STM8L151/L152, STM8L162, STM8AL31, STM8AL3L MCU lines reference manual (RM0031).

- 2. [] Alternate function remapping option (if the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

- 3. Available onSTM8AL3L8xdevices only.

- 4. A pull-up is applied to PB0 and PB4 during the reset phase. These two pins are input floating after reset release.

- 5. In the 5 V tolerant I/Os, the protection diode to  $V_{DD}$  is not implemented.

- In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up and protection diode to V<sub>DD</sub> are not implemented).

- 7. Available on STM8AL3L8x devices only. On STM8AL318x devices it is reserved and must be tied to  $V_{DD}$ .

- 8. The PA0 pin is in input pull-up during the reset phase and after reset release.

- 9. High Sink LED driver capability available on PA0.

#### System configuration options

As shown in *Table 5: High-density* STM8AL3x8x pin description, some alternate functions can be remapped on different I/O ports by programming one of the two remapping registers described in the "Routing interface (RI) and system configuration controller" section in STM8L051/L052 Value Line, STM8L151/L152, STM8L162, STM8AL31, STM8AL3L MCU lines reference manual (RM0031).

Note: The slope control of all GPIO pins, except true open drain pins, are programmable. By default the slope control is limited to 2 MHz.

| Address                      | Block | Register label         | Register name                           | Reset status |  |

|------------------------------|-------|------------------------|-----------------------------------------|--------------|--|

| 0x00 50CA                    |       | CLK_CSSR               | Clock security system register          | 0x00         |  |

| 0x00 50CB                    | -     | CLK_CBEEPR             | Clock BEEP register                     | 0x00         |  |

| 0x00 50CC                    |       | CLK_HSICALR            | HSI calibration register                | 0xXX         |  |

| 0x00 50CD                    | CLK   | CLK_HSITRIMR           | HSI clock calibration trimming register | 0x00         |  |

| 0x00 50CE                    |       | CLK_HSIUNLCKR          | HSI unlock register                     | 0x00         |  |

| 0x00 50CF                    | -     | CLK_REGCSR             | Main regulator control status register  | 0bxx11 100X  |  |

| 0x00 50D0                    | -     | CLK_PCKENR3            | Peripheral clock gating register 3      | 0x00         |  |

| 0x00 50D1<br>to<br>0x00 50D2 |       |                        | Reserved area (2 byte)                  |              |  |

| 0x00 50D3                    |       | WWDG_CR                | WWDG control register                   | 0x7F         |  |

| 0x00 50D4                    | WWDG  | WWDG_WR                | WWDR window register                    | 0x7F         |  |

| 0x00 50D5<br>to<br>00 50DF   |       | F                      | Reserved area (11 byte)                 |              |  |

| 0x00 50E0                    |       | IWDG_KR                | IWDG key register                       | 0xXX         |  |

| 0x00 50E1                    | IWDG  | IWDG_PR                | IWDG prescaler register                 | 0x00         |  |

| 0x00 50E2                    |       | IWDG_RLR               | IWDG reload register                    | 0xFF         |  |

| 0x00 50E3<br>to<br>0x00 50EF |       | F                      | Reserved area (13 byte)                 |              |  |

| 0x00 50F0                    |       | BEEP_CSR1              | BEEP control/status register 1          | 0x00         |  |

| 0x00 50F1<br>0x00 50F2       | BEEP  |                        | Reserved area (2 byte)                  | 1            |  |

| 0x00 50F3                    |       | BEEP_CSR2              | BEEP control/status register 2          | 0x1F         |  |

| 0x00 50F4<br>to0x00 513F     |       | F                      | Reserved area (76 byte)                 |              |  |

| 0x00 5140                    |       | RTC_TR1                | Time register 1                         | 0x00         |  |

| 0x00 5141                    | RTC   | RTC_TR2                | Time register 2                         | 0x00         |  |

| 0x00 5142                    |       | RTC_TR3                | Time register 3                         | 0x00         |  |

| 0x00 5143                    |       |                        | Reserved area (1 byte)                  |              |  |

| 0x00 5144                    |       | RTC_DR1                | Date register 1                         | 0x01         |  |

| 0x00 5145                    | RTC   | RTC_DR2                | Date register 2                         | 0x21         |  |

| 0x00 5146                    | 1     | RTC_DR3                | Date register 3                         | 0x00         |  |

| 0x00 5147                    |       | Reserved area (1 byte) |                                         |              |  |

Table 9. General hardware register map (continued)

| Address   | Block    | Register label | Register name                          | Reset status |

|-----------|----------|----------------|----------------------------------------|--------------|

| 0x00 52B0 |          | TIM1_CR1       | TIM1 control register 1                | 0x00         |

| 0x00 52B1 |          | TIM1_CR2       | TIM1 control register 2                | 0x00         |

| 0x00 52B2 |          | TIM1_SMCR      | TIM1 Slave mode control register       | 0x00         |

| 0x00 52B3 |          | TIM1_ETR       | TIM1 external trigger register         | 0x00         |

| 0x00 52B4 |          | TIM1_DER       | TIM1 DMA1 request enable register      | 0x00         |

| 0x00 52B5 |          | TIM1_IER       | TIM1 Interrupt enable register         | 0x00         |

| 0x00 52B6 |          | TIM1_SR1       | TIM1 status register 1                 | 0x00         |

| 0x00 52B7 |          | TIM1_SR2       | TIM1 status register 2                 | 0x00         |

| 0x00 52B8 |          | TIM1_EGR       | TIM1 event generation register         | 0x00         |

| 0x00 52B9 |          | TIM1_CCMR1     | TIM1 Capture/Compare mode register 1   | 0x00         |

| 0x00 52BA |          | TIM1_CCMR2     | TIM1 Capture/Compare mode register 2   | 0x00         |

| 0x00 52BB |          | TIM1_CCMR3     | TIM1 Capture/Compare mode register 3   | 0x00         |

| 0x00 52BC |          | TIM1_CCMR4     | TIM1 Capture/Compare mode register 4   | 0x00         |

| 0x00 52BD |          | TIM1_CCER1     | TIM1 Capture/Compare enable register 1 | 0x00         |

| 0x00 52BE |          | TIM1_CCER2     | TIM1 Capture/Compare enable register 2 | 0x00         |

| 0x00 52BF |          | TIM1_CNTRH     | TIM1 counter high                      | 0x00         |

| 0x00 52C0 | TIM1     | TIM1_CNTRL     | TIM1 counter low                       | 0x00         |

| 0x00 52C1 | 1 11/1 1 | TIM1_PSCRH     | TIM1 prescaler register high           | 0x00         |

| 0x00 52C2 |          | TIM1_PSCRL     | TIM1 prescaler register low            | 0x00         |

| 0x00 52C3 |          | TIM1_ARRH      | TIM1 Auto-reload register high         | 0xFF         |

| 0x00 52C4 |          | TIM1_ARRL      | TIM1 Auto-reload register low          | 0xFF         |

| 0x00 52C5 |          | TIM1_RCR       | TIM1 Repetition counter register       | 0x00         |

| 0x00 52C6 |          | TIM1_CCR1H     | TIM1 Capture/Compare register 1 high   | 0x00         |

| 0x00 52C7 |          | TIM1_CCR1L     | TIM1 Capture/Compare register 1 low    | 0x00         |

| 0x00 52C8 |          | TIM1_CCR2H     | TIM1 Capture/Compare register 2 high   | 0x00         |

| 0x00 52C9 |          | TIM1_CCR2L     | TIM1 Capture/Compare register 2 low    | 0x00         |

| 0x00 52CA |          | TIM1_CCR3H     | TIM1 Capture/Compare register 3 high   | 0x00         |

| 0x00 52CB |          | TIM1_CCR3L     | TIM1 Capture/Compare register 3 low    | 0x00         |

| 0x00 52CC |          | TIM1_CCR4H     | TIM1 Capture/Compare register 4 high   | 0x00         |

| 0x00 52CD |          | TIM1_CCR4L     | TIM1 Capture/Compare register 4 low    | 0x00         |

| 0x00 52CE |          | TIM1_BKR       | TIM1 break register                    | 0x00         |

| 0x00 52CF |          | TIM1_DTR       | TIM1 dead-time register                | 0x00         |

| 0x00 52D0 |          | TIM1_OISR      | TIM1 output idle state register        | 0x00         |

| 0x00 52D1 |          | TIM1_DCR1      | DMA1 control register 1                | 0x00         |

Table 9. General hardware register map (continued)

|                              |       | erennin debug me | adie/interrupt controller registers (continued | /               |

|------------------------------|-------|------------------|------------------------------------------------|-----------------|

| Address                      | Block | Register label   | Register name                                  | Reset<br>status |

| 0x00 7F90                    |       | DM_BK1RE         | DM breakpoint 1 register extended byte         | 0xFF            |

| 0x00 7F91                    |       | DM_BK1RH         | DM breakpoint 1 register high byte             | 0xFF            |

| 0x00 7F92                    |       | DM_BK1RL         | DM breakpoint 1 register low byte              | 0xFF            |

| 0x00 7F93                    |       | DM_BK2RE         | DM breakpoint 2 register extended byte         | 0xFF            |

| 0x00 7F94                    |       | DM_BK2RH         | DM breakpoint 2 register high byte             | 0xFF            |

| 0x00 7F95                    | DM    | DM_BK2RL         | DM breakpoint 2 register low byte              | 0xFF            |

| 0x00 7F96                    |       | DM_CR1           | DM Debug module control register 1             | 0x00            |

| 0x00 7F97                    |       | DM_CR2           | DM Debug module control register 2             | 0x00            |

| 0x00 7F98                    |       | DM_CSR1          | DM Debug module control/status register 1      | 0x10            |

| 0x00 7F99                    |       | DM_CSR2          | DM Debug module control/status register 2      | 0x00            |

| 0x00 7F9A                    |       | DM_ENFCTR        | DM enable function register                    | 0xFF            |

| 0x00 7F9B<br>to<br>0x00 7F9F |       |                  | Reserved area (5 byte)                         |                 |

#### Table 10. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

# 9 Electrical parameters

### 9.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

#### 9.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A$ = 25 °C and  $T_A$  =  $T_A$  max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production.

#### 9.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25 \text{ °C}$ ,  $V_{DD} = 3 \text{ V}$ . They are given only as design guidelines and are not tested.

Typical ADC and DAC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range.

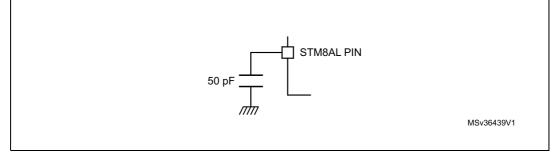

### 9.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

### 9.1.4 Loading capacitor

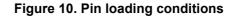

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

# 9.3 Operating conditions

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

### 9.3.1 General operating conditions

| Symbol                             | Parameter                            |                                                          | operating conditions                        | Min.                | Max. | Unit |

|------------------------------------|--------------------------------------|----------------------------------------------------------|---------------------------------------------|---------------------|------|------|

| f <sub>SYSCLK</sub> <sup>(1)</sup> | System clock<br>frequency            | 1.65 V                                                   | 0                                           | 16                  | MHz  |      |

| $V_{DD}$                           | Standard operating voltage           | BOR detector e                                           | nabled                                      | 1.65 <sup>(2)</sup> | 3.6  | V    |

| M                                  | Analog operating                     | ADC and DAC not used                                     | Must be at the same                         | 1.65 <sup>(2)</sup> | 3.6  | V    |

| V <sub>DDA</sub>                   | voltage                              | ADC or DAC<br>used                                       | potential as V <sub>DD</sub>                | 1.8                 | 3.6  | V    |

|                                    | Power dissipation at                 | LQFP80                                                   | -                                           | -                   | 288  |      |

| P <sub>D</sub> <sup>(3)</sup>      | T <sub>A</sub> = 85 °C for suffix A  | LQFP64                                                   | -                                           | -                   | 288  |      |

|                                    | devices                              | LQFP48                                                   | -                                           | -                   | 288  |      |

|                                    | Power dissipation at                 | LQFP80                                                   | -                                           | -                   | 131  | mW   |

|                                    | T <sub>A</sub> = 125 °C for suffix C | LQFP64                                                   | -                                           | _                   | 104  |      |

|                                    | devices                              | LQFP48                                                   | -                                           | -                   | 77   |      |

| т                                  |                                      | 1.65 V ≤V <sub>DD</sub> <<br>3.6 V (A suffix<br>version) | -                                           | -40                 | 85   |      |

| T <sub>A</sub>                     | Temperature range                    | 1.65 V ≤V <sub>DD</sub> <<br>3.6 V (C suffix<br>version) | -                                           | -40                 | 125  | °C   |

| ТJ                                 | - Junction temperature               |                                                          | C ≤T <sub>A</sub> < 85 °C<br>uffix version) | -40                 | 105  |      |

| IJ                                 | range                                |                                                          | ≤ T <sub>A</sub> < 125 °C<br>uffix version) | -40                 | 130  |      |

### Table 19. General operating conditions

1.  $f_{SYSCLK} = f_{CPU}$

2. 1.8 V at power-up, 1.65 V at power-down if BOR is disabled.

3. To calculate  $P_{Dmax}(T_A)$ , use the formula  $P_{Dmax}=(T_{Jmax} - T_A)/\Theta_{JA}$  with  $T_{Jmax}$  in this table and  $\Theta_{JA}$  in "Thermal characteristics" table.

#### 9.3.2 Embedded reset and power control block characteristics

|                   | Table 20. Embedded             | reset and power c                                 | ontrol block        | character | istics              |      |

|-------------------|--------------------------------|---------------------------------------------------|---------------------|-----------|---------------------|------|

| Symbol            | Parameter                      | Conditions                                        | Min.                | Тур.      | Max.                | Unit |

| +                 | V <sub>DD</sub> rise time rate | BOR detector<br>enabled                           | 0 <sup>(1)</sup>    | -         | <sub>∞</sub> (1)    | µs/V |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate | BOR detector<br>enabled                           | 20 <sup>(1)</sup>   | -         | <sub>∞</sub> (1)    | µs/V |

| t <sub>TEMP</sub> | Reset release delay            | V <sub>DD</sub> rising<br>BOR detector<br>enabled | -                   | 3         | -                   | ms   |

| V <sub>PDR</sub>  | Power-down reset threshold     | Falling edge                                      | 1.3                 | 1.5       | 1.65 <sup>(2)</sup> |      |

|                   | Brown-out reset threshold 0    | Falling edge                                      | 1.67                | 1.7       | 1.74 <sup>(2)</sup> |      |

| V <sub>BOR0</sub> | (BOR_TH[2:0]=000)              | Rising edge                                       | 1.69 <sup>(2)</sup> | 1.75      | 1.80                |      |

| N/                | Brown-out reset threshold 1    | Falling edge                                      | 1.87                | 1.93      | 1.97 <sup>(2)</sup> |      |

| V <sub>BOR1</sub> | (BOR_TH[2:0]=001)              | Rising edge                                       | 1.96 <sup>(2)</sup> | 2.04      | 2.07                |      |

| N/                | Brown-out reset threshold 2    | Falling edge                                      | 2.22                | 2.3       | 2.35 <sup>(2)</sup> | V    |

| V <sub>BOR2</sub> | (BOR_TH[2:0]=010)              | Rising edge                                       | 2.31 <sup>(2)</sup> | 2.41      | 2.44                |      |

|                   | Brown-out reset threshold 3    | Falling edge                                      | 2.45                | 2.55      | 2.60 <sup>(2)</sup> |      |

| V <sub>BOR3</sub> | (BOR_TH[2:0]=011)              | Rising edge                                       | 2.54 <sup>(2)</sup> | 2.66      | 2.7                 |      |

|                   | Brown-out reset threshold 4    | Falling edge                                      | 2.68                | 2.80      | 2.85 <sup>(2)</sup> |      |

| V <sub>BOR4</sub> | (BOR_TH[2:0]=100)              | Rising edge                                       | 2.78 <sup>(2)</sup> | 2.90      | 2.95                |      |

| V                 | DVD threehold 0                | Falling edge                                      | 1.80                | 1.84      | 1.88 <sup>(2)</sup> |      |

| V <sub>PVD0</sub> | PVD threshold 0                | Rising edge                                       | 1.88 <sup>(2)</sup> | 1.94      | 1.99                |      |

| N/                | D) (D three hold 4             | Falling edge                                      | 1.98                | 2.04      | 2.09 <sup>(2)</sup> |      |

| V <sub>PVD1</sub> | PVD threshold 1                | Rising edge                                       | 2.08 <sup>(2)</sup> | 2.14      | 2.18                |      |

| N/                | D) (D threehold 2              | Falling edge                                      | 2.2                 | 2.24      | 2.28 <sup>(2)</sup> |      |

| V <sub>PVD2</sub> | PVD threshold 2                | Rising edge                                       | 2.28 <sup>(2)</sup> | 2.34      | 2.38                |      |

| V                 | D)/D threshold 2               | Falling edge                                      | 2.39                | 2.44      | 2.48 <sup>(2)</sup> |      |

| V <sub>PVD3</sub> | PVD threshold 3                | Rising edge                                       | 2.47 <sup>(2)</sup> | 2.54      | 2.58                | V    |

| N/                | D)/D threehold (               | Falling edge                                      | 2.57                | 2.64      | 2.69 <sup>(2)</sup> |      |

| V <sub>PVD4</sub> | PVD threshold 4                | Rising edge                                       | 2.68 <sup>(2)</sup> | 2.74      | 2.79                |      |

| V                 | D) (D three hold 5             | Falling edge                                      | 2.77                | 2.83      | 2.88 <sup>(2)</sup> |      |

| V <sub>PVD5</sub> | PVD threshold 5                | Rising edge                                       | 2.87 <sup>(2)</sup> | 2.94      | 2.99                | 1    |

| V                 | D) (D three hold C             | Falling edge                                      | 2.97                | 3.05      | 3.09 <sup>(2)</sup> |      |

| V <sub>PVD6</sub> | PVD threshold 6                | Rising edge                                       | 3.08 <sup>(2)</sup> | 3.15      | 3.20                |      |

# Table 20 Embedded reset and nower control block characteristic

Figure 19. Typical  $I_{DD(AH)}$  vs.  $V_{DD}$  (LSI clock source)

#### STM8AL318x STM8AL3L8x

| Symbol           | Parameter                                         | Conditions <sup>(1)</sup>                                                                        | Min.                   | Тур. | Max.                                | Unit |

|------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------|------|-------------------------------------|------|

| V <sub>IL</sub>  | Input low-level voltage                           | Input voltage on all<br>pins                                                                     | Vss-0.3                | -    | 0.3 x V <sub>DD</sub>               | V    |

|                  |                                                   | Input voltage on true<br>open-drain pins (PC0<br>and PC1)<br>with V <sub>DD</sub> < 2 V          |                        | -    | 5.2 <sup>(2)</sup>                  |      |

|                  |                                                   | Input voltage on true open-drain pins (PC0 and PC1) with $V_{DD} \ge 2 V$                        |                        | -    | 5.5 <sup>(2)</sup>                  |      |

| V <sub>IH</sub>  | Input high-level voltage                          | Input voltage on five-<br>volt tolerant (FT) pins<br>with V <sub>DD</sub> < 2 V                  | 0.70 x V <sub>DD</sub> | -    | 5.2 <sup>(2)</sup>                  | V    |

|                  |                                                   | Input voltage on five-<br>volt tolerant (FT) pins<br>with $V_{DD} \ge 2 V$                       |                        | -    | 5.5 <sup>(2)</sup>                  |      |

|                  |                                                   | Input voltage on any other pin                                                                   |                        | -    | V <sub>DD</sub> +0.3 <sup>(2)</sup> |      |

| V.               | Q                                                 | Standard I/Os                                                                                    | -                      | 200  | -                                   | mV   |

| V <sub>hys</sub> | Schmitt trigger voltage hysteresis <sup>(3)</sup> | True open drain I/Os                                                                             | -                      | 200  | -                                   |      |

|                  |                                                   | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os                               | -                      | -    | 50                                  |      |

| I <sub>lkg</sub> | Input leakage current <sup>(4)</sup>              | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>True open drain I/Os                        | -                      | -    | 200                                 | nA   |

|                  |                                                   | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>PA0 with high sink LED<br>driver capability | -                      | -    | 200                                 |      |

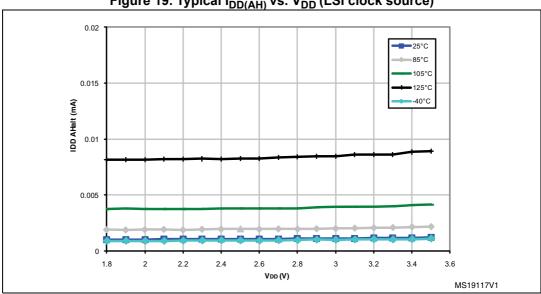

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>   | V <sub>IN</sub> =V <sub>SS</sub>                                                                 | 30 <sup>(6)</sup>      | 45   | 60 <sup>(6)</sup>                   | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                               | -                                                                                                | -                      | 5    | -                                   | pF   |

| Table 41 | . I/O stati | c characteristics |

|----------|-------------|-------------------|

|----------|-------------|-------------------|

1.  $V_{DD}$  = 3.0 V,  $T_A$  = -40 to 125  $^\circ C$  unless otherwise specified.

2. If  $V_{IH}$  maximum is not respected, the injection current must be limited externally to  $I_{INJ(PIN)}$  maximum.

3. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

R<sub>PU</sub> pull-up equivalent resistor based on a resistive transistor (corresponding I<sub>PU</sub> current characteristics described in Figure 28).

6. Guaranteed by characterization results.

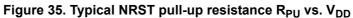

### NRST pin

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                | Parameter                                    | Conditions                                                       | Min.                         | Тур. | Max.                           | Unit |

|-----------------------|----------------------------------------------|------------------------------------------------------------------|------------------------------|------|--------------------------------|------|

| V <sub>IL(NRST)</sub> | NRST input low-level voltage                 | -                                                                | $V_{SS}^{(1)}$               | -    | 0.8 <sup>(1)</sup>             |      |

| V <sub>IH(NRST)</sub> | NRST input high-level voltage <sup>(1)</sup> | -                                                                | 1.4 <sup>(1)</sup>           | -    | V <sub>DD</sub> <sup>(1)</sup> |      |

| Vermeen               | NRST output low-level voltage <sup>(1)</sup> | $I_{OL}$ = 2 mA<br>for 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V | -                            | -    | 0.4 <sup>(1)</sup>             | V    |

| V <sub>OL(NRST)</sub> |                                              | I <sub>OL</sub> = 1.5 mA<br>for V <sub>DD</sub> < 2.7 V          | -                            | -    | 0.4\''                         |      |

| V <sub>HYST</sub>     | NRST input hysteresis                        | -                                                                | 10%V <sub>DD</sub><br>(2)(3) | -    | -                              | mV   |

| R <sub>PU(NRST)</sub> | NRST pull-up equivalent resistor             | -                                                                | 30 <sup>(1)</sup>            | 45   | 60 <sup>(1)</sup>              | kΩ   |

| V <sub>F(NRST)</sub>  | NRST input filtered pulse                    | -                                                                | -                            | -    | 50 <sup>(3)</sup>              | ns   |

| V <sub>NF(NRST)</sub> | NRST input not filtered pulse                | -                                                                | 300 <sup>(3)</sup>           | -    | -                              | 115  |

Table 45. NRST pin characteristics

1. Guaranteed by characterization results.

2. 200 mV min.

3. Guaranteed by design.

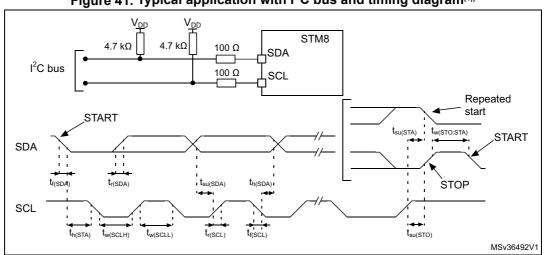

### I<sup>2</sup>C - Inter IC control interface

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{SYSCLK}},$  and  $T_{\text{A}}$  unless otherwise specified.

The STM8AL I<sup>2</sup>C interface (I2C1) meets the requirements of the Standard I<sup>2</sup>C communication protocol described in the following table with the restriction mentioned below:

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                               | Standard mode I <sup>2</sup> C |                     | Fast mode I <sup>2</sup> C <sup>(1)</sup> |                     | Unit |  |

|--------------------------------------------|-----------------------------------------|--------------------------------|---------------------|-------------------------------------------|---------------------|------|--|

|                                            | Faiameter                               | Min. <sup>(2)</sup>            | Max. <sup>(2)</sup> | Min. <sup>(2)</sup>                       | Max. <sup>(2)</sup> | Unit |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                            | -                   | 1.3                                       | -                   |      |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                            | -                   | 0.6                                       | -                   | μs   |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                            | -                   | 100                                       | -                   |      |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0                              | -                   | 0                                         | 900                 |      |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   | -                              | 1000                | -                                         | 300                 | ns   |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   | -                              | 300                 | -                                         | 300                 |      |  |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                            | -                   | 0.6                                       | -                   |      |  |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                            | -                   | 0.6                                       | -                   |      |  |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                            | -                   | 0.6                                       | -                   | μs   |  |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7                            | -                   | 1.3                                       | -                   |      |  |

| Cb                                         | Capacitive load for each bus line       | -                              | 400                 | -                                         | 400                 | pF   |  |

|                                            |                                         |                                |                     |                                           |                     |      |  |

1.  $f_{SYSCLK}$  must be at least equal to 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz).

2. Data based on standard  $\mathsf{I}^2\mathsf{C}$  protocol requirement, not tested in production.

Note: For speeds around 200 kHz, the achieved speed has a  $\pm$ 5% tolerance. For other speed ranges, the achieved speed has a  $\pm$ 2% tolerance. The above variations depend on the accuracy of the external components used.

Figure 41. Typical application with I<sup>2</sup>C bus and timing diagram<sup>(1))</sup>

1. Measurement points are done at CMOS levels: 0.3 x  $V_{\text{DD}}$  and 0.7 x  $V_{\text{DD}}$

#### **Electromagnetic interference (EMI)**

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm IEC61967-2 which specifies the board and the loading of each pin.

| Symbol           | Parameter  | Conditions                                                                      | Monitored            | Max vs. | 11   |

|------------------|------------|---------------------------------------------------------------------------------|----------------------|---------|------|

|                  |            |                                                                                 | frequency band       | 16 MHz  | Unit |

| S <sub>EMI</sub> | Peak level | V <sub>DD</sub> = 3.6 V,                                                        | 0.1 MHz to 30 MHz 10 | 10      | dBµV |

|                  |            | $V_{DD} = 3.6 \text{ V},$<br>$T_A = +25 \text{ °C},$<br>LQFP80<br>conforming to | 30 MHz to 130 MHz    | 4       |      |

|                  |            |                                                                                 | 130 MHz to 1 GHz     | 1       |      |

|                  |            | IEC61967-2                                                                      | EMI Level            | 1.5     | -    |

| Table | 61. | EMI | data | (1) |

|-------|-----|-----|------|-----|

|-------|-----|-----|------|-----|

1. Guaranteed by characterization results.

#### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models are simulated: human body model and charge device model. This test conforms to the ANSI/ESDA/JEDEC JS-001, JESD22-A115 and ANSI/ESD S5.3.1.

| Table 62 | ESD | absolute | maximum | ratings |

|----------|-----|----------|---------|---------|

|----------|-----|----------|---------|---------|

| Symbol                | Ratings                                               | Conditions                                                          | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|---------------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | T <sub>A</sub> = 25 °C, conforming<br>to ANSI/ESDA/<br>JEDEC JS-001 | 2     | 2000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = 25 \ ^{\circ}C$ , conforming to ANSI/ESD S5.3.1              | C4B   | 500                             | V    |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage (machine model)       | $T_A = 25 \ ^{\circ}C$ , conforming to JESD22-A115                  | M2    | 200                             | ſ    |

1. Guaranteed by characterization results.

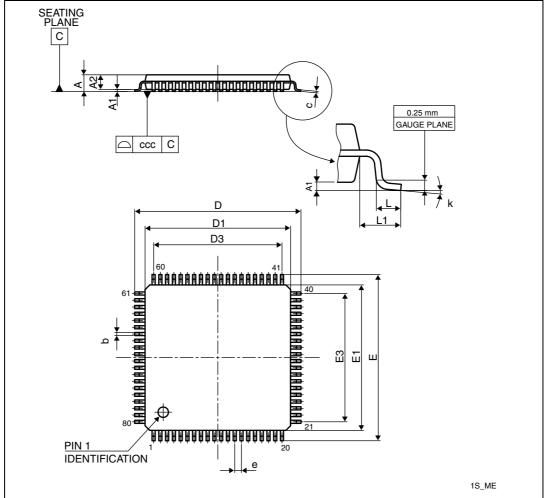

# **10** Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 10.1 LQFP80 package information

Figure 46. LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

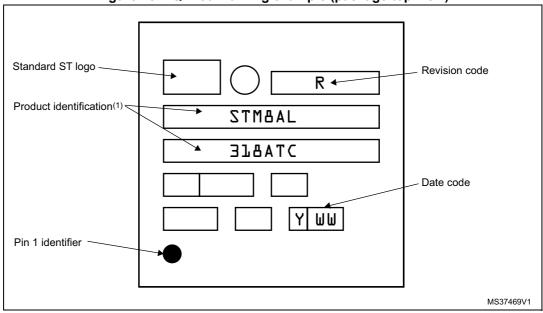

Figure 48. LQFP80 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted to run a qualification activity prior to any decision to use these engineering samples.