Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                       |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM9®                                                                     |

| Core Size                  | 16/32-Bit                                                                 |

| Speed                      | 125MHz                                                                    |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB           |

| Peripherals                | DMA, POR, PWM, WDT                                                        |

| Number of I/O              | 104                                                                       |

| Program Memory Size        | 768KB (768K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 16K × 8                                                                   |

| RAM Size                   | 56K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                              |

| Data Converters            | A/D 24x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 144-LQFP                                                                  |

| Supplier Device Package    | 144-LQFP (20x20)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc2929fbd144-551 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ARM9 microcontroller with CAN, LIN, and USB

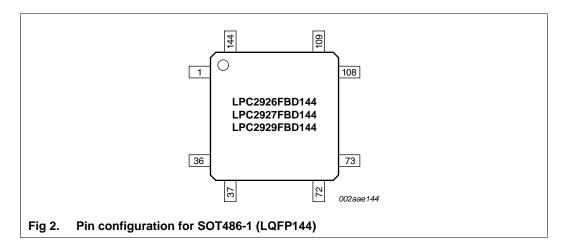

### 5. Pinning information

#### 5.1 Pinning

### 5.2 Pin description

#### 5.2.1 General description

The LPC2926/2927/2929 uses five ports: port 0 with 32 pins, ports 1 and 2 with 28 pins each, port 3 with 16 pins, and port 5 with 2 pins. Port 4 is not used. The pin to which each function is assigned is controlled by the SFSP registers in the System Control Unit (SCU). The functions combined on each port pin are shown in the pin description tables in this section.

#### 5.2.2 LQFP144 pin assignment

| Pin name                      | Pin          | Description             | Description |             |             |  |

|-------------------------------|--------------|-------------------------|-------------|-------------|-------------|--|

|                               |              | Function 0<br>(default) | Function 1  | Function 2  | Function 3  |  |

| TDO                           | 1 <u>[1]</u> | IEEE 1149.1 test d      | ata out     |             |             |  |

| P2[21]/SDI2/<br>PCAP2[1]/D19  | 2[1]         | GPIO2, pin 21           | SPI2 SDI    | PWM2 CAP1   | EXTBUS D19  |  |

| P0[24]/TXD1/<br>TXDC1/SCS2[0] | 3 <u>[1]</u> | GPIO0, pin 24           | UART1 TXD   | CAN1 TXD    | SPI2 SCS0   |  |

| P0[25]/RXD1/<br>RXDC1/SDO2    | 4 <u>[1]</u> | GPIO0, pin 25           | UART1 RXD   | CAN1 RXD    | SPI2 SDO    |  |

| P0[26]/TXD1/SDI2              | 5 <u>[1]</u> | GPIO0, pin 26           | -           | UART1 TXD   | SPI2 SDI    |  |

| P0[27]/RXD1/SCK2              | 6 <u>[1]</u> | GPIO0, pin 27           | -           | UART1 RXD   | SPI2 SCK    |  |

| P0[28]/CAP0[0]/<br>MAT0[0]    | 7 <u>[1]</u> | GPIO0, pin 28           | -           | TIMER0 CAP0 | TIMER0 MAT0 |  |

| P0[29]/CAP0[1]/<br>MAT0[1]    | 8 <u>[1]</u> | GPIO0, pin 29           | -           | TIMER0 CAP1 | TIMER0 MAT1 |  |

| V <sub>DD(IO)</sub>           | 9            | 3.3 V power supply      | / for I/O   |             |             |  |

Table 3.

LQFP144 pin assignment

LPC2926\_27\_29

#### ARM9 microcontroller with CAN, LIN, and USB

| Pin name                                     | Pin                      | Description             | Description                    |             |               |  |  |

|----------------------------------------------|--------------------------|-------------------------|--------------------------------|-------------|---------------|--|--|

|                                              |                          | Function 0<br>(default) | Function 1                     | Function 2  | Function 3    |  |  |

| P2[22]/SCK2/<br>PCAP2[2]/D20                 | 10 <u>[1]</u>            | GPIO2, pin 22           | SPI2 SCK                       | PWM2 CAP2   | EXTBUS D20    |  |  |

| P2[23]/SCS1[0]/<br>PCAP3[0]/D21              | 11 <u>[1]</u>            | GPIO2, pin 23           | SPI1 SCS0                      | PWM3 CAP0   | EXTBUS D21    |  |  |

| P3[6]/SCS0[3]/<br>PMAT1[0]/TXDL1             | 12 <u>[1]</u>            | GPIO3, pin 6            | SPI0 SCS3                      | PWM1 MAT0   | LIN1/UART TXD |  |  |

| P3[7]/SCS2[1]/<br>PMAT1[1]/RXDL1             | 13 <u>[1]</u>            | GPIO3, pin 7            | SPI2 SCS1                      | PWM1 MAT1   | LIN1/UART RXD |  |  |

| P0[30]/CAP0[2]/<br>MAT0[2]                   | 14 <u><sup>[1]</sup></u> | GPIO0, pin 30           | -                              | TIMER0 CAP2 | TIMER0 MAT2   |  |  |

| P0[31]/CAP0[3]/<br>MAT0[3]                   | 15 <u>[1]</u>            | GPIO0, pin 31           | -                              | TIMER0 CAP3 | TIMER0 MAT3   |  |  |

| P2[24]/SCS1[1]/<br>PCAP3[1]/D22              | 16 <u>[1]</u>            | GPIO2, pin 24           | SPI1 SCS1                      | PWM3 CAP1   | EXTBUS D22    |  |  |

| P2[25]/SCS1[2]/<br>PCAP3[2]/D23              | 17 <u>[1]</u>            | GPIO2, pin 25           | SPI1 SCS2                      | PWM3 CAP2   | EXTBUS D23    |  |  |

| V <sub>SS(IO)</sub>                          | 18                       | ground for I/O          |                                |             |               |  |  |

| P5[19]/USB_D+                                | 19 <u>[2]</u>            | GPIO5, pin 19           | USB_D+                         | -           | -             |  |  |

| P5[18]/USB_D-                                | 20 <u>[2]</u>            | GPIO5, pin 18           | USB_D-                         | -           | -             |  |  |

| V <sub>DD(IO)</sub>                          | 21                       | 3.3 V power suppl       | 3.3 V power supply for I/O     |             |               |  |  |

| V <sub>DD(CORE)</sub>                        | 22                       | 1.8 V power suppl       | y for digital core             |             |               |  |  |

| V <sub>SS(CORE)</sub>                        | 23                       | ground for core         |                                |             |               |  |  |

| V <sub>SS(IO)</sub>                          | 24                       | ground for I/O          |                                |             |               |  |  |

| P3[8]/SCS2[0]/<br>PMAT1[2]                   | 25 <u>[1]</u>            | GPIO3, pin 8            | SPI2 SCS0                      | PWM1 MAT2   | -             |  |  |

| P3[9]/SDO2/<br>PMAT1[3]                      | 26 <u>[1]</u>            | GPIO3, pin 9            | SPI2 SDO                       | PWM1 MAT3   | -             |  |  |

| P2[26]/CAP0[2]/<br>MAT0[2]/EI6               | 27 <u>[1]</u>            | GPIO2, pin 26           | TIMER0 CAP2                    | TIMER0 MAT2 | EXTINT6       |  |  |

| P2[27]/CAP0[3]/<br>MAT0[3]/EI7               | 28 <u>[1]</u>            | GPIO2, pin 27           | TIMER0 CAP3                    | TIMER0 MAT3 | EXTINT7       |  |  |

| P1[27]/CAP1[2]/<br>TRAP2/PMAT3[3]            | 29 <u>[1]</u>            | GPIO1, pin 27           | TIMER1 CAP2, ADC2<br>EXT START | PWM TRAP2   | PWM3 MAT3     |  |  |

| P1[26]/PMAT2[0]/<br>TRAP3/PMAT3[2]           | 30 <u>[1]</u>            | GPIO1, pin 26           | PWM2 MAT0                      | PWM TRAP3   | PWM3 MAT2     |  |  |

| V <sub>DD(IO)</sub>                          | 31                       | 3.3 V power suppl       | y for I/O                      |             |               |  |  |

| P1[25]/PMAT1[0]/<br>USB_VBUS/<br>PMAT3[1]    | 32 <u>[1]</u>            | GPIO1, pin 25           | PWM1 MAT0                      | USB_VBUS    | PWM3 MAT1     |  |  |

| P1[24]/PMAT0[0]/<br>USB_CONNECT/<br>PMAT3[0] | 33 <u>[1]</u>            | GPIO1, pin 24           | PWM0 MAT0                      | USB_CONNECT | PWM3 MAT0     |  |  |

| P1[23]/RXD0/<br>USB_SSPND/CS5                | 34 <u>[1]</u>            | GPIO1, pin 23           | UART0 RXD                      | USB_SSPND   | EXTBUS CS5    |  |  |

#### Table 3. LQFP144 pin assignment ...continued

LPC2926\_27\_29

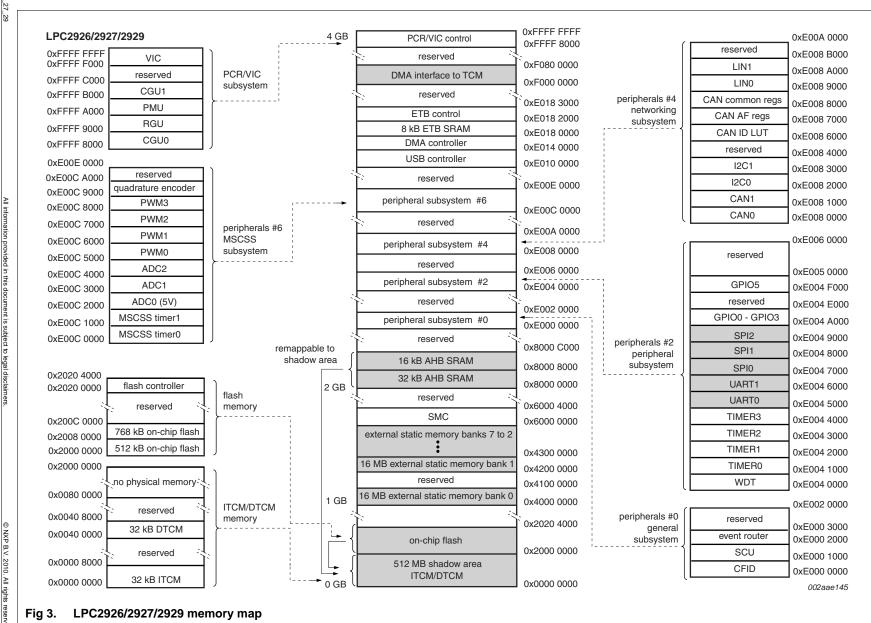

#### 6.5 Memory map

NXP Semiconductors

ARM9 microcontroller with CAN, LIN, and USB

14 of 95

Product data

sheet

Rev.

ъ

28

September

2010

ARM9 microcontroller with CAN, LIN, and USB

#### 6.6 Reset, debug, test, and power description

#### 6.6.1 Reset and power-up behavior

The LPC2926/2927/2929 contains external reset input and internal power-up reset circuits. This ensures that a reset is extended internally until the oscillators and flash have reached a stable state. See <u>Section 8</u> for trip levels of the internal power-up reset circuit<sup>1</sup>. See <u>Section 9</u> for characteristics of the several start-up and initialization times. <u>Table 4</u> shows the reset pin.

| Table 4. | Reset pin |                                                        |

|----------|-----------|--------------------------------------------------------|

| Symbol   | Direction | Description                                            |

| RST      | IN        | external reset input, active LOW; pulled up internally |

At activation of the RST pin the JTAGSEL pin is sensed as logic LOW. If this is the case the LPC2926/2927/2929 is assumed to be connected to debug hardware, and internal circuits re-program the source for the BASE\_SYS\_CLK to be the crystal oscillator instead of the Low-Power Ring Oscillator (LP\_OSC). This is required because the clock rate when running at LP\_OSC speed is too low for the external debugging environment.

#### 6.6.2 Reset strategy

The LPC2926/2927/2929 contains a central module, the Reset Generator Unit (RGU) in the Power, Clock and Reset Subsystem (PCRSS), which controls all internal reset signals towards the peripheral modules. The RGU provides individual reset control as well as the monitoring functions needed for tracing a reset back to source.

#### 6.6.3 IEEE 1149.1 interface pins (JTAG boundary scan test)

The LPC2926/2927/2929 contains boundary-scan test logic according to IEEE 1149.1, also referred to in this document as Joint Test Action Group (JTAG). The boundary-scan test pins can be used to connect a debugger probe for the embedded ARM processor. Pin JTAGSEL selects between boundary-scan mode and debug mode. <u>Table 5</u> shows the boundary scan test pins.

| Symbol  | Description                                                                                                                                       |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAGSEL | TAP controller select input. LOW level selects ARM debug mode and HIGH level<br>selects boundary scan and flash programming; pulled up internally |

| TRST    | test reset input; pulled up internally (active LOW)                                                                                               |

| TMS     | test mode select input; pulled up internally                                                                                                      |

| TDI     | test data input, pulled up internally                                                                                                             |

| TDO     | test data output                                                                                                                                  |

| TCK     | test clock input                                                                                                                                  |

Table 5. IEEE 1149.1 boundary-scan test and debug interface

LPC2926 27 29

<sup>1.</sup> Only for 1.8 V power sources

All information provided in this document is subject to legal disclaimers.

#### ARM9 microcontroller with CAN, LIN, and USB

#### 6.6.3.1 ETM/ETB

The ETM provides real-time trace capability for deeply embedded processor cores. It outputs information about processor execution to a trace buffer. A software debugger allows configuration of the ETM using a JTAG interface and displays the trace information that has been captured in a format that a user can easily understand. The ETB stores trace data produced by the ETM.

The ETM/ETB module has the following features:

- Closely tracks the instructions that the ARM core is executing.

- On-chip trace data storage (ETB).

- All registers are programmed through JTAG interface.

- Does not consume power when trace is not being used.

- THUMB/Java instruction set support.

#### 6.6.4 Power supply pins

Table 6 shows the power supply pins.

| Table 6. Power supply pins |                                              |  |  |

|----------------------------|----------------------------------------------|--|--|

| Symbol                     | Description                                  |  |  |

| V <sub>DD(CORE)</sub>      | digital core supply 1.8 V                    |  |  |

| V <sub>SS(CORE)</sub>      | digital core ground (digital core, ADC0/1/2) |  |  |

| V <sub>DD(IO)</sub>        | I/O pins supply 3.3 V                        |  |  |

| V <sub>SS(IO)</sub>        | I/O pins ground                              |  |  |

| V <sub>DD(OSC_PLL)</sub>   | oscillator and PLL supply                    |  |  |

| V <sub>SS(OSC)</sub>       | oscillator ground                            |  |  |

| V <sub>SS(PLL)</sub>       | PLL ground                                   |  |  |

| V <sub>DDA(ADC3V3)</sub>   | ADC1 and ADC2 3.3 V supply                   |  |  |

| V <sub>DDA(ADC5V0)</sub>   | ADC0 5.0 V supply                            |  |  |

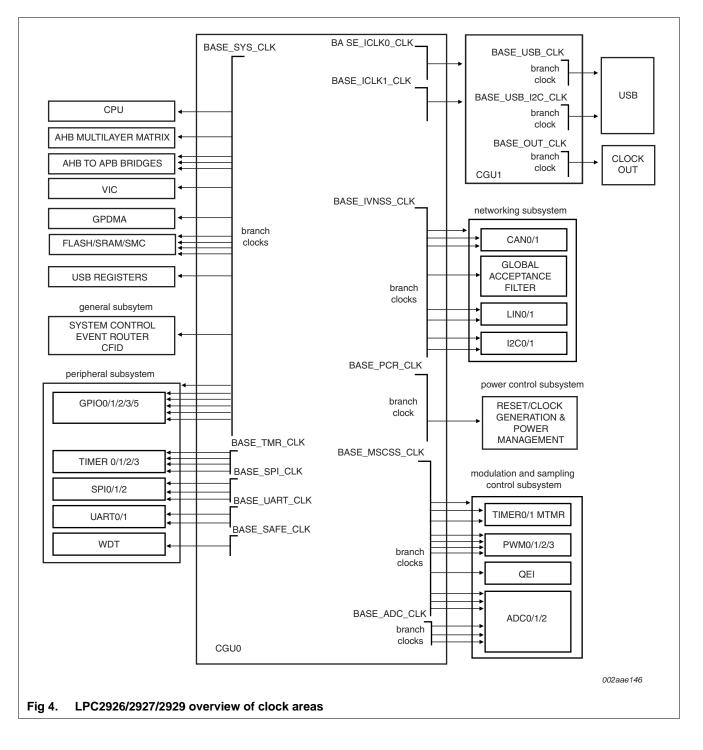

#### 6.7 Clocking strategy

#### 6.7.1 Clock architecture

The LPC2926/2927/2929 contains several different internal clock areas. Peripherals like Timers, SPI, UART, CAN and LIN have their own individual clock sources called base clocks. All base clocks are generated by the Clock Generator Unit (CGU0). They may be unrelated in frequency and phase and can have different clock sources within the CGU.

The system clock for the CPU and AHB Bus infrastructure has its own base clock. This means most peripherals are clocked independently from the system clock. See Figure 4 for an overview of the clock areas within the device.

Within each clock area there may be multiple branch clocks, which offers very flexible control for power-management purposes. All branch clocks are outputs of the Power Management Unit (PMU) and can be controlled independently. Branch clocks derived from the same base clock are synchronous in frequency and phase. See Section 6.16 for more details of clock and power control within the device.

#### ARM9 microcontroller with CAN, LIN, and USB

Two of the base clocks generated by the CGU0 are used as input into a second, dedicated CGU (CGU1). The CGU1 uses its own PLL and fractional dividers to generate two base clocks for the USB controller and one base clock for an independent clock output.

#### ARM9 microcontroller with CAN, LIN, and USB

#### 6.7.2 Base clock and branch clock relationship

<u>Table 7</u> contains an overview of all the base blocks in the LPC2926/2927/2929 and their derived branch clocks. A short description is given of the hardware parts that are clocked with the individual branch clocks. In relevant cases more detailed information can be found in the specific subsystem description. Some branch clocks have special protection since they clock vital system parts of the device and should not be switched off. See Section 6.16.5 for more details of how to control the individual branch clocks.

| Base clock     | Branch clock name | Parts of the device clocked<br>by this branch clock | Remarl |

|----------------|-------------------|-----------------------------------------------------|--------|

| BASE_SAFE_CLK  | CLK_SAFE          | watchdog timer                                      | [1]    |

| BASE_SYS_CLK   | CLK_SYS_CPU       | ARM968E-S and TCMs                                  |        |

|                | CLK_SYS_SYS       | AHB bus infrastructure                              |        |

|                | CLK_SYS_PCRSS     | AHB side of bridge in PCRSS                         |        |

|                | CLK_SYS_FMC       | Flash Memory Controller                             |        |

|                | CLK_SYS_RAM0      | Embedded SRAM Controller 0<br>(32 kB)               |        |

|                | CLK_SYS_RAM1      | Embedded SRAM Controller 1 (16 kB)                  |        |

|                | CLK_SYS_SMC       | External Static Memory<br>Controller                |        |

|                | CLK_SYS_GESS      | General Subsystem                                   |        |

|                | CLK_SYS_VIC       | Vectored Interrupt Controller                       |        |

|                | CLK_SYS_PESS      | Peripheral Subsystem                                | [2][3] |

|                | CLK_SYS_GPIO0     | GPIO bank 0                                         |        |

|                | CLK_SYS_GPIO1     | GPIO bank 1                                         |        |

|                | CLK_SYS_GPIO2     | GPIO bank 2                                         |        |

|                | CLK_SYS_GPIO3     | GPIO bank 3                                         |        |

|                | CLK_SYS_GPIO5     | GPIO bank 5                                         |        |

|                | CLK_SYS_IVNSS_A   | AHB side of bridge of IVNSS                         |        |

|                | CLK_SYS_MSCSS_A   | AHB side of bridge of MSCSS                         |        |

|                | CLK_SYS_DMA       | GPDMA                                               |        |

|                | CLK_SYS_USB       | USB registers                                       |        |

| BASE_PCR_CLK   | CLK_PCR_SLOW      | PCRSS, CGU, RGU and PMU logic clock                 | [1][4] |

| BASE_IVNSS_CLK | CLK_IVNSS_APB     | APB side of the IVNSS                               |        |

|                | CLK_IVNSS_CANCA   | CAN controller Acceptance<br>Filter                 |        |

|                | CLK_IVNSS_CANC0   | CAN channel 0                                       |        |

|                | CLK_IVNSS_CANC1   | CAN channel 1                                       |        |

|                | CLK_IVNSS_I2C0    | I2C0                                                |        |

|                | CLK_IVNSS_I2C1    | I2C1                                                |        |

|                | CLK_IVNSS_LIN0    | LIN channel 0                                       |        |

Table 7. CGU0 base clock and branch clock overview

\_ . . . . .

\_. .

### LPC2926/2927/2929

#### ARM9 microcontroller with CAN, LIN, and USB

| Sector number | Sector size (kB) | Sector base address |

|---------------|------------------|---------------------|

| 11            | 8                | 0x2000 0000         |

| 12            | 8                | 0x2000 2000         |

| 13            | 8                | 0x2000 4000         |

| 14            | 8                | 0x2000 6000         |

| 15            | 8                | 0x2000 8000         |

| 16            | 8                | 0x2000 A000         |

| 17            | 8                | 0x2000 C000         |

| 18            | 8                | 0x2000 E000         |

| 0             | 64               | 0x2001 0000         |

| 1             | 64               | 0x2002 0000         |

| 2             | 64               | 0x2003 0000         |

| 3 <u>[1]</u>  | 64               | 0x2004 0000         |

| 4 <u>[1]</u>  | 64               | 0x2005 0000         |

| 5 <u>[1]</u>  | 64               | 0x2006 0000         |

| 6 <u>[1]</u>  | 64               | 0x2007 0000         |

| 7[1]          | 64               | 0x2008 0000         |

| 8[1]          | 64               | 0x2009 0000         |

| 9[1]          | 64               | 0x200A 0000         |

| 10 <u>[1]</u> | 64               | 0x200B 0000         |

Table 10 gives an overview of the flash-sector base addresses.

.

[1] Availability of sector 3 to sector 10 depends on device type, see Section 3 "Ordering information".

The index sector is a special sector in which the JTAG access protection and sector security are located. The address space becomes visible by setting the FS\_ISS bit and overlaps the regular flash sector's address space.

Note that the index sector, once programmed, cannot be erased. Any flash operation must be executed out of SRAM (internal or external).

#### 6.8.5 Flash bridge wait-states

To eliminate the delay associated with synchronizing flash-read data, a predefined number of wait-states must be programmed. These depend on flash memory response time and system clock period. The minimum wait-states value can be calculated with the following formulas:

Synchronous reading:

$$WST > \frac{t_{acc(clk)}}{t_{t_{clk(sys)}}} - 1$$

(1)

Asynchronous reading:

$$WST > \frac{t_{acc(addr)}}{t_{tclk(sys)}} - 1$$

<sup>(2)</sup>

PC2926\_27\_29 Product data sheet

#### ARM9 microcontroller with CAN, LIN, and USB

#### 6.13.4 UARTs

The LPC2926/2927/2929 contains two identical UARTs located at different peripheral base addresses. The key features are:

- 16-byte receive and transmit FIFOs.

- Register locations conform to 550 industry standard.

- Receiver FIFO trigger points at 1 byte, 4 bytes, 8 bytes and 14 bytes.

- Built-in baud rate generator.

- Support for RS-485/9-bit mode allows both software address detection and automatic address detection using 9-bit mode.

The UART is commonly used to implement a serial interface such as RS232. The LPC2926/2927/2929 contains two industry-standard 550 UARTs with 16-byte transmit and receive FIFOs, but they can also be put into 450 mode without FIFOs.

**Remark:** The LIN controller can be configured to provide two additional standard UART interfaces (see <u>Section 6.14.2</u>).

#### 6.13.4.1 Pin description

The UART pins are combined with other functions on the port pins of the LPC2926/2927/2929. Table 17 shows the UART pins (x runs from 0 to 1).

| Symbol    | Pin name | Direction | Description                         |

|-----------|----------|-----------|-------------------------------------|

| UARTx TXD | TXDx     | OUT       | UART channel x transmit data output |

| UARTx RXD | RXDx     | IN        | UART channel x receive data input   |

#### 6.13.4.2 Clock description

The UART modules are clocked by two different clocks; CLK\_SYS\_PESS and CLK\_UARTx (x = 0 to 1), see <u>Section 6.7.2</u>. Note that each UART has its own CLK\_UARTx branch clock for power management. The frequency of all CLK\_UARTx clocks is identical since they are derived from the same base clock BASE\_CLK\_UART. The register interface towards the system bus is clocked by CLK\_SYS\_PESS. The baud generator is clocked by the CLK\_UARTx.

#### 6.13.5 Serial Peripheral Interface (SPI)

The LPC2926/2927/2929 contains three Serial Peripheral Interface modules (SPIs) to allow synchronous serial communication with slave or master peripherals.

The key features are:

- Master or slave operation.

- Each SPI supports up to four slaves in sequential multi-slave operation.

- Supports timer-triggered operation.

- Programmable clock bit rate and prescale based on SPI source clock (BASE\_SPI\_CLK), independent of system clock.

- Separate transmit and receive FIFO memory buffers; 16 bits wide, 32 locations deep.

#### ARM9 microcontroller with CAN, LIN, and USB

<u>Figure 8</u> provides an overview of the MSCSS. An AHB-to-APB bus bridge takes care of communication with the AHB system bus. Two internal timers are dedicated to this subsystem. MSCSS timer 0 can be used to generate start pulses for the ADCs and the first PWM. The second timer (MSCSS timer 1) is used to generate 'carrier' signals for the PWMs. These carrier patterns can be used, for example, in applications requiring current control. Several other trigger possibilities are provided for the ADCs (external, cascaded or following a PWM). The capture inputs of both timers can also be used to capture the start pulse of the ADCs.

The PWMs can be used to generate waveforms in which the frequency, duty cycle and rising and falling edges can be controlled very precisely. Capture inputs are provided to measure event phases compared to the main counter. Depending on the applications, these inputs can be connected to digital sensor motor outputs or digital external signals. Interrupt signals are generated on several events to closely interact with the CPU.

The ADCs can be used for any application needing accurate digitized data from analog sources. To support applications like motor control, a mechanism to synchronize several PWMs and ADCs is available (sync\_in and sync\_out).

Note that the PWMs run on the PWM clock and the ADCs on the ADC clock, see <u>Section 6.16.2</u>.

#### ARM9 microcontroller with CAN, LIN, and USB

#### 6.15.2 Pin description

The pins of the LPC2926/2927/2929 MSCSS associated with the three ADC modules are described in <u>Section 6.15.4.2</u>. Pins connected to the four PWM modules are described in <u>Section 6.15.5.4</u>, pins directly connected to the MSCSS timer 1 module are described in <u>Section 6.15.6.1</u>, and pins connected to the quadrature encoder interface are described in <u>Section 6.15.7.1</u>.

#### 6.15.3 Clock description

The MSCSS is clocked from a number of different sources:

- CLK\_SYS\_MSCSS\_A clocks the AHB side of the AHB-to-APB bus bridge

- CLK\_MSCSS\_APB clocks the subsystem APB bus

- CLK\_MSCSS\_MTMR0/1 clocks the timers

- CLK\_MSCSS\_PWM[0:3] clocks the PWMs.

Each ADC has two clock areas; a APB part clocked by CLK\_MSCSS\_ADCx\_APB (x = 0, 1, or 2) and a control part for the analog section clocked by CLK\_ADCx = 0, 1, or 2), see <u>Section 6.7.2</u>.

All clocks are derived from the BASE\_MSCSS\_CLK, except for CLK\_SYS\_MSCSS\_A which is derived form BASE\_SYS\_CLK, and the CLK\_ADCx clocks which are derived from BASE\_CLK\_ADC. If specific PWM or ADC modules are not used their corresponding clocks can be switched off.

#### 6.15.4 Analog-to-digital converter

The MSCSS in the LPC2926/2927/2929 includes three 10-bit successive-approximation analog-to-digital converters.

The key features of the ADC interface module are:

- ADC0: Eight analog inputs; time-multiplexed; measurement range up to 5.0 V.

- ADC1 and ADC2: Eight analog inputs; time-multiplexed; measurement range up to 3.3 V.

- External reference-level inputs.

- 400 ksamples per second at 10-bit resolution up to 1500 ksamples per second at 2-bit resolution.

- Programmable resolution from 2-bit to 10-bit.

- Single analog-to-digital conversion scan mode and continuous analog-to-digital conversion scan mode.

- Optional conversion on transition on external start input, timer capture/match signal, PWM\_sync or 'previous' ADC.

- Converted digital values are stored in a register for each channel.

- Optional compare condition to generate a 'less than' or an 'equal to or greater than' compare-value indication for each channel.

- Power-down mode.

#### ARM9 microcontroller with CAN, LIN, and USB

#### 6.15.5.3 Master and slave mode

A PWM module can provide synchronization signals to other modules (also called Master mode). The signal sync\_out is a pulse of one clock cycle generated when the internal PWM counter (re)starts. The signal trans\_enable\_out is a pulse synchronous to sync\_out, generated if a transfer from system registers to PWM shadow registers occurred when the PWM counter restarted. A delay may be inserted between the counter start and generation of trans\_enable\_out and sync\_out.

A PWM module can use input signals trans\_enable\_in and sync\_in to synchronize its internal PWM counter and the transfer of shadow registers (Slave mode).

#### 6.15.5.4 Pin description

Each of the four PWM modules in the MSCSS has the following pins. These are combined with other functions on the port pins of the LPC2926/2927/2929. <u>Table 24</u> shows the PWM0 to PWM3 pins.

| Symbol      | Pin name | Direction | Description           |

|-------------|----------|-----------|-----------------------|

| PWMn CAP[0] | PCAPn[0] | IN        | PWM n capture input 0 |

| PWMn CAP[1] | PCAPn[1] | IN        | PWM n capture input 1 |

| PWMn CAP[2] | PCAPn[2] | IN        | PWM n capture input 2 |

| PWMn MAT[0] | PMATn[0] | OUT       | PWM n match output 0  |

| PWMn MAT[1] | PMATn[1] | OUT       | PWM n match output 1  |

| PWMn MAT[2] | PMATn[2] | OUT       | PWM n match output 2  |

| PWMn MAT[3] | PMATn[3] | OUT       | PWM n match output 3  |

| PWMn MAT[4] | PMATn[4] | OUT       | PWM n match output 4  |

| PWMn MAT[5] | PMATn[5] | OUT       | PWM n match output 5  |

| PWMn TRAP   | TRAPn    | IN        | PWM n trap input      |

#### Table 24. PWM pins

#### 6.15.5.5 Clock description

The PWM modules are clocked by CLK\_MSCSS\_PWMx (x = 0 to 3), see Section 6.7.2. Note that each PWM has its own CLK\_MSCSS\_PWMx branch clock for power management. The frequency of all these clocks is identical to CLK\_MSCSS\_APB since they are derived from the same base clock BASE\_MSCSS\_CLK.

Also note that unlike the timer modules in the Peripheral SubSystem, the actual timer counter registers of the PWM modules run at the same clock as the APB system interface CLK\_MSCSS\_APB. This clock is independent of the AHB system clock.

If a PWM module is not used its CLK\_MSCSS\_PWMx branch clock can be switched off.

#### 6.15.6 Timers in the MSCSS

The two timers in the MSCSS are functionally identical to the timers in the peripheral subsystem, see <u>Section 6.13.3</u>. The features of the timers in the MSCSS are the same as the timers in the peripheral subsystem, but the capture inputs and match outputs are not available on the device pins. These signals are instead connected to the ADC and PWM modules as outlined in the description of the MSCSS, see <u>Section 6.15.1</u>.

See Section 6.13.3 for a functional description of the timers.

#### ARM9 microcontroller with CAN, LIN, and USB

#### 6.16.4.2 Pin description

The RGU module in the LPC2926/2927/2929 has the following pins. <u>Table 31</u> shows the RGU pins.

#### Table 31. RGU pins

| Symbol | Direction | Description                                            |

|--------|-----------|--------------------------------------------------------|

| RST    | IN        | external reset input, Active LOW; pulled up internally |

#### 6.16.5 Power Management Unit (PMU)

This module enables software to actively control the system's power consumption by disabling clocks not required in a particular operating mode.

Using the base clocks from the CGU as input, the PMU generates branch clocks to the rest of the LPC2926/2927/2929. Output clocks branched from the same base clock are phase- and frequency-related. These branch clocks can be individually controlled by software programming.

#### The key features are:

- Individual clock control for all LPC2926/2927/2929 sub-modules.

- Activates sleeping clocks when a wake-up event is detected.

- Clocks can be individually disabled by software.

- Supports AHB master-disable protocol when AUTO mode is set.

- Disables wake-up of enabled clocks when Power-down mode is set.

- Activates wake-up of enabled clocks when a wake-up event is received.

- Status register is available to indicate if an input base clock can be safely switched off (i.e. all branch clocks are disabled).

#### 6.16.5.1 Functional description

The PMU controls all internal clocks coming out of the CGU0 for power-mode management. With some exceptions, each branch clock can be switched on or off individually under control of software register bits located in its individual configuration register. Some branch clocks controlling vital parts of the device operate in a fixed mode. <u>Table 32</u> shows which mode-control bits are supported by each branch clock.

By programming the configuration register the user can control which clocks are switched on or off, and which clocks are switched off when entering Power-down mode.

Note that the standby-wait-for-interrupt instructions of the ARM968E-S processor (putting the ARM CPU into a low-power state) are not supported. Instead putting the ARM CPU into power-down should be controlled by disabling the branch clock for the CPU.

**Remark:** For any disabled branch clocks to be re-activated their corresponding base clocks must be running (controlled by CGU0).

<u>Table 32</u> shows the relation between branch and base clocks, see also <u>Section 6.7.1</u>. Every branch clock is related to one particular base clock: it is not possible to switch the source of a branch clock in the PMU.

#### ARM9 microcontroller with CAN, LIN, and USB

### 7. Limiting values

#### Table 33. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                   | Parameter                                  | Conditions                                                                                        | ľ                     | Min  | Max                               | Unit |

|--------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------|------|-----------------------------------|------|

| Supply pins              |                                            |                                                                                                   |                       |      |                                   |      |

| P <sub>tot</sub>         | total power dissipation                    |                                                                                                   | <u>[1]</u> -          |      | 1.5                               | W    |

| V <sub>DD(CORE)</sub>    | core supply voltage                        |                                                                                                   | -                     | -0.5 | +2.0                              | V    |

| V <sub>DD(OSC_PLL)</sub> | oscillator and PLL supply voltage          |                                                                                                   | -                     | -0.5 | +2.0                              | V    |

| V <sub>DDA(ADC3V3)</sub> | 3.3 V ADC analog supply voltage            |                                                                                                   | -                     | -0.5 | +4.6                              | V    |

| V <sub>DDA(ADC5V0)</sub> | 5.0 V ADC analog supply voltage            |                                                                                                   | -                     | -0.5 | +6.0                              | V    |

| V <sub>DD(IO)</sub>      | input/output supply voltage                |                                                                                                   | -                     | -0.5 | +4.6                              | V    |

| I <sub>DD</sub>          | supply current                             | average value per supply pin                                                                      | [2] _                 |      | 98                                | mA   |

| I <sub>SS</sub>          | ground current                             | average value per ground pin                                                                      | [2] -                 | ,    | 98                                | mA   |

| Input pins and           | d I/O pins                                 |                                                                                                   |                       |      |                                   |      |

| V <sub>XIN_OSC</sub>     | voltage on pin XIN_OSC                     |                                                                                                   | -                     | -0.5 | +2.0                              | V    |

| V <sub>I(IO)</sub>       | I/O input voltage                          |                                                                                                   | [3][4][5]             | -0.5 | $V_{DD(IO)}$ + 3.0                | V    |

| V <sub>I(ADC)</sub>      | ADC input voltage                          | for ADC1/2: I/O port 0 pin 8 to pin 23.                                                           | [4][5]                | -0.5 | V <sub>DDA(ADC3V3)</sub><br>+ 0.5 | V    |

|                          |                                            | for ADC0: I/O port 0 pin 5 to<br>pin 7; I/O port 2 pins 12 and<br>13; I/O port 3 pins 0<br>and 1. | <u>[4][5][6][7]</u> _ | -0.5 | V <sub>DDA(ADC5V0)</sub><br>+ 0.5 | V    |

| V <sub>VREFP</sub>       | voltage on pin VREFP                       |                                                                                                   | -                     | -0.5 | +3.6                              | V    |

| V <sub>VREFN</sub>       | voltage on pin VREFN                       |                                                                                                   | -                     | -0.5 | +3.6                              | V    |

| I <sub>I(ADC)</sub>      | ADC input current                          | average value per input pin                                                                       | [2] -                 |      | 35                                | mA   |

| Output pins a            | nd I/O pins configured as ou               | utput                                                                                             |                       |      |                                   |      |

| I <sub>OHS</sub>         | HIGH-level short-circuit<br>output current | drive HIGH, output shorted to $V_{SS(IO)}$                                                        | [8] _                 |      | -33                               | mA   |

| I <sub>OLS</sub>         | LOW-level short-circuit<br>output current  | drive LOW, output shorted to $V_{DD(IO)}$                                                         | [8] _                 |      | +38                               | mA   |

| General                  |                                            |                                                                                                   |                       |      |                                   |      |

| T <sub>stg</sub>         | storage temperature                        |                                                                                                   | -                     | -65  | +150                              | °C   |

| T <sub>amb</sub>         | ambient temperature                        |                                                                                                   | -                     | -40  | +85                               | °C   |

#### ARM9 microcontroller with CAN, LIN, and USB

#### Symbol Conditions Parameter Min Unit Max ESD electrostatic discharge on all pins VESD voltage human body model [9] -2000 +2000 V charged device model -500 +500 V on corner pins -750 V charged device model +750

#### Table 33. Limiting values ... continued

In accordance with the Absolute Maximum Rating System (IEC 60134).

[1] Based on package heat transfer, not device power consumption.

[2] Peak current must be limited at 25 times average current.

[3] For I/O Port 0, the maximum input voltage is defined by V<sub>I(ADC)</sub>.

Only when V<sub>DD(IO)</sub> is present. [4]

[5] Note that pull-up should be off. With pull-up do not exceed 3.6 V.

For these input pins a fixed amplification of  $\frac{2}{3}$  is performed on the input voltage before feeding into the ADC0 itself. The maximum input [6] voltage on ADC0 is V<sub>DDA(ADC5V0)</sub>.

[7] Not exceeding 6 V.

112 mA per V<sub>DD(IO)</sub> or V<sub>SS(IO)</sub> should not be exceeded. [8]

Human-body model: discharging a 100 pF capacitor via a 10 k $\Omega$  series resistor. [9]

#### ARM9 microcontroller with CAN, LIN, and USB

#### 9.6 Dynamic characteristics: external static memory

#### Table 42. External static memory interface dynamic characteristics

$V_{DD(CORE)} = V_{DD(OSC\_PLL)}$ ;  $V_{DD(IO)} = 2.7 \text{ V to } 3.6 \text{ V}$ ;  $V_{DDA(ADC3V3)} = 3.0 \text{ V to } 3.6 \text{ V}$ ; all voltages are measured with respect to ground.<sup>[1]</sup>

| Symbol                | Parameter                                                      | Conditions | Min                           | Тур                                       | Ma<br>x  | Unit |

|-----------------------|----------------------------------------------------------------|------------|-------------------------------|-------------------------------------------|----------|------|

| T <sub>CLCL</sub>     | clock cycle time                                               |            | 8                             | -                                         | 100      | ns   |

| t <sub>a(R)int</sub>  | internal read access time                                      |            | -                             | -                                         | 20.<br>5 | ns   |

| t <sub>a(W)int</sub>  | internal write access time                                     |            | -                             | -                                         | 24.<br>9 | ns   |

| Read cyc              | le parameters                                                  |            |                               |                                           |          |      |

| t <sub>CSLAV</sub>    | CS LOW to address valid time                                   |            | -5                            | -2.5                                      | -        | ns   |

| t <sub>OELAV</sub>    | OE LOW to address valid time                                   |            | $-5 - WSTOEN \times T_{CLCL}$ | $-2.5-WSTOEN\times T_{CLCL}$              | -        | ns   |

| t <sub>CSLOEL</sub>   | CS LOW to OE LOW time                                          |            | -                             | $0 + WSTOEN \times T_{CLCL}$              | -        | ns   |

| t <sub>su(DQ)</sub>   | data input/output set-up<br>time                               |            | 11                            | 16                                        | 22       | ns   |

| t <sub>h(D)</sub>     | data input hold time                                           |            | 0                             | 2.5                                       | 5        | ns   |

| t <sub>CSHOEH</sub>   | CS HIGH to OE HIGH time                                        |            | -                             | 0                                         | -        | ns   |

| t <sub>BLSLBLSH</sub> | BLS LOW to BLS HIGH time                                       |            | -                             | (WST1 – WSTOEN + 1) × $T_{CLCL}$          | -        | ns   |

| t <sub>OELOEH</sub>   | OE LOW to OE HIGH time                                         |            | -                             | (WST1 – WSTOEN + 1) × $T_{CLCL}$          | -        | ns   |

| t <sub>BLSLAV</sub>   | BLS LOW to address valid time                                  |            |                               | $0 + WSTOEN \times T_{CLCL}$              | -        | ns   |

| Write cyc             | le parameters                                                  |            |                               |                                           |          |      |

| t <sub>CSHBLSH</sub>  | CS HIGH to BLS HIGH time                                       | [2]        | -                             | 0                                         | -        | ns   |

| t <sub>CSLWEL</sub>   | CS LOW to WE LOW time                                          |            | -                             | (WSTWEN + 0.5) $\times$ T <sub>CLCL</sub> | -        | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW time                                         | [3]        | -                             | $WSTWEN \times T_{CLCL}$                  | -        | ns   |

| t <sub>WELDV</sub>    | WE LOW to data valid time                                      |            | -                             | (WSTWEN + 0.5) $\times$ T <sub>CLCL</sub> | -        | ns   |

| t <sub>CSLDV</sub>    | $\overline{\text{CS}}$ LOW to data valid time                  |            | -0.5                          | -0.1                                      | 0.3      | ns   |

| t <sub>WELWEH</sub>   | $\overline{\text{WE}}$ LOW to $\overline{\text{WE}}$ HIGH time |            | -                             | (WST2 – WSTWEN + 1) × $T_{CLCL}$          | -        | ns   |

| t <sub>BLSLBLSH</sub> | BLS LOW to BLS HIGH time                                       | [4]        | -                             | (WST2 – WSTWEN + 2) × $T_{CLCL}$          | -        | ns   |

[1] All parameters are guaranteed over the virtual junction temperature range by design. Pre-testing is performed at  $T_{amb} = 85 \text{ °C}$  ambient temperature on wafer level. Cased products are tested at  $T_{amb} = 25 \text{ °C}$  (final testing). Both pre-testing and final testing use correlated test conditions to cover the specified temperature and power supply voltage range.

[2] When the byte lane select signals are used to connect the write enable input (8 bit devices),  $t_{CSHBLSH} = -0.5 \times T_{CLCL}$ .

[3] When the byte lane select signals are used to connect the write enable input (8 bit devices),  $t_{CSLBLSL} = t_{CSLWEL}$ .

[4] For 16 and 32 bit devices.

ARM9 microcontroller with CAN, LIN, and USB

#### 9.7 Dynamic characteristics: ADC

#### Table 43. ADC dynamic characteristics

$V_{DD(CORE)} = V_{DD(OSC_PLL)}$ ;  $V_{DD(IO)} = 2.7 \text{ V to } 3.6 \text{ V}$ ;  $V_{DDA(ADC3V3)} = 3.0 \text{ V to } 3.6 \text{ V}$ ; all voltages are measured with respect to ground.<sup>[1]</sup>

| Symbol              | Parameter             | Conditions                                                                                                                | M            | lin Typ | Max  | Unit      |

|---------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------|--------------|---------|------|-----------|

| 5.0 V ADC           | 0                     |                                                                                                                           |              |         |      |           |

| f <sub>i(ADC)</sub> | ADC input frequency   |                                                                                                                           | [2] 4        | -       | 4.5  | MHz       |

| f <sub>s(max)</sub> | maximum sampling rate | $\begin{array}{l} f_{i(ADC)} = 4.5 \text{ MHz}; \\ f_s = f_{i(ADC)} / (n + 1) \text{ with} \\ n = resolution \end{array}$ |              |         |      |           |

|                     |                       | resolution 2 bit                                                                                                          | -            | -       | 1500 | ksample/s |

|                     |                       | resolution 10 bit                                                                                                         | -            | -       | 400  | ksample/s |

| t <sub>conv</sub>   | conversion time       | In number of ADC<br>clock cycles                                                                                          | 3            | -       | 11   | cycles    |

|                     |                       | In number of bits                                                                                                         | 2            | -       | 10   | bits      |

| 3.3 V ADC           | 51/2                  |                                                                                                                           |              |         |      |           |

| f <sub>i(ADC)</sub> | ADC input frequency   |                                                                                                                           | <u>[2]</u> 4 | -       | 4.5  | MHz       |

| f <sub>s(max)</sub> | maximum sampling rate | $\begin{array}{l} f_{i(ADC)} = 4.5 \text{ MHz}; \\ f_s = f_{i(ADC)} / (n + 1) \text{ with} \\ n = resolution \end{array}$ |              |         |      |           |

|                     |                       | resolution 2 bit                                                                                                          | -            | -       | 1500 | ksample/s |

|                     |                       | resolution 10 bit                                                                                                         | -            | -       | 400  | ksample/s |

| t <sub>conv</sub>   | conversion time       | In number of ADC<br>clock cycles                                                                                          | 3            | -       | 11   | cycles    |

|                     |                       | In number of bits                                                                                                         | 2            | -       | 10   | bits      |

[1] All parameters are guaranteed over the virtual junction temperature range by design. Pre-testing is performed at  $T_{amb} = 85$  °C ambient temperature on wafer level. Cased products are tested at  $T_{amb} = 25$  °C (final testing). Both pre-testing and final testing use correlated test conditions to cover the specified temperature and power supply voltage range.

[2] Duty cycle clock should be as close as possible to 50 %.

### **10.** Application information

#### **10.1** Operating frequency selection

The LPC2926/2927/2929 is specified to operate at a maximum frequency of 125 MHz, maximum temperature of 85 °C, and maximum core voltage of 1.89 V. Figure 30 and Figure 31 show that the user can achieve higher operating frequencies for the LPC2926/2927/2929 by controlling the temperature and the core voltage accordingly.

ARM9 microcontroller with CAN, LIN, and USB

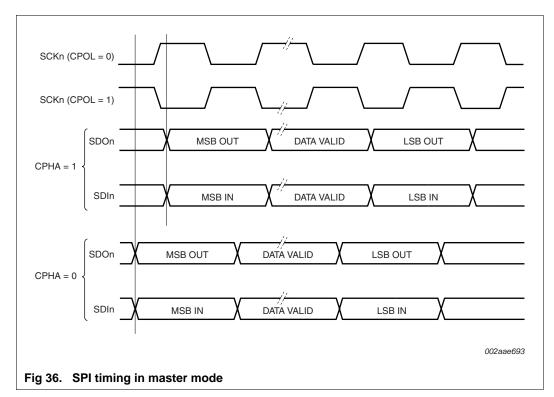

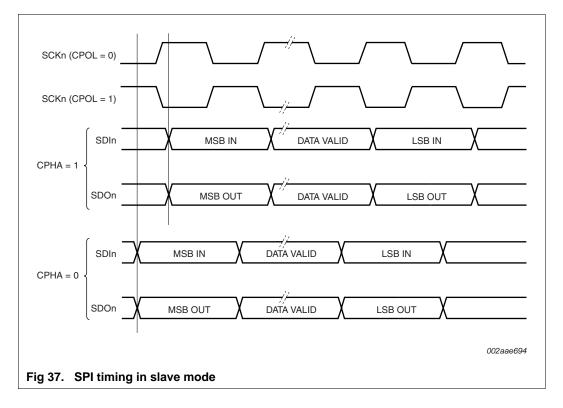

### 10.3 SPI signal forms

#### **NXP Semiconductors**

### LPC2926/2927/2929

#### ARM9 microcontroller with CAN, LIN, and USB

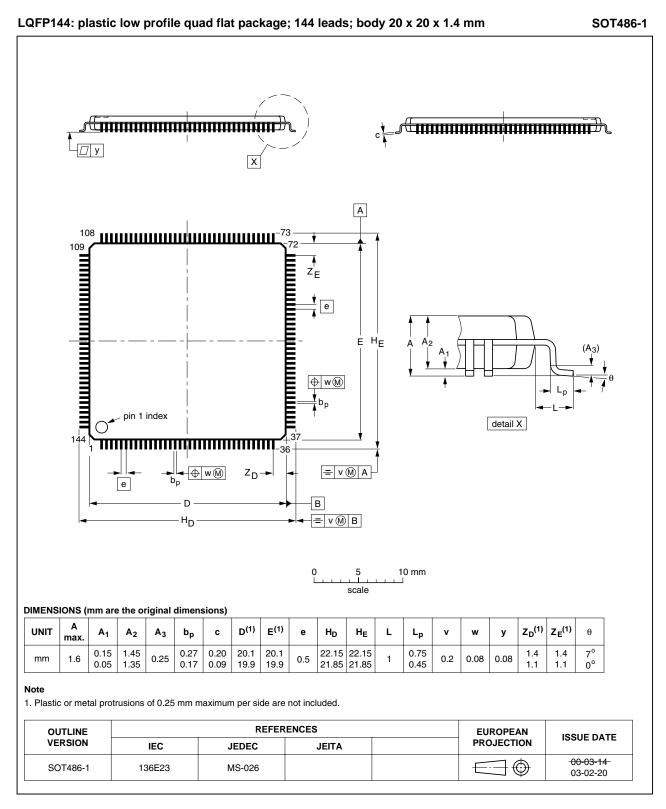

### 11. Package outline

#### Fig 39. Package outline SOT486-1 (LQFP144)

All information provided in this document is subject to legal disclaimers.

LPC2926\_27\_29

ARM9 microcontroller with CAN, LIN, and USB

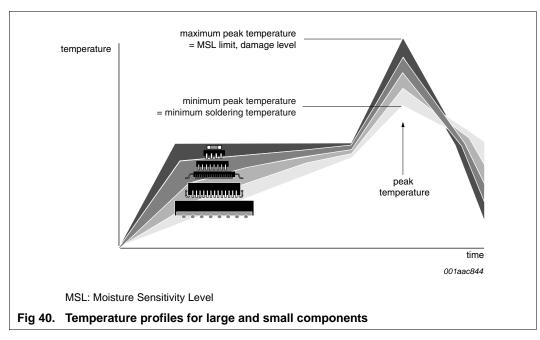

For further information on temperature profiles, refer to Application Note *AN10365 "Surface mount reflow soldering description"*.

LPC2926\_27\_29