Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 16                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 128 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                           |

| Data Converters            | A/D 5x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 20-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s003f3p6tr |

# List of figures

| Figure 1.    | STM8S003F3/K3 value line block diagram                                                            | 11 |

|--------------|---------------------------------------------------------------------------------------------------|----|

| Figure 2.    | Flash memory organization                                                                         | 14 |

| Figure 3.    | STM8S003K3 LQFP32 pinout                                                                          | 22 |

| Figure 4.    | STM8S003F3 TSSOP20 pinout                                                                         | 25 |

| Figure 5.    | STM8S003F3 UFQFPN20 pinout                                                                        | 26 |

| Figure 6.    | Memory map                                                                                        | 30 |

| Figure 7.    | Pin loading conditions                                                                            | 46 |

| Figure 8.    | Pin input voltage                                                                                 | 47 |

| Figure 9.    | f <sub>CPUmax</sub> versus V <sub>DD</sub>                                                        | 49 |

| Figure 10.   | External capacitor C <sub>EXT</sub>                                                               |    |

| Figure 11.   | Typ. I <sub>DD(RUN)</sub> vs V <sub>DD</sub> , HSE user external clock, f <sub>CPU</sub> = 16 MHz | 58 |

| Figure 12.   | Typ. I <sub>DD(RUN)</sub> vs f <sub>CPU</sub> , HSE user external clock, V <sub>DD</sub> = 5 V    |    |

| Figure 13.   | Typ. I <sub>DD(RUN)</sub> vs V <sub>DD</sub> , HSI RC osc, f <sub>CPU</sub> = 16 MHz              |    |

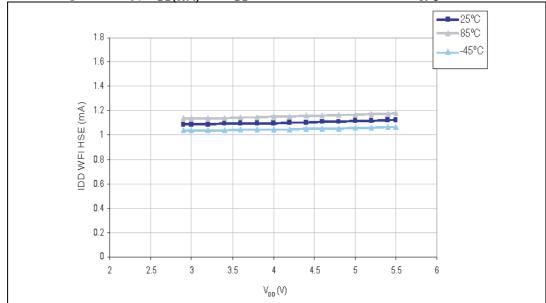

| Figure 14.   | Typ. I <sub>DD(WFI)</sub> vs. V <sub>DD</sub> HSE user external clock, f <sub>CPU</sub> = 16MHz   |    |

| Figure 15.   | Typ. I <sub>DD(WFI)</sub> vs. f <sub>CPU</sub> , HSE user external clock, V <sub>DD</sub> = 5 V   |    |

| Figure 16.   | Typ. I <sub>DD(WFI)</sub> vs V <sub>DD</sub> , HSI RC osc, f <sub>CPU</sub> = 16 MHz              |    |

| Figure 17.   | HSE external clock source                                                                         |    |

| Figure 18.   | HSE oscillator circuit diagram                                                                    |    |

| Figure 19.   | Typical HSI frequency variation vs V <sub>DD</sub> at 4 temperatures                              |    |

| Figure 20.   | Typical LSI frequency variation vs V <sub>DD</sub> @ 4 temperatures                               |    |

| Figure 21.   | Typical V <sub>IL</sub> and V <sub>IH</sub> vs V <sub>DD</sub> @ 4 temperatures                   |    |

| Figure 22.   | Typical pull-up resistance vs V <sub>DD</sub> @ 4 temperatures                                    |    |

| Figure 23.   | Typical pull-up current vs V <sub>DD</sub> @ 4 temperatures                                       |    |

| Figure 24.   | Typ. $V_{OL}$ @ $V_{DD}$ = 5 V (standard ports)                                                   |    |

| Figure 25.   | Typ. $V_{OL}$ @ $V_{DD}$ = 3.3 V (standard ports)                                                 |    |

| Figure 26.   | Typ. V <sub>OL</sub> @ V <sub>DD</sub> = 5 V (true open drain ports)                              |    |

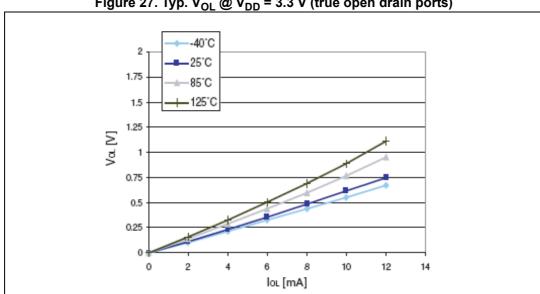

| Figure 27.   | Typ. $V_{OL}$ @ $V_{DD}$ = 3.3 V (true open drain ports)                                          |    |

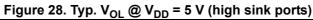

| Figure 28.   | Typ. $V_{OL}$ @ $V_{DD}$ = 5 V (high sink ports)                                                  |    |

| Figure 29.   | Typ. $V_{OL}$ @ $V_{DD}$ = 3.3 V (high sink ports)                                                |    |

| Figure 30.   | Typ. V <sub>DD</sub> - V <sub>OH</sub> @ V <sub>DD</sub> = 5 V (standard ports)                   |    |

| Figure 31.   | Typ. $V_{DD} - V_{OH} @ V_{DD} = 3.3 \text{ V (standard ports)}$                                  |    |

| Figure 32.   | Typ. V <sub>DD</sub> - V <sub>OH</sub> @ V <sub>DD</sub> = 5 V (high sink ports)                  |    |

| Figure 33.   | Typ. $V_{DD} - V_{OH} @ V_{DD} = 3.3 \text{ V (high sink ports)}$                                 |    |

| Figure 34.   | Typical NRST V <sub>II</sub> and V <sub>IH</sub> vs V <sub>DD</sub> @ 4 temperatures              |    |

| Figure 35.   | Typical NRST pull-up resistance vs V <sub>DD</sub> @ 4 temperatures                               |    |

| Figure 36.   | Typical NRST pull-up current vs V <sub>DD</sub> @ 4 temperatures                                  |    |

| Figure 37.   | Recommended reset pin protection                                                                  |    |

| Figure 38.   | SPI timing diagram - slave mode and CPHA = 0                                                      |    |

| Figure 39.   | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                                       | 78 |

| Figure 40.   | SPI timing diagram - master mode <sup>(1)</sup>                                                   |    |

| Figure 41.   | Typical application with I <sup>2</sup> C bus and timing diagram                                  |    |

| Figure 42.   | ADC accuracy characteristics                                                                      |    |

| Figure 43.   | Typical application with ADC                                                                      |    |

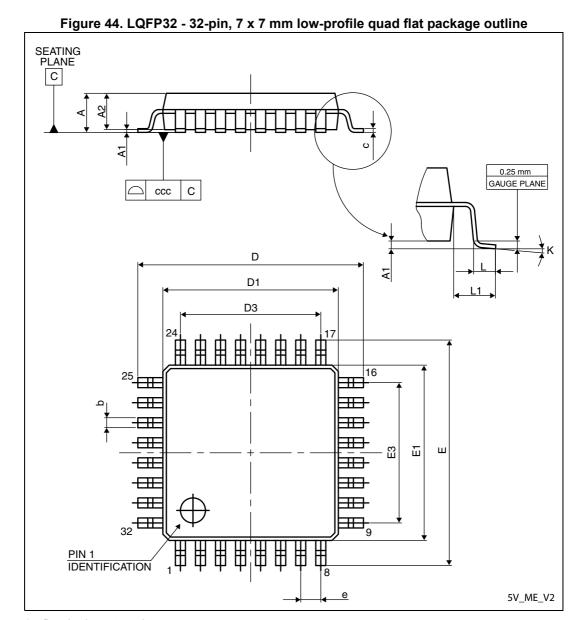

| Figure 44.   | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline                                   |    |

| Figure 45.   | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat recommended footprint                             |    |

| Figure 46.   | LQFP32 marking example (package top view)                                                         |    |

| Figure 40.   | TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch,                         | 90 |

| i igui e 📆 . | nackage outline                                                                                   | 91 |

|              |                                                                                                   |    |

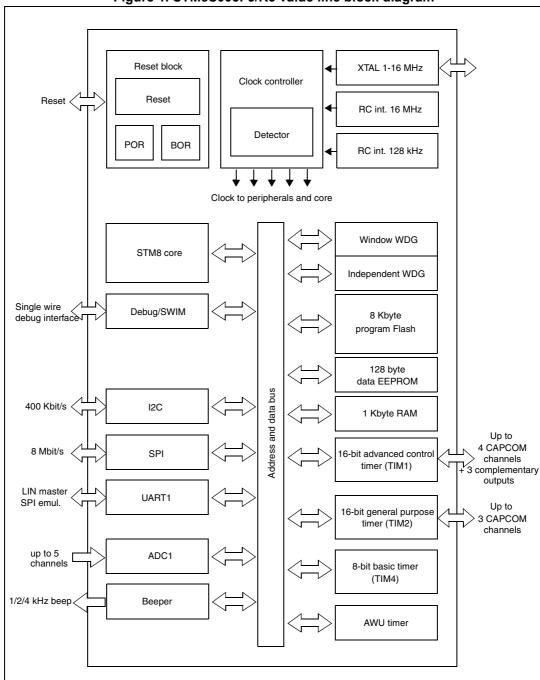

# 3 Block diagram

Figure 1. STM8S003F3/K3 value line block diagram

#### 4.12 TIM4 - 8-bit basic timer

8-bit autoreload, adjustable prescaler ratio to any power of 2 from 1 to 128

Clock source: CPU clock

Interrupt source: 1 x overflow/update

Table 3. TIM timer features

| Timer | Counter<br>size<br>(bits) | Prescaler                      | Counting mode | CAPCOM channels | Complem. outputs | Ext.<br>trigger | Timer<br>synchr-<br>onization/<br>chaining |

|-------|---------------------------|--------------------------------|---------------|-----------------|------------------|-----------------|--------------------------------------------|

| TIM1  | 16                        | Any integer from 1 to 65536    | Up/down       | 4               | 3                | Yes             |                                            |

| TIM2  | 16                        | Any power of 2 from 1 to 32768 | Up            | 3               | 0                | No              | No                                         |

| TIM4  | 8                         | Any power of 2 from 1 to 128   | Up            | 0               | 0                | No              |                                            |

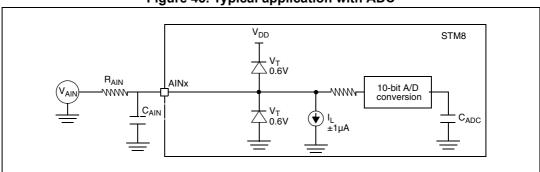

#### 4.13 Analog-to-digital converter (ADC1)

STM8S003F3/K3 value line products contain a 10-bit successive approximation A/D converter (ADC1) with up to 5 external multiplexed input channels and the following main features:

Input voltage range: 0 to V<sub>DDA</sub> Conversion time: 14 clock cycles

- Single and continuous, buffered continuous conversion modes

- Buffer size (10 x 10 bits)

- Scan mode for single and continuous conversion of a sequence of channels

- Analog watchdog capability with programmable upper and lower thresholds

- Analog watchdog interrupt

- External trigger input

- Trigger from TIM1 TRGO

- End of conversion (EOC) interrupt

Note:

Additional AIN12 analog input is not selectable in ADC scan mode or with analog watchdog. Values converted from AIN12 are stored only into the ADC\_DRH/ADC\_DRL registers.

#### **Communication interfaces** 4.14

The following communication interfaces are implemented:

- UART1: full feature UART, synchronous mode, SPI master mode, SmartCard mode, IrDA mode, LIN2.1 master capability

- SPI: full and half-duplex, 8 Mbit/s

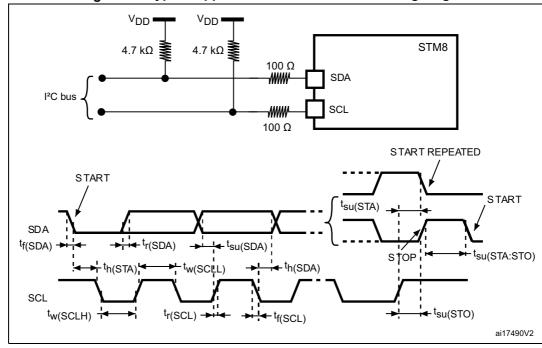

- I2C: up to 400 Kbit/s

## 4.14.3 I<sup>2</sup>C

- I2C master features

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds

- Standard speed (up to 100 kHz)

- Fast speed (up to 400 kHz)

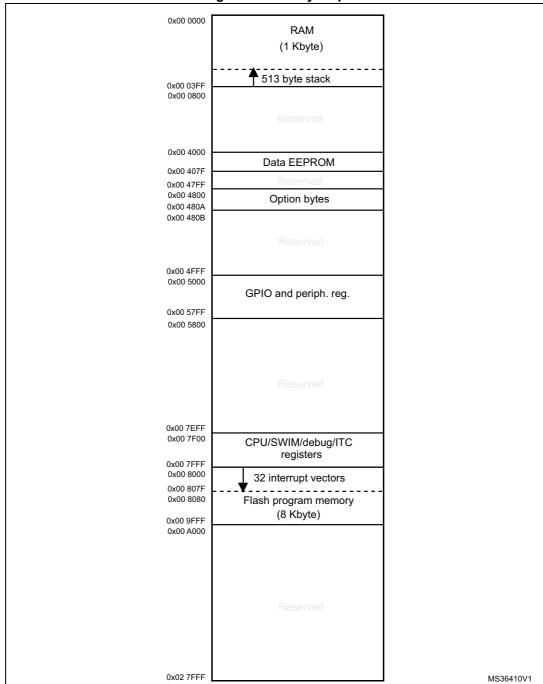

# 6 Memory and register map

## 6.1 Memory map

Figure 6. Memory map

Table 9. General hardware register map (continued)

| Address                   | Block            | Register label | Register name                                   | Reset<br>status |

|---------------------------|------------------|----------------|-------------------------------------------------|-----------------|

| 0x00 5216                 |                  | I2C_DR         | I <sup>2</sup> C data register                  | 0x00            |

| 0x00 5217                 | 1                | I2C_SR1        | I <sup>2</sup> C status register 1              | 0x00            |

| 0x00 5218                 |                  | I2C_SR2        | I <sup>2</sup> C status register 2              | 0x00            |

| 0x00 5219                 | 1                | I2C_SR3        | I <sup>2</sup> C status register 3              | 0x00            |

| 0x00 521A                 | I <sup>2</sup> C | I2C_ITR        | I <sup>2</sup> C interrupt control register     | 0x00            |

| 0x00 521B                 | 1                | I2C_CCRL       | I <sup>2</sup> C clock control register low     | 0x00            |

| 0x00 521C                 | 1                | I2C_CCRH       | I <sup>2</sup> C clock control register high    | 0x00            |

| 0x00 521D                 | 1                | I2C_TRISER     | I <sup>2</sup> C TRISE register                 | 0x02            |

| 0x00 521E                 | 1                | I2C_PECR       | I <sup>2</sup> C packet error checking register | 0x00            |

| 0x00 521F to<br>0x00 522F |                  |                | Reserved area (17 byte)                         |                 |

| 0x00 5230                 |                  | UART1_SR       | UART1 status register                           | 0xC0            |

| 0x00 5231                 | ]                | UART1_DR       | UART1 data register                             | 0xXX            |

| 0x00 5232                 | ]                | UART1_BRR1     | UART1 baud rate register 1                      | 0x00            |

| 0x00 5233                 | ]                | UART1_BRR2     | UART1 baud rate register 2                      | 0x00            |

| 0x00 5234                 | ]                | UART1_CR1      | UART1 control register 1                        | 0x00            |

| 0x00 5235                 | UART1            | UART1_CR2      | UART1 control register 2                        | 0x00            |

| 0x00 5236                 | ]                | UART1_CR3      | UART1 control register 3                        | 0x00            |

| 0x00 5237                 | ]                | UART1_CR4      | UART1 control register 4                        | 0x00            |

| 0x00 5238                 | ]                | UART1_CR5      | UART1 control register 5                        | 0x00            |

| 0x00 5239                 | ]                | UART1_GTR      | UART1 guard time register                       | 0x00            |

| 0x00 523A                 | ]                | UART1_PSCR     | UART1 prescaler register                        | 0x00            |

| 0x00 523B to<br>0x00523F  |                  |                | Reserved area (21 byte)                         |                 |

Table 13. Option byte description (continued)

|                 | Table 13. Option byte description (continued)                                                                                                                                                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Option byte no. | Description                                                                                                                                                                                                                                     |

| OPT1            | UBC[7:0] User boot code area  0x00: no UBC, no write-protection 0x01: Pages 0 defined as UBC, memory write-protected 0x02: Pages 0 to 1 defined as UBC, memory write-protected Page 0 and page 1 contain the interrupt vectors.                 |

|                 | 0x7F: Pages 0 to 126 defined as UBC, memory write-protected Other values: Pages 0 to 127 defined as UBC, memory-write protected. Note: Refer to the family reference manual (RM0016) section on Flash/EEPROM write protection for more details. |

| OPT2            | AFR[7:0] Refer to the following section for alternate function remapping descriptions of bits [7:2] and [1:0] respectively.                                                                                                                     |

|                 | HSITRIM: high-speed internal clock trimming register size  0: 3-bit trimming supported in CLK_HSITRIMR register  1: 4-bit trimming supported in CLK_HSITRIMR register                                                                           |

|                 | LSI_EN: Low speed internal clock enable  0: LSI clock is not available as CPU clock source  1: LSI clock is available as CPU clock source                                                                                                       |

| OPT3            | IWDG_HW: Independent watchdog  0: IWDG Independent watchdog activated by software  1: IWDG Independent watchdog activated by hardware                                                                                                           |

|                 | WWDG_HW: Window watchdog activation  0: WWDG window watchdog activated by software  1: WWDG window watchdog activated by hardware                                                                                                               |

|                 | WWDG_HALT: Window watchdog reset on halt  0: No reset generated on halt if WWDG active  1: Reset generated on halt if WWDG active                                                                                                               |

|                 | EXTCLK: External clock selection  0: External crystal connected to OSCIN/OSCOUT  1: External clock signal on OSCIN                                                                                                                              |

| OPT4            | CKAWUSEL: Auto wakeup unit/clock  0: LSI clock source selected for AWU  1: HSE clock with prescaler selected as clock source for for AWU                                                                                                        |

|                 | PRSC[1:0] AWU clock prescaler 0x: 16 MHz to 128 kHz prescaler 10: 8 MHz to 128 kHz prescaler 11: 4 MHz to 128 kHz prescaler                                                                                                                     |

| OPT5            | HSECNT[7:0]: HSE crystal oscillator stabilization time This configures the stabilization time. 0x00: 2048 HSE cycles 0xB4: 128 HSE cycles 0xD2: 8 HSE cycles 0xE1: 0.5 HSE cycles                                                               |

Table 15. STM8S003F3 alternate function remapping bits for 20-pin devices

| Option byte number | Description                                                                                                                                                                                                |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | AFR7Alternate function remapping option 7  0: AFR7 remapping option inactive: default alternate function <sup>(1)</sup> 1: Port C3 alternate function = TIM1_CH1N; port C4 alternate function = TIM1_CH2N. |

|                    | AFR6 Alternate function remapping option 6 Reserved.                                                                                                                                                       |

|                    | AFR5 Alternate function remapping option 5 Reserved.                                                                                                                                                       |

|                    | AFR4 Alternate function remapping option 4                                                                                                                                                                 |

|                    | 0: AFR4 remapping option inactive: default alternate function <sup>(1)</sup> . 1: Port B4 alternate function = ADC_ETR; port B5 alternate function = TIM1_BKIN.                                            |

| OPT2               | AFR3 Alternate function remapping option 3                                                                                                                                                                 |

|                    | O: AFR3 remapping option inactive: default alternate function <sup>(1)</sup> 1: Port C3 alternate function = TLI.                                                                                          |

|                    | AFR2 Alternate function remapping option 2                                                                                                                                                                 |

|                    | Reserved.                                                                                                                                                                                                  |

|                    | AFR1 Alternate function remapping option 1 (2)                                                                                                                                                             |

|                    | 0: AFR1 remapping option inactive: default alternate function <sup>(1)</sup> 1: Port A3 alternate function = SPI_NSS; port D2 alternate function = TIM2_CH3.                                               |

|                    | AFR0 Alternate function remapping option 0 <sup>(2)</sup>                                                                                                                                                  |

|                    | 0: AFR0 remapping option inactive: Default alternate functions <sup>(1)</sup> 1: Port C5 alternate function = TIM2_CH1; port C6 alternate function = TIM1_CH1; port C7 alternate function = TIM1_CH2.      |

- 1. Refer to the pinout description.

- 2. Do not use more than one remapping option in the same port. It is forbidden to enable both AFR1 and AFR0.

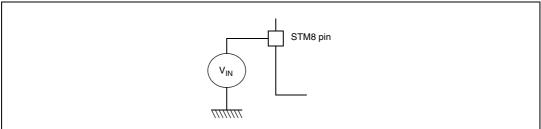

Figure 8. Pin input voltage

## 9.2 Absolute maximum ratings

Stresses above those listed as 'absolute maximum ratings' may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 16. Voltage characteristics

| Symbol                             | Ratings                                                     | Min                   | Max                   | Unit |

|------------------------------------|-------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>DDx</sub> - V <sub>SS</sub> | Supply voltage <sup>(1)</sup>                               | -0.3                  | 6.5                   |      |

| V                                  | Input voltage on true open drain pins <sup>(2)</sup>        | V <sub>SS</sub> - 0.3 | 6.5                   | V    |

| V <sub>IN</sub>                    | Input voltage on any other pin <sup>(2)</sup>               | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3 |      |

| $ V_{DDx} - V_{DD} $               | Variations between different power pins                     | -                     | 50                    | mV   |

| V <sub>SSx</sub> - V <sub>SS</sub> | Variations between all the different ground pins            | -                     | 50                    | IIIV |

| V <sub>ESD</sub>                   | See Absolute maxim ratings (electrical sensitivity) on page |                       | electrical            | -    |

<sup>1.</sup> All power (V<sub>DD</sub>) and ground (V<sub>SS</sub>) pins must always be connected to the external power supply

I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

### Total current consumption in wait mode

Table 23. Total current consumption in wait mode at  $V_{DD}$  = 5 V

| Symbol               | Parameter            | Conditions                                            |                                                             |                                       | Max <sup>(1)</sup> | Unit |  |

|----------------------|----------------------|-------------------------------------------------------|-------------------------------------------------------------|---------------------------------------|--------------------|------|--|

|                      |                      |                                                       | HSE crystal osc. (16 MHz)                                   | 1.6                                   | -                  |      |  |

|                      |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz       | HSE user ext. clock (16 MHz)                                |                                       | 1.3                |      |  |

| Supp                 | Supply               |                                                       | HSI RC osc. (16 MHz)                                        | 0.89                                  | 1.1                |      |  |

| I <sub>DD(WFI)</sub> | current in wait mode | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz | HSI RC osc. (16 MHz)                                        | 0.7                                   | 0.88               | mA   |  |

| Wa                   | wait mode            | wait mode                                             | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.45               | 0.57 |  |

|                      |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz      | LSI RC osc. (128 kHz)                                       | 0.4                                   | 0.54               |      |  |

<sup>1.</sup> Data based on characterization results, not tested in production.

Table 24. Total current consumption in wait mode at  $V_{DD}$  = 3.3 V

| Symbol                                           | Parameter                                                   | Conditions                                                  |                           |      | Max <sup>(1)</sup> | Unit |

|--------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|---------------------------|------|--------------------|------|

| I <sub>DD(WFI)</sub> Supply current in wait mode |                                                             |                                                             | HSE crystal osc. (16 MHz) | 1.1  | -                  |      |

|                                                  | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE user ext. clock (16 MHz)                                | 1.1                       | 1.3  |                    |      |

|                                                  | Cupply                                                      |                                                             | HSI RC osc. (16 MHz)      | 0.89 | 1.1                |      |

|                                                  |                                                             | $f_{CPU} = f_{MASTER}/128 = 125 \text{ kHz}$                | HSI RC osc. (16 MHz)      | 0.7  | 0.88               | mA   |

|                                                  | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8) <sup>(2)</sup>                       | 0.45                      | 0.57 |                    |      |

|                                                  |                                                             | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | LSI RC osc. (128 kHz)     | 0.4  | 0.54               |      |

<sup>1.</sup> Data based on characterization results, not tested in production.

<sup>2.</sup> Default clock configuration measured with all peripherals off.

<sup>2.</sup> Default clock configuration measured with all peripherals off.

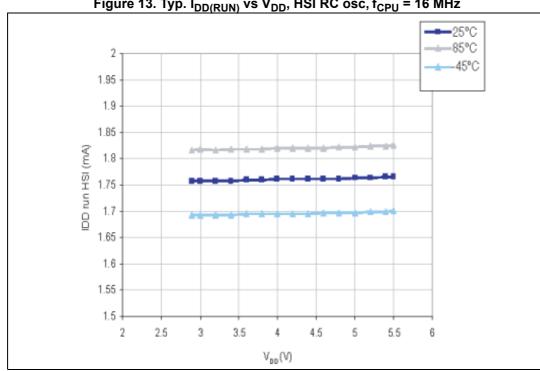

Figure 13. Typ.  $I_{DD(RUN)}$  vs  $V_{DD}$ , HSI RC osc,  $f_{CPU}$  = 16 MHz

Figure 27. Typ.  $V_{OL} @ V_{DD} = 3.3 \text{ V}$  (true open drain ports)

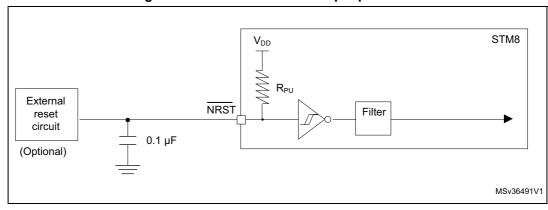

Figure 37. Recommended reset pin protection

### 9.3.8 SPI serial peripheral interface

Unless otherwise specified, the parameters given in *Table 43* are derived from tests performed under ambient temperature,  $f_{MASTER}$  frequency and  $V_{DD}$  supply voltage conditions.  $t_{MASTER} = 1/f_{MASTER}$ .

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                               | Parameter                    | Conditions                      |                          | Max                      | Unit    |

|------------------------------------------------------|------------------------------|---------------------------------|--------------------------|--------------------------|---------|

| f <sub>SCK</sub>                                     | SPI clock frequency          | Master mode                     | 0                        | 8                        | MHz     |

| 1/t <sub>c(SCK)</sub>                                | SF1 clock frequency          | Slave mode                      | 0                        | 7                        | IVII IZ |

| t <sub>r(SCK)</sub>                                  | SPI clock rise and fall time | Capacitive load: C = 30 pF      | -                        | 25                       |         |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                  | NSS setup time               | Slave mode                      | 4 x t <sub>MASTER</sub>  | -                        |         |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                   | NSS hold time                | Slave mode                      | 70                       | -                        |         |

| t <sub>w(SCKH)</sub> (1)<br>t <sub>w(SCKL)</sub> (1) | SCK high and low time        | Master mode                     | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |         |

| t <sub>su(MI)</sub> (1)                              | Data input setup time        | Master mode                     | 5                        | -                        |         |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)   | Data input setup time        | Slave mode                      |                          | -                        |         |

| t <sub>h(MI)</sub> (1)<br>t <sub>h(SI)</sub> (1)     | Data input hold time         | Master mode                     | 7                        | -                        | ns      |

| t <sub>h(SI)</sub> (1)                               | Data input noid time         | Slave mode                      | 10                       | -                        |         |

| t <sub>a(SO)</sub> (1)(2)                            | Data output access time      | Slave mode                      | -                        | 3 x t <sub>MASTER</sub>  |         |

| t <sub>dis(SO)</sub> (1)(3)                          | Data output disable time     | Slave mode                      | 25                       | -                        |         |

| t <sub>v(SO)</sub> (1)                               | Data output valid time       | Slave mode (after enable edge)  | -                        | 65                       |         |

| t <sub>v(MO)</sub> <sup>(1)</sup>                    | Data output valid time       | Master mode (after enable edge) | -                        | 30                       |         |

| t <sub>h(SO)</sub> <sup>(1)</sup>                    | Data output hold time        | Slave mode (after enable edge)  | 27                       | -                        |         |

| t <sub>h(MO)</sub> <sup>(1)</sup>                    | Data output hold time        | Master mode (after enable edge) | 11                       | -                        |         |

**Table 43. SPI characteristics**

<sup>2.</sup> Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

<sup>1.</sup> Values based on design simulation and/or characterization results, and not tested in production.

Figure 41. Typical application with I<sup>2</sup>C bus and timing diagram

1. Measurement points are made at CMOS levels: 0.3 x  $\rm V_{DD}$  and 0.7 x  $\rm V_{DD}$

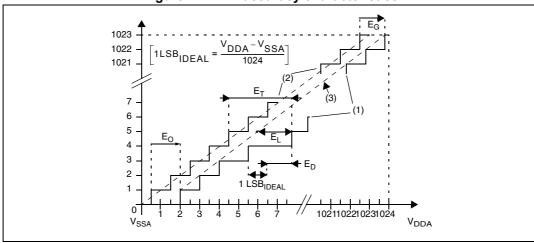

Figure 42. ADC accuracy characteristics

- 1. Example of an actual transfer curve.

- The ideal transfer curve

- End point correlation line

E<sub>T</sub> = Total unadjusted error: maximum deviation between the actual and the ideal transfer curves.

E<sub>O</sub> = Offset error: deviation between the first actual transition and the first ideal one.

E<sub>G</sub> = Gain error: deviation between the last ideal transition and the last actual one.

E<sub>D</sub> = Differential linearity error: maximum deviation between actual steps and the ideal one.

E<sub>L</sub> = Integral linearity error: maximum deviation between any actual transition and the end point correlation

Figure 43. Typical application with ADC

#### 9.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

### Functional EMS (electromagnetic susceptibility)

While executing a simple application (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- · Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be recovered by applying a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

Table 48. EMS data

| Symbol            | Parameter                                                                                                                                      | Conditions                                                                                                                                                 | Level/class       |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                 | $\begin{split} V_{DD} &= 3.3 \text{ V}, \text{ T}_{A} = 25 \text{ °C}, \\ f_{MASTER} &= 16 \text{ MHz}, \\ \text{conforming to IEC 61000-4-2} \end{split}$ | 2B <sup>(1)</sup> |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | $\begin{split} V_{DD} &= 3.3 \text{ V}, \text{ T}_{A} = 25 \text{ °C}, \\ f_{MASTER} &= 16 \text{ MHz}, \\ \text{conforming to IEC 61000-4-4} \end{split}$ | 4A <sup>(1)</sup> |

Data obtained with HSI clock configuration, after applying HW recommendations described in AN2860 -EMC guidelines for STM8Smicrocontrollers.

# 10 Package information

To meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at <a href="https://www.st.com">www.st.com</a>. ECOPACK® is an ST trademark.

### 10.1 LQFP32 package information

1. Drawing is not to scale.

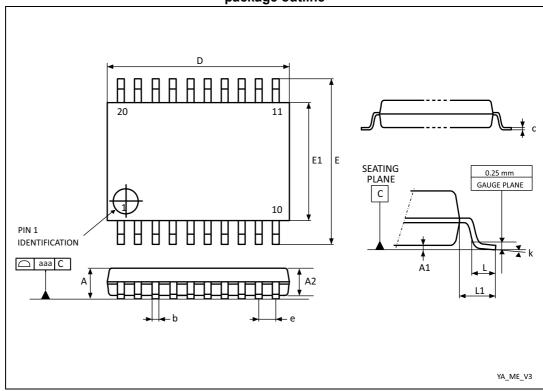

# 10.2 TSSOP20 package information

Figure 47.TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, package outline

1. Drawing is not to scale.

Table 53. TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, package mechanical data

|                   | puoluge meenumen uuta |             |       |        |                       |        |  |  |

|-------------------|-----------------------|-------------|-------|--------|-----------------------|--------|--|--|

| Symbol            |                       | millimeters |       |        | inches <sup>(1)</sup> |        |  |  |

| Зуппоп            | Min.                  | Тур.        | Max.  | Min.   | Тур.                  | Max.   |  |  |

| Α                 | -                     | -           | 1.200 | -      | -                     | 0.0472 |  |  |

| A1                | 0.050                 | -           | 0.150 | 0.0020 | -                     | 0.0059 |  |  |

| A2                | 0.800                 | 1.000       | 1.050 | 0.0315 | 0.0394                | 0.0413 |  |  |

| b                 | 0.190                 | -           | 0.300 | 0.0075 | -                     | 0.0118 |  |  |

| С                 | 0.090                 | -           | 0.200 | 0.0035 | -                     | 0.0079 |  |  |

| D <sup>(2)</sup>  | 6.400                 | 6.500       | 6.600 | 0.2520 | 0.2559                | 0.2598 |  |  |

| E                 | 6.200                 | 6.400       | 6.600 | 0.2441 | 0.2520                | 0.2598 |  |  |

| E1 <sup>(3)</sup> | 4.300                 | 4.400       | 4.500 | 0.1693 | 0.1732                | 0.1772 |  |  |

| е                 | -                     | 0.650       | -     | -      | 0.0256                | -      |  |  |

| L                 | 0.450                 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |  |  |

| L1                | -                     | 1.000       | -     | -      | 0.0394                | -      |  |  |

Table 53. TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, package mechanical data

| Symbol | millimeters |      |       | inches <sup>(1)</sup> |      |        |

|--------|-------------|------|-------|-----------------------|------|--------|

|        | Min.        | Тур. | Max.  | Min.                  | Тур. | Max.   |

| k      | 0°          | -    | 8°    | 0°                    | -    | 8°     |

| aaa    | -           | -    | 0.100 | -                     | -    | 0.0039 |

- 1. Values in inches are converted from mm and rounded to four decimal digits.

- 2. Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15mm per side.

- 3. Dimension "E1" does not include interlead flash or protrusions. Interlead flash or protrusions shall not exceed 0.25mm per side.

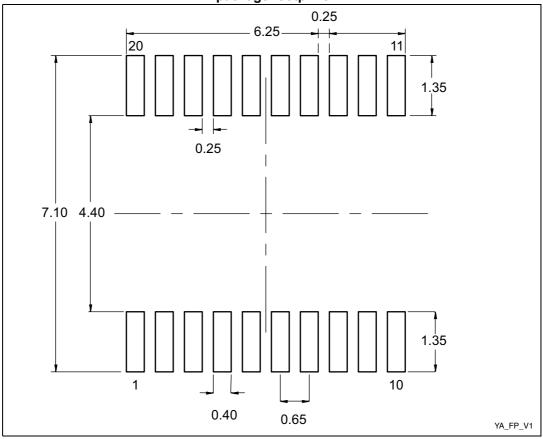

Figure 48. TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, package footprint

1. Dimensions are expressed in millimeters.

92/103 DocID018576 Rev 8

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics - All rights reserved