#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                           |

|---------------------------------|------------------------------------------------------------------------------------|

| Core Processor                  | MIPS32                                                                             |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                                     |

| Speed                           | 350MHz                                                                             |

| Co-Processors/DSP               | -                                                                                  |

| RAM Controllers                 | DDR                                                                                |

| Graphics Acceleration           | No                                                                                 |

| Display & Interface Controllers | -                                                                                  |

| Ethernet                        | 10/100Mbps (1)                                                                     |

| SATA                            | -                                                                                  |

| USB                             | -                                                                                  |

| Voltage - I/O                   | 3.3V                                                                               |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                                  |

| Security Features               |                                                                                    |

| Package / Case                  | 256-LBGA                                                                           |

| Supplier Device Package         | 256-CABGA (17x17)                                                                  |

| Purchase URL                    | https://www.e-xfl.com/product-detail/renesas-electronics-america/79rc32h434-350bci |

|                                 |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Signal      | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EJTAG_TMS   | Ι    | <b>EJTAG Mode</b> . The value on this signal controls the test mode select of the EJTAG Controller. When using the JTAG boundary scan, this pin should be left disconnected (since there is an internal pull-up) or driven high.                                                                                                                                                                                                                                                                                                                                                        |

| JTAG_TRST_N | I    | JTAG Reset. This active low signal asynchronously resets the boundary scan<br>logic, JTAG TAP Controller, and the EJTAG Debug TAP Controller. An external<br>pull-up on the board is recommended to meet the JTAG specification in cases<br>where the tester can access this signal. However, for systems running in func-<br>tional mode, one of the following should occur:<br>1) actively drive this signal low with control logic<br>2) statically drive this signal low with an external pull-down on the board<br>3) clock JTAG_TCK while holding EJTAG_TMS and/or JTAG_TMS high. |

| JTAG_TCK    | I    | JTAG Clock. This is an input test clock used to clock the shifting of data into or out of the boundary scan logic, JTAG Controller, or the EJTAG Controller. JTAG_TCK is independent of the system and the processor clock with a nominal 50% duty cycle.                                                                                                                                                                                                                                                                                                                               |

| JTAG_TDO    | 0    | <b>JTAG Data Output</b> . This is the serial data shifted out from the boundary scan logic, JTAG Controller, or the EJTAG Controller. When no data is being shifted out, this signal is tri-stated.                                                                                                                                                                                                                                                                                                                                                                                     |

| JTAG_TDI    | Ι    | <b>JTAG Data Input</b> . This is the serial data input to the boundary scan logic, JTAG Controller, or the EJTAG Controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| System      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CLK         | I    | <b>Master Clock</b> . This is the master clock input. The processor frequency is a mul-<br>tiple of this clock frequency. This clock is used as the system clock for all mem-<br>ory and peripheral bus operations.                                                                                                                                                                                                                                                                                                                                                                     |

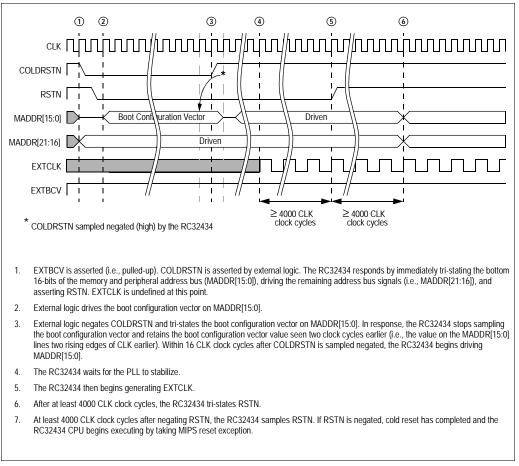

| EXTBCV      | I    | <b>Load External Boot Configuration Vector.</b> When this pin is asserted (i.e., high) the boot configuration vector is loaded from an externally supplied value during a cold reset.                                                                                                                                                                                                                                                                                                                                                                                                   |

| EXTCLK      | 0    | <b>External Clock.</b> This clock is used for all memory and peripheral bus operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| COLDRSTN    | Ι    | <b>Cold Reset.</b> The assertion of this signal initiates a cold reset. This causes the processor state to be initialized, boot configuration to be loaded, and the internal PLL to lock onto the master clock (CLK).                                                                                                                                                                                                                                                                                                                                                                   |

| RSTN        | I/O  | <b>Reset</b> . The assertion of this bidirectional signal initiates a warm reset. This signal is asserted by the RC32434 during a warm reset.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Table 1 Pin Description (Part 6 of 6)

### **Pin Characteristics**

**Note:** Some input pads of the RC32434 do not contain internal pull-ups or pull-downs. Unused inputs should be tied off to appropriate levels. This is especially critical for unused control signal inputs (such as WAITACKN) which, if left floating, could adversely affect the RC32434's operation. Also, any input pin left floating can cause a slight increase in power consumption.

| Function                       | Pin Name      | Туре | Buffer             | I/О Туре       | Internal<br>Resistor | Notes <sup>1</sup>            |

|--------------------------------|---------------|------|--------------------|----------------|----------------------|-------------------------------|

| Memory and Peripheral          | BDIRN         | 0    | LVTTL              | High Drive     |                      |                               |

| Bus                            | BOEN          | 0    | LVTTL              | High Drive     |                      |                               |

|                                | WEN           | 0    | LVTTL              | High Drive     |                      |                               |

|                                | CSN[3:0]      | 0    | LVTTL              | High Drive     |                      |                               |

|                                | MADDR[21:0]   | I/O  | LVTTL              | High Drive     |                      |                               |

|                                | MDATA[7:0]    | I/O  | LVTTL              | High Drive     |                      |                               |

|                                | OEN           | 0    | LVTTL              | High Drive     |                      |                               |

|                                | RWN           | 0    | LVTTL              | High Drive     |                      |                               |

|                                | WAITACKN      | I    | LVTTL              | STI            | pull-up              |                               |

| DDR Bus                        | DDRADDR[13:0] | 0    | SSTL_2             |                |                      |                               |

|                                | DDRBA[1:0]    | 0    | SSTL_2             |                |                      |                               |

|                                | DDRCASN       | 0    | SSTL_2             |                |                      |                               |

|                                | DDRCKE        | 0    | SSTL_2/LVC-<br>MOS |                |                      |                               |

|                                | DDRCKN        | 0    | SSTL_2             |                |                      |                               |

|                                | DDRCKP        | 0    | SSTL_2             |                |                      |                               |

|                                | DDRCSN        | 0    | SSTL_2             |                |                      |                               |

|                                | DDRDATA[15:0] | I/O  | SSTL_2             |                |                      |                               |

|                                | DDRDM[1:0]    | 0    | SSTL_2             |                |                      |                               |

|                                | DDRDQS[1:0]   | I/O  | SSTL_2             |                |                      |                               |

|                                | DDRRASN       | 0    | SSTL_2             |                |                      |                               |

|                                | DDRVREF       |      | Analog             |                |                      |                               |

|                                | DDRWEN        | 0    | SSTL_2             |                |                      |                               |

| PCI Bus Interface              | PCIAD[31:0]   | I/O  | PCI                |                |                      |                               |

|                                | PCICBEN[3:0]  | I/O  | PCI                |                |                      |                               |

|                                | PCICLK        | 1    | PCI                |                |                      |                               |

|                                | PCIDEVSELN    | I/O  | PCI                |                |                      | pull-up on board              |

|                                | PCIFRAMEN     | I/O  | PCI                |                |                      | pull-up on board              |

|                                | PCIGNTN[3:0]  | I/O  | PCI                |                |                      | pull-up on board              |

|                                | PCIIRDYN      | I/O  | PCI                |                |                      | pull-up on board              |

|                                | PCILOCKN      | I/O  | PCI                |                |                      |                               |

|                                | PCIPAR        | I/O  | PCI                |                |                      |                               |

|                                | PCIPERRN      | I/O  | PCI                |                |                      |                               |

|                                | PCIREQN[3:0]  | I/O  | PCI                |                |                      | pull-up on board              |

|                                | PCIRSTN       | I/O  | PCI                |                |                      | pull-down on board            |

|                                | PCISERRN      | I/O  | PCI                | Open Collector |                      | pull-up on board              |

|                                | PCISTOPN      | I/O  | PCI                |                |                      | pull-up on board              |

|                                | PCITRDYN      | I/O  | PCI                |                |                      | pull-up on board              |

| General Purpose I/O            | GPIO[8:0]     | I/O  | LVTTL              | High Drive     | pull-up              | · ·                           |

|                                | GPIO[13:9]    | I/O  | PCI                | Ť              |                      | pull-up on board              |

| Serial Peripheral              | SCK           | 1/0  | LVTTL              | High Drive     | pull-up              | pull-up on board              |

| Interface                      | SDI           | I/O  | LVTTL              | High Drive     | pull-up              | pull-up on board              |

|                                | SDO           | I/O  | LVTTL              | High Drive     | pull-up              | pull-up on board              |

| I <sup>2</sup> C-Bus Interface | SCL           | 1/0  | LVTTL              | Low Drive/STI  | 1 ° F                | pull-up on board <sup>2</sup> |

|                                | SDA           | I/O  | LVTTL              | Low Drive/STI  |                      | pull-up on board <sup>2</sup> |

Table 2 Pin Characteristics (Part 1 of 2)

### **Boot Configuration Vector**

The encoding of the boot configuration vector is described in Table 3, and the vector input is illustrated in Figure 4. The value of the boot configuration vector read in by the RC32434 during a cold reset may be determined by reading the Boot Configuration Vector (BCV) Register.

| Signal      | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MADDR[3:0]  | CPU Pipeline Clock Multiplier. This field specifies the value by which the PLL multiplies the master clock input (CLK) to obtain the processor clock frequency (PCLK). For master clock input frequency constraints, refer to Table 3.2 in the RC32434 User Manual.         0x0 - PLL Bypass         0x1 - Multiply by 3         0x2 - Multiply by 4         0x3 - Multiply by 5 - Reserved         0x5 - Multiply by 6 - Reserved         0x6 - Multiply by 8         0x7 - Multiply by 10         0x8 - Multiply by 10         0x9 through 0xF - Reserved                                                                                                                                                                                                                                     |

| MADDR[5:4]  | External Clock Divider. This field specifies the value by which the IPBus clock<br>(ICLK), which is always 1/2 PCLK, is divided in order to generate the external clock<br>output on the EXTCLK pin.<br>0x0 - Divide by 1<br>0x1 - Divide by 2<br>0x2 - Divide by 4<br>0x3 - reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MADDR[6]    | Endian. This bit specifies the endianness.<br>0x0 - little endian<br>0x1 - big endian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MADDR[7]    | Reset Mode. This bit specifies the length of time the RSTN signal is driven.0x0 - Normal reset: RSTN driven for minimum of 4000 clock cycles. If the internal bootconfiguration vector is selected, the expiration of an 18-bit counter operating at themaster clock input (CLK) frequency is used as the PLL stabilization delay.0x1 - Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MADDR[10:8] | <ul> <li>PCI Mode. This bit controls the operating mode of the PCI bus interface. The initial value of the EN bit in the PCIC register is determined by the PCI mode.</li> <li>0x0 - Disabled (EN initial value is zero)</li> <li>0x1 - PCI satellite mode with PCI target not ready (EN initial value is one)</li> <li>0x2 - PCI satellite mode with suspended CPU execution (EN initial value is one)</li> <li>0x3 - PCI host mode with external arbiter (EN initial value is zero)</li> <li>0x4 - PCI host mode with internal arbiter using fixed priority arbitration algorithm (EN initial value is zero)</li> <li>0x5 - PCI host mode with internal arbiter using round robin arbitration algorithm (EN initial value is zero)</li> <li>0x6 - reserved</li> <li>0x7 - reserved</li> </ul> |

Table 3 Boot Configuration Encoding (Part 1 of 2)

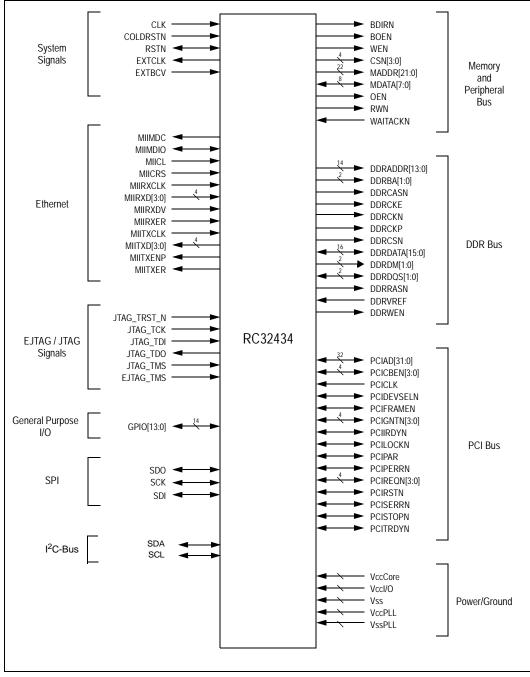

# Logic Diagram — RC32434

Figure 1 Logic Diagram

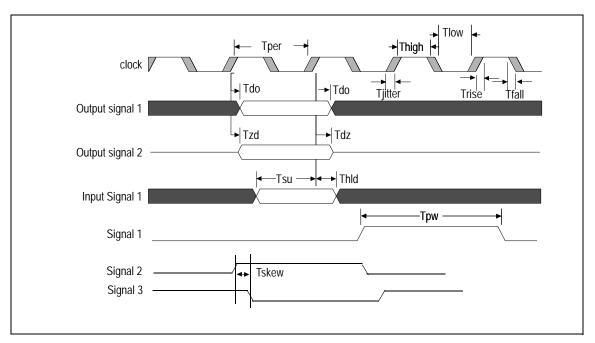

### AC Timing Definitions

Below are examples of the AC timing characteristics used throughout this document.

#### Figure 2 AC Timing Definitions Waveform

| Symbol   | Definition                                                                                                                                                                                                                  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tper     | Clock period.                                                                                                                                                                                                               |

| Tlow     | Clock low. Amount of time the clock is low in one clock period.                                                                                                                                                             |

| Thigh    | Clock high. Amount of time the clock is high in one clock period.                                                                                                                                                           |

| Trise    | Rise time. Low to high transition time.                                                                                                                                                                                     |

| Tfall    | Fall time. High to low transition time.                                                                                                                                                                                     |

| Tjitter  | Jitter. Amount of time the reference clock (or signal) edge can vary on either the rising or falling edges.                                                                                                                 |

| Tdo      | Data out. Amount of time after the reference clock edge that the output will become valid. The minimum time represents the data output hold. The maximum time represents the earliest time the designer can use the data.   |

| Tzd      | Z state to data valid. Amount of time after the reference clock edge that the tri-stated output takes to become valid.                                                                                                      |

| Tdz      | Data valid to Z state. Amount of time after the reference clock edge that the valid output takes to become tri-stated.                                                                                                      |

| Tsu      | Input set-up. Amount of time before the reference clock edge that the input must be valid.                                                                                                                                  |

| Thld     | Input hold. Amount of time after the reference clock edge that the input must remain valid.                                                                                                                                 |

| Трw      | Pulse width. Amount of time the input or output is active for asynchronous signals.                                                                                                                                         |

| Tslew    | Slew rate. The rise or fall rate for a signal to go from a high to low, or low to high.                                                                                                                                     |

| X(clock) | Timing value. This notation represents a value of 'X' multiplied by the clock time period of the specified clock. Using 5(CLK) as an example: $X = 5$ and the oscillator clock (CLK) = 25MHz, then the timing value is 200. |

| Tskew    | Skew. The amount of time two signal edges deviate from one another.                                                                                                                                                         |

Table 4 AC Timing Definitions

Figure 4 COLD Reset Operation with External Boot Configuration Vector AC Timing Waveform

**Note:** For a diagram showing the COLD Reset Operation with Internal Boot Configuration Vector, see Figure 3.6 in the RC32434 User Reference Manual.

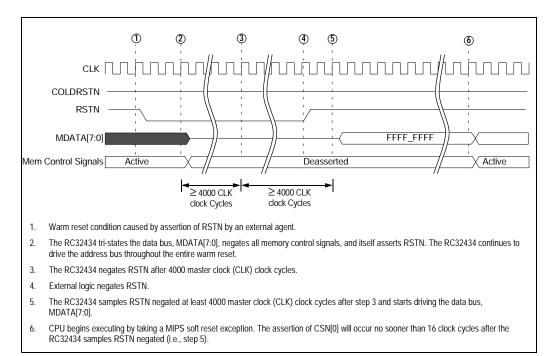

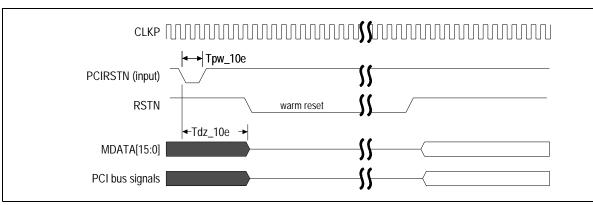

Figure 5 Externally Initiated Warm Reset AC Timing Waveform

| Signal                                                                                | Symbol              | Reference | 266   | MHz  | 300   | MHz              | 350  | MHz | 400  | MHz | Unit | Timing<br>Diagram |

|---------------------------------------------------------------------------------------|---------------------|-----------|-------|------|-------|------------------|------|-----|------|-----|------|-------------------|

| Signal                                                                                | Symbol              | Edge      | Min   | Max  | Min   | Max              | Min  | Max | Min  | Max | Onit | Reference         |

| Memory Bus - DI                                                                       | DR Access           |           |       |      |       |                  |      |     |      |     |      |                   |

| DDRDATA[15:0]                                                                         | Tskew_7g            | DDRDQSx   | 0     | 0.9  | 0     | 0.8 <sup>1</sup> | 0    | 0.7 | 0.0  | 0.6 | ns   | See Figures 6     |

|                                                                                       | Tdo_7k <sup>2</sup> |           | 1.2   | 1.9  | 1.0   | 1.7              | 0.7  | 1.5 | 0.5  | 1.4 | ns   | and 7.            |

| DDRDM[1:0]                                                                            | Tdo_7I              | DDRDQSx   | 1.2   | 1.9  | 1.0   | 1.7              | 0.7  | 1.5 | 0.5  | 1.4 | ns   |                   |

| DDRDQS[1:0]                                                                           | Tdo_7i              | DDRCKP    | -0.75 | 0.75 | -0.75 | 0.75             | -0.7 | 0.7 | -0.7 | 0.7 | ns   |                   |

| DDRADDR[13:0],<br>DDRBA[1:0],<br>DDRCASN,<br>DDRCKE,<br>DDRCSN,<br>DDRRASN,<br>DDRWEN | Tdo_7m              | DDRCKP    | 1.0   | 4.0  | 1.0   | 4.3              | 1.0  | 4.0 | 1.0  | 4.0 | ns   |                   |

#### Table 7 DDR SDRAM Timing Characteristics

<sup>1.</sup> Meets DDR timing requirements for 150MHz clock rate DDR SDRAMs with 300 ps remaining margin to compensate for PCB propagation mismatches, which is adequate to guarantee functional timing, provided the RC32434 DDR layout guidelines are adhered to.

<sup>2.</sup> Setup times are calculated as applicable clock period - Tdo max. For example, if the DDR is running at 266MHz, it uses a 133MHz input clock. The period for a 133MHz clock is 7.5ns. If the Tdo max value is 4.6ns, the T<sub>IS</sub> parameter is 7.5ns minus 4.6ns = 2.9ns. The DDR spec for this parameter is 1.9ns of slack left over for board propagation. Calculations for T<sub>DS</sub> are similar, but since this parameter is taken relative to the DDRDQS signals, which are referenced on both edges, the effective period with a 133MHz input clock is only 3.75ns. So, if the max Tdo is 1.9ns, we have 3.75ns minus 1.9ns = 1.85ns for T<sub>DS</sub>. The DDR data sheet specs a value of 0.5ns for 266MHz, so this leaves 1.35ns slack for board propagation delays.

| Signal                | Symbol              | Reference     | 266       | MHz | 300       | MHz | 350       | MHz | 400       | MHz | Unit | Condi- | Timing<br>Diagram |

|-----------------------|---------------------|---------------|-----------|-----|-----------|-----|-----------|-----|-----------|-----|------|--------|-------------------|

| Signal                | Зупрог              | Edge          | Min       | Мах | Min       | Мах | Min       | Мах | Min       | Max | Unit | tions  | Reference         |

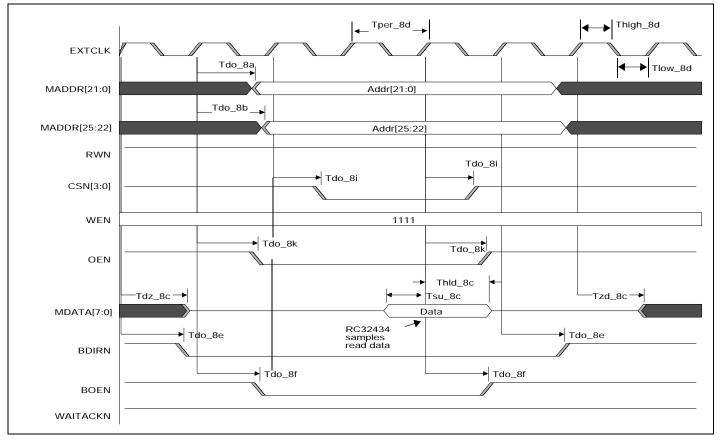

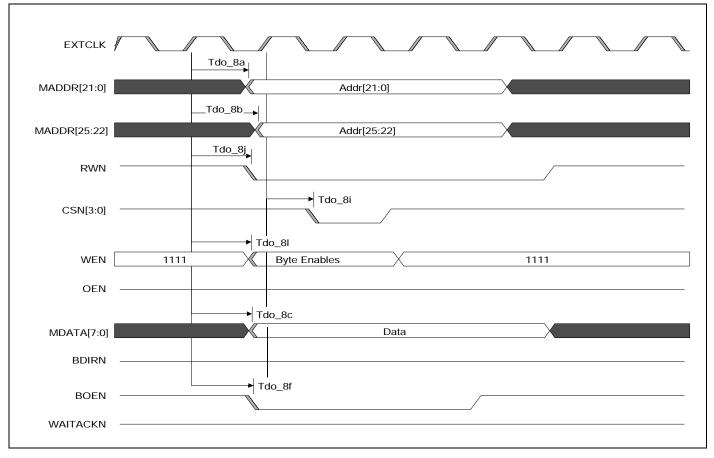

| MDATA[7:0]            | Tsu_8c              | EXTCLK rising | 6.0       | _   | 6.0       | _   | 6.0       |     | 6.0       | _   | ns   |        | See Figures 8     |

|                       | Thld_8c             |               | 0         | _   | 0         | _   | 0         | _   | 0         | _   | ns   |        | and 9 (cont.).    |

|                       | Tdo_8c              |               | 0.4       | 4.5 | 0.4       | 4.5 | 0.4       | 4.5 | 0.4       | 4.5 | ns   |        |                   |

|                       | Tdz_8c <sup>2</sup> |               | 0         | 0.5 | 0         | 0.5 | 0         | 0.5 | 0         | 0.5 | ns   |        |                   |

|                       | Tzd_8c <sup>2</sup> |               | 0.4       | 3.3 | 0.4       | 3.3 | 0.4       | 3.3 | 0.4       | 3.3 | ns   |        |                   |

| EXTCLK <sup>3</sup>   | Tper_8d             | none          | 7.5       | _   | 6.66      | _   | 6.66      | -   | 6.66      | _   | ns   |        |                   |

| BDIRN                 | Tdo_8e              | EXTCLK rising | 0.4       | 3.8 | 0.4       | 3.8 | 0.4       | 3.8 | 0.4       | 3.8 | ns   |        |                   |

|                       | Tdz_8e <sup>2</sup> |               | _         | —   | _         | _   | —         |     | —         | _   | ns   |        |                   |

|                       | Tzd_8e <sup>2</sup> |               | _         | —   | —         | —   | —         |     | —         | —   | ns   |        |                   |

| BOEN                  | Tdo_8f              | EXTCLK rising | 0.4       | 3.8 | 0.4       | 3.8 | 0.4       | 3.8 | 0.4       | 3.8 | ns   |        |                   |

|                       | Tdz_8f <sup>2</sup> |               | _         | —   | —         | —   | —         |     | —         | —   | ns   |        |                   |

|                       | Tzd_8f <sup>2</sup> |               | _         | —   | —         | —   | —         |     | —         | —   | ns   |        |                   |

| WAITACKN <sup>4</sup> | Tsu_8h              | EXTCLK rising | 6.5       | —   | 6.5       | _   | 6.5       |     | 6.5       | _   | ns   |        |                   |

|                       | Thld_8h             |               | 0         | -   | 0         | —   | 0         | _   | 0         | —   | ns   |        |                   |

|                       | Tpw_8h <sup>2</sup> | none          | 2(EXTCLK) | —   | 2(EXTCLK) | —   | 2(EXTCLK) | _   | 2(EXTCLK) | —   | ns   |        |                   |

| CSN[3:0]              | Tdo_8i              | EXTCLK rising | 0.4       | 4.0 | 0.4       | 4.0 | 0.4       | 4.0 | 0.4       | 4.0 | ns   |        |                   |

|                       | Tdz_8i <sup>2</sup> |               | —         | _   | —         | —   | -         | -   | —         | _   | ns   |        |                   |

|                       | Tzd_8i <sup>2</sup> |               | —         | —   | —         | —   | —         |     | —         | —   | ns   |        |                   |

| RWN                   | Tdo_8j              | EXTCLK rising | 0.4       | 3.8 | 0.4       | 3.8 | 0.4       | 3.8 | 0.4       | 3.8 | ns   |        |                   |

|                       | Tdz_8j <sup>2</sup> |               | _         | —   | _         | —   | —         |     | _         | —   | ns   |        |                   |

|                       | Tzd_8j <sup>2</sup> |               | —         | —   | -         | —   | -         |     | -         | —   | ns   |        |                   |

| OEN                   | Tdo_8k              | EXTCLK rising | 0.4       | 4.0 | 0.4       | 4.0 | 0.4       | 4.0 | 0.4       | 4.0 | ns   |        |                   |

|                       | Tdz_8k <sup>2</sup> |               | —         | —   | —         | —   | —         |     | —         | —   | ns   |        |                   |

|                       | Tzd_8k <sup>2</sup> |               | —         | —   | —         | —   | —         |     | —         | —   | ns   |        |                   |

| WEN                   | Tdo_8I              | EXTCLK rising | 0.4       | 3.7 | 0.4       | 3.7 | 0.4       | 3.7 | 0.4       | 3.7 | ns   |        |                   |

|                       | Tdz_8l <sup>2</sup> |               | _         | _   | _         | _   | —         |     | —         | _   | ns   |        |                   |

|                       | Tzd_8l <sup>2</sup> |               | _         | _   | _         | _   | _         |     | —         | _   | ns   |        |                   |

#### Table 8 Memory and Peripheral Bus AC Timing Characteristics (Part 2 of 2)

<sup>1.</sup> The RC32434 provides bus turnaround cycles to prevent bus contention when going from read to write, write to read, and during external bus ownership. For example, there are no cycles where an external device and the RC32434 are both driving. See Chapter 6, Device Controller, in the RC32434 User Reference Manual.

<sup>2.</sup> The values for this symbol were determined by calculation, not by testing.

<sup>3.</sup> The frequency of EXTCLK is programmable. See the External Clock Divider (MDATA[5:4]) description in Table 3 of this data sheet.

<sup>4.</sup> WAITACKN must meet the setup and hold times if it is synchronous or the minimum pulse width if it is asynchronous.

Figure 8 Memory and Peripheral Bus AC Timing Waveform — Read Access

Figure 9 Memory and Peripheral Bus AC Timing Waveform — Write Access

| Cianal                                                        | Cumple of              | Reference          | 266           | MHz  | 300           | MHz  | 350           | MHz  | 400           | MHz  | 1.1  | Condi-        | Timing                   |

|---------------------------------------------------------------|------------------------|--------------------|---------------|------|---------------|------|---------------|------|---------------|------|------|---------------|--------------------------|

| Signal                                                        | Symbol                 | Edge               | Min           | Мах  | Min           | Мах  | Min           | Max  | Min           | Мах  | Unit | tions         | Diagram<br>Reference     |

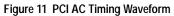

| PCI <sup>1</sup>                                              |                        |                    |               |      |               |      |               |      |               |      | •    |               | 1                        |

| PCICLK <sup>2</sup>                                           | Tper_10a               | none               | 15.0          | 30.0 | 15.0          | 30.0 | 15.0          | 30.0 | 15.0          | 30.0 | ns   | 66 MHz<br>PCI | See Figure 11.           |

|                                                               | Thigh_10a,<br>Tlow_10a |                    | 6.0           | _    | 6.0           | _    | 6.0           | _    | 6.0           | _    | ns   |               |                          |

|                                                               | Tslew_10a              |                    | 1.5           | 4.0  | 1.5           | 4.0  | 1.5           | 4.0  | 1.5           | 4.0  | V/ns |               |                          |

| PCIAD[31:0],                                                  | Tsu_10b                | PCICLK rising      | 3.0           | —    | 3.0           | —    | 3.0           | —    | 3.0           | —    | ns   |               |                          |

| PCIBEN[3:0],<br>PCIDEVSELN,                                   | Thld_10b               |                    | 0             | —    | 0             | —    | 0             | —    | 0             | —    | ns   |               |                          |

| PCIFRA-                                                       | Tdo_10b                |                    | 2.0           | 6.0  | 2.0           | 6.0  | 2.0           | 6.0  | 2.0           | 6.0  | ns   |               |                          |

| MEN,PCIIR-<br>DYN,                                            | Tdz_10b <sup>3</sup>   |                    | —             | 14.0 | —             | 14.0 | —             | 14.0 | —             | 14.0 | ns   |               |                          |

| PCILOCKN,<br>PCIPAR, PCI-<br>PERRN, PCIS-<br>TOPN,<br>PCITRDY | Tzd_10b <sup>3</sup>   |                    | 2.0           | _    | 2.0           | _    | 2.0           | _    | 2.0           | _    | ns   |               |                          |

| PCIGNTN[3:0],                                                 | Tsu_10c                | PCICLK rising      | 5.0           | —    | 5.0           | _    | 5.0           | _    | 5.0           | _    | ns   |               |                          |

| PCIREQN[3:0]                                                  | Thld_10c               |                    | 0             | -    | 0             | -    | 0             | _    | 0             | -    | ns   |               |                          |

|                                                               | Tdo_10c                |                    | 2.0           | 6.0  | 2.0           | 6.0  | 2.0           | 6.0  | 2.0           | 6.0  | ns   |               |                          |

| PCIRSTN (out-<br>put) <sup>4</sup>                            | Tpw_10d <sup>3</sup>   | None               | 4000<br>(CLK) | —    | 4000<br>(CLK) | —    | 4000<br>(CLK) | _    | 4000<br>(CLK) | —    | ns   |               | See Figures 15<br>and 16 |

| PCIRSTN                                                       | Tpw_10e <sup>3</sup>   | None               | 2(CLK)        | —    | 2(CLK)        | —    | 2(CLK)        | _    | 2(CLK)        | —    | ns   |               |                          |

| (input) <sup>4,5</sup>                                        | Tdz_10e <sup>3</sup>   | PCIRSTN<br>falling | 6(CLK)        | _    | 6(CLK)        | _    | 6(CLK)        | _    | 6(CLK)        | _    | ns   |               |                          |

| PCISERRN <sup>6</sup>                                         | Tsu_10f                | PCICLK rising      | 3.0           | —    | 3.0           | —    | 3.0           | —    | 3.0           | —    | ns   |               | See Figure 11            |

|                                                               | Thld_10f               |                    | 0             | —    | 0             | —    | 0             | —    | 0             | —    | ns   |               |                          |

|                                                               | Tdo_10f                |                    | 2.0           | 6.0  | 2.0           | 6.0  | 2.0           | 6.0  | 2.0           | 6.0  | ns   |               |                          |

| PCIMUINTN <sup>6</sup>                                        | Tdo_10g                | PCICLK rising      | 4.7           | 11.1 | 4.7           | 11.1 | 4.7           | 11.1 | 4.7           | 11.1 | ns   |               |                          |

#### Table 10 PCI AC Timing Characteristics

$^{1\cdot}$  This PCI interface conforms to the PCI Local Bus Specification, Rev 2.2.

<sup>2.</sup> PCICLK must be equal to or less than two times ICLK (PCICLK <= 2(ICLK)) with a maximum PCICLK of 66 MHz.

$^{\mbox{3.}}$  The values for this symbol were determined by calculation, not by testing.

$^{\rm 4.}$  PCIRSTN is an output in host mode and an input in satellite mode.

<sup>5.</sup> To meet the PCI delay specification from reset asserted to outputs floating, the PCI reset should be logically combined with the COLDRSTN input, instead of input on PCIRSTN.

<sup>6.</sup> PCISERRN and PCIMUINTN use open collector I/O types.

| COLDRSTN<br>PCIRSTN (output)<br>RSTN | cold reset<br>PCI interface enabled<br>(tri-state)<br>warm reset                                                                                      |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                      | t, PCIRSTN is tri-stated and requires a pull-down to reach a low state.<br>d in host mode, PCIRSTN will be driven either high or low depending on the |  |

Figure 12 PCI AC Timing Waveform — PCI Reset in Host Mode

Figure 13 PCI AC Timing Waveform — PCI Reset in Satellite Mode

|                                                          | <b>C 1 1</b>           | Reference   | 266 | MHz  | 300 | MHz  | 350 | MHz  | 400 | MHz  |      |            | Timing               |

|----------------------------------------------------------|------------------------|-------------|-----|------|-----|------|-----|------|-----|------|------|------------|----------------------|

| Signal                                                   | Symbol                 | Edge        | Min | Мах  | Min | Max  | Min | Max  | Min | Max  | Unit | Conditions | Diagram<br>Reference |

| I <sup>2</sup> C <sup>1</sup>                            |                        |             |     |      |     |      |     |      |     |      |      |            |                      |

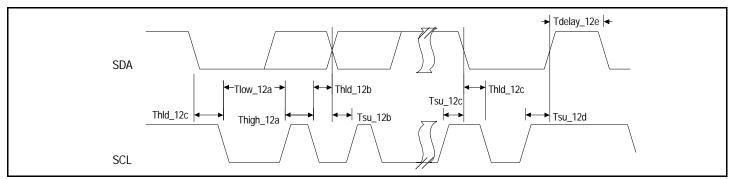

| SCL                                                      | Frequency              | none        | 0   | 100  | 0   | 100  | 0   | 100  | 0   | 100  | kHz  | 100 KHz    | See Figure 14.       |

|                                                          | Thigh_12a,<br>Tlow_12a |             | 4.0 | -    | 4.0 | Ι    | 4.0 | Ι    | 4.0 | Ι    | μs   |            |                      |

|                                                          | Trise_12a              |             | _   | 1000 | _   | 1000 | _   | 1000 | _   | 1000 | ns   |            |                      |

|                                                          | Tfall_12a              |             | _   | 300  | _   | 300  | _   | 300  | —   | 300  | ns   |            |                      |

| SDA                                                      | Tsu_12b                | SCL rising  | 250 | _    | 250 | —    | 250 | —    | 250 | —    | ns   |            |                      |

|                                                          | Thld_12b               |             | 0   | 3.45 | 0   | 3.45 | 0   | 3.45 | 0   | 3.45 | μs   |            |                      |

|                                                          | Trise_12b              |             | _   | 1000 | _   | 1000 | _   | 1000 | _   | 1000 | ns   |            |                      |

|                                                          | Tfall_12b              |             |     | 300  |     | 300  | _   | 300  | _   | 300  | ns   |            |                      |

| Start or repeated start                                  | Tsu_12c                | SDA falling | 4.7 | _    | 4.7 | _    | 4.7 | —    | 4.7 | —    | μs   |            |                      |

| condition                                                | Thld_12c               |             | 4.0 | —    | 4.0 | —    | 4.0 | —    | 4.0 | —    | μs   |            |                      |

| Stop condition                                           | Tsu_12d                | SDA rising  | 4.0 | _    | 4.0 | —    | 4.0 | —    | 4.0 | —    | μs   |            |                      |

| Bus free time between<br>a stop and start condi-<br>tion | Tdelay_12e             |             | 4.7 |      | 4.7 | Ι    | 4.7 | Ι    | 4.7 | Ι    | μs   |            |                      |

| SCL                                                      | Frequency              | none        | 0   | 400  | 0   | 400  | 0   | 400  | 0   | 400  | kHz  | 400 KHz    |                      |

|                                                          | Thigh_12a,<br>Tlow_12a |             | 0.6 | -    | 0.6 | -    | 0.6 | —    | 0.6 | —    | μs   |            |                      |

|                                                          | Trise_12a              |             |     | 300  |     | 300  | —   | 300  | _   | 300  | ns   |            |                      |

|                                                          | Tfall_12a              |             |     | 300  |     | 300  | —   | 300  | _   | 300  | ns   |            |                      |

| SDA                                                      | Tsu_12b                | SCL rising  | 100 | —    | 100 | —    | 100 | —    | 100 | —    | ns   |            |                      |

|                                                          | Thld_12b               |             | 0   | 0.9  | 0   | 0.9  | 0   | 0.9  | 0   | 0.9  | μs   |            |                      |

|                                                          | Trise_12b              | ]           |     | 300  |     | 300  | _   | 300  | _   | 300  | ns   |            |                      |

|                                                          | Tfall_12ba             |             | _   | 300  | _   | 300  | _   | 300  | —   | 300  | ns   |            |                      |

Table 11 I<sup>2</sup>C AC Timing Characteristics (Part 1 of 2)

| Signal                                                   | Symbol     | Reference<br>Edge | 266MHz |     | 300MHz |     | 350MHz |     | 400MHz |     | Unit | Conditions | Timing<br>Diagram |

|----------------------------------------------------------|------------|-------------------|--------|-----|--------|-----|--------|-----|--------|-----|------|------------|-------------------|

| Signal                                                   | Symbol     |                   | Min    | Мах | Min    | Max | Min    | Мах | Min    | Max | Unit | Conditions | Reference         |

| Start or repeated start                                  | Tsu_12c    | SDA falling       | 0.6    | —   | 0.6    | —   | 0.6    | _   | 0.6    | _   | μs   | 400 KHz    | See Figure 14.    |

| condition                                                | Thld_12c   |                   | 0.6    | —   | 0.6    | _   | 0.6    |     | 0.6    | _   | μs   |            |                   |

| Stop condition                                           | Tsu_12d    | SDA rising        | 0.6    | —   | 0.6    | —   | 0.6    | _   | 0.6    | _   | μs   |            |                   |

| Bus free time between<br>a stop and start condi-<br>tion | Tdelay_12e |                   | 1.3    | _   | 1.3    |     | 1.3    | _   | 1.3    |     | μs   |            |                   |

Table 11 I<sup>2</sup>C AC Timing Characteristics (Part 2 of 2)

$^{1.}$  For more information, see the  $I^{2}C\mbox{-Bus}$  specification by Philips Semiconductor.

#### Figure 14 I2C AC Timing Waveform

| Signal     | Signal I Sympoli     | Reference | 266MHz  |         | 300MHz  |     | 350MHz  |         | 400MHz  |     | Unit | Condi- | Timing<br>Diagram |

|------------|----------------------|-----------|---------|---------|---------|-----|---------|---------|---------|-----|------|--------|-------------------|

| Signal     | Symbol               | Edge      | Min     | Min Max |         | Max | Min     | Min Max |         | Мах | Unit | tions  | Reference         |

| GPIO       |                      |           |         |         |         |     |         |         |         |     |      |        |                   |

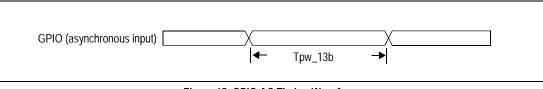

| GPIO[13:0] | Tpw_13b <sup>1</sup> | None      | 2(ICLK) | —       | 2(ICLK) | _   | 2(ICLK) | _       | 2(ICLK) | —   | ns   |        | See Figure 15.    |

Table 12 GPIO AC Timing Characteristics

<sup>1.</sup> The values for this symbol were determined by calculation, not by testing.

۱

#### Using the EJTAG Probe

In Figure 20, the pull-up resistors for JTAG\_TDO and RST\*, the pull-down resistor for JTAG\_TRST\_N, and the series resistor for JTAG\_TDO must be adjusted to the specific design. However, the recommended pull-up/down resistor is 1.0 k $\Omega$  because a low value reduces crosstalk on the cable to the connector, allowing higher JTAG\_TCK frequencies. A typical value for the series resistor is 33  $\Omega$ . Recommended resistor values have ± 5% tolerance.

If a probe is used, the pull-up resistor on JTAG\_TDO must ensure that the JTAG\_TDO level is high when no probe is connected and the JTAG\_TDO output is tri-stated. This requirement allows reliable connection of the probe if it is hooked-up when the power is already on (hot plug). The pull-up resistor value of around 47 k $\Omega$  should be sufficient. Optional diodes to protect against overshoot and undershoot voltage can be added on the signals of the chip with EJTAG.

If a probe is used, the RST\* signal must have a pull-up resistor because it is controlled by an open-collector (OC) driver in the probe, and thus is actively pulled low only. The pull-up resistor is responsible for the high value when not driven by the probe of 25pF. The input on the target system reset circuit must be able to accept the rise time when the pull-up resistor charges the capacitance to a high logical level. Vcc I/O must connect to a voltage reference that drops rapidly to below 0.5V when the target system loses power, even with a capacitive load of 25pF. The probe can thus detect the lost power condition.

For additional information on EJTAG, refer to Chapter 17 of the RC32434 User Reference Manual.

### Phase-Locked Loop (PLL)

The phase-locked loop (PLL) multiplies the external oscillator input (pin CLK) according to the parameter provided by the boot configuration vector to create the processor clock (PCLK). Inherently, PLL circuits are only capable of generating clock frequencies within a limited range.

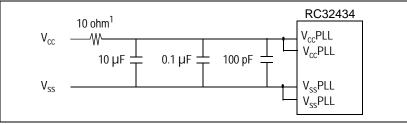

#### PLL Filters

It is recommended that the system designer provide a filter network of passive components for the PLL analog and digital power supplies. The PLL circuit power and PLL circuit ground should be isolated from power and ground with a filter circuit such as the one shown in Figure 21. Because the optimum values for the filter components depend upon the application and the system noise environment, these values should be considered as starting points for further experimentation within your specific application.

Figure 21 PLL Filter Circuit for Noisy Environments

### **Power-on Sequence**

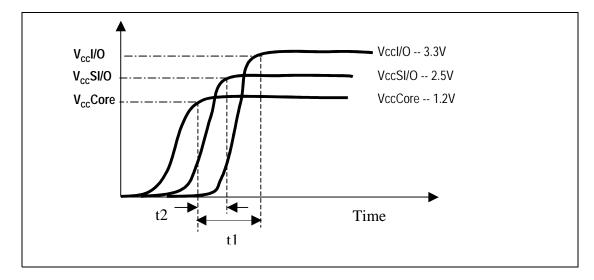

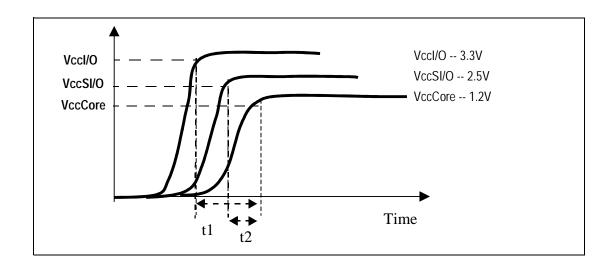

Three power-on sequences are given below. Sequence #1 is recommended because it will prevent I/O conflicts and will also allow the input signals to propagate when the I/O powers are brought up.

Note: The ESD diodes may be damaged if one of the voltages is applied and one of the other voltages is at a ground level.

#### A. Recommended Sequence

- t2 > 0 whenever possible (V<sub>cc</sub>Core)

- t1 t2 can be 0 ( $V_{cc}SI/O$  followed by  $V_{cc}I/O$ )

#### B. Reverse Voltage Sequence

If sequence A is not feasible, then Sequence B can be used:

t1 <50ms and t2 <50ms to prevent damage.

#### C. Simultaneous Power-up

Vccl/O, VccSl/O, and VccCore can be powered up simultaneously.

## **DC Electrical Characteristics**

Values based on systems running at recommended supply voltages, as shown in Table 15.

Note: See Table 2, Pin Characteristics, for a complete I/O listing.

| I/О Туре                       | Para-<br>meter                                 | Min.                                           | Typical | Max.                             | Unit | Conditions                                                        |

|--------------------------------|------------------------------------------------|------------------------------------------------|---------|----------------------------------|------|-------------------------------------------------------------------|

| LOW Drive<br>Output            | I <sub>OL</sub>                                | —                                              | 14.0    | —                                | mA   | $V_{OL} = 0.4V$                                                   |

|                                | I <sub>OH</sub>                                | —                                              | -12.0   | —                                | mA   | V <sub>OH</sub> = 1.5V                                            |

| HIGH Drive<br>Output           | I <sub>OL</sub>                                | —                                              | 41.0    | —                                | mA   | $V_{OL} = 0.4V$                                                   |

|                                | I <sub>OH</sub>                                | —                                              | -42.0   | —                                | mA   | V <sub>OH</sub> = 1.5V                                            |

| Schmitt Trigger<br>Input (STI) | V <sub>IL</sub>                                | -0.3                                           | _       | 0.8                              | V    | _                                                                 |

|                                | V <sub>IH</sub>                                | 2.0                                            | _       | $V_{cc}I/O + 0.5$                | V    | _                                                                 |

| SSTL_2 (for DDR                | I <sub>OL</sub>                                | 7.6                                            | —       | —                                | mA   | V <sub>OL</sub> = 0.5V                                            |

| SDRAM)                         | I <sub>OH</sub>                                | -7.6                                           | —       | —                                | mA   | V <sub>OH</sub> = 1.76V                                           |

|                                | V <sub>IL</sub>                                | -0.3                                           | _       | 0.5(V <sub>cc</sub> SI/O) - 0.18 | V    |                                                                   |

|                                | V <sub>IH</sub>                                | 0.5(V <sub>cc</sub> SI/O) + 0.18               | —       | $V_{cc}SI/O + 0.3$               | V    |                                                                   |

| PCI                            | I <sub>OH</sub> (AC)<br>Switching              | -12(V <sub>cc</sub> I/O)                       | —       | —                                | mA   | 0 < V <sub>OUT</sub> < 0.3(V <sub>cc</sub> I/O)                   |

|                                |                                                | -17.1(V <sub>cc</sub> I/O - V <sub>OUT</sub> ) |         | —                                | mA   | $0.3(V_{cc}I/O) < V_{OUT} < 0.9(V_{cc}I/O)$                       |

|                                |                                                | —                                              | _       | -32(V <sub>cc</sub> I/O)         | —    | 0.7(V <sub>cc</sub> l/O)                                          |

|                                |                                                | 16(V <sub>cc</sub> I/O)                        | _       | See Note 1                       | mA   | 0.7(V <sub>cc</sub> I/O) < V <sub>OUT</sub> < V <sub>cc</sub> I/O |

|                                | I <sub>OL</sub> (AC)<br>Switching              | +16(V <sub>cc</sub> I/O)                       |         | —                                | mA   | $V_{cc}I/O > V_{OUT} > 0.6(V_{cc}I/O)$                            |

|                                |                                                | +26.7(V <sub>OUT</sub> )                       | _       | —                                | mA   | $0.6(V_{cc}I/O) > V_{OUT} > 0.1(V_{cc}I/O)$                       |

|                                |                                                | —                                              | _       | +38(V <sub>cc</sub> I/O)         | mA   | $V_{OUT} = 0.18(V_{cc}I/O)$                                       |

|                                |                                                | —                                              | _       | See Note 2                       | mA   | 0.18(V <sub>cc</sub> I/O) > V <sub>OUT</sub> > 0                  |

|                                | V <sub>IL</sub>                                | -0.3                                           | _       | 0.3(V <sub>cc</sub> I/O)         | V    |                                                                   |

|                                | V <sub>IH</sub>                                | 0.5(V <sub>cc</sub> I/O)                       | _       | 5.5                              | V    |                                                                   |

| Capacitance                    | C <sub>IN</sub>                                | —                                              | _       | 10.5                             | pF   | _                                                                 |

| Leakage                        | Inputs                                         | —                                              | _       | <u>+</u> 10                      | μA   | Vcc (max)                                                         |

|                                | I/O <sub>LEAK W/O</sub><br>Pull-ups/<br>downs  | —                                              | _       | <u>+</u> 10                      | μA   | Vcc (max)                                                         |

|                                | I/O <sub>LEAK WITH</sub><br>Pull-ups/<br>downs | _                                              | _       | <u>+</u> 80                      | μA   | Vcc (max)                                                         |

### Table 18 DC Electrical Characteristics

Note 1:  $I_{OH}(AC)$  max = (98/V<sub>CC</sub>I/O) \* (V<sub>OUT</sub> - V<sub>CC</sub>I/O) \* (V<sub>OUT</sub> + 0.4V<sub>CC</sub>I/O)

Note 2:  $I_{OL}(AC)$  max = (256/ $V_{CC}I/O$ ) \*  $V_{OUT}$  \* ( $V_{CC}I/O$  -  $V_{OUT}$ )

## RC32434 Ground Pins

| V <sub>ss</sub> | V <sub>ss</sub> | V <sub>ss</sub> PLL |

|-----------------|-----------------|---------------------|

|                 |                 |                     |

| F6              | J6              | A11, B12            |

| F7              | J7              |                     |

| F8              | J8              |                     |

| F10             | J9              |                     |

| F11             | J10             |                     |

| G6              | K7              |                     |

| G7              | K8              |                     |

| G8              | К9              |                     |

| G9              | K10             |                     |

| G10             | K11             |                     |

| G11             | L6              |                     |

| H7              | L7              |                     |

| H8              | L9              |                     |

| H9              | L10             |                     |

| H10             | L11             |                     |

| H11             |                 |                     |

Table 23 RC32434 Ground Pins

## RC32434 Signals Listed Alphabetically

The following table lists the RC32434 pins in alphabetical order.

| Signal Name | I/О Туре | Location | Signal Category           |

|-------------|----------|----------|---------------------------|

| BDIRN       | 0        | C2       | Memory and Peripheral Bus |

| BOEN        | 0        | B1       |                           |

| CLK         | I        | C13      | System                    |

| COLDRSTN    | I        | C3       |                           |

| CSN[0]      | 0        | A4       | Memory and Peripheral Bus |

| CSN[1]      | 0        | B4       |                           |

| CSN[2]      | 0        | A3       |                           |

| CSN[3]      | 0        | B3       |                           |

Table 24 RC32434 Alphabetical Signal List (Part 1 of 7)

| Signal Name | I/О Туре | Location | Signal Category              |

|-------------|----------|----------|------------------------------|

| DDRDATA[15] | I/O      | H13      | DDR Bus                      |

| DDRDM[0]    | 0        | F15      |                              |

| DDRDM[1]    | 0        | G13      |                              |

| DDRDQS[0]   | I/O      | J16      |                              |

| DDRDQS[1]   | I/O      | G14      |                              |

| DDRRASN     | 0        | M13      |                              |

| DDRVREF     | I        | J14      |                              |

| DDRWEN      | 0        | L14      |                              |

| EJTAG_TMS   | I        | J4       | JTAG / EJTAG                 |

| EXTBCV      | I        | D11      | System                       |

| EXTCLK      | 0        | C1       |                              |

| GPIO[0]     | I/O      | H3       | General Purpose Input/Output |

| GPIO[1]     | I/O      | H4       |                              |

| GPIO[2]     | I/O      | J3       |                              |

| GPIO[3]     | I/O      | J1       |                              |

| GPIO[4]     | I/O      | A8       |                              |

| GPIO[5]     | I/O      | B8       |                              |

| GPIO[6]     | I/O      | C7       |                              |

| GPIO[7]     | I/O      | A7       |                              |

| GPIO[8]     | I/O      | L3       |                              |

| GPIO[9]     | I/O      | M4       |                              |

| GPIO[10]    | I/O      | P3       |                              |

| GPIO[11]    | I/O      | M3       |                              |

| GPIO[12]    | I/O      | M1       | 1                            |

| GPIO[13]    | I/O      | T2       | 1                            |

| JTAG_TCK    | Ι        | J2       | JTAG / EJTAG                 |

| JTAG_TDI    | Ι        | A12      | 1                            |

| JTAG_TDO    | 0        | K1       | 1                            |

| JTAG_TMS    | Ι        | C11      | 1                            |

| JTAG_TRSTN  | Ι        | D12      | 1                            |

Table 24 RC32434 Alphabetical Signal List (Part 3 of 7)

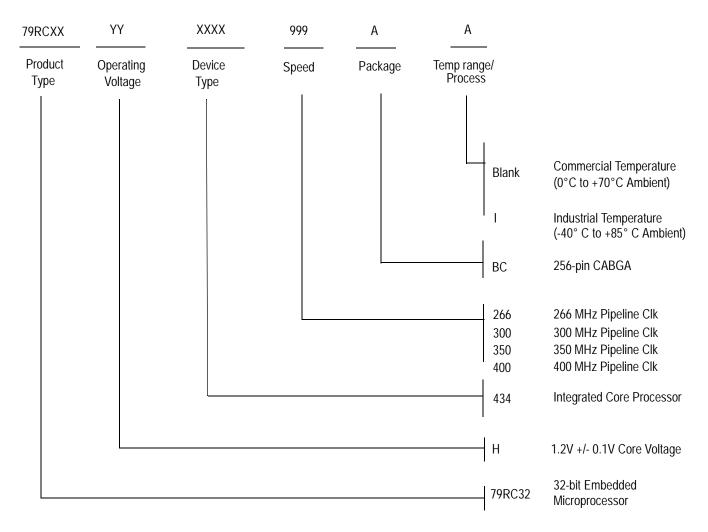

## Ordering Information

#### Valid Combinations

79RC32H434 - 266BC, 300BC, 350BC, 400BC256-pin CABGA package, Commercial Temperature79RC32H434 - 266BCI, 300BCI, 350BCI256-pin CABGA package, Industrial Temperature

*CORPORATE HEADQUARTERS* 6024 Silver Creek Valley Road San Jose, CA 95138 *for SALES:* 800-345-7015 or 408-284-8200 fax: 408-284-2775 www.idt.com *for Tech Support:* email: rischelp@idt.com phone: 408-284-8208