Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | 192KB (192K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 6K x 8                                                                  |

| RAM Size                   | 20K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

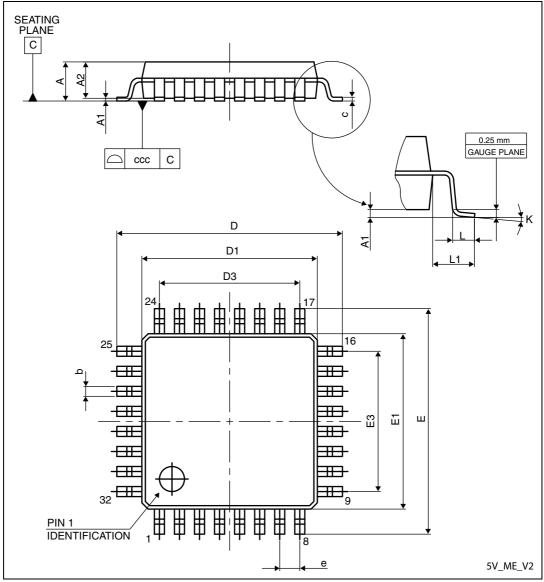

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l072czt6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.2 Interconnect matrix

Several peripherals are directly interconnected. This allows autonomous communication between peripherals, thus saving CPU resources and power consumption. In addition, these hardware connections allow fast and predictable latency.

Depending on peripherals, these interconnections can operate in Run, Sleep, Low-power run, Low-power sleep and Stop modes.

| Table 6. STM32LUXX peripherals interconnect matrix |                             |                                                                             |   |   |   |                        |      |  |  |

|----------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------|---|---|---|------------------------|------|--|--|

| Interconnect<br>source                             | Interconnect<br>destination | Interconnect action Run                                                     |   |   |   | Low-<br>power<br>sleep | Stop |  |  |

|                                                    | TIM2,TIM21,<br>TIM22        | Timer input channel,<br>trigger from analog<br>signals comparison           | Y | Y | Y | Y                      | -    |  |  |

| COMPx                                              | LPTIM                       | Timer input channel,<br>trigger from analog<br>signals comparison           | Y | Y | Y | Y                      | Y    |  |  |

| TIMx                                               | TIMx                        | Timer triggered by other timer                                              | Y | Y | Y | Y                      | -    |  |  |

| RTC                                                | TIM21                       | Timer triggered by Auto<br>wake-up                                          | Y | Y | Y | Y                      | -    |  |  |

| RIC                                                | LPTIM                       | Timer triggered by RTC event                                                | Y | Y | Y | Y                      | Y    |  |  |

| All clock<br>source                                | TIMx                        | Clock source used as<br>input channel for RC<br>measurement and<br>trimming | Y | Y | Y | Y                      | -    |  |  |

| USB                                                | CRS/HSI48                   | the clock recovery<br>system trims the HSI48<br>based on USB SOF            | Y | Y | - | -                      | -    |  |  |

|                                                    | TIM3                        | USB_SOF is channel<br>input for calibration                                 | Y | Y | - | -                      | -    |  |  |

|                                                    | TIMx                        | Timer input channel and trigger                                             | Y | Y | Y | Y                      | -    |  |  |

| GPIO                                               | LPTIM                       | Timer input channel and trigger                                             | Y | Y | Y | Y                      | Y    |  |  |

|                                                    | ADC,DAC                     | Conversion trigger                                                          | Y | Y | Y | Y                      | -    |  |  |

Table 6. STM32L0xx peripherals interconnect matrix

# 3.6 Low-power real-time clock and backup registers

The real time clock (RTC) and the 5 backup registers are supplied in all modes including standby mode. The backup registers are five 32-bit registers used to store 20 bytes of user application data. They are not reset by a system reset, or when the device wakes up from Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- Automatically correction for 28, 29 (leap year), 30, and 31 day of the month

- Two programmable alarms with wake up from Stop and Standby mode capability

- Periodic wakeup from Stop and Standby with programmable resolution and period

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- 2 anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 37 kHz)

- The high-speed external clock

# 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated alternate function registers. All GPIOs are high current capable. Each GPIO output, speed can be slowed (40 MHz, 10 MHz, 2 MHz, 400 kHz). The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to a dedicated IO bus with a toggling speed of up to 32 MHz.

## Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 29 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 84 GPIOs can be connected to the 16 configurable interrupt/event lines. The 13 other lines are connected to PVD, RTC, USB, USARTS, I2C, LPUART, LPTIMER or comparator events.

DocID027100 Rev 3

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                    | Memory address            |

|------------------------|--------------------------------------------------------------------------------|---------------------------|

| TSENSE_CAL1            | TS ADC raw data acquired at<br>temperature of 30 °C,<br>V <sub>DDA</sub> = 3 V | 0x1FF8 007A - 0x1FF8 007B |

| TSENSE_CAL2            | TS ADC raw data acquired at<br>temperature of 130 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |

Table 7. Temperature sensor calibration values

## 3.12.1 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (when no external voltage,  $V_{REF+}$ , is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

| Calibration value name | Description                                                            | Memory address            |  |  |

|------------------------|------------------------------------------------------------------------|---------------------------|--|--|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |  |  |

Table 8. Internal voltage reference measured values

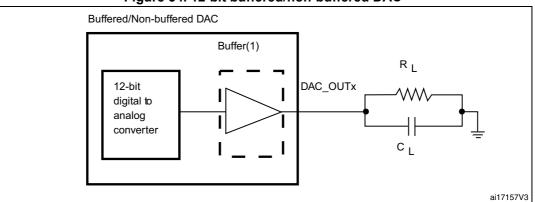

# 3.13 Digital-to-analog converter (DAC)

Two 12-bit buffered DACs can be used to convert digital signal into analog voltage signal output. An optional amplifier can be used to reduce the output signal impedance.

This digital Interface supports the following features:

- One data holding register (for each channel)

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channels with independent or simultaneous conversions

- DMA capability (including the underrun interrupt)

- External triggers for conversion

- Input reference voltage V<sub>REF+</sub>

Six DAC trigger inputs are used in the STM32L072xx. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

| Nar           | ne                     | Abbreviation                                                                                      | Definition                                                                                                                            |  |  |  |  |  |

|---------------|------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin n         | ame                    |                                                                                                   | Unless otherwise specified in brackets below the pin name, the pin function during and after reset is the same as the actual pin name |  |  |  |  |  |

|               |                        | S                                                                                                 | Supply pin                                                                                                                            |  |  |  |  |  |

| Pin t         | уре                    | I                                                                                                 | Input only pin                                                                                                                        |  |  |  |  |  |

|               |                        | I/O                                                                                               | Input / output pin                                                                                                                    |  |  |  |  |  |

|               |                        | FT                                                                                                | 5 V tolerant I/O                                                                                                                      |  |  |  |  |  |

|               |                        | FTf                                                                                               | 5 V tolerant I/O, FM+ capable                                                                                                         |  |  |  |  |  |

| I/O stru      | ucture                 | TC                                                                                                | Standard 3.3V I/O                                                                                                                     |  |  |  |  |  |

|               |                        | B Dedicated BOOT0 pin                                                                             |                                                                                                                                       |  |  |  |  |  |

|               |                        | RST                                                                                               | Bidirectional reset pin with embedded weak pull-up resistor                                                                           |  |  |  |  |  |

| Not           | es                     | Unless otherwise specified by a note, all I/Os are set as floating inputs during and after reset. |                                                                                                                                       |  |  |  |  |  |

| Pin functions | Alternate<br>functions | Functions selected throu                                                                          | gh GPIOx_AFR registers                                                                                                                |  |  |  |  |  |

|               | Additional functions   | Functions directly selected                                                                       | unctions directly selected/enabled through peripheral registers                                                                       |  |  |  |  |  |

| Table 15. Legend/abbreviations used in the | pinout table |

|--------------------------------------------|--------------|

|                                            |              |

# Table 16. STM32L072xxx pin definition

|        |                         |        | Pin n  | umb             | er      |         |         |                                       |          |               |      |                     |                      |  |

|--------|-------------------------|--------|--------|-----------------|---------|---------|---------|---------------------------------------|----------|---------------|------|---------------------|----------------------|--|

| LQFP32 | UFQFPN32 <sup>(1)</sup> | LQFP48 | LQFP64 | UFBGA64/TFBGA64 | WLCSP49 | LQFP100 | UFBG100 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Note | Alternate functions | Additional functions |  |

| -      | -                       | -      | -      | -               | -       | 1       | B2      | PE2                                   | I/O      | FT            | -    | TIM3_ETR            | -                    |  |

| -      | -                       | -      | -      | -               | -       | 2       | A1      | PE3                                   | I/O      | FT            | -    | TIM22_CH1, TIM3_CH1 | -                    |  |

| -      | -                       | -      | -      | -               | -       | 3       | B1      | PE4                                   | I/O      | FT            | -    | TIM22_CH2, TIM3_CH2 | -                    |  |

| -      | -                       | -      | -      | -               | -       | 4       | C2      | PE5                                   | I/O      | FT            | -    | TIM21_CH1, TIM3_CH3 | -                    |  |

| -      | -                       | -      | -      | -               | -       | 5       | D2      | PE6                                   | I/O      | FT            | I    | TIM21_CH2, TIM3_CH4 | RTC_TAMP3/WKUP3      |  |

| 1      | -                       | 1      | 1      | B2              | B6      | 6       | E2      | VDD                                   | S        |               | -    | _                   | -                    |  |

|        |                         | I      | Pin n  | umb             | er      |         |         |                                       |          |               |      |                                                                                                             |                           |

|--------|-------------------------|--------|--------|-----------------|---------|---------|---------|---------------------------------------|----------|---------------|------|-------------------------------------------------------------------------------------------------------------|---------------------------|

| LQFP32 | UFQFPN32 <sup>(1)</sup> | LQFP48 | LQFP64 | UFBGA64/TFBGA64 | WLCSP49 | LQFP100 | UFBG100 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Note | Alternate functions                                                                                         | Additional functions      |

| 27     | 26                      | 40     | 56     | A4              | В3      | 90      | A7      | PB4                                   | I/O      | FTf           | -    | SPI1_MISO, TIM3_CH1,<br>TSC_G5_IO2,<br>TIM22_CH1,<br>USART1_CTS,<br>USART5_RX, I2C3_SDA                     | COMP2_INP                 |

| 28     | 27                      | 41     | 57     | C4              | A4      | 91      | C5      | PB5                                   | I/O      | FT            | -    | SPI1_MOSI,<br>LPTIM1_IN1,<br>I2C1_SMBA,<br>TIM3_CH2/TIM22_CH2,<br>USART1_CK,<br>USART5_CK/USART5_R<br>TS_DE | COMP2_INP                 |

| 29     | 28                      | 42     | 58     | D3              | B4      | 92      | B5      | PB6                                   | I/O      | FTf           | -    | USART1_TX, I2C1_SCL,<br>LPTIM1_ETR,<br>TSC_G5_IO3                                                           | COMP2_INP                 |

| 30     | 29                      | 43     | 59     | C3              | C3      | 93      | B4      | PB7                                   | I/O      | FTf           | -    | USART1_RX,I2C1_SDA,<br>LPTIM1_IN2,<br>TSC_G5_IO4,<br>USART4_CTS                                             | COMP2_INP,<br>VREF_PVD_IN |

| 31     | 30                      | 44     | 60     | B4              | A5      | 94      | A4      | BOOT0                                 | Ι        |               | -    | _                                                                                                           | -                         |

| -      | -                       | 45     | 61     | В3              | B5      | 95      | A3      | PB8                                   | I/O      | FTf           | -    | TSC_SYNC, I2C1_SCL                                                                                          | -                         |

| -      | -                       | 46     | 62     | A3              | A6      | 96      | B3      | PB9                                   | I/O      | FTf           | -    | EVENTOUT, I2C1_SDA,<br>SPI2_NSS/I2S2_WS                                                                     | -                         |

| -      | -                       | -      | -      | -               | -       | 97      | C3      | PE0                                   | I/O      | FT            | -    | EVENTOUT                                                                                                    | -                         |

| -      | -                       | -      | -      | -               | -       | 98      | A2      | PE1                                   | I/O      | FT            | -    | EVENTOUT                                                                                                    | -                         |

| 32     | 31                      | 47     | 63     | D4              | -       | 99      | D3      | VSS                                   | S        | -             | -    | -                                                                                                           | -                         |

| -      | 32                      | 48     | 64     | E4              | A7      | 100     | C4      | VDD                                   | S        | -             | -    | -                                                                                                           | -                         |

Table 16. STM32L072xxx pin definition (continued)

1. UFQFPN32 pinout differs from other STM32 devices except STM32L07xxx and STM32L8xxx.

2. PA4 offers a reduced touch sensing sensitivity. It is thus recommended to use it as sampling capacitor I/O.

3. These pins are powered by VDD\_USB. For all characteristics that refer to  $V_{DD}$ ,  $V_{DD_USB}$  must be used instead.

# 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the ambient temperature condition summarized in *Table 26*.

| Symbol                          | Parameter                                  | Conditions                                          | Min       | Тур    | Мах      | Unit |

|---------------------------------|--------------------------------------------|-----------------------------------------------------|-----------|--------|----------|------|

|                                 |                                            | BOR detector enabled                                | 0         | -      | $\infty$ |      |

| t <sub>VDD</sub> <sup>(1)</sup> | V <sub>DD</sub> rise time rate             | BOR detector disabled                               | 0         | -      | 1000     | μs/V |

|                                 | ) ( foll time rete                         | 20 - ∞                                              | x         | - μs/v |          |      |

|                                 | V <sub>DD</sub> fall time rate             | BOR detector disabled                               | 0         | -      | 1000     |      |

| т (1)                           | Reset temporization                        | V <sub>DD</sub> rising, BOR enabled                 | -         | 2      | 3.3      | ma   |

| RSTTEMPO <sup>(1)</sup>         | Reset temponzation                         | V <sub>DD</sub> rising, BOR disabled <sup>(2)</sup> | 0.4       | 0.7    | 1.6      | ms   |

| M                               | Power on/power down reset                  | Falling edge                                        | 1         | 1.5    | 1.65     |      |

| V <sub>POR/PDR</sub>            | threshold                                  | Rising edge                                         | 1.3       | 1.5    | 1.65     |      |

|                                 |                                            | Falling edge                                        | 1.67      | 1.7    | 1.74     |      |

| V <sub>BOR0</sub>               | Brown-out reset threshold 0                | Rising edge                                         | 1.69      | 1.76   | 1.8      |      |

|                                 | Drewe out react threaded 4                 | Falling edge                                        | 1.87      | 1.93   | 1.97     |      |

| V <sub>BOR1</sub>               | Brown-out reset threshold 1                | Rising edge                                         | 1.96      | 2.03   | 2.07     |      |

| V <sub>BOR2</sub>               | Drewe out react threaded 2                 | Falling edge                                        | 2.22      | 2.30   | 2.35     |      |

|                                 | Brown-out reset threshold 2                | Rising edge                                         | 2.31      | 2.41   | 2.44     | 1    |

|                                 |                                            | Falling edge                                        | 2.45      | 2.55   | 2.6      |      |

| V <sub>BOR3</sub>               | Brown-out reset threshold 3 Rising edge    |                                                     | 2.54      | 2.66   | 2.7      |      |

|                                 |                                            | Falling edge                                        | 2.68      | 2.8    | 2.85     |      |

| V <sub>BOR4</sub>               | Brown-out reset threshold 4                | Rising edge                                         |           | 2.9    | 2.95     |      |

|                                 | Programmable voltage detector Falling edge |                                                     | 1.8       | 1.85   | 1.88     | V    |

| V <sub>PVD0</sub>               | threshold 0                                | Rising edge                                         | 1.88      | 1.94   | 1.99     |      |

| M                               | D) (D) there are a left 4                  | Falling edge                                        | 1.98      | 2.04   | 2.09     |      |

| V <sub>PVD1</sub>               | PVD threshold 1                            | Rising edge                                         | 2.08 2.14 |        | 2.18     |      |

|                                 | D) (D three held 2                         | Falling edge                                        | 2.20      | 2.24   | 2.28     | 1    |

| V <sub>PVD2</sub>               | PVD threshold 2                            | Rising edge                                         | 2.28      | 2.34   | 2.38     | 1    |

| N/                              | DVD threehold 2                            | Falling edge                                        | 2.39      | 2.44   | 2.48     |      |

| V <sub>PVD3</sub>               | PVD threshold 3                            | Rising edge                                         | 2.47      | 2.54   | 2.58     |      |

|                                 | D) (D three held 4                         | Falling edge                                        | 2.57      | 2.64   | 2.69     |      |

| V <sub>PVD4</sub>               | PVD threshold 4                            | Rising edge                                         | 2.68      | 2.74   | 2.79     |      |

|                                 |                                            | Falling edge                                        | 2.77      | 2.83   | 2.88     |      |

| V <sub>PVD5</sub>               | PVD threshold 5                            | Rising edge                                         | 2.87      | 2.94   | 2.99     |      |

| Table 27. Embedded reset and power control block characteristics |

|------------------------------------------------------------------|

|------------------------------------------------------------------|

| Symbol          | Parameter                              | Condition                                                                                                                                        |                                       | f <sub>HCLK</sub> (MHz) | Тур  | Max <sup>(1)</sup> | Unit    |

|-----------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------|------|--------------------|---------|

|                 |                                        |                                                                                                                                                  | Range3,                               | 1                       | 43,5 | 110                |         |

|                 |                                        |                                                                                                                                                  | Vcore=1.2 V                           | 2                       | 72   | 140                | 1       |

|                 |                                        |                                                                                                                                                  | VOS[1:0]=11                           | 4                       | 130  | 200                |         |

|                 |                                        | f <sub>HSE</sub> = f <sub>HCLK</sub> up to                                                                                                       | Range2,                               | 4                       | 160  | 220                |         |

|                 |                                        | 16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above                                                                                | Vcore=1.5 V                           | 8                       | 305  | 380                |         |

|                 |                                        | $16 \text{ MHz} (\text{PLL ON})^{(2)}$                                                                                                           | VOS[1:0]=10                           | 16                      | 590  | 690                |         |

|                 |                                        |                                                                                                                                                  | Range1,                               | 8                       | 370  | 460                |         |

|                 | Supply current in                      |                                                                                                                                                  | Vcore=1.8 V                           | 16                      | 715  | 840                |         |

|                 | Sleep mode, Flash<br>memory switched   |                                                                                                                                                  | VOS[1:0]=01                           | 32                      | 1650 | 2000               |         |

|                 | OFF                                    |                                                                                                                                                  | Range3,                               | 0,065                   | 18   | 93                 |         |

|                 |                                        | MSI clock                                                                                                                                        | Vcore=1.2 V                           | 0,524                   | 31,5 | 110                |         |

|                 |                                        |                                                                                                                                                  | VOS[1:0]=11                           | 4,2                     | 140  | 230                |         |

|                 |                                        | HSI clock source                                                                                                                                 | Range2,<br>Vcore=1.5 V<br>VOS[1:0]=10 | 16                      | 665  | 850                |         |

| I <sub>DD</sub> |                                        | (16 MHz)                                                                                                                                         | Range1,<br>Vcore=1.8 V<br>VOS[1:0]=01 | 32                      | 1750 | 2100               |         |

| (Sleep)         |                                        |                                                                                                                                                  | Range3,<br>Vcore=1.2 V<br>VOS[1:0]=11 | 1                       | 57,5 | 130                | μA<br>- |

|                 |                                        | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above<br>16 MHz (PLL ON) <sup>(2)</sup> |                                       | 2                       | 84   | 160                |         |

|                 |                                        |                                                                                                                                                  |                                       | 4                       | 150  | 220                |         |

|                 |                                        |                                                                                                                                                  | Range2,<br>Vcore=1.5 V<br>VOS[1:0]=10 | 4                       | 170  | 240                |         |

|                 |                                        |                                                                                                                                                  |                                       | 8                       | 315  | 400                |         |

|                 |                                        |                                                                                                                                                  |                                       | 16                      | 605  | 710                |         |

|                 |                                        |                                                                                                                                                  | Range1,                               | 8                       | 380  | 470                |         |

|                 | Supply current in<br>Sleep mode, Flash |                                                                                                                                                  | Vcore=1.8 V                           | 16                      | 730  | 860                |         |

|                 | memory switched                        |                                                                                                                                                  | VOS[1:0]=01                           | 32                      | 1650 | 2000               |         |

|                 | ON                                     |                                                                                                                                                  | Range3,                               | 0,065                   | 29,5 | 110                |         |

|                 |                                        | MSI clock                                                                                                                                        | Vcore=1.2 V                           | 0,524                   | 44,5 | 120                |         |

|                 |                                        |                                                                                                                                                  | VOS[1:0]=11                           | 4,2                     | 150  | 240                |         |

|                 |                                        | HSI clock source                                                                                                                                 | Range2,<br>Vcore=1.5 V<br>VOS[1:0]=10 | 16                      | 680  | 930                |         |

|                 |                                        | (16MHz)                                                                                                                                          | Range1,<br>Vcore=1.8 V<br>VOS[1:0]=01 | 32                      | 1750 | 2200               |         |

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol          | Parameter             |                                              | Condition                                         |                                            |       |          | Max <sup>(1)</sup> | Unit   |      |

|-----------------|-----------------------|----------------------------------------------|---------------------------------------------------|--------------------------------------------|-------|----------|--------------------|--------|------|

|                 |                       |                                              |                                                   | $T_A = -40$ to 25°C                        |       | 9,45     | 12                 |        |      |

|                 |                       |                                              | MSI clock = 65 kHz,                               | T <sub>A</sub> = 85°C                      | 0,032 | 14       | 58                 |        |      |

|                 |                       |                                              | f <sub>HCLK</sub> = 32 kHz                        | T <sub>A</sub> = 105°C                     | 0,032 | 21       | 64                 |        |      |

|                 |                       |                                              |                                                   | T <sub>A</sub> = 125°C                     |       | 36,5     | 160                |        |      |

|                 |                       | All peripherals                              |                                                   | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ |       | 14,5     | 18                 |        |      |

|                 |                       | OFF, code<br>executed from                   | MSI clock = 65 kHz,                               | T <sub>A</sub> = 85°C                      | 0,065 | 19,5     | 60                 |        |      |

|                 |                       | RAM, Flash                                   | f <sub>HCLK</sub> = 65kHz                         | T <sub>A</sub> = 105°C                     | 0,005 | 26       | 65                 |        |      |

|                 |                       | memory switched<br>OFF, V <sub>DD</sub> from |                                                   | T <sub>A</sub> = 125°C                     |       | 42       | 160                |        |      |

|                 |                       | 1.65 to 3.6 V                                |                                                   | $T_A = -40$ to 25°C                        |       |          | 26,5               | 30     |      |

|                 |                       |                                              |                                                   | T <sub>A</sub> = 55°C                      |       |          |                    |        | 27,5 |

|                 |                       |                                              | MSI clock=131 kHz,<br>f <sub>HCLK</sub> = 131 kHz | T <sub>A</sub> = 85°C                      | 0,131 | 0,131 31 | 66                 | μΑ<br> |      |

|                 | Supply                |                                              |                                                   | T <sub>A</sub> = 105°C                     |       | 37,5     | 77                 |        |      |

| I <sub>DD</sub> | Supply<br>current in  |                                              |                                                   | T <sub>A</sub> = 125°C                     |       | 53,5     | 170                |        |      |

| (LP Run)        | Low-power<br>run mode |                                              |                                                   | $T_A = -40$ to 25°C                        |       | 24,5     | 34                 |        |      |

|                 | run mode              |                                              | MSI clock = 65 kHz,                               | T <sub>A</sub> = 85°C                      | 0,032 | 30       | 82                 |        |      |

|                 |                       |                                              | f <sub>HCLK</sub> = 32 kHz                        | T <sub>A</sub> = 105°C                     | 0,032 | 38,5     | 90                 |        |      |

|                 |                       |                                              |                                                   | T <sub>A</sub> = 125°C                     |       | 58       | 120                |        |      |

|                 |                       | All peripherals                              |                                                   | $T_A = -40$ to $25^{\circ}C$               |       | 30,5     | 40                 |        |      |

|                 |                       | OFF, code                                    | MSI clock = 65 kHz,                               | T <sub>A</sub> = 85°C                      | 0,065 | 36,5     | 88                 |        |      |

|                 |                       | executed from<br>Flash memory,               | f <sub>HCLK</sub> = 65 kHz                        | T <sub>A</sub> = 105°C                     | 0,000 | 45       | 96                 |        |      |

|                 |                       | VDD from 1.65 V                              |                                                   | T <sub>A</sub> = 125°C                     |       | 64,5     | 120                |        |      |

|                 |                       | to 3.6 V                                     |                                                   | $T_A = -40$ to $25^{\circ}C$               |       | 45       | 56                 |        |      |

|                 |                       |                                              | MSI clock =                                       | T <sub>A</sub> = 55°C                      | 1     | 48       | 96                 |        |      |

|                 |                       |                                              | 131 kHz,                                          | T <sub>A</sub> = 85°C                      | 0,131 | 51       | 110                |        |      |

|                 |                       |                                              | f <sub>HCLK</sub> = 131 kHz                       | T <sub>A</sub> = 105°C                     |       | 59,5     | 120                |        |      |

|                 |                       |                                              |                                                   | T <sub>A</sub> = 125°C                     |       | 79,5     | 150                |        |      |

| Table 35. Current | consumption in | Low-power run mode |

|-------------------|----------------|--------------------|

|                   | eeneamparen m  | -on poner ran mous |

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

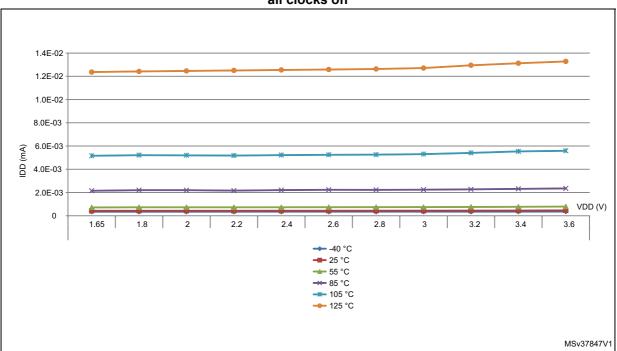

Figure 20.  $I_{DD}$  vs  $V_{DD}$ , at  $T_A$ = 25/55/85/105/125 °C, Stop mode with RTC disabled, all clocks off

| Table 38. Typical and maximum current consumptions in Standby mode |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

| Symbol          | Parameter                 | Conditi                                 | Тур                                        | Max <sup>(1)</sup> | Unit |    |

|-----------------|---------------------------|-----------------------------------------|--------------------------------------------|--------------------|------|----|

|                 |                           |                                         | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 0,855              | 1,70 |    |

|                 |                           |                                         | T <sub>A</sub> = 55 °C                     | -                  | 2,90 |    |

|                 |                           | Independent watchdog<br>and LSI enabled | T <sub>A</sub> = 85 °C                     | -                  | 3,30 |    |

| I <sub>DD</sub> |                           |                                         | T <sub>A</sub> = 105 °C                    | -                  | 4,10 |    |

|                 | Supply current in Standby |                                         | T <sub>A</sub> = 125 °C                    | -                  | 8,50 |    |

| (Standby)       | mode                      |                                         | T <sub>A</sub> = − 40 to 25°C              | 0,29               | 0,60 | μA |

|                 |                           |                                         | T <sub>A</sub> = 55 °C                     | 0,32               | 1,20 |    |

|                 |                           | Independent watchdog<br>and LSI off     | T <sub>A</sub> = 85 °C                     | 0,5                | 2,30 |    |

|                 |                           |                                         | T <sub>A</sub> = 105 °C                    | 0,94               | 3,00 |    |

|                 |                           |                                         | T <sub>A</sub> = 125 °C                    | 2,6                | 7,00 |    |

1. Guaranteed by characterization results at 125 °C, unless otherwise specified

| Symbol                     | Poriphoral                   | Typical consum         | ption, T <sub>A</sub> = 25 °C | – Unit |

|----------------------------|------------------------------|------------------------|-------------------------------|--------|

| Symbol                     | Peripheral –                 | V <sub>DD</sub> =1.8 V | V <sub>DD</sub> =3.0 V        |        |

| I <sub>DD(PVD / BOR)</sub> | I <sub>DD(PVD / BOR)</sub> - |                        | 1.2                           |        |

| I <sub>REFINT</sub>        | -                            | -                      | 1.7                           |        |

| -                          | LSE Low drive <sup>(2)</sup> | 0.11                   | 0,13                          |        |

| -                          | LSI                          | 0.27                   | 0.31                          |        |

| -                          | IWDG                         | 0.2                    | 0.3                           |        |

| -                          | LPTIM1, Input 100 Hz         | 0.01                   | 0,01                          | μA     |

| -                          | LPTIM1, Input 1 MHz          | 11                     | 12                            |        |

| - LPUART1                  |                              | -                      | 0,5                           |        |

| -                          | RTC                          | 0.16                   | 0,3                           |        |

1. LPTIM, LPUART peripherals can operate in Stop mode but not in Standby mode.

2. LSE Low drive consumption is the difference between an external clock on OSC32\_IN and a quartz between OSC32\_IN and OSC32\_OUT.-

## 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI or HSI16 RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is either the MSI oscillator in the range configured before entering Stop mode, the HSI16 or HSI16/4.

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 26*.

| Symbol                      | Parameter                         | Conditions                                               | Тур | Max | Unit               |

|-----------------------------|-----------------------------------|----------------------------------------------------------|-----|-----|--------------------|

| t <sub>WUSLEEP</sub>        | Wakeup from Sleep mode            | f <sub>HCLK</sub> = 32 MHz                               | 7   | 8   |                    |

| t <sub>WUSLEEP_</sub><br>LP | Wakeup from Low-power sleep mode, | f <sub>HCLK</sub> = 262 kHz<br>Flash memory enabled      | 7   | 8   | Number<br>of clock |

|                             | f <sub>HCLK</sub> = 262 kHz       | f <sub>HCLK</sub> = 262 kHz<br>Flash memory switched OFF | 9   | 10  | cycles             |

| Table 42 | Low-power | mode | wakeun | timinas |

|----------|-----------|------|--------|---------|

|          | LOW-POWEI | moue | waneup | unningə |

## 6.3.7 Internal clock source characteristics

The parameters given in *Table 47* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 26*.

### High-speed internal 16 MHz (HSI16) RC oscillator

| Symbol                                | Parameter                              | Conditions                                                                           | Min               | Тур      | Max              | Unit |

|---------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------|-------------------|----------|------------------|------|

| f <sub>HSI16</sub>                    | Frequency                              | V <sub>DD</sub> = 3.0 V                                                              | -                 | 16       | -                | MHz  |

| TRIM <sup>(1)(2)</sup>                | HSI16 user-                            | Trimming code is not a multiple of 16                                                | -                 | $\pm0.4$ | 0.7              | %    |

| TRIM                                  | trimmed resolution                     | Trimming code is a multiple of 16                                                    | -                 | -        | ± 1.5            | %    |

|                                       |                                        | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C                                     | -1 <sup>(3)</sup> | -        | 1 <sup>(3)</sup> | %    |

|                                       |                                        | $V_{DDA}$ = 3.0 V, $T_A$ = 0 to 55 °C                                                | -1.5              | -        | 1.5              | %    |

| ACC                                   | Accuracy of the                        | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 70 °C                                              | -2                | -        | 2                | %    |

| ACC <sub>HSI16</sub>                  | factory-calibrated<br>HSI16 oscillator | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 85 °C                                              | -2.5              | -        | 2                | %    |

|                                       |                                        | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 105 °C                                             | -4                | -        | 2                | %    |

|                                       |                                        | $V_{DDA} = 1.65 V \text{ to } 3.6 V$<br>$T_A = -40 \text{ to } 125 ^{\circ}\text{C}$ | -5.45             | -        | 3.25             | %    |

| t <sub>SU(HSI16)</sub> <sup>(2)</sup> | HSI16 oscillator<br>startup time       | -                                                                                    | -                 | 3.7      | 6                | μs   |

| I <sub>DD(HSI16)</sub> <sup>(2)</sup> | HSI16 oscillator<br>power consumption  | -                                                                                    | -                 | 100      | 140              | μA   |

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results.

3. Guaranteed by test in production.

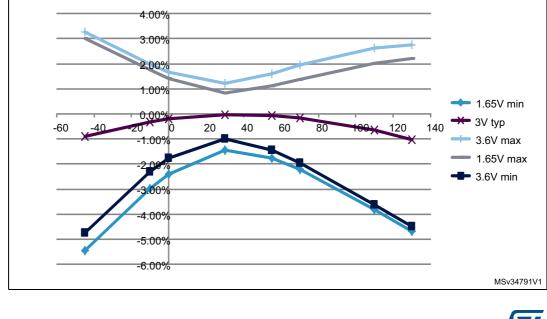

Figure 25. HSI16 minimum and maximum value versus temperature

DocID027100 Rev 3

# 6.3.9 Memory characteristics

# **RAM** memory

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

Table 52. RAM and hardware registers

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

### Flash memory and data EEPROM

| Symbol            | Parameter                                                                      | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |  |  |

|-------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|--|--|

| V <sub>DD</sub>   | Operating voltage<br>Read / Write / Erase                                      | -                                               | 1.65 | -    | 3.6                | V    |  |  |

| t <sub>prog</sub> | Programming time for                                                           | Erasing                                         | -    | 3.28 | 3.94               | me   |  |  |

|                   | word or half-page                                                              | Programming                                     | -    | 3.28 | 3.94               | ms   |  |  |

| I <sub>DD</sub>   | Average current during<br>the whole programming /<br>erase operation           |                                                 | -    | 500  | 700                | μA   |  |  |

|                   | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 1.5  | 2.5                | mA   |  |  |

## Table 53. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

| Table 54. Flash memory | / and data EEPROM endurance an | d retention |

|------------------------|--------------------------------|-------------|

|                        |                                |             |

| Symbol                          | Parameter                                     | Conditions                       | Value              | Unit    |

|---------------------------------|-----------------------------------------------|----------------------------------|--------------------|---------|

| Symbol                          | Falameter                                     | Conditions                       | Min <sup>(1)</sup> | Omt     |

|                                 | Cycling (erase / write)<br>Program memory     | T 40°C to 105 °C                 | 10                 |         |

|                                 | Cycling (erase / write)<br>EEPROM data memory | T <sub>A</sub> = -40°C to 105 °C | 100                | kcycles |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>Program memory     | T 40°C to 125 °C                 | 0.2                | KUYUUUS |

|                                 | Cycling (erase / write)<br>EEPROM data memory | T <sub>A</sub> = -40°C to 125 °C | 2                  |         |

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter                  | Conditions                                            | Monitored<br>frequency band | Max vs.<br>frequency<br>range at<br>32 MHz | Unit |

|------------------|----------------------------|-------------------------------------------------------|-----------------------------|--------------------------------------------|------|

|                  |                            | V                                                     | 0.1 to 30 MHz               | -7                                         |      |

| 6                | Dook lovel                 | $V_{DD} = 3.6 \text{ V},$<br>$T_{A} = 25 \text{ °C},$ | 30 to 130 MHz               | 14                                         | dBµV |

| S <sub>EMI</sub> |                            | LQFP100 package                                       | 130 MHz to 1 GHz            | 9                                          |      |

|                  | compliant with IEC 61967-2 |                                                       | EMI Level                   | 2                                          | -    |

#### Table 56. EMI characteristics

# 6.3.16 DAC electrical specifications

Data guaranteed by design, not tested in production, unless otherwise specified.

| Symbol                              | Parameter                                       | Conditions                                                                 | Min | Тур              | Мах                         | Unit |

|-------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------|-----|------------------|-----------------------------|------|

| V <sub>DDA</sub>                    | Analog supply voltage                           | -                                                                          | 1.8 | -                | 3.6                         | V    |

| V <sub>REF+</sub>                   | Reference supply voltage                        | V <sub>REF+</sub> must always be<br>below V <sub>DDA</sub>                 | 1.8 | -                | 3.6                         | V    |

| V <sub>REF-</sub>                   | Lower reference voltage                         | -                                                                          |     | V <sub>SSA</sub> |                             | V    |

| I <sub>DDVREF+</sub> <sup>(1)</sup> | Current consumption on V <sub>REF+</sub>        | No load, middle code<br>(0x800)                                            | -   | 130              | 220                         | μA   |

| 'DDVREF+`´                          | $V_{\text{REF+}} = 3.3 \text{ V}$               | No load, worst code<br>(0x000)                                             | -   | 220              | 350                         | μΛ   |

| I <sub>DDA</sub> <sup>(2)</sup>     | Current consumption on V <sub>DDA</sub> supply, | No load, middle code<br>(0x800)                                            | -   |                  |                             | μA   |

| 'DDA`´                              | $V_{\text{DDA}} = 3.3 \text{ V}$                | No load, worst code<br>(0xF1C)                                             | -   |                  |                             | μΑ   |

| $R_L^{(3)}$                         | Resistive load                                  | DAC output buffer on                                                       | 5   | -                | -                           | kΩ   |

| C <sub>L</sub> <sup>(3)</sup>       | Capacitive load                                 |                                                                            | -   | -                | 50                          | pF   |

| R <sub>O</sub>                      | Output impedance                                | DAC output buffer off                                                      | 12  | 16               | 20                          | kΩ   |

|                                     |                                                 | DAC output buffer ON                                                       | 0.2 | -                | V <sub>DDA</sub> – 0.2      | v    |

| V <sub>DAC_OUT</sub>                | Voltage on DAC_OUT output                       | DAC output buffer OFF                                                      | 0.5 | -                | V <sub>REF+</sub> –<br>1LSB | mV   |

| DNL <sup>(2)</sup>                  | Differential non linearity <sup>(4)</sup>       | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer on | -   | 1.5              | 3                           |      |

|                                     |                                                 | No $R_{LOAD}$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer off           | -   | 1.5              | 3                           |      |

| INL <sup>(2)</sup>                  | Integral non linearity <sup>(5)</sup>           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer on | -   | 2                | 4                           |      |

|                                     |                                                 | No $R_{LOAD}$ , $C_L \le 50 \text{ pF}$ DAC output buffer off              | -   | 2                | 4                           | LSB  |

| Offset <sup>(2)</sup>               | Offset error at code 0x800 <sup>(6)</sup>       | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer on | -   | ±10              | ±25                         |      |

|                                     |                                                 | No $R_{LOAD}$ , $C_L \le 50 \text{ pF}$ DAC output buffer off              | -   | ±5               | ±8                          |      |

| Offset1 <sup>(2)</sup>              | Offset error at code 0x001 <sup>(7)</sup>       | No $R_{LOAD}$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer off           | -   | ±1.5             | ±5                          |      |

| Tahlo | 67          | DAC | characteristics |

|-------|-------------|-----|-----------------|

| Table | <b>0</b> 7. | DAC | characteristics |

- 6. Difference between the value measured at Code (0x800) and the ideal value =  $V_{REF+}/2$ .

- 7. Difference between the value measured at Code (0x001) and the ideal value.

- 8. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is off, and from code giving 0.2 V and ( $V_{DDA} 0.2$ ) V when buffer is on.

- 9. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

#### Figure 34. 12-bit buffered/non-buffered DAC

## 6.3.17 Temperature sensor characteristics

#### Table 68. Temperature sensor calibration values

| Calibration value name | Description                                                               | Memory address            |  |

|------------------------|---------------------------------------------------------------------------|---------------------------|--|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V  | 0x1FF8 007A - 0x1FF8 007B |  |

| TS_CAL2                | TS ADC raw data acquired at temperature of 130 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |  |

#### Table 69. Temperature sensor characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Max  | Unit  |

|---------------------------------------|------------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | ±2   | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 1.48 | 1.61 | 1.75 | mV/°C |

| V <sub>130</sub>                      | Voltage at 130°C ±5°C <sup>(2)</sup>           | 640  | 670  | 700  | mV    |

| I <sub>DDA(TEMP)</sub> <sup>(3)</sup> | Current consumption                            | -    | 3.4  | 6    | μA    |

| t <sub>START</sub> <sup>(3)</sup>     | Startup time                                   |      | -    | 10   |       |

| T <sub>S_temp</sub> <sup>(4)(3)</sup> | ADC sampling time when reading the temperature | 10   | -    | -    | μs    |

1. Guaranteed by characterization results.

2. Measured at  $V_{DD}$  = 3 V ±10 mV. V130 ADC conversion result is stored in the TS\_CAL2 byte.

- 3. Guaranteed by design.

- 4. Shortest sampling time can be determined in the application by multiple iterations.

# 6.3.18 Comparators

| Symbol                   | Parameter                                                      | Conditions                                                                                        | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |

|--------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|

| $V_{DDA}$                | Analog supply voltage                                          | -                                                                                                 | 1.65               |     | 3.6                | V         |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                        | -                                                                                                 | -                  | 400 | -                  | - kΩ      |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                         | -                                                                                                 | -                  | 10  | -                  | K22       |

| V <sub>IN</sub>          | Comparator 1 input voltage range                               | -                                                                                                 | 0.6                | -   | V <sub>DDA</sub>   | V         |

| t <sub>START</sub>       | Comparator startup time                                        | -                                                                                                 | -                  | 7   | 10                 |           |

| td                       | Propagation delay <sup>(2)</sup>                               | -                                                                                                 | -                  | 3   | 10                 | μs        |

| Voffset                  | Comparator offset                                              | -                                                                                                 | -                  | ±3  | ±10                | mV        |

| d <sub>Voffset</sub> /dt | Comparator offset variation in worst voltage stress conditions | $V_{DDA} = 3.6 \text{ V}, V_{IN+} = 0 \text{ V}, V_{IN-} = V_{REFINT}, T_A = 25 ^{\circ}\text{C}$ | 0                  | 1.5 | 10                 | mV/1000 h |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                             | -                                                                                                 | -                  | 160 | 260                | nA        |

1. Guaranteed by characterization.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

| Symbol              | Parameter Conditions                                                                                                                                                   |                                  | Min  | Тур | Max <sup>(1)</sup> | Unit       |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------|-----|--------------------|------------|

| V <sub>DDA</sub>    | Analog supply voltage                                                                                                                                                  | -                                | 1.65 | -   | 3.6                | V          |

| V <sub>IN</sub>     | Comparator 2 input voltage range                                                                                                                                       | -                                | 0    | -   | V <sub>DDA</sub>   | V          |

| +                   | Comparator startup time                                                                                                                                                | Fast mode                        | -    | 15  | 20                 |            |

| t <sub>START</sub>  |                                                                                                                                                                        | Slow mode                        | -    | 20  | 25                 |            |

| +                   | Propagation delay <sup>(2)</sup> in slow mode                                                                                                                          | $1.65~V \leq V_{DDA} \leq 2.7~V$ | -    | 1.8 | 3.5                |            |

| t <sub>d slow</sub> | Fropagation delay V in slow mode                                                                                                                                       | $2.7~V \leq V_{DDA} \leq 3.6~V$  | -    | 2.5 | 6                  | μs         |

| 4                   | Propagation delay <sup>(2)</sup> in fast mode                                                                                                                          | $1.65~V \leq V_{DDA} \leq 2.7~V$ | -    | 0.8 | 2                  |            |

| t <sub>d fast</sub> | Propagation delay. In fast mode                                                                                                                                        | $2.7~V \leq V_{DDA} \leq 3.6~V$  | -    | 1.2 | 4                  |            |

| V <sub>offset</sub> | Comparator offset error                                                                                                                                                |                                  | -    | ±4  | ±20                | mV         |

| dThreshold/<br>dt   | Threshold voltage temperature coefficient $V_{DDA} = 3.3V, T_{A} = 0 \text{ tr}$ $V_{-} = V_{REFINT}, 3/4 V_{REFINT}, 1/2 V_{REFINT}, 1/2 V_{REFINT}, 1/4 V_{REFINT}.$ |                                  | -    | 15  | 30                 | ppm<br>/°C |

| L                   | Current consumption <sup>(3)</sup>                                                                                                                                     | Fast mode                        | -    | 3.5 | 5                  |            |

| ICOMP2              |                                                                                                                                                                        | Slow mode                        | -    | 0.5 | 2                  | μA         |

### Table 71. Comparator 2 characteristics

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage (required for comparator operation) is not included.

# Table 88. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ballgrid array package mechanical data (continued)

| Symbol | millimeters |       |       |     | inches <sup>(1)</sup> |        |

|--------|-------------|-------|-------|-----|-----------------------|--------|

| Symbol | Min         | Тур   | Мах   | Min | Тур                   | Мах    |

| е      | -           | 0.500 | -     | -   | 0.0197                | -      |

| F      | -           | 0.750 | -     | -   | 0.0295                | -      |

| ddd    | -           | -     | 0.080 | -   | -                     | 0.0031 |

| eee    | -           | -     | 0.150 | -   | -                     | 0.0059 |

| fff    | -           | -     | 0.050 | -   | -                     | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

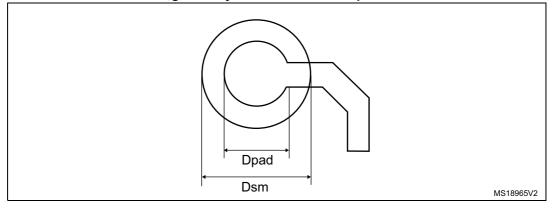

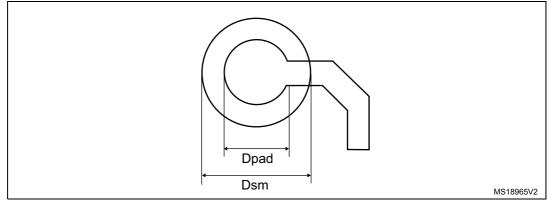

# Figure 52. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball ,grid array recommended footprint

#### Table 89. TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension    | Recommended values                                              |

|--------------|-----------------------------------------------------------------|

| Pitch        | 0.5                                                             |

| Dpad         | 0.27 mm                                                         |

| Dsm          | 0.35 mm typ. (depends on the soldermask registration tolerance) |

| Solder paste | 0.27 mm aperture diameter.                                      |