# E·XFL

Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Product Status          | Active                                                                    |

|-------------------------|---------------------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                                 |

| Core Processor          | ARM® Cortex®-M3                                                           |

| Flash Size              | 512KB                                                                     |

| RAM Size                | 64KB                                                                      |

| Peripherals             | DDR, PCIe, SERDES                                                         |

| Connectivity            | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB                  |

| Speed                   | 166MHz                                                                    |

| Primary Attributes      | FPGA - 90K Logic Modules                                                  |

| Operating Temperature   | -55°C ~ 125°C (TJ)                                                        |

| Package / Case          | 484-BGA                                                                   |

| Supplier Device Package | 484-FPBGA (23x23)                                                         |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/m2s090t-1fg484m |

|                         |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5. Power Consumption

# 5.1 Quiescent Supply Current

### Table 8 • Quiescent Supply Current Characteristics

|                                                                              | Modes and Configurations |                   |       |  |  |

|------------------------------------------------------------------------------|--------------------------|-------------------|-------|--|--|

| Power Supplies/Blocks                                                        | Non-Flash*Freeze Mode    | Flash*Freeze Mode | Notes |  |  |

| FPGA Core                                                                    | On                       | Off               | -     |  |  |

| VDD / SERDES_[01]_VDD                                                        | On                       | On                | 1     |  |  |

| VPP / VPPNVM                                                                 | On                       | On                | -     |  |  |

| MDDR_PLL_VDDA<br>CCC_XX[01]_PLL_VDDA<br>PLL0_PLL1_MDDR_VDDA<br>FDDR_PLL_VDDA | 0 V                      | 0 V               | _     |  |  |

| SERDES_[01]_PLL_VDDA                                                         | 0 V                      | 0 V               | 3     |  |  |

| SERDES_[01]_L[0123]_VDDAPLL / VDD_2V5                                        | On                       | On                | 3     |  |  |

| SERDES_[01]_L[0123]_VDDAIIO                                                  | On                       | On                | 3     |  |  |

| VDDIx                                                                        | On                       | On                | 2, 4  |  |  |

| VREFx                                                                        | On                       | On                | -     |  |  |

| MSSDDR CLK                                                                   | 32 kHz                   | 32 kHz            | -     |  |  |

| RAM                                                                          | On                       | Sleep state       | -     |  |  |

| HPMS Controller                                                              | 50 MHz                   | 50 MHz            | -     |  |  |

| 50 MHz Oscillator (enable/disable)                                           | Enabled                  | Disabled          | -     |  |  |

| 1 MHz Oscillator (enable/disable)                                            | Disabled                 | Disabled          | -     |  |  |

| Crystal Oscillator (enable/disable)                                          | Disabled                 | Disabled          | _     |  |  |

Notes:

1. SERDES\_[01]\_VDD Power Supply is shorted to VDD.

2. VDDIx has been set to ON for test conditions as described. Banks on the east side should always be powered with the appropriate VDDI Bank supplies. For details on bank power supplies, refer to the "Recommendation for Unused Bank Supplies" table in the AC393: SmartFusion2 and IGLOO2 Board Design Guidelines Application Note.

3. SERDES and DDR blocks to be unused.

4. No Differential (that is to say, LVDS) I/O's or ODT attributes to be used.

|           |              |                                      | 010       | 025       | 050       | 090       | 150       |       |

|-----------|--------------|--------------------------------------|-----------|-----------|-----------|-----------|-----------|-------|

| Parameter | Modes        | Conditions                           | VDD=1.2 V | Units |

| IDC1      | Non-         | Typical<br>(T <sub>J</sub> = 25°C)   | 6.9       | 8.9       | 13.1      | 15.4      | 27.5      | mA    |

|           |              | Military<br>(T <sub>J</sub> = 125°C) | 73.0      | 106.4     | 180.9     | 217.5     | 390.5     | mA    |

| IDC2      | Flash*Freeze | Typical<br>(T <sub>J</sub> = 25°C)   | 2.6       | 3.7       | 5.1       | 5.1       | 8.9       | mA    |

|           |              | Military<br>(T <sub>J</sub> = 125°C) | 55.6      | 74.2      | 98.5      | 99.5      | 161.0     | mA    |

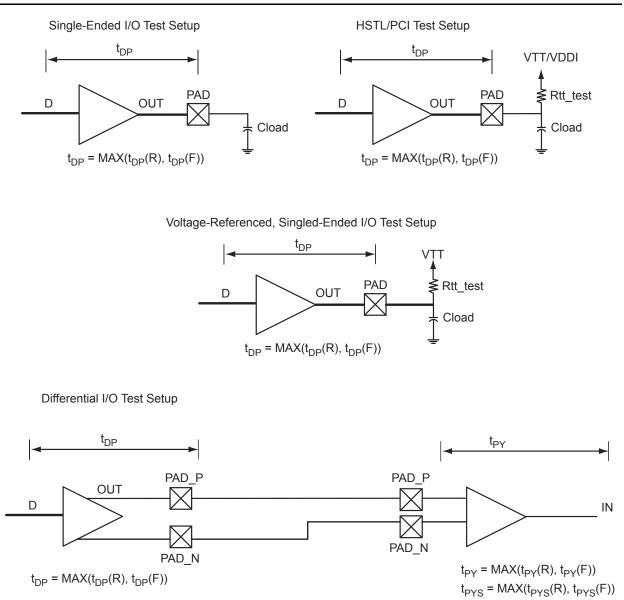

# 8.2. Output Buffer and AC Loading

Figure 3 • Output Buffer AC Loading

# 8.5 Detailed I/O Characteristics

#### Table 18 • Input Capacitance

| Symbol | Definition        | Min | Мах | Units |

|--------|-------------------|-----|-----|-------|

| CIN    | Input Capacitance | -   | 10  | pF    |

Table 19 •

I/O Weak Pull-Up/Pull-Down Resistance Values for DDRIO, MSIO, and MSIOD Banks

Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values at VOH/VOL Level

| VDDI Domain | DDRIO I/O Bank                               |       | ĸ      | MSIO I/O Bank          |       |                     | MSIOD I/O Bank |                        |                                  |       |      |                          |       |

|-------------|----------------------------------------------|-------|--------|------------------------|-------|---------------------|----------------|------------------------|----------------------------------|-------|------|--------------------------|-------|

|             | R <sub>(WEAK</sub><br>PULL-UP)<br>at VOH (Ω) |       | PULL-I | eak<br>Down)<br>DL (Ω) | -     | EAK<br>UP)<br>Η (Ω) | PULL-          | ΈΑΚ<br>DOWN)<br>DL (Ω) | R <sub>(W</sub><br>PULI<br>at VO | UP)   | PULL | veak<br>·Down)<br>DL (Ω) |       |

|             | Min                                          | Max   | Min    | Max                    | Min   | Max                 | Min            | Max                    | Min                              | Max   | Min  | Max                      | Notes |

| 3.3 V       | N/A                                          | N/A   | N/A    | N/A                    | 9.9K  | 14.5K               | 9.98K          | 14.9K                  | N/A                              | N/A   | N/A  | N/A                      |       |

| 2.5 V       | 10K                                          | 15.1K | 9.98K  | 15.3K                  | 10K   | 15K                 | 10.1K          | 15.6K                  | 9.6K                             | 14.1K | 9.5K | 13.9K                    | 1,2   |

| 1.8 V       | 10.3K                                        | 16.2K | 10.3K  | 16.6K                  | 10.4K | 16.2K               | 10.4K          | 17.3K                  | 9.7K                             | 14.7K | 9.7K | 14.5K                    | 1,2   |

| 1.5 V       | 10.6K                                        | 17.2K | 10.6K  | 17.9K                  | 10.7K | 17.3K               | 10.8K          | 18.9K                  | 9.9K                             | 15.3K | 9.8K | 15K                      | 1,2   |

| 1.2 V       | 11.1K                                        | 19.3K | 11.2K  | 20.9K                  | 11.3K | 19.7K               | 11.5K          | 22.7K                  | 10.3K                            | 16.7K | 10K  | 16.2K                    | 1,2   |

| Notes:      | -                                            |       |        |                        |       | -                   | -              |                        |                                  |       |      |                          | -     |

1. R(WEAK PULL-DOWN) = (VOLspec)/I(WEAK PULL-DOWN MAX)

2. R(WEAK PULL-UP) = (VDDImax - VOHspec)/I(WEAK PULL-UP MIN)

#### Table 20 • Schmitt Trigger Input Hysteresis

Hysteresis Voltage Value for Schmitt Trigger Mode Input Buffers

| Input Buffer Configuration         | Hysteresis Value (Typical, unless otherwise noted) |

|------------------------------------|----------------------------------------------------|

| 3.3 V LVTTL / LVCMOS / PCI / PCI-X | 0.05 × VDDI (Worst-case)                           |

| 2.5 V LVCMOS                       | 0.05 × VDDI (Worst-case)                           |

| 1.8 V LVCMOS                       | 0.1 × VDDI (Worst-case)                            |

| 1.5 V LVCMOS                       | 60 mV                                              |

| 1.2 V LVCMOS                       | 20 mV                                              |

## 8.6 Single-Ended I/O Standards

## 8.6.1 Low Voltage Complementary Metal Oxide Semiconductor (LVCMOS)

LVCMOS is a widely used switching standard implemented in CMOS transistors. This standard is defined by JEDEC (JESD 8-5). The LVCMOS standards supported in IGLOO2 FPGAs and SmartFusion2 SoC FPGAs are: LVCMOS12, LVCMOS15, LVCMOS18, LVCMOS25, and LVCMOS33.

| Table 63 • DDR1/SSTL2 AC Switching Characteristics for Transmitter (Output and Tristate Buffers) |

|--------------------------------------------------------------------------------------------------|

| Worst-Case Military Conditions: T <sub>J</sub> = 125°C, VDD = 1.14 V, VDDI= 2.375 V (continued)  |

|               |                 | Speed Grade<br>-1 |                 |                 |                 |       |  |  |

|---------------|-----------------|-------------------|-----------------|-----------------|-----------------|-------|--|--|

|               | t <sub>DP</sub> | t <sub>ZL</sub>   | t <sub>ZH</sub> | t <sub>HZ</sub> | t <sub>LZ</sub> | Units |  |  |

| MSIO I/O Bank |                 |                   |                 |                 |                 |       |  |  |

| Single Ended  | 2.563           | 2.208             | 2.19            | 2.205           | 2.187           | ns    |  |  |

| Differential  | 2.703           | 2.566             | 2.555           | 2.363           | 2.353           | ns    |  |  |

## 8.7.4 Stub-Series Terminated Logic 1.8 V (SSTL18)

SSTL18 Class I and Class II are supported in IGLOO2 and SmartFusion2 SoC FPGAs, and also comply with the reduced and full drive double date rate (DDR2) standard. IGLOO2 and SmartFusion2 SoC FPGA I/Os support both standards for single-ended signaling and differential signaling for SSTL18. This standard requires a differential amplifier input buffer and a push-pull output buffer.

### 8.7.4.1 Minimum and Maximum Input and Output Levels Specification

| Symbols    | Parameters Conditions                                 | Min          | Тур   | Max          | Units | Notes |

|------------|-------------------------------------------------------|--------------|-------|--------------|-------|-------|

| Recommend  | ded DC Operating Conditions                           |              |       |              |       |       |

| VDDI       | Supply voltage                                        | 1.71         | 1.8   | 1.89         | V     | _     |

| VTT        | Termination voltage                                   | 0.838        | 0.900 | 0.964        | V     | -     |

| VREF       | Input reference voltage                               | 0.838        | 0.900 | 0.964        | V     | _     |

| SSTL18 DC  | Input Voltage Specification                           |              |       | •            |       | -     |

| VIH (DC)   | DC input logic High                                   | VREF + 0.125 | _     | 1.89         | V     | —     |

| VIL (DC)   | DC input logic Low                                    | -0.3         | _     | VREF – 0.125 | V     | _     |

| IIH (DC)   | Input current High                                    | -            | _     | 10           | μA    | -     |

| IIL (DC)   | Input current Low                                     | -            | _     | 10           | μA    | _     |

| SSTL18 DC  | Output Voltage Specification                          |              |       | •            |       | -     |

| SSTL18     | Class I (DDR2 Reduced Drive)                          |              |       |              |       |       |

| VOH        | DC output logic High                                  | VTT + 0.603  | _     | -            | V     | —     |

| VOL        | DC output logic Low                                   | -            | _     | VTT- 0.603   | V     | _     |

| IOH at VOH | Output minimum source DC current (DDRIC<br>Bank only) | 0 I/O 6.0    | -     | -            | mA    | _     |

| IOL at VOL | Output minimum sink current (DDRIO I/O E only)        | Bank –6.0    | _     | -            | mA    | _     |

| SSTL18     | Class II (DDR2 Full Drive)                            | ł            |       |              |       | *     |

| VOH        | DC output logic High                                  | VTT + 0.603  | -     | -            | V     | _     |

| VOL        | DC output logic Low                                   | -            | -     | VTT- 0.603   | V     | _     |

| IOH at VOH | Output minimum source DC current (DDRIC Bank only)    | D I/O 12.0   | _     | _            | mA    | _     |

#### AC Switching Characteristics for Transmitter (Output and Tristate Buffers

| Table 82 • | LPDDR - LVCMOS 1.8 V AC Switching Characteristics for Transmitter DDRIO I/O Bank (Output and |

|------------|----------------------------------------------------------------------------------------------|

|            | Tristate Buffers)                                                                            |

| Output Drive |              |                 |                 | Speed Grade<br>–1 | )               |                 |       |

|--------------|--------------|-----------------|-----------------|-------------------|-----------------|-----------------|-------|

| Selection    | Slew Control | t <sub>DP</sub> | t <sub>ZL</sub> | t <sub>zH</sub>   | t <sub>HZ</sub> | t <sub>LZ</sub> | Units |

|              | slow         | 4.681           | 4.017           | 4.69              | 5.388           | 4.852           | ns    |

| 2 mA         | medium       | 4.211           | 3.599           | 4.219             | 5.058           | 4.488           | ns    |

|              | medium_fast  | 3.978           | 3.392           | 3.986             | 4.874           | 4.327           | ns    |

|              | fast         | 3.953           | 3.373           | 3.961             | 4.858           | 4.316           | ns    |

|              | slow         | 4.355           | 3.657           | 4.346             | 5.967           | 5.399           | ns    |

| 4 ~ 4        | medium       | 3.886           | 3.246           | 3.879             | 5.628           | 5.01            | ns    |

| 4 mA         | medium_fast  | 3.656           | 3.05            | 3.647             | 5.461           | 4.845           | ns    |

|              | fast         | 3.635           | 3.033           | 3.626             | 5.447           | 4.838           | ns    |

|              | slow         | 4.105           | 3.422           | 4.092             | 6.221           | 5.599           | ns    |

| 6 4          | medium       | 3.68            | 3.05            | 3.668             | 5.9             | .9 5.257        | ns    |

| 6 mA         | medium_fast  | 3.477           | 2.867           | 3.463             | 5.739           | 5.118           | ns    |

|              | fast         | 3.451           | 2.849           | 3.437             | 5.72            | 5.104           | ns    |

|              | slow         | 4.015           | 3.32            | 3.998             | 6.458           | 5.808           | ns    |

| 8 mA         | medium       | 3.59            | 2.947           | 3.574             | 6.129           | 5.449           | ns    |

| oma          | medium_fast  | 3.383           | 2.761           | 3.366             | 5.963           | 5.304           | ns    |

|              | fast         | 3.357           | 2.746           | 3.34              | 5.954           | 5.289           | ns    |

|              | slow         | 3.888           | 3.18            | 3.864             | 6.739           | 6.045           | ns    |

| 10 mA        | medium       | 3.485           | 2.822           | 3.467             | 6.422           | 5.7             | ns    |

| 10 IIIA      | medium_fast  | 3.281           | 2.642           | 3.26              | 6.277           | 5.553           | ns    |

|              | fast         | 3.258           | 2.627           | 3.238             | 6.27            | 5.546           | ns    |

|              | slow         | 3.795           | 3.096           | 3.773             | 6.773           | 6.067           | ns    |

| 12 mA        | medium       | 3.408           | 2.764           | 3.389             | 6.47            | 5.743           | ns    |

| 12 MA        | medium_fast  | 3.215           | 2.599           | 3.194             | 6.346           | 5.61            | ns    |

|              | fast         | 3.196           | 2.584           | 3.175             | 6.335           | 5.604           | ns    |

|              | slow         | 3.744           | 3.035           | 3.719             | 6.944           | 6.207           | ns    |

| 16 mA        | medium       | 3.358           | 2.712           | 3.339             | 6.657           | 5.868           | ns    |

|              | medium_fast  | 3.175           | 2.546           | 3.153             | 6.547           | 5.751           | ns    |

|              | fast         | 3.156           | 2.531           | 3.133             | 6.541           | 5.747           | ns    |

Worst-Case Military Conditions:  $T_J = 125^{\circ}C$ , VDD = 1.14 V, VDDI = 1.71 V

## 8.8. Differential I/O Standards

Configuration of the I/O modules as a differential pair is handled by Microsemi SoC Products Group Libero<sup>®</sup> Systemon-Chip (SoC) software when the user instantiates a differential I/O macro in the design. Differential I/Os can also be used in conjunction with the embedded Input register (InReg), Output register (OutReg), Enable register (EnReg), and Double Data Rate registers (DDR).

## 8.8.1 LVDS

Low-Voltage Differential Signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard.

#### 8.8.1.1 Minimum and Maximum Input and Output Levels

| Symbols    | Parameters                        | Conditions  | Min   | Тур   | Max   | Units    |

|------------|-----------------------------------|-------------|-------|-------|-------|----------|

| LVDS Rec   | ommended DC Operating Condi       | tions       |       |       |       | <u>e</u> |

| VDDI       | Supply voltage                    | 2.5 V range | 2.375 | 2.5   | 2.625 | V        |

| VDDI       | Supply voltage                    | 3.3 V range | 3.15  | 3.3   | 3.45  | V        |

| LVDS DC    | Input Voltage Specification       |             | •     | 1     | 1     |          |

| VI         | DC Input voltage                  | 2.5 V range | 0     | _     | 2.925 | V        |

| VI         | DC input voltage                  | 3.3 V range | 0     | -     | 3.45  | V        |

| IIH (DC)   | Input current High                |             |       | -     | 10    | μA       |

| IIL (DC)   | Input current Low                 |             | -     | _     | 10    | μA       |

| LVDS DC    | Output Voltage Specification      |             |       |       |       |          |

| VOH        | DC output logic High              |             | 1.25  | 1.425 | 1.6   | V        |

| VOL        | DC output logic Low               |             | 0.9   | 1.075 | 1.25  | V        |

| LVDS Diffe | erential Voltage Specification    |             |       |       |       |          |

| VOD        | Differential output voltage swing |             | 250   | 350   | 450   | mV       |

| VOCM       | Output common mode voltage        |             | 1.125 | 1.25  | 1.375 | V        |

| VICM       | Input common mode voltage         |             | 0.05  | 1.25  | 2.35  | V        |

| VID        | Input differential voltage        |             | 100   | 350   | 600   | mV       |

#### Table 83 • LVDS DC Voltage Specification

#### Table 84 • LVDS AC Specifications

| Symbols  | Parameters                                                               | Conditions                                              |   | Тур         | Max | Units |

|----------|--------------------------------------------------------------------------|---------------------------------------------------------|---|-------------|-----|-------|

| LVDS Max | imum AC Switching Speed                                                  |                                                         |   |             |     |       |

| Dmax     | Maximum data rate<br>(for MSIO I/O Bank)                                 | AC loading: 12 pF / 100 $\Omega$ differential load      | _ | -           | 480 | Mbps  |

| Dmax     | Maximum data rate<br>(for MSIOD I/O Bank)                                | AC loading: 10 pF / 100 $\Omega$ differential load      | _ | -           | 480 | Mbps  |

| LVDS Imp | edance Specification                                                     | •                                                       |   |             |     |       |

| Rt       | Termination resistance                                                   | _                                                       | - | 100         | -   | Ω     |

| LVDS AC  | Test Parameters Specifications                                           | •                                                       |   |             |     |       |

| Vtrip    | Measuring/trip point for data path                                       |                                                         | - | Cross point | -   | V     |

| Rent     | Resistance for enable path ( $t_{ZH}$ , $t_{ZL}$ , $t_{HZ}$ , $t_{LZ}$ ) |                                                         |   | 2k          | -   | Ω     |

| Cent     | Capacitive loading for enable path $(t_{ZH})$                            | , t <sub>ZL</sub> , t <sub>HZ</sub> , t <sub>LZ</sub> ) | - | 5           | -   | pF    |

#### 8.8.2.2. AC Switching Characteristics

#### AC Switching Characteristics for Receiver (Input Buffers)

# Table 91 • B-LVDS AC Switching Characteristics for Receiver (Input Buffers)Worst-Case Military Conditions: TJ = 125°C, VDD = 1.14 V, VDDI = 2.375 V

|                               |                          | Speed Grade<br>–1 |       |

|-------------------------------|--------------------------|-------------------|-------|

|                               | On-Die Termination (ODT) | t <sub>PY</sub>   | Units |

|                               | None                     | 3.011             | ns    |

| Bus-LVDS (for MSIO I/O Bank)  | 100                      | 3.006             | ns    |

|                               | None                     | 2.722             | ns    |

| Bus-LVDS (for MSIOD I/O Bank) | 100                      | 2.725             | ns    |

AC Switching Characteristics for Transmitter (Output and Tristate Buffers)

# Table 92 • B-LVDS AC Switching Characteristics for Transmitter (Output and Tristate Buffers)Worst-Case Military Conditions: TJ = 125°C, VDD = 1.14 V, VDDI = 2.375 V

|                              |                 | Speed Grade<br>–1 |                 |                 |                 |       |

|------------------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-------|

|                              | t <sub>DP</sub> | t <sub>ZL</sub>   | t <sub>ZH</sub> | t <sub>HZ</sub> | t <sub>LZ</sub> | Units |

| Bus-LVDS (for MSIO I/O Bank) | 2.78            | 2.632             | 2.617           | 2.448           | 2.436           | ns    |

### 8.8.3 M-LVDS

M-LVDS specifications extend the existing LVDS standard to high-performance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers.

### 8.8.3.1 Minimum and Maximum Input and Output Levels

| Symbols   | Parameters                       | Conditions                 | Min   | Тур   | Max   | Units | Notes |

|-----------|----------------------------------|----------------------------|-------|-------|-------|-------|-------|

| M-LVDS Re | ecommended DC Operating Co       | onditions                  |       |       |       |       | -     |

| VDDI      | Supply voltage                   |                            | 2.375 | 2.5   | 2.625 | V     | *     |

| M-LVDS D  | C Input Voltage Specification    |                            |       | -     | -     |       | -     |

| VI        | DC input voltage                 |                            | 0     | -     | 2.925 | V     | -     |

| IIH (DC)  | Input current High               |                            | _     | -     | 10    | μA    | _     |

| IIL (DC)  | Input current Low                |                            | -     | -     | 10    | μA    | -     |

| M-LVDS D  | C Output Voltage Specification   | (for MSIO I/O Bank Only)   |       | -     | -     |       | _     |

| VOH       | DC output logic High             |                            | 1.25  | 1.425 | 1.6   | V     | _     |

| VOL       | DC output logic Low              |                            | 0.9   | 1.075 | 1.25  | V     | -     |

| M-LVDS Di | fferential Voltage Specification | 1                          |       | -     | -     |       | _     |

| VOD       | Differential output voltage Swin | g (for MSIO I/O Bank only) | 300   | -     | 650   | mV    | _     |

| VOCM      | Output common mode voltage       | (for MSIO I/O Bank only)   | 0.3   | -     | 2.1   | V     | -     |

| VICM      | Input common mode voltage        |                            | 0.3   | -     | 1.2   | V     | -     |

licrosemi

| Table 106 • LVPECL Maximum AC Switching Speeds (Applicable to MSIO I/O Banks Only) | ) |

|------------------------------------------------------------------------------------|---|

|------------------------------------------------------------------------------------|---|

| Symbols                  | Parameters                        | Conditions | Min | Тур | Max | Units |  |

|--------------------------|-----------------------------------|------------|-----|-----|-----|-------|--|

| LVPECL AC Specifications |                                   |            |     |     |     |       |  |

| Fmax                     | Maximum data rate (for MSIO I/O E | Bank)      | _   | _   | 810 | Mbps  |  |

### 8.8.6.2 AC Switching Characteristics

AC Switching Characteristics for Receiver (Input Buffers)

# *Table 107* • LVPECL Receiver Characteristics Worst-case Military conditions: T<sub>J</sub> = 125°C, VDD = 1.14 V, VDDI = 3.15 V

|                            |                          | t <sub>PY</sub>   |       |

|----------------------------|--------------------------|-------------------|-------|

|                            | On-Die Termination (ODT) | Speed Grade<br>–1 | Units |

|                            | None                     | 2.71              | ns    |

| LVPECL (for MSIO I/O Bank) | 100                      | 2.71              | ns    |

## 8.9 I/O Register Specifications

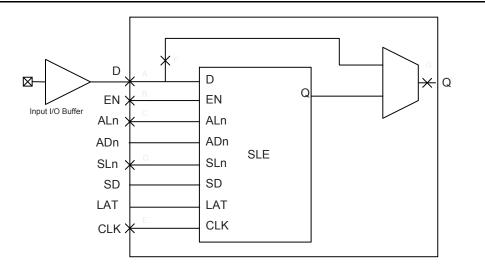

## 8.9.1 Input Register

Figure 5 • Timing Model for Input Register

| Parameter            | Description                                                  | Measuring<br>Nodes<br>(from, to)* | Speed<br>Grade<br>–1 | Units |

|----------------------|--------------------------------------------------------------|-----------------------------------|----------------------|-------|

| t <sub>IREMALn</sub> | Asynchronous Load Removal Time for the Input Register        | C,E                               | 0                    | ns    |

| t <sub>IRECALn</sub> | Asynchronous Load Recovery Time for the Input Register       | C,E                               | 0.076                | ns    |

| t <sub>IWALn</sub>   | Asynchronous Load Minimum Pulse Width for the Input Register | C,C                               | 0.313                | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width High for the Input Register        | E,E                               | 0.078                | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width Low for the Input Register         | E,E                               | 0.164                | ns    |

#### *Table 108* • Input Data Register Propagation Delays (continued) Worst-Case Military Conditions: T<sub>J</sub> = 125°C, VDD = 1.14 V

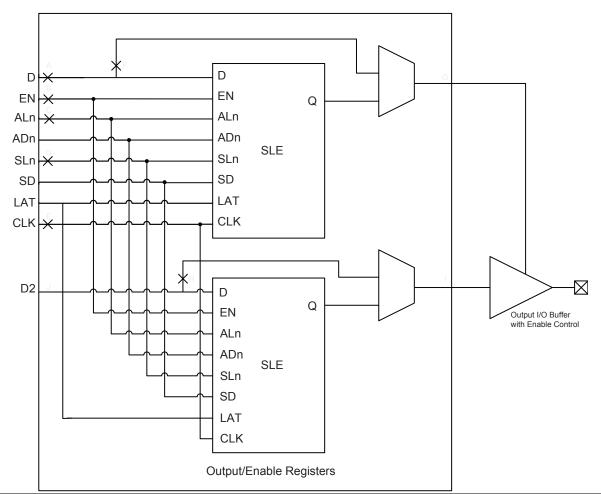

## 8.9.2 Output/Enable Register

Figure 7 • Timing Model for Output/Enable Register

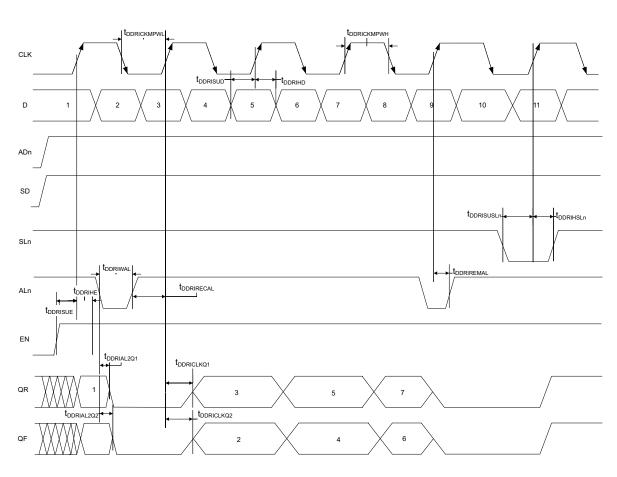

## 8.10.2 Input DDR Timing Diagram

Figure 10 • Input DDR Timing Diagram

# 8.10.3 Timing Characteristics

# *Table 110* • Input DDR Propagation Delays Worst-Case Military Conditions: T<sub>J</sub> = 125°C, VDD=1.14 V

| Parameter   | Description                                         | Measuring Nodes<br>(from, to) | Speed Grade<br>-1 | Units |

|-------------|-----------------------------------------------------|-------------------------------|-------------------|-------|

| tDDRICLKQ1  | Clock-to-Out Out_QR for Input DDR                   | B,C                           | 0.165             | ns    |

| tDDRICLKQ2  | Clock-to-Out Out_QF for Input DDR                   | B,D                           | 0.172             | ns    |

| tDDRISUD    | Data Setup for Input DDR                            | A,B                           | 0.372             | ns    |

| tDDRIHD     | Data Hold for Input DDR                             | A,B                           | 0                 | ns    |

| tDDRISUE    | Enable Setup for Input DDR                          | E,B                           | 0.475             | ns    |

| tDDRIHE     | Enable Hold for Input DDR                           | E,B                           | 0                 | ns    |

| tDDRISUSLn  | Synchronous Load Setup for Input DDR                | G,B                           | 0.475             | ns    |

| tDDRIHSLn   | Synchronous Load Hold for Input DDR                 | G,B                           | 0                 | ns    |

| tDDRIAL2Q1  | Asynchronous Load-to-Out QR for Input DDR           | F,C                           | 0.606             | ns    |

| tDDRIAL2Q2  | Asynchronous Load-to-Out QF for Input DDR           | F,D                           | 0.558             | ns    |

| tDDRIREMAL  | Asynchronous Load Removal time for Input<br>DDR     | F,B                           | 0                 | ns    |

| tDDRIRECAL  | Asynchronous Load Recovery time for Input DDR       | F,B                           | 0.076             | ns    |

| tDDRIWAL    | Asynchronous Load Minimum Pulse Width for Input DDR | F,F                           | 0.313             | ns    |

| tDDRICKMPWH | Clock Minimum Pulse Width High for Input DDR        | B,B                           | 0.078             | ns    |

| tDDRICKMPWL | Clock Minimum Pulse Width Low for Input DDR         | B,B                           | 0.164             | ns    |

|            |                                                                           | Speed  |       |       |

|------------|---------------------------------------------------------------------------|--------|-------|-------|

| Parameter  | Description                                                               | Min    | Мах   | Units |

| tplclkmpwl | Pipelined Clock Minimum pulse Width Low                                   | 1.5    | -     | ns    |

|            | Read Access Time with Pipeline Register                                   | _      | 0.332 | ns    |

| tclk2q     | Read Access Time without Pipeline Register                                | _      | 2.342 | ns    |

|            | Access Time with Feed-Through Write Timing                                | _      | 1.559 | ns    |

| taddrsu    | Address Setup Time                                                        | 0.646  | -     | ns    |

| taddrhd    | Address Hold Time                                                         | 0.282  | -     | ns    |

| tdsu       | Data Setup Time                                                           | 0.332  | -     | ns    |

| tdhd       | Data Hold Time                                                            | 0.084  | -     | ns    |

| tblksu     | Block Select Setup Time                                                   | 0.214  | -     | ns    |

| tblkhd     | Block Select Hold Time                                                    | 0.223  | -     | ns    |

| tblk2q     | Block Select to Out Disable Time (when Pipe-Lined Registered is Disabled) | _      | 1.559 | ns    |

| tblkmpw    | Block Select Minimum Pulse Width                                          | 0.218  | -     | ns    |

| trdesu     | Read Enable Setup Time                                                    | 0.547  | -     | ns    |

| trdehd     | Read Enable Hold Time                                                     | 0.073  | -     | ns    |

| trdplesu   | Pipelined Read Enable Setup Time (A_DOUT_EN, B_DOUT_EN)                   | 0.256  | -     | ns    |

| trdplehd   | Pipelined Read Enable Hold Time (A_DOUT_EN, B_DOUT_EN)                    | 0.106  | -     | ns    |

| tr2q       | Asynchronous Reset to Output Propagation Delay                            |        | 1.603 | ns    |

| trstrem    | Asynchronous Reset Removal Time                                           | 0.522  | -     | ns    |

| trstrec    | Asynchronous Reset Recovery Time                                          | 0.005  | -     | ns    |

| trstmpw    | Asynchronous Reset Minimum Pulse Width                                    | 0.352  | -     | ns    |

| tpIrstrem  | Pipelined Register Asynchronous Reset Removal Time                        | -0.288 | -     | ns    |

| tpIrstrec  | Pipelined Register Asynchronous Reset Recovery Time                       | 0.338  | -     | ns    |

| tpIrstmpw  | Pipelined Register Asynchronous Reset Minimum Pulse Width                 | 0.33   | -     | ns    |

| tsrstsu    | Synchronous Reset Setup Time                                              | 0.233  | _     | ns    |

| tsrsthd    | Synchronous Reset Hold Time                                               | 0.037  | _     | ns    |

| twesu      | Write Enable Setup Time                                                   | 0.468  | _     | ns    |

| twehd      | Write Enable Hold Time                                                    | 0.05   | _     | ns    |

| Fmax       | Maximum Frequency                                                         | _      | 300   | MHz   |

# Table 123 • RAM1K18 – Dual-Port Mode for Depth × Width Configuration 16Kx1Worst-Case Military Conditions: $T_J = 125^{\circ}$ C, VDD = 1.14 V (continued)

# 12. Embedded NVM (eNVM) Characteristics

#### Table 132 • eNVM Read Performance

Worst-Case Conditions: VDD = 1.14 V, VPPNVM = VPP = 2.375 V

| Symbol               | Description                 | Operating Temperature Range |     |                |     |             | Unit |     |

|----------------------|-----------------------------|-----------------------------|-----|----------------|-----|-------------|------|-----|

| Тj                   | Junction Temperature Range  | -55°C to 125°C              |     | -40°C to 100°C |     | 0°C to 85°C |      | °C  |

| Speed grade          |                             | -1                          | Std | -1             | Std | -1          | Std  | -   |

| F <sub>MAXREAD</sub> | eNVM Maximum Read Frequency | 25                          | 25  | 25             | 25  | 25          | 25   | MHz |

Table 133 • eNVM Page Programming Worst-Case Conditions: VDD = 1.14 V, VPPNVM = VPP = 2.375 V

| Symbol               | Description                | Operating Temperature Range |     |                |     | Unit        |     |    |

|----------------------|----------------------------|-----------------------------|-----|----------------|-----|-------------|-----|----|

| Т <sub>ј</sub>       | Junction Temperature Range | -55°C to 125°C              |     | -40°C to 100°C |     | 0°C to 85°C |     | °C |

| Speed grade          |                            | -1                          | Std | -1             | Std | -1          | Std | -  |

| t <sub>PAGEPGM</sub> | eNVM Page Programming Time | 40                          | 40  | 40             | 40  | 40          | 40  | ms |

# 21. DDR Memory Interface Characteristics

*Table 150* • DDR Memory Interface Characteristics Worst-Case Military Conditions: T<sub>J</sub> = 125°C, VDD = 1.14 V

|          | Supported Data Rate |     |     |      |  |

|----------|---------------------|-----|-----|------|--|

| Standard | Min                 | Тур | Max | Unit |  |

| DDR3     |                     | 667 |     | Mbps |  |

| DDR2     |                     | 667 |     | Mbps |  |

| LPDDR    | 50                  | _   | 400 | Mbps |  |

# 23. PCIe Electrical and Timing AC and DC Characteristics

PCIe<sup>®</sup> is a high speed, packet-based, point-to-point, low pin count, serial interconnect bus. The IGLOO2 and SmartFusion2 SoC FPGAs has up to four hard high-speed serial interface blocks. Each SERDES block contains a PCIe system block. The PCIe system is connected to the SERDES block.

| Parameter     | Parameter Description                                   |       | Тур | Max              | Units |

|---------------|---------------------------------------------------------|-------|-----|------------------|-------|

| VTX-DIFF-PP   | Differential swing PCIe Gen1                            | 0.8   | -   | 1.2              | V     |

| VTX-CM-AC-P   | Output common mode voltage PCIe Gen1                    | -     | -   | 20               | mV    |

| VTX-RISE-FALL | Rise and fall time (20% to 80%) PCIe Gen1               | 0.125 | -   | -                | UI    |

| ZTX-DIFF-DC   | Output impedance – differential                         | 80    | -   | 120              | Ω     |

| LTX-SKEW      | Lane-to-lane TX skew within a SERDES block<br>PCle Gen1 | _     | -   | 500 ps<br>+ 2 UI | ps    |

| RLTX-DIFF     | Return loss differential mode PCIe Gen1                 | -10   | -   | -                | dB    |

| RLTX-CM       | Return loss common mode PCIe Gen1                       |       | _   | -                | dB    |

| TX-LOCK-RST   | Transmit PLL lock time from reset                       | _     | -   | 10               | μs    |

**Table 152** • Transmitter Parameters Worst-Case Military Conditions: T<sub>J</sub> = 125°C, VDD = 1.14 V

# Table 153 • Receiver ParametersWorst-Case Military Conditions: T<sub>J</sub> = 125°C, VDD = 1.14 V

| Parameter                                                                                    | Description                                            | Min   | Тур   | Max   | Units |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------|-------|-------|-------|-------|

| VRX-DIFF-PP-CC                                                                               | Input levels PCIe Gen1                                 | 0.175 | -     | 1.2   | V     |

| VRX-CM-DC-P Input common mode range (DC coupled)<br>Note: PCIe standard mandates AC coupling |                                                        | NA    | NA    | NA    | -     |

| VRX-CM-AC-P                                                                                  | Input common mode range (AC coupled)                   | -     | -     | 150   | mV    |

| VRX-DIFF-PP-CC                                                                               | Differential input sensitivity Gen1                    | 0.175 | -     | -     | mV    |

| ZRX-DIFF-DC                                                                                  | Differential input termination                         | 80    | 100   | 120   | Ω     |

| REXT                                                                                         | External calibration resistor                          | 1,188 | 1,200 | 1,212 | Ω     |

| CDR-LOCK-RST                                                                                 | CDR relock time from reset                             | _     | -     | 15    | μs    |

| RLRX-DIFF                                                                                    | Return loss differential mode PCIe Gen1                | -10   | -     | -     | dB    |

| RLRX-CM                                                                                      | Return loss common mode PCIe Gen1                      | -6    | -     | -     | dB    |

|                                                                                              | CID limit (set by 8B/10B coding, not the receiver PLL) | -     | -     | 4     | UI    |

| VRX-IDLE-DET-DIFF-PP                                                                         | Signal detect limit                                    | 65    | -     | 175   | mV    |

Table 154 • SERDES Reference Clock AC Specifications

Worst-Case Military Conditions: T<sub>J</sub> = 125°C, Worst-Case VDD = 1.14V

| Symbols  | Description                     | Min  | Тур | Max  | Units |

|----------|---------------------------------|------|-----|------|-------|

| FREFCLK  | Reference Clock Frequency       | 100  | -   | 160  | MHz   |

| TRISE    | Reference Clock Rise Time       | 0.6  | -   | 4    | V/ns  |

| TFALL    | Reference Clock Fall Time       | 0.6  | -   | 4    | V/ns  |

| TCYC     | Reference Clock Duty Cycle      | 40   | -   | 60   | %     |

| Mmrefclk | Reference Clock Mismatch        | -300 | -   | 300  | ppm   |

| SSCref   | Reference Spread Spectrum Clock | 0    | -   | 5000 | ppm   |

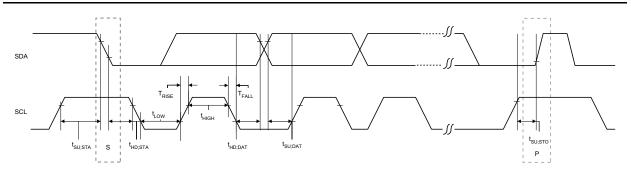

# Table 159 • I2C Switching CharacteristicsWorst-Case Military Conditions: TJ = 125°C, VDD = 1.14 V

|                     |                          |            | Speed<br>_^ |     |             |

|---------------------|--------------------------|------------|-------------|-----|-------------|

| Parameter           | Definition               | Conditions | Min         | Max | Units       |

| t <sub>LOW</sub>    | Low period of I2C_x_SCL  | -          | 1           | -   | pclk cycles |

| t <sub>HIGH</sub>   | High period of I2C_x_SCL | -          | 1           | -   | pclk cycles |

| t <sub>HD;STA</sub> | START hold time          | -          | 1           | -   | pclk cycles |

| t <sub>SU;STA</sub> | START setup time         | -          | 1           | -   | pclk cycles |

| t <sub>HD;DAT</sub> | DATA hold time           | -          | 1           | -   | pclk cycles |

| t <sub>SU;DAT</sub> | DATA setup time          | -          | 1           | -   | pclk cycles |

| t <sub>su;sto</sub> | STOP setup time          | -          | 1           | -   | pclk cycles |

Figure 16 • I<sup>2</sup>C Timing Parameter Definition

# 25. CAN Controller Characteristics

#### Table 161 • CAN Controller Characteristics

Worst-Case Military Conditions:  $T_J = 125^{\circ}C$ , VDD = 1.14 V

| Parameter       | Description                                               |                                   | Тур | Max  | Units | Notes |

|-----------------|-----------------------------------------------------------|-----------------------------------|-----|------|-------|-------|

| FCANREFCLK      | Internally Sourced CAN Reference Clock Frequency          | _                                 | _   | 128  | MHz   | *     |

| BAUDCAN         | CAN Performance Baud Rate                                 | rformance Baud Rate 0.05 – 1 Mbps |     | Mbps | -     |       |

| Note: PCLK to 0 | Note: PCLK to CAN controller must be a multiple of 8 MHz. |                                   |     |      |       |       |

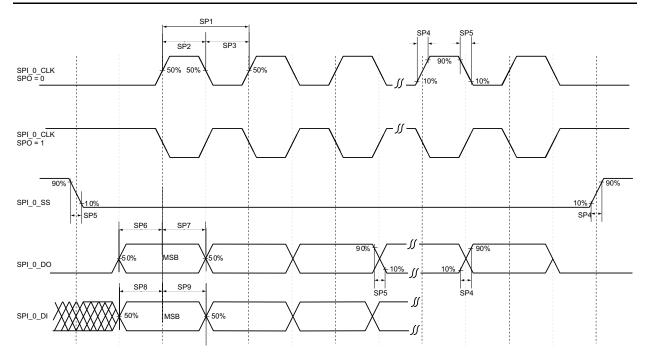

#### Table 164 • SPI Characteristics

Worst-Case Military Conditions: T<sub>J</sub> = 125°C, VDD = 1.14 V (continued)

|        |                        | All Devices/Speed Grades |     |     |         |          |           |

|--------|------------------------|--------------------------|-----|-----|---------|----------|-----------|

| Symbol | Description            | Conditions               | Min | Тур | Ma<br>x | Uni<br>t | Note<br>s |

| sp9s   | SPI_[0 1]_DI hold time | -                        | 3   | -   | 1       | ns       | 2         |

Notes:

1. For specific Rise/Fall Times board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website:

http://www.microsemi.com/products/fpga-soc/design-resources/ibis-models.

2. For allowable pclk configurations, refer to the Serial Peripheral Interface Controller section in the UG0331: SmartFusion2 Microcontroller Subsystem User Guide.

Figure 18 • SPI Timing for a Single Frame Transfer in Motorola Mode (SPH = 1)

# **Datasheet Categories**

## Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in Table 1 on page 10 is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

# **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

## Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production.

This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

# Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

# Production

This version contains information that is considered to be final.

# **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,600 employees globally. Learn more at **www.microsemi.com**.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.