Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Obsolete                                                     |

| Core Processor             | XCore                                                        |

| Core Size                  | 32-Bit 6-Core                                                |

| Speed                      | 400MIPS                                                      |

| Connectivity               | Configurable                                                 |

| Peripherals                | -                                                            |

| Number of I/O              | 42                                                           |

| Program Memory Size        | 64KB (16K x 32)                                              |

| Program Memory Type        | SRAM                                                         |

| EEPROM Size                | -                                                            |

| RAM Size                   | -                                                            |

| Voltage - Supply (Vcc/Vdd) | 0.90V ~ 5.5V                                                 |

| Data Converters            | A/D 4x12b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 96-LFBGA                                                     |

| Supplier Device Package    | 96-FBGA (10×10)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xs1-a6a-64-fb96-i4 |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TO OUR VALUED CUSTOMERS

X9530,

It is our intention to provide you with accurate and comprehensive documentation for the hardware and software components used in this product. To subscribe to receive updates, visit <a href="http://www.xmos.com/">http://www.xmos.com/</a>.

XMOS Ltd. is the owner or licensee of the information in this document and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd. makes no representation that the information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries, and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.

XS1-A6A-64-FB96

#### 1 xCORE Multicore Microcontrollers

The XS1-A Series is a comprehensive range of 32-bit multicore microcontrollers that brings the low latency and timing determinism of the xCORE architecture to mainstream embedded applications. Unlike conventional microcontrollers, xCORE multicore microcontrollers execute multiple real-time tasks simultaneously and communicate between tasks using a high speed network. Because xCORE multicore microcontrollers are completely deterministic, you can write software to implement functions that traditionally require dedicated hardware.

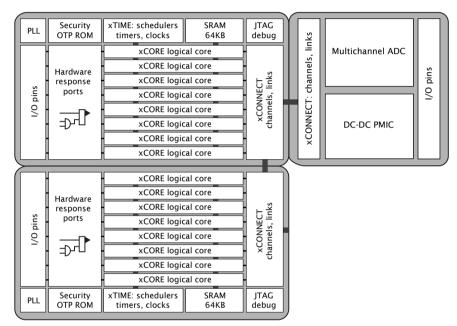

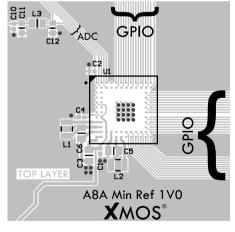

Figure 1: XS1-A Series:6-16 core devices

Key features of the XS1-A6A-64-FB96 include:

- ▶ **Tiles**: Devices consist of one or more xCORE tiles. Each tile contains between four and eight 32-bit xCOREs with highly integrated I/O and on-chip memory.

- ▶ Logical cores Each logical core can execute tasks such as computational code, DSP code, control software (including logic decisions and executing a state machine) or software that handles I/O. Section 7.1

- ➤ xTIME scheduler The xTIME scheduler performs functions similar to an RTOS, in hardware. It services and synchronizes events in a core, so there is no requirement for interrupt handler routines. The xTIME scheduler triggers cores on events generated by hardware resources such as the I/O pins, communication channels and timers. Once triggered, a core runs independently and concurrently to other cores, until it pauses to wait for more events. Section 7.2

# 3 Pin Configuration

|   | 1             | 2           | 3     | 4       | 5       | 6       | 7              | 8     | 9           | 10          | 11                     | 12           |

|---|---------------|-------------|-------|---------|---------|---------|----------------|-------|-------------|-------------|------------------------|--------------|

| А | AVDD          | ADC0        | ADC2  | NC      | X0D00   | X0D02   | X0D04          | X0D06 | X0D08       | 10<br>X0D10 | X0D12                  | X0D14        |

| В | TDO           | ADC1        | ADC3  | NC      | X0D01   | X0D03   | X0D05          | X0D07 | X0D09       | X0D11       | X0D13                  | X0D15        |

| С | тск           | RST_N       |       |         |         |         |                |       |             |             | X0D17                  | X0D16        |

| D | TMS           | TDI         |       |         |         |         |                |       |             |             | X0D19                  | X0D18        |

| E | OSC_<br>EXT_N | DEBUG_<br>N |       |         | GND     | GND     | GND            | GND   |             |             | X0D21                  | X0D20        |

| F | XI/<br>CLK    | NC          |       |         | AVSS    | GND     | GND            | GND   |             |             | X0D23                  | 1G<br>X0D22  |

| G | хо            | NC          |       |         | GND     | GND     | GND            | GND   |             |             | ADC<br>SAMPLE          | 32A<br>X0D70 |

| н | NC            | VSUP        |       |         | GND     | GND     | GND            | GND   |             |             | X0D25                  | X0D24        |

| J | SW1           | SW1         |       |         |         |         |                |       |             |             | <sup>4E</sup><br>X0D27 | 4E<br>X0D26  |

| К | VDDCORE       | VDDCORE     |       |         |         |         |                |       |             |             | 4F<br>X0D29            | 4F<br>X0D28  |

| L | PGND          | PGND        | VDDIO | MODE[0] | MODE[1] | MODE[2] | X0D43/<br>WAKE | X0D35 | X0D39       | 1N<br>X0D37 | 4F<br>X0D31            | 4F<br>X0D30  |

| М | VSUP          | VSUP        | VDDIO | PGND    | VDD1V8  | SW2     | MODE[3]        | X0D34 | 10<br>X0D38 | X0D36       | X0D33                  | 4E<br>X0D32  |

#### 6 Product Overview

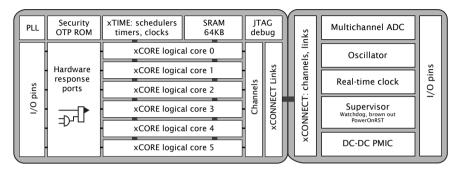

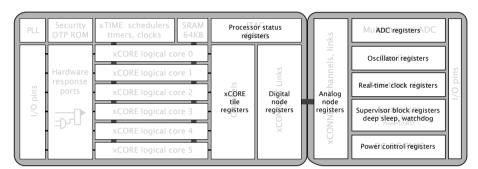

The XS1-A6A-64-FB96 comprises a digital and an analog node, as shown in Figure 3. The digital node comprises an xCORE Tile, a Switch, and a PLL (Phase-locked-loop). The analog node comprises a multi-channel ADC (Analog to Digital Converter), deep sleep memory, an oscillator, a real-time counter, and power supply control.

Figure 3: Block Diagram

All communication between the digital and analog node takes place over a link that is connected to the Switch of the digital node. As such, the analog node can be controlled from any node on the system. The analog functions can be configured using a set of node configuration registers, and a set of registers for each of the peripherals.

The device can be programmed using high-level languages such as C/C++ and the XMOS-originated XC language, which provides extensions to C that simplify the control over concurrency, I/O and timing, or low-level assembler.

#### 6.1 XCore Tile

The xCORE Tile is a flexible multicore microcontroller component with tightly integrated I/O and on-chip memory. The tile contains multiple logical cores that run simultaneously, each of which is guaranteed a slice of processing power and can execute computational code, control software and I/O interfaces. The logical cores use channels to exchange data within a tile or across tiles. Multiple devices can be deployed and connected using an integrated switching network, enabling more resources to be added to a design. The I/O pins are driven using intelligent ports that can serialize data, interpret strobe signals and wait for scheduled times or events, making the device ideal for real-time control applications.

#### 6.2 ADC and Power Management

Each XS1-A6A-64-FB96 device includes a set of analog components, including a 12b, 4-channel ADC, power management unit, watchdog timer, real-time counter and deep sleep memory. The device reduces the number of additional external components required and allows designs to be implemented using simple 2-layer boards.

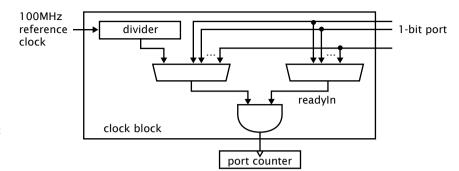

Figure 6: Clock block diagram

On reset, each port is connected to clock block 0, which runs from the processor reference clock.

#### 7.5 Channels and Channel Ends

Logical cores communicate using point-to-point connections, formed between two channel ends. A channel-end is a resource on an xCORE tile, that is allocated by the program. Each channel-end has a unique system-wide identifier that comprises a unique number and their tile identifier. Data is transmitted to a channel-end by an output-instruction; and the other side executes an input-instruction. Data can be passed synchronously or asynchronously between the channel ends.

#### 7.6 xCONNECT Switch and Links

XMOS devices provide a scalable architecture, where multiple xCORE devices can be connected together to form one system. Each xCORE device has an xCONNECT interconnect that provides a communication infrastructure for all tasks that run on the various xCORE tiles on the system.

The interconnect relies on a collection of switches and XMOS links. Each xCORE device has an on-chip switch that can set up circuits or route data. The switches are connected by xConnect Links. An XMOS link provides a physical connection between two switches. The switch has a routing algorithm that supports many different topologies, including lines, meshes, trees, and hypercubes.

The links operate in either 2 wires per direction or 5 wires per direction mode, depending on the amount of bandwidth required. Circuit switched, streaming and packet switched data can both be supported efficiently. Streams provide the fastest possible data rates between tiles, but each stream requires a single link to be reserved between switches on two tiles. All packet communications can be multiplexed onto a single link.

Information on the supported routing topologies that can be used to connect multiple devices together can be found in the XS1-L Link Performance and Design Guide, X2999.

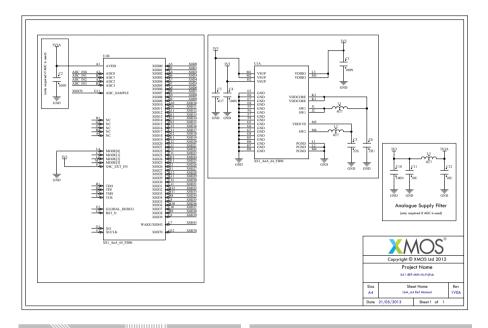

If the ADC Is used, it requires a 100nF X5R or X7R ceramic decoupling capacitor placed as close as possible to the AVDD pin. Care should be taken to minimize noise on these inputs, and if necessary an extra 10uF decoupling capacitor and ferrite bead can be used to remove noise from this supply.

The crystal oscillator requires careful routing of the XI / XO nodes as these are high impedance and very noise sensitive. Hence, the traces should be as wide and short as possible, and routed over a continuous ground plane. They should not be routed near noisy supply lines or clocks. The device has a load capacitance of 18pF for the crystal. Care must be taken, so that the inductance and resistance of the ground returns from the capacitors to the ground of the device is minimized.

#### 15.1 Land patterns and solder stencils

The land pattern recommendations in this document are based on a RoHS compliant process and derived, where possible, from the nominal *Generic Requirements for Surface Mount Design and Land Pattern Standards* IPC-7351B specifications. This standard aims to achieve desired targets of heel, toe and side fillets for solder-joints.

Solder paste and ground via recommendations are based on our engineering and development kit board production. They have been found to work and optimized as appropriate to achieve a high yield. These factors should be taken into account during design and manufacturing of the PCB.

The following land patterns and solder paste contains recommendations. Final land pattern and solder paste decisions are the responsibility of the customer. These should be tuned during manufacture to suit the manufacturing process.

The package is a 96 pin Ball Grid Array package on a 0.8mm pitch with 0.4mm balls.

An example land pattern is shown in Figure 20.

Pad widths and spacings are such that solder mask can still be applied between the pads using standard design rules. This is highly recommended to reduce solder shorts.

#### 15.2 Ground and Thermal Vias

Vias next to each ground ball into the ground plane of the PCB are recommended for a low inductance ground connection and good thermal performance. Vias with with a 0.6mm diameter annular ring and a 0.3mm drill would be suitable.

#### 15.3 Moisture Sensitivity

XMOS devices are, like all semiconductor devices, susceptible to moisture absorption. When removed from the sealed packaging, the devices slowly absorb moisture from the surrounding environment. If the level of moisture present in the device is too high during reflow, damage can occur due to the increased internal vapour

Figure 23:

Example

minimal

system

schematic,

with top and

bottom

layout of a

2-layer PCB

### **Appendices**

### A Configuring the device

The device is configured through ten banks of registers, as shown in Figure 40.

Figure 40: Registers

### A.1 Accessing a processor status register

The processor status registers are accessed directly from the processor instruction set. The instructions GETPS and SETPS read and write a word. The register number should be translated into a processor-status resource identifier by shifting the register number left 8 places, and ORing it with 0x0C. Alternatively, the functions getps (reg) and setps (reg, value) can be used from XC.

### A.2 Accessing an xCORE Tile configuration register

xCORE Tile configuration registers can be accessed through the interconnect using the functions write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tile \( \to \) ref, ...), where tileref is the name of the xCORE Tile, e.g. tile[1]. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the xCORE tile configuration registers. The destination of the channel-end should be set to OxnonnC20C where nnnnn is the tile-identifier.

A write message comprises the following:

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

| Bits  | Perm | Init | Description                                                                        |

|-------|------|------|------------------------------------------------------------------------------------|

| 31:24 | RO   | -    | Reserved                                                                           |

| 23:16 | RO   |      | xCORE tile number on the switch.                                                   |

| 15:9  | RO   | -    | Reserved                                                                           |

| 8     | RO   |      | Set to 1 if boot from OTP is enabled.                                              |

| 7:0   | RO   |      | The boot mode pins MODE0, MODE1,, specifying the boot frequency, boot source, etc. |

0x03: xCORE Tile boot status

### B.5 Security configuration: 0x05

Copy of the security register as read from OTP.

0x05: Security configuration

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | RO   |      | Value.      |

### **B.6** Ring Oscillator Control: 0x06

There are four free-running oscillators that clock four counters. The oscillators can be started and stopped using this register. The counters should only be read when the ring oscillator is stopped. The counter values can be read using four subsequent registers. The ring oscillators are asynchronous to the xCORE tile clock and can be used as a source of random bits.

**0x06:** Ring Oscillator Control

| Bits | Perm | Init | Description                                        |

|------|------|------|----------------------------------------------------|

| 31:2 | RO   | -    | Reserved                                           |

| 1    | RW   | 0    | Set to 1 to enable the xCORE tile ring oscillators |

| 0    | RW   | 0    | Set to 1 to enable the peripheral ring oscillators |

### B.7 Ring Oscillator Value: 0x07

This register contains the current count of the xCORE Tile Cell ring oscillator. This value is not reset on a system reset.

0x07: Ring Oscillator Value

| Bits  | Perm | Init | Description                   |

|-------|------|------|-------------------------------|

| 31:16 | RO   | -    | Reserved                      |

| 15:0  | RO   | -    | Ring oscillator counter data. |

### B.19 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over JTAG. This is the same set of registers as the Debug Scratch registers in the xCORE tile configuration.

0x20 .. 0x27: Debug scratch

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | DRW  |      | Value.      |

### B.20 Instruction breakpoint address: 0x30 .. 0x33

This register contains the address of the instruction breakpoint. If the PC matches this address, then a debug interrupt will be taken. There are four instruction breakpoints that are controlled individually.

0x30 .. 0x33: Instruction breakpoint address

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | DRW  |      | Value.      |

### B.21 Instruction breakpoint control: 0x40 .. 0x43

This register controls which logical cores may take an instruction breakpoint, and under which condition.

| Bits  | Perm | Init | Description                                                                                                                                                                           |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | RO   | -    | Reserved                                                                                                                                                                              |

| 23:16 | DRW  | 0    | A bit for each logical core in the tile allowing the breakpoint to be enabled individually for each logical core.                                                                     |

| 15:2  | RO   | -    | Reserved                                                                                                                                                                              |

| 1     | DRW  | 0    | Set to 1 to cause an instruction breakpoint if the PC is not equal to the breakpoint address. By default, the breakpoint is triggered when the PC is equal to the breakpoint address. |

| 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                                                                                                         |

0x40 .. 0x43: Instruction breakpoint control

#### B.22 Data watchpoint address 1: 0x50 ... 0x53

This set of registers contains the first address for the four data watchpoints.

0x60: SR of logical core 0

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | RO   |      | Value.      |

### C.17 SR of logical core 1: 0x61

0x61: SR of logical core 1

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | RO   |      | Value.      |

### C.18 SR of logical core 2: 0x62

0x62: SR of logical core 2

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | RO   |      | Value.      |

# C.19 SR of logical core 3: 0x63

**0x63:** SR of logical core 3

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | RO   |      | Value.      |

# C.20 SR of logical core 4: 0x64

**0x64:** SR of logical core 4

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | RO   |      | Value.      |

### C.21 SR of logical core 5: 0x65

**0x65:** SR of logical core 5

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | RO   |      | Value.      |

# **D** Digital Node Configuration

The digital node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...) for reads and writes).

| Number    | Perm | Description                           |

|-----------|------|---------------------------------------|

| 0x00      | RO   | Device identification                 |

| 0x01      | RO   | System switch description             |

| 0x04      | RW   | Switch configuration                  |

| 0x05      | RW   | Switch node identifier                |

| 0x06      | RW   | PLL settings                          |

| 0x07      | RW   | System switch clock divider           |

| 0x08      | RW   | Reference clock                       |

| 0x0C      | RW   | Directions 0-7                        |

| 0x0D      | RW   | Directions 8-15                       |

| 0x10      | RW   | DEBUG_N configuration                 |

| 0x1F      | RO   | Debug source                          |

| 0x20 0x27 | RW   | Link status, direction, and network   |

| 0x40 0x43 | RW   | PLink status and network              |

| 0x80 0x87 | RW   | Link configuration and initialization |

| 0xA0 0xA7 | RW   | Static link configuration             |

Figure 43: Summary

#### D.1 Device identification: 0x00

This register contains version and revision identifiers and the mode-pins as sampled at boot-time.

| Bits  | Perm | Init | Description                                    |

|-------|------|------|------------------------------------------------|

| 31:24 | RO   | 0x00 | Chip identifier.                               |

| 23:16 | RO   |      | Sampled values of pins MODE0, MODE1, on reset. |

| 15:8  | RO   |      | SSwitch revision.                              |

| 7:0   | RO   |      | SSwitch version.                               |

**0x00:**Device identification

### D.2 System switch description: 0x01

This register specifies the number of processors and links that are connected to this switch.

| Bits  | Perm | Init | Description                                                                         |

|-------|------|------|-------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                            |

| 25:23 | RW   |      | OD: Output divider value The initial value depends on pins MODE0 and MODE1.         |

| 22:21 | RO   | -    | Reserved                                                                            |

| 20:8  | RW   |      | F: Feedback multiplication ratio The initial value depends on pins MODE0 and MODE1. |

| 7     | RO   | -    | Reserved                                                                            |

| 6:0   | RW   |      | R: Oscilator input divider value The initial value depends on pins MODE0 and MODE1. |

0x06: PLL settings

### D.6 System switch clock divider: 0x07

Sets the ratio of the PLL clock and the switch clock.

**0x07:** System switch clock divider

| Bits  | Perm | Init | Description                                                                                            |

|-------|------|------|--------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | -    | Reserved                                                                                               |

| 15:0  | RW   | 0    | Switch clock divider. The PLL clock will be divided by this value plus one to derive the switch clock. |

#### D.7 Reference clock: 0x08

Sets the ratio of the PLL clock and the reference clock used by the node.

**0x08:** Reference clock

| Bits  | Perm | Init | Description                                                                                                                       |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | -    | Reserved                                                                                                                          |

| 15:0  | RW   | 3    | Architecture reference clock divider. The PLL clock will be divided by this value plus one to derive the 100 MHz reference clock. |

#### D.8 Directions 0-7: 0x0C

This register contains eight directions, for packets with a mismatch in bits 7..0 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

| Bits  | Perm | Init | Description                                                 |

|-------|------|------|-------------------------------------------------------------|

| 31:28 | RW   | 0    | The direction for packets whose first mismatching bit is 7. |

| 27:24 | RW   | 0    | The direction for packets whose first mismatching bit is 6. |

| 23:20 | RW   | 0    | The direction for packets whose first mismatching bit is 5. |

| 19:16 | RW   | 0    | The direction for packets whose first mismatching bit is 4. |

| 15:12 | RW   | 0    | The direction for packets whose first mismatching bit is 3. |

| 11:8  | RW   | 0    | The direction for packets whose first mismatching bit is 2. |

| 7:4   | RW   | 0    | The direction for packets whose first mismatching bit is 1. |

| 3:0   | RW   | 0    | The direction for packets whose first mismatching bit is 0. |

**0x0C:** Directions 0-7

#### D.9 Directions 8-15: 0x0D

This register contains eight directions, for packets with a mismatch in bits 15..8 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

| Bits  | Perm | Init | Description                                                  |

|-------|------|------|--------------------------------------------------------------|

| 31:28 | RW   | 0    | The direction for packets whose first mismatching bit is 15. |

| 27:24 | RW   | 0    | The direction for packets whose first mismatching bit is 14. |

| 23:20 | RW   | 0    | The direction for packets whose first mismatching bit is 13. |

| 19:16 | RW   | 0    | The direction for packets whose first mismatching bit is 12. |

| 15:12 | RW   | 0    | The direction for packets whose first mismatching bit is 11. |

| 11:8  | RW   | 0    | The direction for packets whose first mismatching bit is 10. |

| 7:4   | RW   | 0    | The direction for packets whose first mismatching bit is 9.  |

| 3:0   | RW   | 0    | The direction for packets whose first mismatching bit is 8.  |

**0x0D:** Directions 8-15

### D.10 DEBUG\_N configuration: 0x10

Configures the behavior of the DEBUG\_N pin.

| Bits | Perm | Init | Description                                                                          |

|------|------|------|--------------------------------------------------------------------------------------|

| 31:2 | RO   | -    | Reserved                                                                             |

| 1    | RW   | 0    | Set to 1 to enable signals on DEBUG_N to generate DCALL on the core.                 |

| 0    | RW   | 0    | When set to 1, the DEBUG_N wire will be pulled down when the node enters debug mode. |

0x10: DEBUG\_N configuration

#### E.8 Watchdog Disable: 0xD7

To enable the watchdog, write 0 to this register. To disable the watchdog, write the value 0x0D1SAB1E to this register.

**0xD7:** Watchdog Disable

| Bits | Perm | Init       | Description                                                                            |

|------|------|------------|----------------------------------------------------------------------------------------|

| 31:0 | RW   | 0x0D15AB1E | A value of 0x0D15AB1E written to this register resets and disables the watchdog timer. |

# F ADC Configuration

The device has a 12-bit Analogue to Digital Converter (ADC). It has multiple input pins, and on each positive clock edge on port 11, it samples and converts a value on the next input pin. The data is transmitted to a channel-end that must be set on enabling the ADC input pin.

The ADC is peripheral 2. The control registers are accessed using 32-bit reads and writes (use write\_periph\_32(device, 2, ...) and read\_periph\_32(device, 2, ...) for reads and writes).

| Number                                                          | Perm                            | Description             |

|-----------------------------------------------------------------|---------------------------------|-------------------------|

| 0x00 RW ADC Control input pin 0                                 |                                 | ADC Control input pin 0 |

| 0x04                                                            | 0x04 RW ADC Control input pin 1 |                         |

| 0x08 RW ADC Control input pin 2 0x0C RW ADC Control input pin 3 |                                 | ADC Control input pin 2 |

|                                                                 |                                 | ADC Control input pin 3 |

| 0x20                                                            | RW                              | ADC General Control     |

Figure 45: Summary

#### F.1 ADC Control input pin 0: 0x00

Controls specific to ADC input pin 0.

| Bits | Perm | Init | Description                                                                                                                                                                      |

|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RW   | 0    | The node and channel-end identifier to which data for this ADC input pin should be send to. This is the top 24 bits of the channel-end identifier as allocated on an xCORE Tile. |

| 7:1  | RO   | -    | Reserved                                                                                                                                                                         |

| 0    | RW   | 0    | Set to 1 to enable this input pin on the ADC.                                                                                                                                    |

0x00: ADC Control input pin 0

| Number | Perm              | Description                                |

|--------|-------------------|--------------------------------------------|

| 0x00   | RW                | General control                            |

| 0x04   | RW                | Time to wake-up, least significant 32 bits |

| 0x08   | RW                | Time to wake-up, most significant 32 bits  |

| 0x0C   | RW                | Power supply states whilst ASLEEP          |

| 0x10   | RW                | Power supply states whilst WAKING1         |

| 0x14   | RW                | Power supply states whilst WAKING2         |

| 0x18   | RW                | Power supply states whilst AWAKE           |

| 0x1C   | RW                | Power supply states whilst SLEEPING1       |

| 0x20   | RW                | Power supply states whilst SLEEPING2       |

| 0x24   | RW                | Power sequence status                      |

| 0x2C   | C RW DCDC control |                                            |

| 0x30   | RW                | Power supply status                        |

| 0x34   | RW                | VDDCORE level control                      |

| 0x40   | RW                | LDO5 level control                         |

Figure 49: Summary

### J.1 General control: 0x00

This register controls the basic settings for power modes.

### J.5 Power supply states whilst WAKING1: 0x10

This register controls what state the power control block should be in when in the WAKING1 state. It also defines the minimum time that the system shall stay in this state. When the minimum time is expired, the next state is entered if all enabled power supplies are good.

| Bits  | Perm | Init | Description                                                                                                                    |  |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------|--|

| 31:21 | RO   | -    | Reserved                                                                                                                       |  |

| 20:16 | RW   | 16   | Log2 number of cycles to stay in this state: 0: 1 clock cycles 1: 2 clock cycles 2: 4 clock cycles 31: 2147483648 clock cycles |  |

| 15    | RO   | -    | Reserved                                                                                                                       |  |

| 14    | RW   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                   |  |

| 13:10 | RO   | -    | Reserved                                                                                                                       |  |

| 9     | RW   | 0    | ets modulation used by DCDC2:<br>1: PWM modulation (max 475 mA)<br>: PFM modulation (max 50 mA)                                |  |

| 8     | RW   | 0    | Sets modulation used by DCDC1: 0: PWM modulation (max 700 mA) 1: PFM modulation (max 50 mA)                                    |  |

| 7:6   | RO   | -    | Reserved                                                                                                                       |  |

| 5     | RW   | 1    | Set to 1 to enable VOUT6 (IO supply).                                                                                          |  |

| 4     | RW   | 0    | Set to 1 to enable LDO5 (core PLL supply).                                                                                     |  |

| 3:2   | RO   | -    | Reserved                                                                                                                       |  |

| 1     | RO   | 0    | Set to 1 to enable DCDC2 (analogue supply).                                                                                    |  |

| 0     | RW   | 0    | Set to 1 to enable DCDC1 (core supply).                                                                                        |  |

0x10: Power supply states whilst WAKING1

# J.6 Power supply states whilst WAKING2: 0x14

This register controls what state the power control block should be in when in the WAKING2 state. It also defines the minimum time that the system shall stay in this state. When the minimum time is expired, the next state is entered if all enabled power supplies are good.

| Bits  | Perm | Init | Description                                                                                                                    |  |  |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| 31:21 | RO   | -    | Reserved                                                                                                                       |  |  |

| 20:16 | RW   | 16   | Log2 number of cycles to stay in this state: 0: 1 clock cycles 1: 2 clock cycles 2: 4 clock cycles 31: 2147483648 clock cycles |  |  |

| 15    | RO   | -    | Reserved                                                                                                                       |  |  |

| 14    | RW   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                   |  |  |

| 13:10 | RO   | -    | Reserved                                                                                                                       |  |  |

| 9     | RW   | 0    | Sets modulation used by DCDC2:<br>0: PWM modulation (max 475 mA)<br>1: PFM modulation (max 50 mA)                              |  |  |

| 8     | RW   | 0    | Sets modulation used by DCDC1:<br>0: PWM modulation (max 700 mA)<br>1: PFM modulation (max 50 mA)                              |  |  |

| 7:6   | RO   | -    | Reserved                                                                                                                       |  |  |

| 5     | RW   | 1    | Set to 1 to enable VOUT6 (IO supply).                                                                                          |  |  |

| 4     | RW   | 0    | Set to 1 to enable LDO5 (core PLL supply).                                                                                     |  |  |

| 3:2   | RO   | -    | Reserved                                                                                                                       |  |  |

| 1     | RO   | 1    | Set to 1 to enable DCDC2 (analogue supply).                                                                                    |  |  |

| 0     | RW   | 0    | Set to 1 to enable DCDC1 (core supply).                                                                                        |  |  |

0x1C: Power supply states whilst SLEEPING1

# J.9 Power supply states whilst SLEEPING2: 0x20

This register controls what state the power control block should be in when in the SLEEPING2 state. It also defines the time that the system shall stay in this state.

| Bits  | Perm | Init | Description                                                                                                                                                                           |  |  |  |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                              |  |  |  |

| 25:24 | RW   | 2    | Sets the power good level for VDDCORE and VDD1V8: 0: 0.80 x VDDCORE, 0.80 x VDD1V8 1: 0.85 x VDDCORE, 0.85 x VDD1V8 2: 0.90 x VDDCORE, 0.90 x VDD1V8 3: 0.75 x VDDCORE, 0.75 x VDD1V8 |  |  |  |

| 23:17 | RO   | -    | Reserved                                                                                                                                                                              |  |  |  |

| 16    | RW   | 0    | Clear DCDC1 and DCDC2 error flags, not self clearing.                                                                                                                                 |  |  |  |

| 15    | RO   | -    | Reserved                                                                                                                                                                              |  |  |  |

| 14:13 | RW   | 0    | Sets the DCDC2 current limit: 0: 1A 1: 1.5A 2: 2A 3: 0.5A                                                                                                                             |  |  |  |

| 12:10 | RO   | -    | Reserved                                                                                                                                                                              |  |  |  |

| 9:8   | RW   | 1    | Sets the clock used by DCDC2 to generate VDD1V8: 0: 0.9 MHz 1: 1.0 MHz 2: 1.1 MHz 3: 1.2 MHz                                                                                          |  |  |  |

| 7     | RO   | -    | Reserved                                                                                                                                                                              |  |  |  |

| 6:5   | RW   | 0    | Sets the DCDC1 current limit: 0: 1.2A 1: 1.8A 2: 2.5A 3: 0.8A                                                                                                                         |  |  |  |

| 4:2   | RO   | -    | Reserved                                                                                                                                                                              |  |  |  |

| 1:0   | RW   | 1    | Sets the clock used by DCDC1 to generate VDDCORE: 0: 0.9 MHz 1: 1.0 MHz 2: 1.1 MHz 3: 1.2 MHz                                                                                         |  |  |  |

0x2C: DCDC control

# J.12 Power supply status: 0x30

This register provides the current status of the power supplies.

# N Schematics Design Check List

This section is a checklist for use by schematics designers using the XS1-A6A-64-FB96. Each of the following sections contains items to check for each design.

N.1 Clock

|   | frequency. The MODE settings are shown in the Oscillator section Section 8. If you have a choice between two values, choose the value with the highest multiplier ratio since that will boot faster. |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| П | OSC_EXT_N is tied to ground (for use with a crystal or oscillator) or                                                                                                                                |

|             | OSC_EXI_N is tied to ground (for use with a crystal or oscillator) or       |

|-------------|-----------------------------------------------------------------------------|

| <del></del> | tied to VDDIO (for use with the internal oscillator). If using the internal |

|             | oscillator, set MODE0 and MODE1 to be for the 20-48 MHz range               |

|             | (Section 8).                                                                |

|             |                                                                             |

| If you have used an oscillator, it is a 1V8 oscillator. (Section 10) | <b>6</b> ) |

|----------------------------------------------------------------------|------------|

|----------------------------------------------------------------------|------------|

### N.2 USB ULPI Mode

This section can be skipped if you do not have an external USB PHY.

| If using ULPI, | the ULPI | signals | are ( | connected | to | specific | ports | as | shown |

|----------------|----------|---------|-------|-----------|----|----------|-------|----|-------|

| in Section K.  |          |         |       |           |    |          |       |    |       |

| If using ULPI, the ports that are used internally are not connected,     |

|--------------------------------------------------------------------------|

| see Section K. (Note that this limitation only applies when the ULPI is  |

| enabled, they can still be used before or after the ULPI is being used.) |

#### N.3 Boot

| The device is connected to a SPI flash | Tiol booting, connected to AUDO |

|----------------------------------------|---------------------------------|

| X0D01, X0D10, and X0D11 (Section       | n 9). If not, you must boot the |

| device through OTP or JTAG.            |                                 |

| DDE2 and MOI  | DE3       |

|---------------|-----------|

| no debug adap | oter      |

| 2 and MODE3   | are       |

|               |           |

| 2             | and MODE3 |

|   | The SPI flash that you have chosen is supported by <b>xflash</b> , or you hav | e |

|---|-------------------------------------------------------------------------------|---|

| _ | created a specification file for it.                                          |   |