Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Obsolete                                                     |

| Core Processor             | XCore                                                        |

| Core Size                  | 32-Bit 6-Core                                                |

| Speed                      | 500MIPS                                                      |

| Connectivity               | Configurable                                                 |

| Peripherals                | -                                                            |

| Number of I/O              | 42                                                           |

| Program Memory Size        | 64KB (16K x 32)                                              |

| Program Memory Type        | SRAM                                                         |

| EEPROM Size                | -                                                            |

| RAM Size                   | -                                                            |

| Voltage - Supply (Vcc/Vdd) | 0.90V ~ 5.5V                                                 |

| Data Converters            | A/D 4x12b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 96-LFBGA                                                     |

| Supplier Device Package    | 96-FBGA (10x10)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xs1-a6a-64-fb96-i5 |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4 Signal Description

This section lists the signals and I/O pins available on the XS1-A6A-64-FB96. The device provides a combination of 1 bit, 4bit, 8bit and 16bit ports, as well as wider ports that are fully or partially (gray) bonded out. All pins of a port provide either output or input, but signals in different directions cannot be mapped onto the same port.

Pins may have one or more of the following properties:

- ▶ PD/PU: The IO pin a weak pull-down or pull-up resistor. On GPIO pins this resistor can be enabled.

- ▶ ST: The IO pin has a Schmitt Trigger on its input.

| Power pins (9) |                               |      |            |  |

|----------------|-------------------------------|------|------------|--|

| Signal         | Function                      | Туре | Properties |  |

| AVSS           | Digital ground                | GND  |            |  |

| GND            | Digital ground                | GND  |            |  |

| PGND           | Power ground                  | GND  |            |  |

| SW1            | DCDC1 switched output voltage | PWR  |            |  |

| SW2            | DCDC2 switched output voltage | PWR  |            |  |

| VDD1V8         | 1v8 voltage supply            | PWR  |            |  |

| VDDCORE        | Core voltage supply           | PWR  |            |  |

| VDDIO          | Digital I/O power             | PWR  |            |  |

| VSUP           | Power supply (3V3/5V0)        | PWR  |            |  |

| Analog pins (6) |                              |       |            |  |

|-----------------|------------------------------|-------|------------|--|

| Signal          | Function                     | Type  | Properties |  |

| ADC0            | Analog input                 | Input |            |  |

| ADC1            | Analog input                 | Input |            |  |

| ADC2            | Analog input                 | Input |            |  |

| ADC3            | Analog input                 | Input |            |  |

| ADC_SAMPLE      | Sample Analog input          | I/O   |            |  |

| AVDD            | Supply and reference voltage | PWR   |            |  |

|           | Clocks pins (4)                |        |            |  |  |

|-----------|--------------------------------|--------|------------|--|--|

| Signal    | Function                       | Type   | Properties |  |  |

| MODE[3:0] | Boot mode select               | Input  | PU, ST     |  |  |

| OSC_EXT_N | Use Silicon Oscillator         | Input  | ST         |  |  |

| XI/CLK    | Crystal Oscillator/Clock Input | Input  |            |  |  |

| хо        | Crystal Oscillator Output      | Output |            |  |  |

| JTAG pins (5) |                  |        |            |  |

|---------------|------------------|--------|------------|--|

| Signal        | Function         | Type   | Properties |  |

| DEBUG_N       | Multi-chip debug | I/O    | PU         |  |

| TCK           | Test clock       | Input  | PU, ST     |  |

| TDI           | Test data input  | Input  | PU, ST     |  |

| TDO           | Test data output | Output | PD, OT     |  |

| TMS           | Test mode select | Input  | PU, ST     |  |

| Misc pins (1) |                    |       |            |

|---------------|--------------------|-------|------------|

| Signal        | Function           | Type  | Properties |

| RST_N         | Global reset input | Input | PU, ST     |

| I/O pins (42) |                                                                                                    |      |                                  |  |

|---------------|----------------------------------------------------------------------------------------------------|------|----------------------------------|--|

| Signal        | Function                                                                                           | Туре | Properties                       |  |

| X0D00         | 1A <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>S</sub> |  |

| X0D01         | XLA <sub>out</sub> 1B <sup>0</sup>                                                                 | I/O  | PD <sub>S</sub> , R <sub>S</sub> |  |

| X0D02         | XLA <sub>out</sub> 4A <sup>0</sup> 8A <sup>0</sup> 16A <sup>0</sup> 32A <sup>20</sup>              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D03         | XLA <sub>out</sub> 4A <sup>1</sup> 8A <sup>1</sup> 16A <sup>1</sup> 32A <sup>21</sup>              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D04         | XLA <sub>out</sub> 4B <sup>0</sup> 8A <sup>2</sup> 16A <sup>2</sup> 32A <sup>22</sup>              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D05         | XLA <sub>out</sub> 4B <sup>1</sup> 8A <sup>3</sup> 16A <sup>3</sup> 32A <sup>23</sup>              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D06         | XLA <sub>in</sub> 4B <sup>2</sup> 8A <sup>4</sup> 16A <sup>4</sup> 32A <sup>24</sup>               | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D07         | XLA <sub>in</sub> 4B <sup>3</sup> 8A <sup>5</sup> 16A <sup>5</sup> 32A <sup>25</sup>               | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D08         | XLA <sub>in</sub> <sup>2</sup> 4A <sup>2</sup> 8A <sup>6</sup> 16A <sup>6</sup> 32A <sup>26</sup>  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D09         | XLA <sub>in</sub> 4A <sup>3</sup> 8A <sup>7</sup> 16A <sup>7</sup> 32A <sup>27</sup>               | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D10         | XLA <sub>in</sub> 1C <sup>0</sup>                                                                  | I/O  | PD <sub>S</sub> , R <sub>S</sub> |  |

| X0D11         | 1D <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>S</sub> |  |

| X0D12         | 1E <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D13         | XLB <sup>4</sup> <sub>out</sub> 1F <sup>0</sup>                                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D14         | XLB <sup>3</sup> <sub>out</sub> 4C <sup>0</sup> 8B <sup>0</sup> 16A <sup>8</sup> 32A <sup>28</sup> | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D15         | XLB <sub>out</sub> 4C <sup>1</sup> 8B <sup>1</sup> 16A <sup>9</sup> 32A <sup>29</sup>              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D16         | XLB <sup>1</sup> <sub>out</sub> 4D <sup>0</sup> 8B <sup>2</sup> 16A <sup>10</sup>                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D17         | XLB <sup>0</sup> <sub>out</sub> 4D <sup>1</sup> 8B <sup>3</sup> 16A <sup>11</sup>                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D18         | XLB <sub>in</sub> 4D <sup>2</sup> 8B <sup>4</sup> 16A <sup>12</sup>                                | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D19         | XLB <sup>1</sup> <sub>in</sub> 4D <sup>3</sup> 8B <sup>5</sup> 16A <sup>13</sup>                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D20         | XLB <sub>in</sub> <sup>2</sup> 4C <sup>2</sup> 8B <sup>6</sup> 16A <sup>14</sup> 32A <sup>30</sup> | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D21         | XLB <sup>3</sup> 4C <sup>3</sup> 8B <sup>7</sup> 16A <sup>15</sup> 32A <sup>31</sup>               | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D22         | XLB <sup>4</sup> <sub>in</sub> 1G <sup>0</sup>                                                     | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D23         | 1H <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

| X0D24         | 110                                                                                                | I/O  | PDs                              |  |

| X0D25         | 1J <sup>0</sup>                                                                                    | I/O  | PDs                              |  |

| X0D26         | 4E <sup>0</sup> 8C <sup>0</sup> 16B <sup>0</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |

(continued)

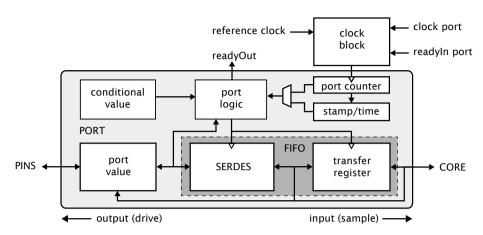

Figure 5: Port block diagram

Data is transferred between the pins and core using a FIFO that comprises a SERDES and transfer register, providing options for serialization and buffered data.

Each port has a 16-bit counter that can be used to control the time at which data is transferred between the port value and transfer register. The counter values can be obtained at any time to find out when data was obtained, or used to delay I/O until some time in the future. The port counter value is automatically saved as a timestamp, that can be used to provide precise control of response times.

The ports and xCONNECT links are multiplexed onto the physical pins. If an xConnect Link is enabled, the pins of the underlying ports are disabled. If a port is enabled, it overrules ports with higher widths that share the same pins. The pins on the wider port that are not shared remain available for use when the narrower port is enabled. Ports always operate at their specified width, even if they share pins with another port.

#### 7.4 Clock blocks

xCORE devices include a set of programmable clocks called clock blocks that can be used to govern the rate at which ports execute. Each xCORE tile has six clock blocks: the first clock block provides the tile reference clock and runs at a default frequency of 100MHz; the remaining clock blocks can be set to run at different frequencies.

A clock block can use a 1-bit port as its clock source allowing external application clocks to be used to drive the input and output interfaces.

In many cases I/O signals are accompanied by strobing signals. The xCORE ports can input and interpret strobe (known as readyln and readyOut) signals generated by external sources, and ports can generate strobe signals to accompany output data.

The PLL creates a high-speed clock that is used for the switch, tile, and reference clock.

The PLL multiplication value is selected through the two MODE pins, and can be changed by software to speed up the tile or use less power. The MODE pins are set as shown in Figure 8:

Figure 8: PLL multiplier values and MODE pins

| Oscillator I |   | DDE         | Tile           | PLL Ratio | PLL | setting | gs |

|--------------|---|-------------|----------------|-----------|-----|---------|----|

| Frequency    | 1 | 0 Frequency |                |           | OD  | F       | R  |

| 5-13 MHz     | 0 | 0           | 130-399.75 MHz | 30.75     | 1   | 122     | 0  |

| 13-20 MHz    | 1 | 1           | 260-400.00 MHz | 20        | 2   | 119     | 0  |

| 20-48 MHz    | 1 | 0           | 167-400.00 MHz | 8.33      | 2   | 49      | 0  |

| 48-100 MHz   | 0 | 1           | 196-400.00 MHz | 4         | 2   | 23      | 0  |

Figure 8 also lists the values of OD, F and R, which are the registers that define the ratio of the tile frequency to the oscillator frequency:

$$F_{core} = F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \times \frac{1}{OD+1}$$

OD, F and R must be chosen so that  $0 \le R \le 63$ ,  $0 \le F \le 4095$ ,  $0 \le OD \le 7$ , and  $260MHz \le F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \le 1.3GHz$ . The OD, F, and R values can be modified by writing to the digital node PLL configuration register.

The MODE pins must be held at a static value during and after deassertion of the system reset.

If a different tile frequency is required (eg, 500 MHz), then the PLL must be reprogrammed after boot to provide the required tile frequency. The XMOS tools perform this operation by default. Further details on configuring the clock can be found in the XS1-L Clock Frequency Control document, X1433.

#### 9 Boot Procedure

The device is kept in reset by driving RST\_N low. When in reset, all GPIO pins are high impedance. When the device is taken out of reset by releasing RST\_N the processor starts its internal reset process. After approximately 750,000 input clocks, all GPIO pins have their internal pull-resistor enabled, and the processor boots at a clock speed that depends on MODE0 and MODE1.

The processor boot procedure is illustrated in Figure 9. In normal usage, MODE[3:2] controls the boot source according to the table in Figure 10. If bit 5 of the security register (see §10.1) is set, the device boots from OTP.

The boot image has the following format:

- ▶ A 32-bit program size *s* in words.

- $\triangleright$  Program consisting of  $s \times 4$  bytes.

## 12 Supervisor Logic

An independent supervisor circuit provides power-on-reset, brown-out, and watch-dog capabilities. This facilitates the design of systems that fail gracefully, whilst keeping BOM costs down.

21

The reset supervisor holds the chip in reset until all power supplies are good. This provides a power-on-reset (POR). An external reset is optional and the pin RST\_N can be left not-connected.

If at any time any of the power supplies drop because of too little supply or too high a demand, the power supervisor will bring the chip into reset until the power supplies have been restored. This will reboot the system as if a cold-start has happened.

The 16-bit watchdog timer provides 1ms accuracy and runs independently of the real-time counter. It can be programmed with a time-out of between 1 ms and 65 seconds (Appendix E). If the watchdog is not set before it times out, the XS1-A6A-64-FB96 is reset. On boot, the program can read a register to test whether the reset was due to the watchdog. The watchdog timer is only enabled and clocked whilst the processor is in the AWAKE power state.

## 13 Energy management

XS1-A6A-64-FB96 devices can be powered by:

- ► An external 5v core and 3.3v I/O supply.

- ► A single 3.3v supply.

#### 13.1 DC-DC

XS1-A6A-64-FB96 devices include two DC-DC buck converters which can be configured to take input voltages between 3.3-5V power supply and output circuit voltages (nominally 1.8V and 1.0V) required by the analog peripherals and digital node.

#### 13.2 Power mode controller

The device transitions through multiple states during the power-up and powerdown process.

The device is quiescent in the ASLEEP state, and is running in the AWAKE state. The other states allow a controlled transition between AWAKE and ASLEEP.

A transition from AWAKE state to ASLEEP state is instigated by a write to the general control register. Sleep requests must only be made in the AWAKE state.

A transition from the ASLEEP state into the AWAKE state is instigated by a wakeup request triggered by an input, or a timer. The device only responds to a wakeup

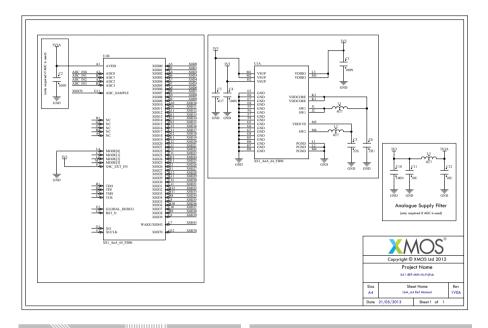

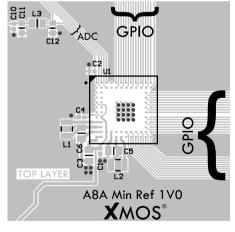

Figure 23:

Example

minimal

system

schematic,

with top and

bottom

layout of a

2-layer PCB

# 17 DC and Switching Characteristics

## 17.1 Operating Conditions

| Symbol                                     | Parameter                                     | MIN  | TYP  | MAX  | UNITS | Notes |

|--------------------------------------------|-----------------------------------------------|------|------|------|-------|-------|

| VSUP                                       | Power Supply (3.3V Mode)                      | 3.00 | 3.30 | 3.60 | V     |       |

| V301                                       | Power Supply (5V Mode)                        | 4.50 | 5.00 | 5.50 | V     |       |

| VDDIO                                      | I/O supply voltage                            | 3.00 | 3.30 | 3.60 | V     |       |

| AVDD                                       | Analog Supply and Reference<br>Voltage        | 3.00 | 3.30 | 3.60 | V     |       |

| Cl                                         | Cl xCORE Tile I/O load capacitance            |      |      | 25   | pF    |       |

| Та                                         | Ta Ambient operating temperature (Commercial) |      |      | 70   | °C    |       |

| Ambient operating temperature (Industrial) |                                               | -40  |      | 85   | °C    |       |

| Tj                                         | Junction temperature                          |      |      | 125  | °C    |       |

| Tstq                                       | Storage temperature                           | -65  |      | 150  | °C    |       |

Figure 24: Operating conditions

## 17.2 DC1 Characteristics

| Symbol                   | Parameter                                | MIN  | TYP  | MAX  | UNITS     | Notes |

|--------------------------|------------------------------------------|------|------|------|-----------|-------|

| VDDCORE                  | Tile Supply Voltage                      | 0.90 | 1.00 | 1.10 | V         |       |

| V(RIPPLE)                | Ripple Voltage (peak to peak)            |      | 10   | 40   | mV        |       |

| V(ACC)                   | Voltage Accuracy                         | -5   |      | 5    | %         | Α     |

| F(S) Switching Frequency |                                          |      | 1    |      | MHz       |       |

| F(SVAR)                  | F(SVAR) Variation in Switching Frequency |      |      | 10   | %         |       |

| Effic                    | Efficiency                               |      | 80   |      | %         |       |

| PGT(HIGH)                | Powergood Threshold<br>(High)            |      | 95   |      | %/VDDCORE |       |

| PGT(LOW)                 | Powergood Threshold<br>(Low)             |      | 80   |      | %/VDDCORE |       |

Figure 25: DC1 characteristics

A If supplied externally.

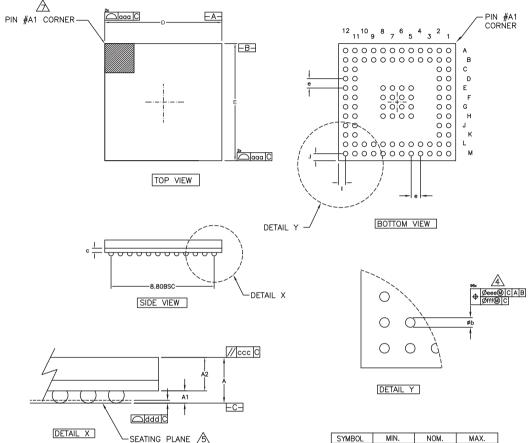

## 18 Package Information

#### NOTE:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS, ANGLE IS DEGREES.

- 2. "e" REPRESENTS THE BASIC SOLDER BALL GRID PITCH.

- 3. "M" REPRESENTS THE MAXIMUM SOLDER BALL MATRIX SIZE.

5 PRIMARY DATUM FC- AND SEATING PLANE ARE DESIGNED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

6. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994

A1 CORNER MUST BE IDENTIFIED BY LASER MARK.

8. PACKAGE DIMENSIONS CONFORM TO JEDEC REGISTRATION MO-275.

| SYMBOL | MIN.                              | NOM.  | MAX.  |  |  |

|--------|-----------------------------------|-------|-------|--|--|

| Α      | 1.26                              | 1.36  | 1.46  |  |  |

| A1     | 0.25                              | 0.30  | 0.35  |  |  |

| A2     | 1.01                              | 1.06  | 1.11  |  |  |

| D      | 9.90                              | 10.00 | 10.10 |  |  |

| Е      | 9.90                              | 10.00 | 10.10 |  |  |

| - 1    | 0.60 REF.                         |       |       |  |  |

| J      | 0.60 REF.                         |       |       |  |  |

| М      | 10x10 <depopulated></depopulated> |       |       |  |  |

| aaa    |                                   |       | 0.15  |  |  |

| ccc    |                                   |       | 0.20  |  |  |

| ddd    |                                   |       | 0.10  |  |  |

| eee    |                                   |       | 0.15  |  |  |

| fff    | 0.08                              |       |       |  |  |

| b      | 0.35 0.40 0.45                    |       |       |  |  |

| е      | 0.80 BSC.                         |       |       |  |  |

| С      | 0.36 REF.                         |       |       |  |  |

| Bits  | Perm | Init | Description                                                                        |

|-------|------|------|------------------------------------------------------------------------------------|

| 31:24 | RO   | -    | Reserved                                                                           |

| 23:16 | RO   |      | xCORE tile number on the switch.                                                   |

| 15:9  | RO   | -    | Reserved                                                                           |

| 8     | RO   |      | Set to 1 if boot from OTP is enabled.                                              |

| 7:0   | RO   |      | The boot mode pins MODE0, MODE1,, specifying the boot frequency, boot source, etc. |

0x03: xCORE Tile boot status

### B.5 Security configuration: 0x05

Copy of the security register as read from OTP.

0x05: Security configuration

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | RO   |      | Value.      |

### **B.6** Ring Oscillator Control: 0x06

There are four free-running oscillators that clock four counters. The oscillators can be started and stopped using this register. The counters should only be read when the ring oscillator is stopped. The counter values can be read using four subsequent registers. The ring oscillators are asynchronous to the xCORE tile clock and can be used as a source of random bits.

**0x06:** Ring Oscillator Control

| Bits | Perm | Init | Description                                        |

|------|------|------|----------------------------------------------------|

| 31:2 | RO   | -    | Reserved                                           |

| 1    | RW   | 0    | Set to 1 to enable the xCORE tile ring oscillators |

| 0    | RW   | 0    | Set to 1 to enable the peripheral ring oscillators |

### B.7 Ring Oscillator Value: 0x07

This register contains the current count of the xCORE Tile Cell ring oscillator. This value is not reset on a system reset.

0x07: Ring Oscillator Value

| Bits  | Perm | Init | Description                   |

|-------|------|------|-------------------------------|

| 31:16 | RO   | -    | Reserved                      |

| 15:0  | RO   | -    | Ring oscillator counter data. |

0x50 .. 0x53: Data watchpoint address 1

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | DRW  |      | Value.      |

### B.23 Data watchpoint address 2: 0x60 .. 0x63

This set of registers contains the second address for the four data watchpoints.

0x60 .. 0x63: Data watchpoint address 2

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | DRW  |      | Value.      |

## B.24 Data breakpoint control register: 0x70 .. 0x73

This set of registers controls each of the four data watchpoints.

| Bits  | Perm | Init | Description                                                                                                                                                                                                                                                                                       |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | RO   | -    | Reserved                                                                                                                                                                                                                                                                                          |

| 23:16 | DRW  | 0    | A bit for each logical core in the tile allowing the breakpoint to be enabled individually for each logical core.                                                                                                                                                                                 |

| 15:3  | RO   | -    | Reserved                                                                                                                                                                                                                                                                                          |

| 2     | DRW  | 0    | Set to 1 to enable breakpoints to be triggered on loads. Breakpoints always trigger on stores.                                                                                                                                                                                                    |

| 1     | DRW  | 0    | By default, data watchpoints trigger if memory in the range [Address1Address2] is accessed (the range is inclusive of Address1 and Address2). If set to 1, data watchpoints trigger if memory outside the range (Address2Address1) is accessed (the range is exclusive of Address2 and Address1). |

| 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                                                                                                                                                                                                                     |

0x70 .. 0x73: Data breakpoint control register

### B.25 Resources breakpoint mask: 0x80 .. 0x83

This set of registers contains the mask for the four resource watchpoints.

### C.22 Chanend status: 0x80 .. 0x9F

These registers record the status of each channel-end on the tile.

| Bits  | Perm | Init | Description                                                                                                    |

|-------|------|------|----------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                       |

| 25:24 | RO   |      | 00 - ChannelEnd, 01 - ERROR, 10 - PSCTL, 11 - Idle.                                                            |

| 23:16 | RO   |      | Based on SRC_TARGET_TYPE value, it represents channelEnd ID or Idle status.                                    |

| 15:6  | RO   | -    | Reserved                                                                                                       |

| 5:4   | RO   |      | Two-bit network identifier                                                                                     |

| 3     | RO   | -    | Reserved                                                                                                       |

| 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                                          |

| 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                 |

| 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch. |

0x80 .. 0x9F: Chanend status

#### E.6 Link Control and Status: 0x80

| Bits  | Perm | Init | Description                                                                                                                                                                                         |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:28 | RO   | -    | Reserved                                                                                                                                                                                            |

| 27    | RO   | 0    | Set to 1 on error: an RX buffer overflow or illegal token encoding has been received. This bit clears on reading.                                                                                   |

| 26    | RO   | 0    | 1 if this end of the link has issued credit to allow the remote end to transmit.                                                                                                                    |

| 25    | RO   | 0    | 1 if this end of the link has credits to allow it to transmit.                                                                                                                                      |

| 24    | WO   | 0    | Set to 1 to initialize a half-duplex link. This clears this end of<br>the link's credit and issues a HELLO token; the other side of the<br>link will reply with credits. This bit is self-clearing. |

| 23    | WO   | 0    | Set to 1 to reset the receiver. The next symbol that is detected will be assumed to be the first symbol in a token. This bit is self-clearing.                                                      |

| 22    | RO   | -    | Reserved                                                                                                                                                                                            |

| 21:11 | RW   | 1    | The number of system clocks between two subsequent transitions within a token                                                                                                                       |

| 10:0  | RW   | 1    | The number of system clocks between two subsequent transmit tokens.                                                                                                                                 |

0x80: Link Control and Status

#### E.7 1 KHz Watchdog Control: 0xD6

The watchdog provides a mechanism to prevent programs from hanging by resetting the xCORE Tile after a pre-set time. The watchdog should be periodically "kicked" by the application, causing the count-down to be restarted. If the watchdog expires, it may be due to a program hanging, for example because of a (transient) hardware issue.

The watchdog timeout is measured in 1 ms clock ticks, meaning that a time between 1 ms and 65 seconds can be set for the timeout. The watchdog timer is only clocked during the AWAKE power state. When writing the timeout value, both the timeout and its one's complement should be written. This reduces the chances of accidentally setting kicking the watchdog. If the written value does not comprise a 16-bit value with a 16-bit one's complement, the request will be NACKed, otherwise an ACK will be sent.

If the watchdog expires, the xCORE Tile is reset.

| -          | xD6         |

|------------|-------------|

| ا<br>Watcl | KHz<br>hdog |

| Co         | ntrol       |

| Bits  | Perm | Init | Description                                                                               |

|-------|------|------|-------------------------------------------------------------------------------------------|

| 31:16 | RO   | 0    | Current value of watchdog timer.                                                          |

| 15:0  | RW   | 1000 | Number of 1kHz cycles after which the watchdog should expire and initiate a system reset. |

#### E.8 Watchdog Disable: 0xD7

To enable the watchdog, write 0 to this register. To disable the watchdog, write the value 0x0D1SAB1E to this register.

**0xD7:** Watchdog Disable

| Bits | Perm | Init       | Description                                                                            |

|------|------|------------|----------------------------------------------------------------------------------------|

| 31:0 | RW   | 0x0D15AB1E | A value of 0x0D15AB1E written to this register resets and disables the watchdog timer. |

## F ADC Configuration

The device has a 12-bit Analogue to Digital Converter (ADC). It has multiple input pins, and on each positive clock edge on port 11, it samples and converts a value on the next input pin. The data is transmitted to a channel-end that must be set on enabling the ADC input pin.

The ADC is peripheral 2. The control registers are accessed using 32-bit reads and writes (use write\_periph\_32(device, 2, ...) and read\_periph\_32(device, 2, ...) for reads and writes).

| Number | Perm | Description             |

|--------|------|-------------------------|

| 0x00   | RW   | ADC Control input pin 0 |

| 0x04   | RW   | ADC Control input pin 1 |

| 0x08   | RW   | ADC Control input pin 2 |

| 0x0C   | RW   | ADC Control input pin 3 |

| 0x20   | RW   | ADC General Control     |

Figure 45: Summary

#### F.1 ADC Control input pin 0: 0x00

Controls specific to ADC input pin 0.

| Bits | Perm | Init | Description                                                                                                                                                                      |

|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RW   | 0    | The node and channel-end identifier to which data for this ADC input pin should be send to. This is the top 24 bits of the channel-end identifier as allocated on an xCORE Tile. |

| 7:1  | RO   | -    | Reserved                                                                                                                                                                         |

| 0    | RW   | 0    | Set to 1 to enable this input pin on the ADC.                                                                                                                                    |

0x00: ADC Control input pin 0

#### F.2 ADC Control input pin 1: 0x04

Controls specific to ADC input pin 1.

| Bits | Perm | Init | Description                                                                                                                                                                      |

|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RW   | 0    | The node and channel-end identifier to which data for this ADC input pin should be send to. This is the top 24 bits of the channel-end identifier as allocated on an xCORE Tile. |

| 7:1  | RO   | -    | Reserved                                                                                                                                                                         |

| 0    | RW   | 0    | Set to 1 to enable this input pin on the ADC.                                                                                                                                    |

0x04: ADC Control input pin 1

### F.3 ADC Control input pin 2: 0x08

Controls specific to ADC input pin 2.

| Bits | Perm | Init | Description                                                                                                                                                                      |

|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RW   | 0    | The node and channel-end identifier to which data for this ADC input pin should be send to. This is the top 24 bits of the channel-end identifier as allocated on an xCORE Tile. |

| 7:1  | RO   | -    | Reserved                                                                                                                                                                         |

| 0    | RW   | 0    | Set to 1 to enable this input pin on the ADC.                                                                                                                                    |

0x08: ADC Control input pin 2

### F.4 ADC Control input pin 3: 0x0C

Controls specific to ADC input pin 3.

| Bits | Perm | Init | Description                                                                                                                                                                      |

|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RW   | 0    | The node and channel-end identifier to which data for this ADC input pin should be send to. This is the top 24 bits of the channel-end identifier as allocated on an xCORE Tile. |

| 7:1  | RO   | -    | Reserved                                                                                                                                                                         |

| 0    | RW   | 0    | Set to 1 to enable this input pin on the ADC.                                                                                                                                    |

0x0C: ADC Control input pin 3

#### F.5 ADC General Control: 0x20

General ADC control.

0x08: Time to wake-up, most significant 32 bits

| Bits | Perm | Init | Description                                                                                      |

|------|------|------|--------------------------------------------------------------------------------------------------|

| 31:0 | RW   | 0    | Most significant 32 bits of time to wake-up (ignored unless 64-bit timer comparison is enabled). |

### J.4 Power supply states whilst ASLEEP: 0x0C

This register controls the state the power control block should be in when in the ASLEEP state. It also defines the minimum time that the system shall stay in this state. When the minimum time is expired, the next state may be entered if either of the wake conditions (real-time counter or WAKE pin) happens. Note that the minimum number of cycles is counted in according to the currently enabled clock, which may be the slow 31 KHz clock.

| Bits  | Perm | Init | Description                                                                                                                    |  |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------|--|

| 31:21 | RO   | -    | Reserved                                                                                                                       |  |

| 20:16 | RW   | 16   | Log2 number of cycles to stay in this state: 0: 1 clock cycles 1: 2 clock cycles 2: 4 clock cycles 31: 2147483648 clock cycles |  |

| 15    | RO   | -    | Reserved                                                                                                                       |  |

| 14    | RW   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                   |  |

| 13:10 | RO   | -    | Reserved                                                                                                                       |  |

| 9     | RW   | 0    | Sets modulation used by DCDC2:<br>0: PWM modulation (max 475 mA)<br>1: PFM modulation (max 50 mA)                              |  |

| 8     | RW   | 0    | Sets modulation used by DCDC1:<br>0: PWM modulation (max 700 mA)<br>1: PFM modulation (max 50 mA)                              |  |

| 7:6   | RO   | -    | Reserved                                                                                                                       |  |

| 5     | RW   | 0    | Set to 1 to enable VOUT6 (IO supply).                                                                                          |  |

| 4     | RW   | 0    | Set to 1 to enable LDO5 (core PLL supply).                                                                                     |  |

| 3:2   | RO   | -    | Reserved                                                                                                                       |  |

| 1     | RO   | 0    | Set to 1 to enable DCDC2 (analogue supply).                                                                                    |  |

| 0     | RW   | 0    | Set to 1 to enable DCDC1 (core supply).                                                                                        |  |

0x0C: Power supply states whilst ASLEEP

| Bits  | Perm | Init | Description                                                                                                                    |  |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------|--|

| 31:21 | RO   | -    | Reserved                                                                                                                       |  |

| 20:16 | RW   | 16   | Log2 number of cycles to stay in this state: 0: 1 clock cycles 1: 2 clock cycles 2: 4 clock cycles 31: 2147483648 clock cycles |  |

| 15    | RO   | -    | Reserved                                                                                                                       |  |

| 14    | RW   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                   |  |

| 13:10 | RO   | -    | Reserved                                                                                                                       |  |

| 9     | RW   | 0    | Sets modulation used by DCDC2:<br>0: PWM modulation (max 475 mA)<br>1: PFM modulation (max 50 mA)                              |  |

| 8     | RW   | 0    | Sets modulation used by DCDC1:<br>0: PWM modulation (max 700 mA)<br>1: PFM modulation (max 50 mA)                              |  |

| 7:6   | RO   | -    | Reserved                                                                                                                       |  |

| 5     | RW   | 1    | Set to 1 to enable VOUT6 (IO supply).                                                                                          |  |

| 4     | RW   | 1    | Set to 1 to enable LDO5 (core PLL supply).                                                                                     |  |

| 3:2   | RO   | -    | Reserved                                                                                                                       |  |

| 1     | RO   | 1    | Set to 1 to enable DCDC2 (analogue supply).                                                                                    |  |

| 0     | RW   | 1    | Set to 1 to enable DCDC1 (core supply).                                                                                        |  |

0x14: Power supply states whilst WAKING2

## J.7 Power supply states whilst AWAKE: 0x18

This register controls what state the power control block should be in when in the AWAKE state.

| Bits | Perm | Init | Description                                                                   |

|------|------|------|-------------------------------------------------------------------------------|

| 31:3 | RO   | -    | Reserved                                                                      |

| 2:0  | RW   | pin  | The required voltage in 100 mV steps: 0: 0.6V 1: 0.7V 2: 0.8V 6: 1.2V 7: 1.3V |

**0x40:** LDO5 level control

### **K** XMOS USB Interface

XMOS provides a low-level USB interface for connecting the device to a USB transceiver using the UTMI+ Low Pin Interface (ULPI). The ULPI signals must be connected to the pins named in Figure 50. Note also that some ports on the same tile are used internally and are not available for use when the USB driver is active (they are available otherwise).

| Pin            | Signal                  |

|----------------|-------------------------|

| X <i>n</i> D02 |                         |

| XnD03          |                         |

| XnD04          |                         |

| XnD05          | Unavailable<br>when USB |

| XnD06          | active                  |

| XnD07          |                         |

| XnD08          |                         |

| X <i>n</i> D09 |                         |

| Pin            | Signal       |

|----------------|--------------|

| X <i>n</i> D12 | ULPI_STP     |

| X <i>n</i> D13 | ULPI_NXT     |

| XnD14          | ULPI_DATA[0] |

| X <i>n</i> D15 | ULPI_DATA[1] |

| X <i>n</i> D16 | ULPI_DATA[2] |

| XnD17          | ULPI_DATA[3] |

| X <i>n</i> D18 | ULPI_DATA[4] |

| X <i>n</i> D19 | ULPI_DATA[5] |

| X <i>n</i> D20 | ULPI_DATA[6] |

| X <i>n</i> D21 | ULPI_DATA[7] |

| XnD22          | ULPI_DIR     |

| XnD23          | ULPI_CLK     |

| Pin            | Signal                  |

|----------------|-------------------------|

| X <i>n</i> D26 |                         |

| XnD27          |                         |

| XnD28          |                         |

| X <i>n</i> D29 | Unavailable<br>when USB |

| X <i>n</i> D30 | active                  |

| X <i>n</i> D31 |                         |

| XnD32          |                         |

| XnD33          |                         |

| X <i>n</i> D37 |                    |

|----------------|--------------------|

| X <i>n</i> D38 |                    |

| X <i>n</i> D39 | Unavailable        |

| X <i>n</i> D40 | when USB<br>active |

| X <i>n</i> D41 |                    |

| X <i>n</i> D42 |                    |

| X <i>n</i> D43 |                    |

Figure 50: ULPI signals provided by the XMOS USB driver

#### L Device Errata

This section describes minor operational differences from the data sheet and recommended workarounds. As device and documentation issues become known, this section will be updated the document revised.

To guarantee a logic low is seen on the pins DEBUG\_N, MODE[3:0], TMS, TCK and TDI, the driving circuit should present an impedance of less than  $100\,\Omega$  to ground. Usually this is not a problem for CMOS drivers driving single inputs. If one or more of these inputs are placed in parallel, however, additional logic buffers may be required to guarantee correct operation.

For static inputs tied high or low, the relevant input pin should be tied directly to GND or VDDIO.

| N.4  | JTAG, XScope, and debugging                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|

|      | You have decided as to whether you need an XSYS header or not (Section $\mathbf{M}$ )                                                     |

|      | If you included an XSYS header, you connected pin 3 to any MODE2/MODE3 pin that would otherwise be NC (Section M).                        |

|      | If you have not included an XSYS header, you have devised a method to program the SPI-flash or OTP (Section M).                           |

| N.5  | GPIO                                                                                                                                      |

|      | You have not mapped both inputs and outputs to the same multi-bit port.                                                                   |

| N.6  | Multi device designs                                                                                                                      |

| Skip | this section if your design only includes a single XMOS device.                                                                           |

|      | One device is connected to a SPI flash for booting.                                                                                       |

|      | Devices that boot from link have MODE2 grounded and MODE3 NC. These device must have link XLB connected to a device to boot from (see 9). |

|      | If you included an XSYS header, you have included buffers for RST_N, TMS, TCK, MODE2, and MODE3 (Section L).                              |

## **R** Revision History

| Date       | Description                                                                                     |

|------------|-------------------------------------------------------------------------------------------------|

| 2013-04-16 | First release                                                                                   |

| 2013-07-19 | Updated Features list with available ports and links - Section 2                                |

|            | Simplified link bits in Signal Description - Section 4                                          |

|            | New JTAG, xSCOPE and Debugging appendix - Section M                                             |

|            | New Schematics Design Check List - Section N                                                    |

|            | New PCB Layout Design Check List - Section O                                                    |

| 2013-12-09 | Added Industrial Ambient Temperature - Section 17.1                                             |

|            | Annotated V(ACC) parameter - Section 17.2                                                       |

|            | Updated V(IH) parameter - Section 17.9                                                          |

|            | Updated V(OH) parameter - Section 17.5                                                          |

| 2014-03-25 | Added footnotes to DC and Switching Characteristics - Section 17                                |

| 2015-04-14 | Updated Introduction - Section 1; Pin Configuration - Section 3; Signal Description - Section 4 |

Copyright © 2015, All Rights Reserved.

Xmos Ltd. is the owner or licensee of this design, code, or Information (collectively, the "Information") and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. Xmos Ltd. makes no representation that the Information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

X9530, XS1-A6A-64-FB96