Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                           |

|----------------------------|-------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                    |

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 140                                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192К х 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 176-LQFP                                                                                  |

| Supplier Device Package    | 176-LQFP (24x24)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f417iet6                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Timer<br>type | Timer               | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complemen-<br>tary output | Max<br>interface<br>clock<br>(MHz) | Max<br>timer<br>clock<br>(MHz) |

|---------------|---------------------|-----------------------|-------------------------|---------------------------------------|------------------------------|---------------------------------|---------------------------|------------------------------------|--------------------------------|

|               | TIM2,<br>TIM5       | 32-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                        | 42                                 | 84                             |

|               | TIM3,<br>TIM4       | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                        | 42                                 | 84                             |

| General       | TIM9                | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 2                               | No                        | 84                                 | 168                            |

| purpose       | TIM10<br>,<br>TIM11 | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 1                               | No                        | 84                                 | 168                            |

|               | TIM12               | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 2                               | No                        | 42                                 | 84                             |

|               | TIM13<br>,<br>TIM14 | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 1                               | No                        | 42                                 | 84                             |

| Basic         | TIM6,<br>TIM7       | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                        | 42                                 | 84                             |

Table 4. Timer feature comparison (continued)

# Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 and TIM8 support independent DMA request generation.

| USART<br>name | Standard<br>features | Modem<br>(RTS/<br>CTS) | LIN | SPI<br>master | irDA Smartcard |   | Max. baud rate<br>in Mbit/s<br>(oversampling<br>by 16) | Max. baud rate<br>in Mbit/s<br>(oversampling<br>by 8) | APB<br>mapping           |

|---------------|----------------------|------------------------|-----|---------------|----------------|---|--------------------------------------------------------|-------------------------------------------------------|--------------------------|

| USART1        | х                    | х                      | х   | х             | х              | х | 5.25                                                   | 10.5                                                  | APB2<br>(max.<br>84 MHz) |

| USART2        | х                    | х                      | х   | х             | х              | х | 2.62                                                   | 5.25                                                  | APB1<br>(max.<br>42 MHz) |

| USART3        | х                    | х                      | х   | х             | х              | х | 2.62                                                   | 5.25                                                  | APB1<br>(max.<br>42 MHz) |

| UART4         | х                    | -                      | х   | -             | х              | - | 2.62                                                   | 5.25                                                  | APB1<br>(max.<br>42 MHz) |

| UART5         | х                    | -                      | x   | -             | х              | - | 2.62                                                   | 5.25                                                  | APB1<br>(max.<br>42 MHz) |

| USART6        | х                    | х                      | х   | х             | х              | х | 5.25                                                   | 10.5                                                  | APB2<br>(max.<br>84 MHz) |

Table 5. USART feature comparison

# 2.2.24 Serial peripheral interface (SPI)

The STM32F41xxx feature up to three SPIs in slave and master modes in full-duplex and simplex communication modes. SPI1 can communicate at up to 42 Mbits/s, SPI2 and SPI3 can communicate at up to 21 Mbit/s. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes. All SPIs can be served by the DMA controller.

The SPI interface can be configured to operate in TI mode for communications in master mode and slave mode.

# 2.2.25 Inter-integrated sound (I<sup>2</sup>S)

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI2 and SPI3) are available. They can be operated in master or slave mode, in full duplex and half-duplex communication modes, and can be configured to operate with a 16-/32-bit resolution as an input or output channel. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All  $I^2Sx$  can be served by the DMA controller.

# 2.2.26 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S application. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an  $I^2S$  sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the  $I^2S$  flow with an external PLL (or Codec output).

# 2.2.27 Secure digital input/output interface (SDIO)

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 48 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

# 2.2.28 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

Peripheral available only on the STM32F417xx devices.

The STM32F417xx devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard mediumindependent interface (MII) or a reduced medium-independent interface (RMII). The STM32F417xx requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). the PHY is connected to the STM32F417xx MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) from the STM32F417xx.

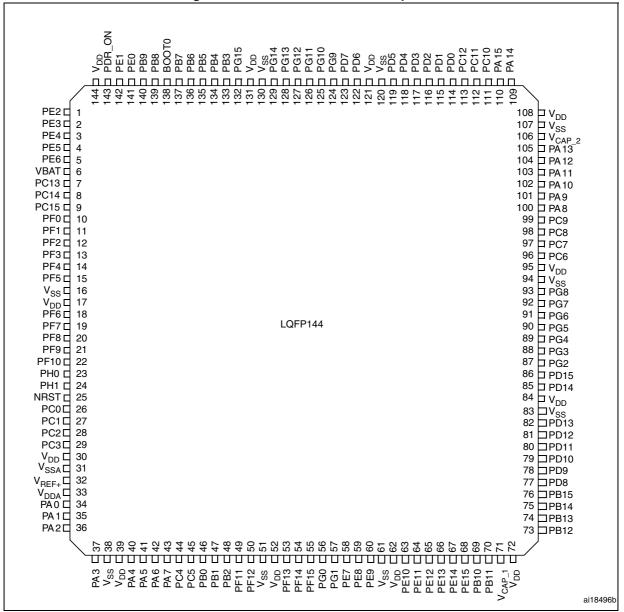

#### Figure 14. STM32F41xxx LQFP144 pinout

1. The above figure shows the package top view.

|   | 1     | 2    | 3    | 4              | 5   | 6      | 7    | 8    | 9    | 10     | 11   | 12   | 13     | 14   | 15       |

|---|-------|------|------|----------------|-----|--------|------|------|------|--------|------|------|--------|------|----------|

| А | PE3   | PE2  | PE1  | PE0            | PB8 | PB5    | PG14 | PG13 | PB4  | PB3    | PD7  | PC12 | PA15   | PA14 | PA13     |

| В | PE4   | PE5  | PE6  | PB9            | PB7 | PB6    | PG15 | PG12 | PG11 | PG10   | PD6  | PD0  | PC11   | PC10 | PA12     |

| С | VBAT  | PI7  | PI6  | PI5            | VDD | PDR_ON | VDD  | VDD  | VDD  | PG9    | PD5  | PD1  | PI3    | Pl2  | PA11     |

| D | PC13  | PI8  | PI9  | Pl4            | VSS | BOOT0  | VSS  | VSS  | VSS  | PD4    | PD3  | PD2  | PH15   | PI1  | PA10     |

| E | PC14  | PF0  | PI10 | PI11           |     |        |      |      |      |        |      | PH13 | PH14   | P10  | PA9      |

| F | PC15  | VSS  | VDD  | PH2            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | VSS  | VCAP_2 | PC9  | PA8      |

| G | PH0   | VSS  | VDD  | PH3            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | VSS  | VDD    | PC8  | PC7      |

| Н | PH1   | PF2  | PF1  | PH4            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | VSS  | VDD    | PG8  | PC6      |

| J | NRST  | PF3  | PF4  | PH5            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | VDD  | VDD    | PG7  | PG6      |

| к | PF7   | PF6  | PF5  | VDD            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | PH12 | PG5    | PG4  | PG3      |

| L | PF10  | PF9  | PF8  | BYPASS_<br>REG |     |        |      |      |      |        | •    | PH11 | PH10   | PD15 | PG2      |

| М | VSSA  | PC0  | PC1  | PC2            | PC3 | PB2    | PG1  | VSS  | VSS  | VCAP_1 | PH6  | PH8  | PH9    | PD14 | PD13     |

| Ν | VREF- | PA 1 | PA0  | PA4            | PC4 | PF13   | PG0  | VDD  | VDD  | VDD    | PE13 | PH7  | PD12   | PD11 | PD10     |

| Ρ | VREF+ | PA2  | PA 6 | PA5            | PC5 | PF12   | PF15 | PE8  | PE9  | PE11   | PE14 | PB12 | PB13   | PD9  | PD8      |

| R | VDDA  | PA3  | PA7  | PB1            | PB0 | PF11   | PF14 | PE7  | PE10 | PE12   | PE15 | PB10 | PB11   | PB14 | PB15     |

|   |       |      |      |                |     |        |      |      |      |        |      |      |        |      | ai18497b |

## Figure 16. STM32F41xxx UFBGA176 ballout

1. This figure shows the package top view.

|        | I       | Pin r   | numb    | er       |         |                                                      |          |                 |       |                                                                                                            |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                        | Additional<br>functions |

| 29     | H4      | 47      | 69      | R12      | 79      | PB10                                                 | I/O      | FT              | -     | SPI2_SCK / I2S2_CK /<br>I2C2_SCL/ USART3_TX /<br>OTG_HS_ULPI_D3 /<br>ETH_MII_RX_ER /<br>TIM2_CH3/ EVENTOUT | _                       |

| 30     | J4      | 48      | 70      | R13      | 80      | PB11                                                 | I/O      | FT              | -     | I2C2_SDA/USART3_RX/<br>OTG_HS_ULPI_D4 /<br>ETH_RMII_TX_EN/<br>ETH_MII_TX_EN /<br>TIM2_CH4/ EVENTOUT        | -                       |

| 31     | F4      | 49      | 71      | M10      | 81      | V <sub>CAP_1</sub>                                   | S        |                 | -     | -                                                                                                          | -                       |

| 32     | -       | 50      | 72      | N10      | 82      | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                                          | -                       |

| -      | -       | -       | -       | M11      | 83      | PH6                                                  | I/O      | FT              | -     | I2C2_SMBA / TIM12_CH1 /<br>ETH_MII_RXD2/<br>EVENTOUT                                                       | -                       |

| -      | -       | -       | -       | N12      | 84      | PH7                                                  | I/O      | FT              | -     | I2C3_SCL /<br>ETH_MII_RXD3/<br>EVENTOUT                                                                    | -                       |

| -      | -       | -       | -       | M12      | 85      | PH8                                                  | I/O      | FT              | -     | I2C3_SDA /<br>DCMI_HSYNC/<br>EVENTOUT                                                                      | -                       |

| -      | -       | -       | -       | M13      | 86      | PH9                                                  | I/O      | FT              | -     | I2C3_SMBA / TIM12_CH2/<br>DCMI_D0/ EVENTOUT                                                                | -                       |

| -      | -       | -       | -       | L13      | 87      | PH10                                                 | I/O      | FT              | -     | TIM5_CH1 / DCMI_D1/<br>EVENTOUT                                                                            | -                       |

| -      | -       | -       | -       | L12      | 88      | PH11                                                 | I/O      | FT              | -     | TIM5_CH2 / DCMI_D2/<br>EVENTOUT                                                                            | -                       |

| -      | -       | -       | -       | K12      | 89      | PH12                                                 | I/O      | FT              | -     | TIM5_CH3 / DCMI_D3/<br>EVENTOUT                                                                            | -                       |

| -      | -       | -       | -       | H12      | 90      | V <sub>SS</sub>                                      | S        | -               | -     | -                                                                                                          | -                       |

| -      | -       | -       | -       | J12      | 91      | $V_{DD}$                                             | S        | -               | -     | -                                                                                                          | -                       |

Table 7. STM32F41xxx pin and ball definitions (continued)

|        | I       | Pin r   | numb    |          |         |                                                      | - <b>P</b> |                 |       | definitions (continued)                                                                                                                                 |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|------------|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type   | I / O structure | Notes | Alternate functions                                                                                                                                     | Additional<br>functions |

| 33     | J3      | 51      | 73      | P12      | 92      | PB12                                                 | I/O        | FT              | -     | SPI2_NSS / I2S2_WS /<br>I2C2_SMBA/<br>USART3_CK/ TIM1_BKIN /<br>CAN2_RX /<br>OTG_HS_ULPI_D5/<br>ETH_RMII_TXD0 /<br>ETH_MII_TXD0/<br>OTG_HS_ID/ EVENTOUT | -                       |

| 34     | J1      | 52      | 74      | P13      | 93      | PB13                                                 | I/O        | FT              | -     | SPI2_SCK / I2S2_CK /<br>USART3_CTS/<br>TIM1_CH1N /CAN2_TX /<br>OTG_HS_ULPI_D6 /<br>ETH_RMII_TXD1 /<br>ETH_MII_TXD1/<br>EVENTOUT                         | OTG_HS_VBUS             |

| 35     | J2      | 53      | 75      | R14      | 94      | PB14                                                 | I/O        | FT              | -     | SPI2_MISO/ TIM1_CH2N /<br>TIM12_CH1 /<br>OTG_HS_DM/<br>USART3_RTS /<br>TIM8_CH2N/I2S2ext_SD/<br>EVENTOUT                                                | -                       |

| 36     | H1      | 54      | 76      | R15      | 95      | PB15                                                 | I/O        | FT              | -     | SPI2_MOSI / I2S2_SD/<br>TIM1_CH3N / TIM8_CH3N<br>/ TIM12_CH2 /<br>OTG_HS_DP/ EVENTOUT                                                                   | RTC_REFIN               |

| -      | H2      | 55      | 77      | P15      | 96      | PD8                                                  | I/O        | FT              | -     | FSMC_D13 / USART3_TX/<br>EVENTOUT                                                                                                                       | -                       |

| -      | H3      | 56      | 78      | P14      | 97      | PD9                                                  | I/O        | FT              | -     | FSMC_D14 / USART3_RX/<br>EVENTOUT                                                                                                                       | -                       |

| -      | G3      | 57      | 79      | N15      | 98      | PD10                                                 | I/O        | FT              | -     | FSMC_D15/USART3_CK/<br>EVENTOUT                                                                                                                         | -                       |

| -      | G1      | 58      | 80      | N14      | 99      | PD11                                                 | I/O        | FT              | -     | FSMC_CLE /<br>FSMC_A16/USART3_CTS/<br>EVENTOUT                                                                                                          | -                       |

| -      | G2      | 59      | 81      | N13      | 100     | PD12                                                 | I/O        | FT              | -     | FSMC_ALE/<br>FSMC_A17/TIM4_CH1 /<br>USART3_RTS/<br>EVENTOUT                                                                                             | -                       |

|        | I       | Pin r   | numb    |          |         |                                                      |          |                 |       | definitions (continued)                                                                                                         |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                                             | Additional<br>functions |

| 55     | B6      | 89      | 133     | A10      | 161     | PB3<br>(JTDO/<br>TRACESWO)                           | I/O      | FT              | -     | JTDO/ TRACESWO/<br>SPI3_SCK / I2S3_CK /<br>TIM2_CH2 / SPI1_SCK/<br>EVENTOUT                                                     | -                       |

| 56     | A6      | 90      | 134     | A9       | 162     | PB4<br>(NJTRST)                                      | I/O      | FT              | -     | NJTRST/ SPI3_MISO /<br>TIM3_CH1 / SPI1_MISO /<br>I2S3ext_SD/ EVENTOUT                                                           | -                       |

| 57     | D7      | 91      | 135     | A6       | 163     | PB5                                                  | I/O      | FT              | -     | I2C1_SMBA/ CAN2_RX /<br>OTG_HS_ULPI_D7 /<br>ETH_PPS_OUT/TIM3_CH2<br>/ SPI1_MOSI/ SPI3_MOSI /<br>DCMI_D10 / I2S3_SD/<br>EVENTOUT | -                       |

| 58     | C7      | 92      | 136     | В6       | 164     | PB6                                                  | I/O      | FT              | -     | I2C1_SCL/ TIM4_CH1 /<br>CAN2_TX /<br>DCMI_D5/USART1_TX/<br>EVENTOUT                                                             | -                       |

| 59     | В7      | 93      | 137     | В5       | 165     | PB7                                                  | I/O      | FT              | -     | I2C1_SDA / FSMC_NL /<br>DCMI_VSYNC /<br>USART1_RX/ TIM4_CH2/<br>EVENTOUT                                                        | -                       |

| 60     | A7      | 94      | 138     | D6       | 166     | BOOT0                                                | Ι        | В               | -     | -                                                                                                                               | V <sub>PP</sub>         |

| 61     | D8      | 95      | 139     | A5       | 167     | PB8                                                  | I/O      | FT              | -     | TIM4_CH3/SDIO_D4/<br>TIM10_CH1 / DCMI_D6 /<br>ETH_MII_TXD3 /<br>I2C1_SCL/ CAN1_RX/<br>EVENTOUT                                  | -                       |

| 62     | C8      | 96      | 140     | B4       | 168     | PB9                                                  | I/O      | FT              | -     | SPI2_NSS/ I2S2_WS /<br>TIM4_CH4/ TIM11_CH1/<br>SDIO_D5 / DCMI_D7 /<br>I2C1_SDA / CAN1_TX/<br>EVENTOUT                           | -                       |

| -      | -       | 97      | 141     | A4       | 169     | PE0                                                  | I/O      | FT              | -     | TIM4_ETR / FSMC_NBL0 /<br>DCMI_D2/ EVENTOUT                                                                                     | -                       |

| -      | -       | 98      | 142     | A3       | 170     | PE1                                                  | I/O      | FT              | -     | FSMC_NBL1 / DCMI_D3/<br>EVENTOUT                                                                                                | -                       |

| 63     | -       | 99      | -       | D5       | -       | V <sub>SS</sub>                                      | S        | -               | -     | -                                                                                                                               | -                       |

66/206

DocID022063 Rev 8

|        | Table 9. Alternate function mapping (continued) |                       |           |          |                  |               |                                |                      |                        |                    |                           |                    |                                      |                      |                |      |          |

|--------|-------------------------------------------------|-----------------------|-----------|----------|------------------|---------------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|--------------------|--------------------------------------|----------------------|----------------|------|----------|

|        |                                                 | AF0                   | AF1       | AF2      | AF3              | AF4           | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10               | AF11                                 | AF12                 | AF13           |      |          |

| P      | ort                                             | SYS                   | TIM1/2    | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3      | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS  | ЕТН                                  | FSMC/SDIO<br>/OTG_FS | DCMI           | AF14 | AF15     |

|        | PB0                                             | -                     | TIM1_CH2N | TIM3_CH3 | TIM8_CH2N        | -             | -                              | -                    | -                      | -                  | -                         | OTG_HS_ULPI_<br>D1 | ETH _MII_RXD2                        | -                    | -              | -    | EVENTOUT |

|        | PB1                                             | -                     | TIM1_CH3N | TIM3_CH4 | TIM8_CH3N        |               | -                              | -                    | -                      | -                  | -                         | OTG_HS_ULPI_<br>D2 | ETH _MII_RXD3                        | -                    | -              | -    | EVENTOUT |

|        | PB2                                             | -                     | -         | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                  | -                                    | -                    | -              | -    | EVENTOUT |

|        | PB3                                             | JTDO/<br>TRACES<br>WO | TIM2_CH2  | -        | -                | -             | SPI1_SCK                       | SPI3_SCK<br>I2S3_CK  | -                      | -                  | -                         | -                  | -                                    | -                    | -              | -    | EVENTOUT |

|        | PB4                                             | NJTRST                | -         | TIM3_CH1 |                  | -             | SPI1_MISO                      | SPI3_MISO            | I2S3ext_SD             | -                  | -                         | -                  | -                                    | -                    | -              | -    | EVENTOUT |

|        | PB5                                             | -                     | -         | TIM3_CH2 |                  | I2C1_SMB<br>A | SPI1_MOSI                      | SPI3_MOSI<br>I2S3_SD |                        | -                  | CAN2_RX                   | OTG_HS_ULPI_<br>D7 | ETH_PPS_OUT                          | -                    | DCMI_D10       | -    | EVENTOUT |

|        | PB6                                             | -                     | -         | TIM4_CH1 |                  | I2C1_SCL      | -                              | -                    | USART1_TX              | -                  | CAN2_TX                   | -                  | -                                    | -                    | DCMI_D5        | -    | EVENTOUT |

|        | PB7                                             | -                     | -         | TIM4_CH2 |                  | I2C1_SDA      | -                              | -                    | USART1_RX              | -                  | -                         | -                  | -                                    | FSMC_NL              | DCMI_VSYN<br>C | -    | EVENTOUT |

| Port B | PB8                                             | -                     | -         | TIM4_CH3 | TIM10_CH1        | I2C1_SCL      | -                              | -                    | -                      | -                  | CAN1_RX                   | -                  | ETH _MII_TXD3                        | SDIO_D4              | DCMI_D6        | -    | EVENTOUT |

|        | PB9                                             | -                     | -         | TIM4_CH4 | TIM11_CH1        | I2C1_SDA      | SPI2_NSS<br>I2S2_WS            | -                    | -                      | -                  | CAN1_TX                   | -                  | -                                    | SDIO_D5              | DCMI_D7        | -    | EVENTOUT |

|        | PB10                                            | -                     | TIM2_CH3  | -        | -                | I2C2_SCL      | SPI2_SCK<br>I2S2_CK            | -                    | USART3_TX              | -                  | -                         | OTG_HS_ULPI_<br>D3 | ETH_MII_RX_ER                        | -                    | -              | -    | EVENTOUT |

|        | PB11                                            | -                     | TIM2_CH4  | -        | -                | I2C2_SDA      | -                              | -                    | USART3_RX              | -                  | -                         | OTG_HS_ULPI_<br>D4 | ETH _MII_TX_EN<br>ETH<br>_RMII_TX_EN | -                    | -              | -    | EVENTOUT |

|        | PB12                                            | -                     | TIM1_BKIN | -        | -                | I2C2_<br>SMBA | SPI2_NSS<br>I2S2_WS            | -                    | USART3_CK              | -                  | CAN2_RX                   | OTG_HS_ULPI_<br>D5 | ETH _MII_TXD0<br>ETH _RMII_TXD0      | OTG_HS_ID            | -              | -    | EVENTOUT |

|        | PB13                                            | -                     | TIM1_CH1N | -        | -                | -             | SPI2_SCK<br>I2S2_CK            | -                    | USART3_CTS             | -                  | CAN2_TX                   | OTG_HS_ULPI_<br>D6 | ETH _MII_TXD1<br>ETH _RMII_TXD1      | -                    | -              | -    | EVENTOUT |

|        | PB14                                            | -                     | TIM1_CH2N | -        | TIM8_CH2N        | -             | SPI2_MISO                      | I2S2ext_SD           | USART3_RTS             | -                  | TIM12_CH1                 | -                  | -                                    | OTG_HS_DM            | -              | -    | EVENTOUT |

|        | PB15                                            | RTC_<br>REFIN         | TIM1_CH3N | -        | TIM8_CH3N        | -             | SPI2_MOSI<br>I2S2_SD           | -                    | -                      | -                  | TIM12_CH2                 | -                  | -                                    | OTG_HS_DP            | -              | -    | EVENTOUT |

# Pinouts and pin description

70/206

DocID022063 Rev 8

|        |      |     |        |          |                  |               |                                | I                    |                        |                    | -                         |                   |      |                      |          |      |          |

|--------|------|-----|--------|----------|------------------|---------------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|-------------------|------|----------------------|----------|------|----------|

|        |      | AF0 | AF1    | AF2      | AF3              | AF4           | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10              | AF11 | AF12                 | AF13     |      |          |

| Po     | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3      | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS | ЕТН  | FSMC/SDIO<br>/OTG_FS | DCMI     | AF14 | AF15     |

|        | PF0  | -   | -      | -        | -                | I2C2_SDA      | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A0              | -        | -    | EVENTOUT |

|        | PF1  | -   | -      | -        | -                | I2C2_SCL      | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A1              | -        | -    | EVENTOUT |

|        | PF2  | -   | -      | -        | -                | I2C2_<br>SMBA | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A2              | -        | -    | EVENTOUT |

|        | PF3  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A3              | -        | -    | EVENTOUT |

|        | PF4  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A4              | -        | -    | EVENTOUT |

|        | PF5  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A5              | -        | -    | EVENTOUT |

|        | PF6  | -   | -      | -        | TIM10_CH1        | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_NIORD           | -        | -    | EVENTOUT |

| Port F | PF7  | -   | -      | -        | TIM11_CH1        | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_NREG            | -        | -    | EVENTOUT |

| Ροπι   | PF8  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | TIM13_CH1                 | -                 | -    | FSMC_<br>NIOWR       | -        | -    | EVENTOUT |

|        | PF9  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | TIM14_CH1                 | -                 | -    | FSMC_CD              | -        | -    | EVENTOUT |

|        | PF10 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_INTR            | -        | -    | EVENTOUT |

|        | PF11 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    |                      | DCMI_D12 | -    | EVENTOUT |

|        | PF12 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A6              | -        | -    | EVENTOUT |

|        | PF13 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A7              | -        | -    | EVENTOUT |

|        | PF14 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A8              | -        | -    | EVENTOUT |

|        | PF15 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A9              | -        | -    | EVENTOUT |

Table 9. Alternate function mapping (continued)

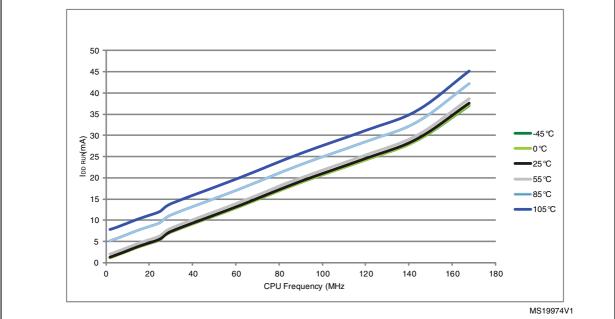

Figure 24. Typical current consumption versus temperature, Run mode, code with data processing running from Flash (ART accelerator ON) or RAM, and peripherals OFF

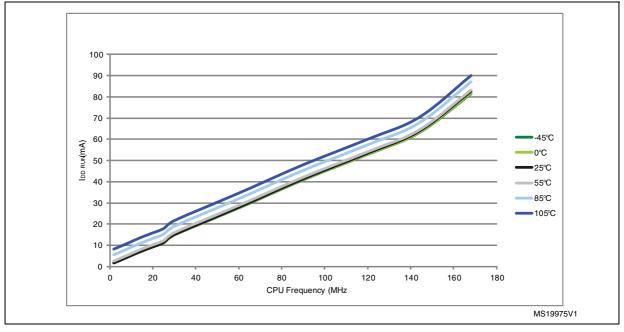

Figure 25. Typical current consumption versus temperature, Run mode, code with data processing running from Flash (ART accelerator ON) or RAM, and peripherals ON

## Low-speed external user clock generated from an external source

The characteristics given in *Table 31* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                     | Parameter                                              | Conditions                                     | Min                | Тур    | Max                | Unit |

|--------------------------------------------|--------------------------------------------------------|------------------------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                                                | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                                                | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   | -                                              | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                                | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                                                | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              | -                                              | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             | -                                              | 30                 | -      | 70                 | %    |

| ال                                         | OSC32_IN Input leakage current                         | $V_{SS} \!\leq\! \! V_{IN} \!\leq\! \! V_{DD}$ | -                  | -      | ±1                 | μA   |

| Table 31. Low-speed external user clock characteristic | s        |

|--------------------------------------------------------|----------|

|                                                        | <u> </u> |

1. Guaranteed by design.

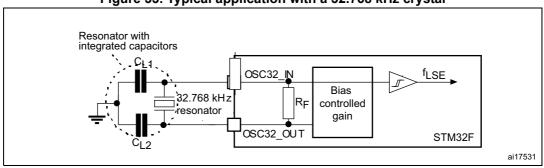

Figure 33. Typical application with a 32.768 kHz crystal

# 5.3.9 Internal clock source characteristics

The parameters given in *Table 34* and *Table 35* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                             | Conditions                           | Min | Тур | Max | Unit |  |  |

|-------------------------------------|---------------------------------------|--------------------------------------|-----|-----|-----|------|--|--|

| f <sub>HSI</sub>                    | Frequency                             | -                                    | -   | 16  | -   | MHz  |  |  |

|                                     | HSI user trimming step <sup>(2)</sup> | -                                    | -   | -   | 1   | %    |  |  |

| ACC <sub>HSI</sub>                  | Accuracy of the HSI oscillator        | $T_A = -40$ to 105 °C <sup>(3)</sup> | -8  | -   | 4.5 | %    |  |  |

|                                     |                                       | $T_A = -10$ to 85 °C <sup>(3)</sup>  | -4  | -   | 4   | %    |  |  |

|                                     |                                       | $T_A = 25 \ ^{\circ}C^{(4)}$         | -1  | -   | 1   | %    |  |  |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time           | -                                    | -   | 2.2 | 4   | μs   |  |  |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power<br>consumption   | -                                    | -   | 60  | 80  | μA   |  |  |

Table 34. HSI oscillator characteristics <sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization.

4. Factory calibrated, parts not soldered.

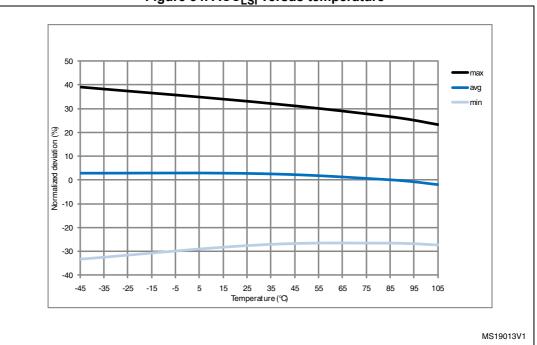

## Low-speed internal (LSI) RC oscillator

| Table 35. LSI oscillator characteristics (1 |

|---------------------------------------------|

|---------------------------------------------|

| Symbol                              | Parameter                        | Min | Тур | Мах | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by characterization.

3. Guaranteed by design.

Figure 34. ACC<sub>LSI</sub> versus temperature

# 5.3.10 PLL characteristics

The parameters given in *Table 36* and *Table 37* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                 | Parameter                             | Conditions         | Min                 | Тур | Max  | Unit |

|------------------------|---------------------------------------|--------------------|---------------------|-----|------|------|

| f <sub>PLL_IN</sub>    | PLL input clock <sup>(1)</sup>        | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 | MHz  |

| f <sub>PLL_OUT</sub>   | PLL multiplier output clock           | -                  | 24                  | -   | 168  | MHz  |

| f <sub>PLL48_OUT</sub> | 48 MHz PLL multiplier output<br>clock | -                  | -                   | 48  | 75   | MHz  |

| f <sub>VCO_OUT</sub>   | PLL VCO output                        | -                  | 100                 | -   | 432  | MHz  |

| t                      | PLL lock time                         | VCO freq = 100 MHz | 75                  | -   | 200  | μs   |

| t <sub>LOCK</sub>      |                                       | VCO freq = 432 MHz | 100                 | -   | 300  | μο   |

Table 36. Main PLL characteristics

| Symbol                   | Parameter                                       | Conditions                               | Min          | Тур | Max          | Unit |  |  |

|--------------------------|-------------------------------------------------|------------------------------------------|--------------|-----|--------------|------|--|--|

| I <sub>DD(PLLI2S)</sub>  | ) PLLI2S power consumption on V <sub>DD</sub>   | VCO freq = 100 MHz<br>VCO freq = 432 MHz | 0.15<br>0.45 | -   | 0.40<br>0.75 | mA   |  |  |

| I <sub>DDA(PLLI2S)</sub> | +) PLLI2S power consumption on V <sub>DDA</sub> | VCO freq = 100 MHz<br>VCO freq = 432 MHz | 0.30<br>0.55 | -   | 0.40<br>0.85 | mA   |  |  |

#### Table 37. PLLI2S (audio PLL) characteristics (continued)

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization.

# 5.3.11 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 44: EMI characteristics*). It is available only on the main PLL.

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|-----------------------|------|-----|--------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                 | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                  | %    |

| MODEPER * INCSTEP |                       | -    | -   | 2 <sup>15</sup> –1 | -    |

# Table 38. SSCG parameters constraint

1. Guaranteed by design.

Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

$MODEPER = round[f_{PLL \ IN}/ \ (4 \times f_{Mod})]$

$f_{\text{PLL}\ \text{IN}}$  and  $f_{\text{Mod}}$  must be expressed in Hz.

As an example:

If  $f_{PLL_IN} = 1$  MHz, and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round[ $10^{6}$ / (4 × 10<sup>3</sup>)] = 250

### Equation 2

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[( $(2^{15}-1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$ ]

f<sub>VCO OUT</sub> must be expressed in MHz.

| Symbol                          | Parameter                                               | Conditions                                    | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|---------------------------------|---------------------------------------------------------|-----------------------------------------------|--------------------|-----|--------------------|------|

| t <sub>prog</sub>               | Double word programming                                 |                                               | -                  | 16  | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>          | Sector (16 KB) erase time                               | Sector (16 KB) erase time $T_A = 0$ to +40 °C |                    | 230 | -                  |      |

| t <sub>ERASE64KB</sub>          | Sector (64 KB) erase time                               | V <sub>DD</sub> = 3.3 V                       | -                  | 490 | -                  | ms   |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                              | V <sub>PP</sub> = 8.5 V                       | -                  | 875 | -                  |      |

| t <sub>ME</sub>                 | Mass erase time                                         |                                               | -                  | 6.9 | -                  | s    |

| V <sub>prog</sub>               | Programming voltage                                     | -                                             | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                           | -                                             | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin            | -                                             | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which V <sub>PP</sub> is applied | -                                             | -                  | -   | 1                  | hour |

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol           | Parameter      | Conditions                                                                              | Value<br>Min <sup>(1)</sup> | Unit    |

|------------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------|---------|

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                          | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                          |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                          | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                          |         |

#### Table 42. Flash memory endurance and data retention

1. Guaranteed by characterization.

2. Cycling performed over the whole temperature range.

# 5.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

DocID022063 Rev 8

| Symbol                           | Parameter                                                                          | Conditions                                           | Min                 | Тур       | Max              | Unit               |

|----------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------|---------------------|-----------|------------------|--------------------|

| t <sub>lat</sub> <sup>(4)</sup>  | Injection trigger conversion                                                       | f <sub>ADC</sub> = 30 MHz                            | -                   | -         | 0.100            | μs                 |

| <sup>l</sup> lat <sup>1</sup>    | latency                                                                            |                                                      | -                   | -         | 3 <sup>(7)</sup> | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (4)            | Regular trigger conversion                                                         | f <sub>ADC</sub> = 30 MHz                            | -                   | -         | 0.067            | μs                 |

| 'latr'                           | latency                                                                            | atency                                               | -                   | -         | 2 <sup>(7)</sup> | 1/f <sub>ADC</sub> |

| ts <sup>(4)</sup>                | Sampling time                                                                      | f <sub>ADC</sub> = 30 MHz                            | 0.100               | -         | 16               | μs                 |

| 0                                |                                                                                    | -                                                    | 3                   | -         | 480              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(4)</sup> | Power-up time                                                                      | -                                                    | -                   | 2         | 3                | μs                 |

|                                  |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution       | 0.50                | -         | 16.40            | μs                 |

| t <sub>CONV</sub> <sup>(4)</sup> | V <sup>(4)</sup> Total conversion time (including sampling time)                   | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution       | 0.43                | -         | 16.34            | μs                 |

|                                  |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution        | 0.37                | -         | 16.27            | μs                 |

|                                  |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution        | 0.30                | -         | 16.20            | μs                 |

|                                  |                                                                                    | 9 to 492 (t <sub>S</sub> for sampling approximation) | +n-bit resolution f | or succes | ssive            | 1/f <sub>ADC</sub> |

|                                  |                                                                                    | 12-bit resolution<br>Single ADC                      | -                   | -         | 2                | Msps               |

| f <sub>S</sub> <sup>(4)</sup>    | Sampling rate<br>(f <sub>ADC</sub> = 30 MHz, and<br>t <sub>S</sub> = 3 ADC cycles) | 12-bit resolution<br>Interleave Dual ADC<br>mode     | -                   | -         | 3.75             | Msps               |

|                                  |                                                                                    | 12-bit resolution<br>Interleave Triple ADC<br>mode   | -                   | -         | 6                | Msps               |

| I <sub>VREF+</sub> (4)           | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode               | -                                                    | -                   | 300       | 500              | μA                 |

| I <sub>VDDA</sub> <sup>(4)</sup> | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode               | -                                                    | -                   | 1.6       | 1.8              | mA                 |

#### Table 67. ADC characteristics (continued)

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to *Section : Internal reset OFF*).

2. It is recommended to maintain the voltage difference between V\_{REF+} and V\_{DDA} below 1.8 V.

3.  $V_{DDA} - V_{REF+} < 1.2 V.$

4. Guaranteed by characterization.

5.  $V_{REF+}$  is internally connected to  $V_{DDA}$  and  $V_{REF-}$  is internally connected to  $V_{SSA}$ .

6.  $R_{ADC}$  maximum value is given for V<sub>DD</sub>=1.8 V, and minimum value for V<sub>DD</sub>=3.3 V.

7. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in *Table* 67.

| Symbol                                             | Parameter                    | Min | Max | Unit |  |

|----------------------------------------------------|------------------------------|-----|-----|------|--|

| t <sub>su(DATA)</sub>                              | Data input setup time        | 2.5 | -   |      |  |

| t <sub>h(DATA)</sub>                               | Data hold time               | 1   | -   |      |  |

| t <sub>su(HSYNC)</sub> ,<br>t <sub>su(VSYNC)</sub> | HSYNC/VSYNC input setup time | 2   | -   | ns   |  |

| t <sub>h(HSYNC)</sub> ,<br>t <sub>h(VSYNC)</sub>   | HSYNC/VSYNC input hold time  | 0.5 | -   |      |  |

Table 87. DCMI characteristics<sup>(1)</sup> (continued)

1. Guaranteed by characterization.

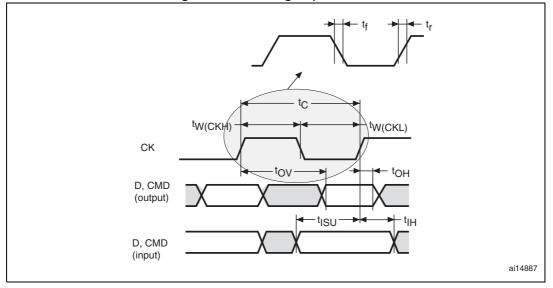

# 5.3.28 SD/SDIO MMC card host interface (SDIO) characteristics

Unless otherwise specified, the parameters given in *Table 88* are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14* with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 5.3.16: I/O port characteristics for more details on the input/output characteristics.

#### Figure 73. SDIO high-speed mode

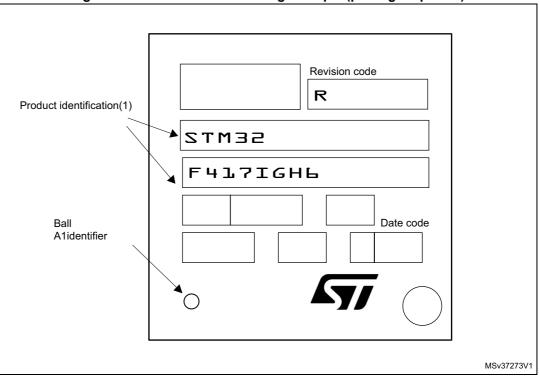

#### **Device marking for UFBGA176+25**

The following figure gives an example of topside marking and ball A 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

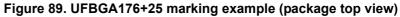

#### **Device marking for LQFP176**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.