Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------|

| Product Status            | Active                                                                                    |

| Core Processor            | ARM® Cortex®-M4                                                                           |

| Core Size                 | 32-Bit Single-Core                                                                        |

| Speed                     | 168MHz                                                                                    |

| Connectivity              | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals               | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O             | 140                                                                                       |

| Program Memory Size       | 1MB (1M x 8)                                                                              |

| Program Memory Type       | FLASH                                                                                     |

| EEPROM Size               | -                                                                                         |

| AAM Size                  | 192K x 8                                                                                  |

| oltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| ata Converters            | A/D 24x12b; D/A 2x12b                                                                     |

| Oscillator Type           | Internal                                                                                  |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| ounting Type              | Surface Mount                                                                             |

| ackage / Case             | 201-UFBGA                                                                                 |

| Supplier Device Package   | 176+25UFBGA (10x10)                                                                       |

| Purchase URL              | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f417igh6                     |

|            | recommended footprint                                                     | 179 |

|------------|---------------------------------------------------------------------------|-----|

| Figure 86. | LQFP144 marking example (package top view)                                |     |

| Figure 87. | UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch             |     |

| J          | ball grid array package outline                                           | 181 |

| Figure 88. | UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch       |     |

| J          | ball grid array recommended footprint                                     | 182 |

| Figure 89. | UFBGA176+25 marking example (package top view)                            |     |

| Figure 90. | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline       | 184 |

| Figure 91. | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint | 186 |

| Figure 92. | LQFP176 marking example (package top view)                                | 187 |

| Figure 93. | USB controller configured as peripheral-only and used                     |     |

|            | in Full speed mode                                                        | 190 |

| Figure 94. | USB controller configured as host-only and used in full speed mode        | 190 |

| Figure 95. | USB controller configured in dual mode and used in full speed mode        | 191 |

| Figure 96. | USB controller configured as peripheral, host, or dual-mode               |     |

| J          | and used in high speed mode                                               | 192 |

| Figure 97. | MII mode using a 25 MHz crystal                                           | 193 |

| Figure 98. | RMII with a 50 MHz oscillator                                             |     |

| Figure 99  | RMII with a 25 MHz crystal and PHY with PLI                               |     |

### 2.2.26 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S application. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I<sup>2</sup>S flow with an external PLL (or Codec output).

### 2.2.27 Secure digital input/output interface (SDIO)

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 48 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

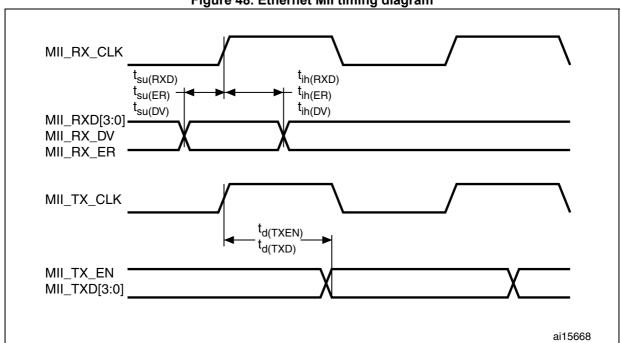

## 2.2.28 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

Peripheral available only on the STM32F417xx devices.

The STM32F417xx devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard medium-independent interface (MII) or a reduced medium-independent interface (RMII). The STM32F417xx requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). the PHY is connected to the STM32F417xx MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) from the STM32F417xx.

10 2 8 7 PA14 PB4 VBAT PC13 PDR\_ON воото PD7 PD4 PC12 VDD PC14 PI1 PB3 PC15 VDD PD6 PD2 PA15 VCAP\_2 PB7 В С PA0 VSS PB9 PB6 PD5 PD1 PC11 PI0 PA12 PA11 BYPASS REG PA13 PB8 PD0 PC10 PA8 PC3 Е PC0 VSS VDD VSS VDD PC9 PC8 PC7 VSS F PH0 PH1 PE10 PE14 VCAP\_1 PD14 PD15 VDD PC6 PA1 G NRST VDDA PB0 PE7 PE13 PD11 VSSA PA6 PB1 PE8 PE12 PB10 PD9 PB15 PB2 PE9 PE11 PB11 PB12 PB14 PB13 PA7 MS30402V1

Figure 17. STM32F41xxx WLCSP90 ballout

Table 6. Legend/abbreviations used in the pinout table

| Name                 | Abbreviation       | Definition                                                                                         |  |  |  |  |  |  |

|----------------------|--------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin name             |                    | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |  |  |  |

|                      | S                  | Supply pin                                                                                         |  |  |  |  |  |  |

| Pin type             | I                  | Input only pin                                                                                     |  |  |  |  |  |  |

|                      | I/O                | Input / output pin                                                                                 |  |  |  |  |  |  |

|                      | FT                 | 5 V tolerant I/O                                                                                   |  |  |  |  |  |  |

| I/O structure        | TTa                | 3.3 V tolerant I/O directly connected to ADC                                                       |  |  |  |  |  |  |

| i/O structure        | В                  | Dedicated BOOT0 pin                                                                                |  |  |  |  |  |  |

|                      | RST                | Bidirectional reset pin with embedded weak pull-up resistor                                        |  |  |  |  |  |  |

| Notes                | Unless otherwise   | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |  |  |  |

| Alternate functions  | Functions selected | Functions selected through GPIOx_AFR registers                                                     |  |  |  |  |  |  |

| Additional functions | Functions directly | Functions directly selected/enabled through peripheral registers                                   |  |  |  |  |  |  |

<sup>1.</sup> This figure shows the package bump view.

Table 7. STM32F41xxx pin and ball definitions (continued)

|        | ı       | Pin r   | numb    | er       |         |                                                      |          |                 |       | ,                                                                                               |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|-------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                             | Additional<br>functions |

|        | D9      |         |         | L4       | 48      | BYPASS_REG                                           | I        | FT              | -     | -                                                                                               | -                       |

| 19     | E4      | 28      | 39      | K4       | 49      | V <sub>DD</sub> S                                    |          | -               |       |                                                                                                 |                         |

| 20     | J9      | 29      | 40      | N4       | 50      | PA4                                                  | I/O      | ТТа             | (4)   | SPI1_NSS / SPI3_NSS /<br>USART2_CK /<br>DCMI_HSYNC /<br>OTG_HS_SOF/ I2S3_WS/<br>EVENTOUT        | ADC12_IN4<br>/DAC_OUT1  |

| 21     | G8      | 30      | 41      | P4       | 51      | PA5                                                  | I/O      | ТТа             | (4)   | SPI1_SCK/ OTG_HS_ULPI_CK / TIM2_CH1_ETR/ TIM8_CH1N/ EVENTOUT                                    | ADC12_IN5/DAC_<br>OUT2  |

| 22     | Н8      | 31      | 42      | P3       | 52      | PA6                                                  | I/O      | FT              | (4)   | SPI1_MISO /<br>TIM8_BKIN/TIM13_CH1 /<br>DCMI_PIXCLK / TIM3_CH1<br>/ TIM1_BKIN/ EVENTOUT         | ADC12_IN6               |

| 23     | J8      | 32      | 43      | R3       | 53      | PA7                                                  | I/O      | FT              | (4)   | SPI1_MOSI/TIM8_CH1N / TIM14_CH1/TIM3_CH2/ ETH_MII_RX_DV / TIM1_CH1N / ETH_RMII_CRS_DV/ EVENTOUT | ADC12_IN7               |

| 24     | -       | 33      | 44      | N5       | 54      | PC4                                                  | I/O      | FT              | (4)   | ETH_RMII_RX_D0 /<br>ETH_MII_RX_D0/<br>EVENTOUT                                                  | ADC12_IN14              |

| 25     | -       | 34      | 45      | P5       | 55      | PC5                                                  | I/O      | FT              | (4)   | ETH_RMII_RX_D1 /<br>ETH_MII_RX_D1/<br>EVENTOUT                                                  | ADC12_IN15              |

| 26     | G7      | 35      | 46      | R5       | 56      | PB0                                                  | I/O      | FT              | (4)   | TIM3_CH3 / TIM8_CH2N/<br>OTG_HS_ULPI_D1/<br>ETH_MII_RXD2 /<br>TIM1_CH2N/ EVENTOUT               | ADC12_IN8               |

| 27     | H7      | 36      | 47      | R4       | 57      | PB1                                                  | I/O      | FT              | (4)   | TIM3_CH4 / TIM8_CH3N/<br>OTG_HS_ULPI_D2/<br>ETH_MII_RXD3 /<br>TIM1_CH3N/ EVENTOUT               | ADC12_IN9               |

| 28     | J7      | 37      | 48      | M6       | 58      | PB2/BOOT1<br>(PB2)                                   | I/O      | FT              | -     | EVENTOUT                                                                                        | -                       |

Pin number / O structure Pin type Pin name Notes **UFBGA176** Additional LQFP176 WLCSP90 LQFP100 LQFP144 LQFP64 (function after **Alternate functions** functions reset)(1) 143 C6 171 PDR\_ON I FT **A8** 10 64 A1 144 C5 172 S  $V_{DD}$ 0 TIM8\_BKIN / DCMI\_D5/ PI4 I/O FT Π4 173 **EVENTOUT** TIM8\_CH1/ 174 PI5 I/O FT DCMI VSYNC/ C4 **EVENTOUT** TIM8 CH2 / DCMI D6/ C3 175 PI6 I/O FT **EVENTOUT** TIM8\_CH3 / DCMI\_D7/ C2 176 PI7 I/O FT **EVENTOUT**

Table 7. STM32F41xxx pin and ball definitions (continued)

- 1. Function availability depends on the chosen device.

- PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF.

- These I/Os must not be used as a current source (e.g. to drive an LED).

- 3. Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F4xx reference manual, available from the STMicroelectronics website:

- 4. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

- If the device is delivered in an UFBGA176 or WLCSP90 and the BYPASS\_REG pin is set to VDD (Regulator off/internal reset ON mode), then PA0 is used as an internal Reset (active low).

Table 8. FSMC pin definition

|                     |    |                    |               | WLCSP90     |                        |     |

|---------------------|----|--------------------|---------------|-------------|------------------------|-----|

| Pins <sup>(1)</sup> | CF | NOR/PSRAM/<br>SRAM | NOR/PSRAM Mux | NAND 16 bit | LQFP100 <sup>(2)</sup> | (2) |

| PE2                 | -  | A23                | A23           | -           | Yes                    | -   |

| PE3                 | -  | A19                | A19           | -           | Yes                    | -   |

| PE4                 | -  | A20                | A20           | -           | Yes                    | -   |

| PE5                 | -  | A21                | A21           | -           | Yes                    | -   |

| PE6                 | ı  | A22                | A22           | -           | Yes                    | -   |

| PF0                 | A0 | A0                 | -             | -           | -                      | -   |

62/206 DocID022063 Rev 8

**Table 8. FSMC pin definition (continued)**

|                     |        |                    | FSMC          | . (         | ,                      |                |

|---------------------|--------|--------------------|---------------|-------------|------------------------|----------------|

| Pins <sup>(1)</sup> | CF     | NOR/PSRAM/<br>SRAM | NOR/PSRAM Mux | NAND 16 bit | LQFP100 <sup>(2)</sup> | WLCSP90<br>(2) |

| PG2                 | -      | A12                | -             | -           | -                      | -              |

| PG3                 | -      | A13                | -             | =           | -                      | -              |

| PG4                 | -      | A14                | -             | -           | -                      | -              |

| PG5                 | -      | A15                | -             | -           | -                      | -              |

| PG6                 | -      | -                  | -             | INT2        | -                      | -              |

| PG7                 | -      | -                  | -             | INT3        | -                      | -              |

| PD0                 | D2     | D2                 | DA2           | D2          | Yes                    | Yes            |

| PD1                 | D3     | D3                 | DA3           | D3          | Yes                    | Yes            |

| PD3                 | -      | CLK                | CLK           | -           | Yes                    | -              |

| PD4                 | NOE    | NOE                | NOE           | NOE         | Yes                    | Yes            |

| PD5                 | NWE    | NWE                | NWE           | NWE         | Yes                    | Yes            |

| PD6                 | NWAIT  | NWAIT              | NWAIT         | NWAIT       | Yes                    | Yes            |

| PD7                 | -      | NE1                | NE1           | NCE2        | Yes                    | Yes            |

| PG9                 | -      | NE2                | NE2           | NCE3        | -                      | -              |

| PG10                | NCE4_1 | NE3                | NE3           | -           | -                      | -              |

| PG11                | NCE4_2 | -                  | -             | -           | -                      | -              |

| PG12                | -      | NE4                | NE4           | -           | -                      | -              |

| PG13                | -      | A24                | A24           | -           | -                      | -              |

| PG14                | -      | A25                | A25           | -           | -                      | -              |

| PB7                 | -      | NADV               | NADV          | -           | Yes                    | Yes            |

| PE0                 | -      | NBL0               | NBL0          | -           | Yes                    | -              |

| PE1                 | -      | NBL1               | NBL1          | -           | Yes                    | -              |

Full FSMC features are available on LQFP144, LQFP176, and UFBGA176. The features available on smaller packages are given in the dedicated package column.

<sup>2.</sup> Ports F and G are not available in devices delivered in 100-pin packages.

## **Table 9. Alternate function mapping (continued)**

|        |      | AF0  | AF1    | AF2      | AF3              | AF4      | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10                | AF11                            | AF12                 | AF13    |      |          |

|--------|------|------|--------|----------|------------------|----------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|---------------------|---------------------------------|----------------------|---------|------|----------|

| P      | ort  | sys  | TIM1/2 | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3 | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS   | ЕТН                             | FSMC/SDIO<br>/OTG_FS | DCMI    | AF14 | AF15     |

|        | PC0  |      | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | OTG_HS_ULPI_<br>STP | -                               | -                    | -       |      | EVENTOUT |

|        | PC1  | -    | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                   | ETH_MDC                         | -                    | -       | -    | EVENTOUT |

|        | PC2  | -    | -      | -        | -                | -        | SPI2_MISO                      | I2S2ext_SD           | -                      | -                  | -                         | OTG_HS_ULPI_<br>DIR | ETH _MII_TXD2                   | -                    | -       |      | EVENTOUT |

|        | PC3  | -    | -      | -        | -                | =        | SPI2_MOSI<br>I2S2_SD           | -                    | -                      | =                  | -                         | OTG_HS_ULPI_<br>NXT | ETH<br>_MII_TX_CLK              | =                    | -       | -    | EVENTOUT |

|        | PC4  |      | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                   | ETH_MII_RXD0<br>ETH_RMII_RXD0   | -                    | -       | -    | EVENTOUT |

|        | PC5  |      | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                   | ETH _MII_RXD1<br>ETH _RMII_RXD1 | -                    | -       | -    | EVENTOUT |

|        | PC6  | -    | -      | TIM3_CH1 | TIM8_CH1         |          | I2S2_MCK                       |                      | -                      | USART6_TX          | -                         | -                   | -                               | SDIO_D6              | DCMI_D0 | -    | EVENTOUT |

| Port C | PC7  | i    | -      | TIM3_CH2 | TIM8_CH2         | -        | -                              | I2S3_MCK             | -                      | USART6_RX          | -                         | -                   | -                               | SDIO_D7              | DCMI_D1 | -    | EVENTOUT |

|        | PC8  | i    | -      | TIM3_CH3 | TIM8_CH3         | -        | -                              | -                    | -                      | USART6_CK          | -                         | -                   | -                               | SDIO_D0              | DCMI_D2 | -    | EVENTOUT |

|        | PC9  | MCO2 | -      | TIM3_CH4 | TIM8_CH4         | I2C3_SDA | I2S_CKIN                       | -                    | -                      | -                  | -                         | -                   | -                               | SDIO_D1              | DCMI_D3 | -    | EVENTOUT |

|        | PC10 | -    | -      | -        | -                | -        | -                              | SPI3_SCK/<br>I2S3_CK | USART3_TX/             | UART4_TX           | -                         | -                   | =                               | SDIO_D2              | DCMI_D8 | -    | EVENTOUT |

|        | PC11 | -    | -      | -        | -                | -        | I2S3ext_SD                     | SPI3_MISO/           | USART3_RX              | UART4_RX           | -                         | =                   | =                               | SDIO_D3              | DCMI_D4 | -    | EVENTOUT |

|        | PC12 | =    | -      | -        | -                | =        | -                              | SPI3_MOSI<br>I2S3_SD | USART3_CK              | UART5_TX           | -                         | -                   | -                               | SDIO_CK              | DCMI_D9 | =    | EVENTOUT |

|        | PC13 | =    | -      | =        | =                | =        | -                              | =                    | =                      | =                  | =                         | =                   | =                               | =                    | -       | =    | EVENTOUT |

|        | PC14 | =    | -      | =        | =                | =        | -                              | =                    | =                      | =                  | =                         | =                   | =                               | =                    | -       | -    | EVENTOUT |

|        | PC15 | -    | -      | -        | -                | -        | -                              | -                    |                        | -                  | -                         | -                   | -                               | -                    | -       | -    | EVENTOUT |

**Table 9. Alternate function mapping (continued)**

|        |      |              |           |          |                  |          |                                |                      |                        |                    | `                         |                   |               |                      |         |      |          |

|--------|------|--------------|-----------|----------|------------------|----------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|-------------------|---------------|----------------------|---------|------|----------|

|        |      | AF0          | AF1       | AF2      | AF3              | AF4      | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10              | AF11          | AF12                 | AF13    |      |          |

| Pe     | ort  | sys          | TIM1/2    | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3 | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS | ЕТН           | FSMC/SDIO<br>/OTG_FS | DCMI    | AF14 | AF15     |

|        | PE0  | -            | -         | TIM4_ETR | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_NBL0            | DCMI_D2 | ÷    | EVENTOUT |

|        | PE1  | =            | =         | =        | -                | =        | -                              | =                    | =                      | =                  | =                         | i.                | =             | FSMC_NBL1            | DCMI_D3 | -    | EVENTOUT |

|        | PE2  | TRACECL<br>K | =         | -        | -                | =        | -                              | =                    | -                      | -                  | -                         | -                 | ETH _MII_TXD3 | FSMC_A23             | =       | -    | EVENTOUT |

|        | PE3  | TRACED0      | -         | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_A19             | -       | -    | EVENTOUT |

|        | PE4  | TRACED1      | -         | -        | -                | -        | -                              | -                    |                        | -                  | -                         | -                 | -             | FSMC_A20             | DCMI_D4 | -    | EVENTOUT |

|        | PE5  | TRACED2      | -         | -        | TIM9_CH1         | -        | -                              | -                    | -                      | -                  | -                         | =                 | -             | FSMC_A21             | DCMI_D6 | -    | EVENTOUT |

|        | PE6  | TRACED3      | -         | -        | TIM9_CH2         | -        | -                              | -                    | -                      | -                  | -                         | =                 | -             | FSMC_A22             | DCMI_D7 | -    | EVENTOUT |

| Port E | PE7  | -            | TIM1_ETR  | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | =                 | -             | FSMC_D4              | =       | -    | EVENTOUT |

|        | PE8  | -            | TIM1_CH1N | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | =                 | -             | FSMC_D5              | -       | -    | EVENTOUT |

|        | PE9  | -            | TIM1_CH1  | -        | -                | -        | -                              | =                    | =                      | =                  | -                         | =                 | =             | FSMC_D6              | =       | -    | EVENTOUT |

|        | PE10 | -            | TIM1_CH2N | -        | -                | -        | -                              | =                    | =                      | =                  | -                         | =                 | =             | FSMC_D7              | =       | -    | EVENTOUT |

|        | PE11 | -            | TIM1_CH2  | -        | -                | -        | -                              | =                    | =                      | -                  | -                         | =                 | =             | FSMC_D8              | -       | -    | EVENTOUT |

|        | PE12 | -            | TIM1_CH3N | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | =                 | -             | FSMC_D9              | =       | -    | EVENTOUT |

|        | PE13 | -            | TIM1_CH3  | -        | -                | =        | -                              | =                    | =                      | =                  | -                         | =                 | =             | FSMC_D10             | =       | =    | EVENTOUT |

|        | PE14 | =            | TIM1_CH4  | =        | -                | =        | -                              | =                    | =                      | =                  | =                         | =                 | =             | FSMC_D11             | =       | =    | EVENTOUT |

|        | PE15 | -            | TIM1_BKIN | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_D12             | -       |      | EVENTOUT |

DocID022063 Rev 8

### 5.1.7 Current consumption measurement

IDD\_VBAT VBAT VDDA

Figure 22. Current consumption measurement scheme

# 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. Device mission profile (application conditions) is compliant with JEDEC JESD47 Qualification Standard, extended mission profiles are available on demand.

| Symbol                            | Ratings                                                                                  | Min                                                        | Max                 | Unit |

|-----------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------|------|

| $V_{DD}$ – $V_{SS}$               | External main supply voltage (including $V_{DDA}$ , $V_{DD}$ ) <sup>(1)</sup>            | -0.3                                                       | 4.0                 |      |

| V                                 | Input voltage on five-volt tolerant pin <sup>(2)</sup>                                   | V <sub>SS</sub> -0.3                                       | V <sub>DD</sub> +4  | V    |

| $V_{IN}$                          | Input voltage on any other pin                                                           | V <sub>SS</sub> -0.3                                       | 4.0                 |      |

| $ \Delta V_{DDx} $                | Variations between different V <sub>DD</sub> power pins                                  | -                                                          | 50                  |      |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins including $V_{\mbox{\scriptsize REF}-}$ | -                                                          | 50                  | mV   |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                                       | see Section<br>Absolute in<br>ratings (ele<br>sensitivity) | naximum<br>ectrical |      |

Table 11. Voltage characteristics

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

V<sub>IN</sub> maximum value must always be respected. Refer to Table 12 for the values of the maximum allowed injected current.

Table 14. General operating conditions (continued)

| Symbol          | Parameter                                                                                                      | Conditions                                                         | Min  | Тур  | Max                       | Unit  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------|------|---------------------------|-------|--|--|--|--|

|                 | Regulator ON:                                                                                                  | VOS bit in PWR_CR register = 0 <sup>(1)</sup> Max frequency 144MHz | 1.08 | 1.14 | 1.20                      | V     |  |  |  |  |

| V <sub>12</sub> | 1.2 V internal voltage on V <sub>CAP_1</sub> /V <sub>CAP_2</sub> pins                                          | VOS bit in PWR_CR register= 1<br>Max frequency 168MHz              | 1.20 | 1.26 | 1.32                      | ٧     |  |  |  |  |

| 12              | Regulator OFF:                                                                                                 | Max frequency 144MHz                                               | 1.10 | 1.14 | 1.20                      | V     |  |  |  |  |

|                 | 1.2 V external voltage must be supplied from external regulator on V <sub>CAP_1</sub> /V <sub>CAP_2</sub> pins | Max frequency 168MHz                                               | 1.20 | 1.26 | 1.30                      | V     |  |  |  |  |

|                 | Input voltage on RST and FT                                                                                    | 2 V ≤ V <sub>DD</sub> ≤ 3.6 V                                      | -0.3 | -    | 5.5                       |       |  |  |  |  |

|                 | pins <sup>(6)</sup>                                                                                            | V <sub>DD</sub> ≤ 2 V                                              | -0.3 | -    | 5.2                       |       |  |  |  |  |

| $V_{IN}$        | Input voltage on TTa pins                                                                                      | -                                                                  | -0.3 | -    | V <sub>DDA</sub> +<br>0.3 | V     |  |  |  |  |

|                 | Input voltage on B pin                                                                                         | -                                                                  | 5.5  |      |                           |       |  |  |  |  |

|                 |                                                                                                                | LQFP64                                                             | -    | -    | 435                       |       |  |  |  |  |

|                 | Power dissipation at T <sub>A</sub> = 85 °C                                                                    | LQFP100                                                            | -    | -    | 465                       |       |  |  |  |  |

| р               |                                                                                                                | LQFP144                                                            | -    | -    | 500                       | mW    |  |  |  |  |

| $P_{D}$         | for suffix 6 or $T_A = 105$ °C for suffix $7^{(7)}$                                                            | LQFP176                                                            | -    | -    | 526                       | IIIVV |  |  |  |  |

|                 |                                                                                                                | UFBGA176                                                           | -    | -    | 513                       |       |  |  |  |  |

|                 |                                                                                                                | WLCSP90                                                            | -    | -    | 543                       |       |  |  |  |  |

|                 | Ambient temperature for 6 suffix                                                                               | Maximum power dissipation                                          | -40  | -    | 85                        | °C    |  |  |  |  |

| т,              | version                                                                                                        | Low-power dissipation <sup>(8)</sup>                               | -40  | -    | 105                       |       |  |  |  |  |

| TA              | Ambient temperature for 7 suffix                                                                               | Maximum power dissipation                                          | -40  | -    | 105                       | °C    |  |  |  |  |

|                 | version                                                                                                        | Low-power dissipation <sup>(8)</sup>                               | -40  | -    | 125                       | ] °C  |  |  |  |  |

| TJ              | Junction temperature range                                                                                     | 6 suffix version                                                   | -40  | -    | 105                       | - °C  |  |  |  |  |

| IJ              | Junction temperature range                                                                                     | 7 suffix version                                                   | -40  | -    | 125                       |       |  |  |  |  |

The average expected gain in power consumption when VOS = 0 compared to VOS = 1 is around 10% for the whole temperature range, when the system clock frequency is between 30 and 144 MHz.

- 7. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

- 8. In low-power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_{Jmax}$ .

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section: Internal reset OFF).

<sup>3.</sup> When the ADC is used, refer to Table 67: ADC characteristics.

<sup>4.</sup> If  $V_{REF+}$  pin is present, it must respect the following condition:  $V_{DDA}-V_{REF+} < 1.2 \text{ V}$ .

<sup>5.</sup> It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and power-down operation.

<sup>6.</sup> To sustain a voltage higher than  $V_{DD}$ +0.3, the internal pull-up and pull-down resistors must be disabled.

Table 15. Limitations depending on the operating power supply range

| rabio to. Emmanono apportanti on uno oportanti portor cappi, tango |                                      |                                                                                   |                                                                                       |                                                                                             |                                                                                                                                                                                    |                                                  |  |  |

|--------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|

| Operating<br>power<br>supply<br>range                              | ADC<br>operation                     | Maximum Flash memory access frequency with no wait state (f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency<br>with wait<br>states <sup>(1)</sup> (2) | I/O operation                                                                               | Clock output<br>Frequency on<br>I/O pins                                                                                                                                           | Possible<br>Flash<br>memory<br>operations        |  |  |

| V <sub>DD</sub> =1.8 to 2.1 V <sup>(3)</sup>                       | Conversion<br>time up to<br>1.2 Msps | 20 MHz <sup>(4)</sup>                                                             | 160 MHz with 7<br>wait states                                                         | <ul><li>Degraded<br/>speed<br/>performance</li><li>No I/O<br/>compensation</li></ul>        | up to 30 MHz                                                                                                                                                                       | 8-bit erase<br>and program<br>operations<br>only |  |  |

| V <sub>DD</sub> = 2.1 to 2.4 V                                     | Conversion<br>time up to<br>1.2 Msps | 22 MHz                                                                            | 168 MHz with 7<br>wait states                                                         | <ul><li>Degraded<br/>speed<br/>performance</li><li>No I/O<br/>compensation</li></ul>        | up to 30 MHz                                                                                                                                                                       | 16-bit erase<br>and program<br>operations        |  |  |

| V <sub>DD</sub> = 2.4 to 2.7 V                                     | Conversion<br>time up to<br>2.4 Msps | 24 MHz                                                                            | 168 MHz with 6<br>wait states                                                         | <ul><li>Degraded<br/>speed<br/>performance</li><li>I/O<br/>compensation<br/>works</li></ul> | up to 48 MHz                                                                                                                                                                       | 16-bit erase<br>and program<br>operations        |  |  |

| V <sub>DD</sub> = 2.7 to<br>3.6 V <sup>(5)</sup>                   | Conversion<br>time up to<br>2.4 Msps | 30 MHz                                                                            | 168 MHz with 5<br>wait states                                                         | <ul><li>Full-speed operation</li><li>I/O compensation works</li></ul>                       | <ul> <li>up to</li> <li>60 MHz</li> <li>when V<sub>DD</sub> =</li> <li>3.0 to 3.6 V</li> <li>up to</li> <li>48 MHz</li> <li>when V<sub>DD</sub> =</li> <li>2.7 to 3.0 V</li> </ul> | 32-bit erase<br>and program<br>operations        |  |  |

<sup>1.</sup> It applies only when code executed from Flash memory access, when code executed from RAM, no wait state is required.

<sup>2.</sup> Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

V<sub>DD</sub>/VDDA minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section: Internal reset OFF).

<sup>4.</sup> Prefetch is not available. Refer to AN3430 application note for details on how to adjust performance and power.

<sup>5.</sup> The voltage range for OTG USB FS can drop down to 2.7 V. However it is degraded between 2.7 and 3 V.

| Symbol                                  | Parameter                                                                          | Conditions                                                                                | Min  | Тур  | Max  | Unit |

|-----------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| V                                       | Brownout level 2                                                                   | Falling edge                                                                              | 2.44 | 2.50 | 2.56 | V    |

| V <sub>BOR2</sub>                       | threshold                                                                          | Rising edge                                                                               | 2.53 | 2.59 | 2.63 | V    |

| \/                                      | Brownout level 3                                                                   | Falling edge                                                                              | 2.75 | 2.83 | 2.88 | V    |

| V <sub>BOR3</sub>                       | threshold                                                                          | Rising edge                                                                               | 2.85 | 2.92 | 2.97 | V    |

| V <sub>BORhyst</sub> <sup>(1)</sup>     | BOR hysteresis                                                                     | -                                                                                         | -    | 100  | -    | mV   |

| T <sub>RSTTEMPO</sub> <sup>(1)(2)</sup> | Reset temporization                                                                | -                                                                                         | 0.5  | 1.5  | 3.0  | ms   |

| I <sub>RUSH</sub> <sup>(1)</sup>        | InRush current on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby) | -                                                                                         | -    | 160  | 200  | mA   |

| E <sub>RUSH</sub> <sup>(1)</sup>        | InRush energy on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby)  | V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 105 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 μs | -    | -    | 5.4  | μC   |

Table 19. Embedded reset and power control block characteristics (continued)

## 5.3.6 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 22: Current consumption measurement scheme*.

All Run mode current consumption measurements given in this section are performed using a CoreMark-compliant code.

## Typical and maximum current consumption

The MCU is placed under the following conditions:

- At startup, all I/O pins are configured as analog inputs by firmware.

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 30 MHz, 1 wait state from 30 to 60 MHz, 2 wait states from 60 to 90 MHz, 3 wait states from 90 to 120 MHz, 4 wait states from 120 to 150 MHz, and 5 wait states from 150 to 168 MHz).

- When the peripherals are enabled HCLK is the system clock, f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2, except is explicitly mentioned.

- The maximum values are obtained for  $V_{DD} = 3.6 \text{ V}$  and maximum ambient temperature  $(T_A)$ , and the typical values for  $T_A = 25 \,^{\circ}\text{C}$  and  $V_{DD} = 3.3 \,^{\circ}\text{V}$  unless otherwise specified.

<sup>1.</sup> Guaranteed by design.

<sup>2.</sup> The reset temporization is measured from the power-on (POR reset or wakeup from V<sub>BAT</sub>) to the instant when first instruction is read by the user application code.

#### Additional current consumption

The MCU is placed under the following conditions:

- All I/O pins are configured in analog mode.

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency.

- The voltage scaling is adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 2 for f<sub>HCLK</sub> ≤ 144 MHz

- Scale 1 for 144 MHz < f<sub>HCLK</sub> ≤ 168 MHz.

- The system clock is HCLK, f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2.

- The HSE crystal clock frequency is 25 MHz.

- T<sub>Δ</sub>= 25 °C.

Table 26. Typical current consumption in Run mode, code with data processing running from Flash memory, regulator ON (ART accelerator enabled except prefetch), V<sub>DD</sub> = 1.8 V<sup>(1)</sup>

|         | CACC                          | pr preferency, VD          | ) - 1.0 <b>V</b>        |                                   |      |

|---------|-------------------------------|----------------------------|-------------------------|-----------------------------------|------|

| Symbol  | Parameter                     | Conditions                 | f <sub>HCLK</sub> (MHz) | Typ. at T <sub>A</sub> =<br>25 °C | Unit |

|         |                               |                            | 160                     | 36.2                              |      |

|         |                               |                            | 144                     | 29.3                              |      |

|         |                               | All peripheral<br>disabled | 120                     | 24.7                              |      |

| IDD     | Supply current in<br>Run mode |                            | 90                      | 19.3                              | mA   |

| rannodo | diodolod                      | 60                         | 13.4                    | 1                                 |      |

|         |                               |                            | 30                      | 7.7                               |      |

|         |                               |                            | 25                      | 6.0                               |      |

|         |                               |                            |                         |                                   |      |

When peripherals are enabled, the power consumption corresponding to the analog part of the peripherals (such as ADC or DAC) is not included.

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 48: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

Caution:

Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to

96/206 DocID022063 Rev 8

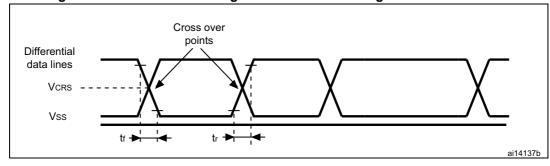

Figure 44. USB OTG FS timings: definition of data signal rise and fall time

Table 59. USB OTG FS electrical characteristics<sup>(1)</sup>

|                  | Driver characteristics          |                                |     |     |      |  |  |  |

|------------------|---------------------------------|--------------------------------|-----|-----|------|--|--|--|

| Symbol           | Parameter                       | Conditions Min                 |     | Max | Unit |  |  |  |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |

| t <sub>f</sub>   | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |

| t <sub>rfm</sub> | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |  |

| V <sub>CRS</sub> | Output signal crossover voltage | -                              | 1.3 | 2.0 | V    |  |  |  |

<sup>1.</sup> Guaranteed by design.

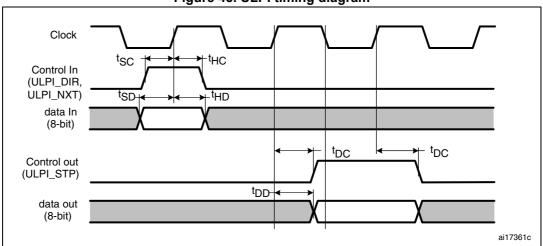

#### **USB HS characteristics**

Unless otherwise specified, the parameters given in *Table 62* for ULPI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency summarized in *Table 61* and  $V_{DD}$  supply voltage conditions summarized in *Table 60*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>.

Refer to Section Section 5.3.16: I/O port characteristics for more details on the input/output characteristics.

Table 60. USB HS DC electrical characteristics

| Symb        | ol       | Parameter                    | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |

|-------------|----------|------------------------------|---------------------|---------------------|------|

| Input level | $V_{DD}$ | USB OTG HS operating voltage | 2.7                 | 3.6                 | V    |

<sup>1.</sup> All the voltages are measured from the local ground potential.

Table 61. USB HS clock timing parameters<sup>(1)</sup>

| Parameter                                                      | Symbol | Min                     | Nominal | Max | Unit |     |

|----------------------------------------------------------------|--------|-------------------------|---------|-----|------|-----|

| f <sub>HCLK</sub> value to guarantee prope<br>USB HS interface | -      | 30                      | -       | -   | MHz  |     |

| Frequency (first transition) 8-bit ±10%                        |        | F <sub>START_8BIT</sub> | 54      | 60  | 66   | MHz |

<sup>2.</sup> Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

5.6

ms

μs

|                                                                    |                     | 0.                      |         |        |      |   |

|--------------------------------------------------------------------|---------------------|-------------------------|---------|--------|------|---|

| Parameter                                                          | Symbol              | Min                     | Nominal | Max    | Unit |   |

| Frequency (steady state) ±500                                      | F <sub>STEADY</sub> | 59.97                   | 60      | 60.03  | MHz  |   |

| Duty cycle (first transition)                                      | 8-bit ±10%          | D <sub>START_8BIT</sub> | 40      | 50     | 60   | % |

| Duty cycle (steady state) ±500                                     | D <sub>STEADY</sub> | 49.975                  | 50      | 50.025 | %    |   |

| Time to reach the steady state duty cycle after the first transiti | T <sub>STEADY</sub> | -                       | -       | 1.4    | ms   |   |

Table 61. USB HS clock timing parameters<sup>(1)</sup>

of the input clock

Clock startup time after the

de-assertion of SuspendM

PHY preparation time after the first transition

Table 62. ULPI timing

$T_{PREP}$

T<sub>START\_DEV</sub>

T<sub>START\_HOST</sub>

Peripheral

Host

| Parameter                                       | Symbol          | Valu | Unit |       |

|-------------------------------------------------|-----------------|------|------|-------|

| Farameter                                       | Symbol          | Min. | Max. | Offic |

| Control in (ULPI_DIR) setup time                | 4               | -    | 2.0  |       |

| Control in (ULPI_NXT) setup time                | t <sub>SC</sub> | -    | 1.5  |       |

| Control in (ULPI_DIR, ULPI_NXT) hold time       | t <sub>HC</sub> | 0    | -    |       |

| Data in setup time                              | t <sub>SD</sub> | -    | 2.0  | ns    |

| Data in hold time                               | t <sub>HD</sub> | 0    | -    |       |

| Control out (ULPI_STP) setup time and hold time | t <sub>DC</sub> | -    | 9.2  |       |

| Data out available from clock rising edge       | t <sub>DD</sub> | -    | 10.7 |       |

<sup>1.</sup>  $V_{DD}$  = 2.7 V to 3.6 V and  $T_A$  = -40 to 85 °C.

Figure 45. ULPI timing diagram

134/206 DocID022063 Rev 8

<sup>1.</sup> Guaranteed by design.

RMII\_REF\_CLK  $t_{d(TXEN)}$  $t_{d(TXD)}$ RMII\_TX\_EN RMII\_TXD[1:0] t<sub>ih(RXD)</sub> t<sub>su(RXD)</sub> t<sub>su(CRS)</sub> t<sub>ih(CRS)</sub> RMII\_RXD[1:0] RMII\_CRS\_DV ai15667

Figure 47. Ethernet RMII timing diagram

Table 65. Dynamic characteristics: Ethernet MAC signals for RMII

| Symbol               | Rating                           | Min | Тур | Max  | Unit |

|----------------------|----------------------------------|-----|-----|------|------|

| t <sub>su(RXD)</sub> | Receive data setup time          | 2   | -   | -    | ns   |

| t <sub>ih(RXD)</sub> | Receive data hold time           | 1   | -   | -    | ns   |

| t <sub>su(CRS)</sub> | Carrier sense set-up time        | 0.5 | -   | -    | ns   |

| t <sub>ih(CRS)</sub> | Carrier sense hold time          | 2   | -   | -    | ns   |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | 8   | 9.5 | 11   | ns   |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | 8.5 | 10  | 11.5 | ns   |

Table 66 gives the list of Ethernet MAC signals for MII and Figure 47 shows the corresponding timing diagram.

136/206 DocID022063 Rev 8

Table 74. DAC characteristics (continued)

| Symbol                            | Parameter                                                                                                    | Min | Тур | Max                      | Unit | Comments                                                                                                                        |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|------|---------------------------------------------------------------------------------------------------------------------------------|--|

| R <sub>LOAD</sub> <sup>(2)</sup>  | Resistive load with buffer ON                                                                                | 5   | -   | -                        | kΩ   |                                                                                                                                 |  |

| R <sub>O</sub> <sup>(2)</sup>     | Impedance output with buffer OFF                                                                             | -   | -   | 15                       | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$         |  |

| C <sub>LOAD</sub> <sup>(2)</sup>  | Capacitive load                                                                                              | -   | -   | 50                       | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                                 |  |

| DAC_OUT min <sup>(2)</sup>        | Lower DAC_OUT voltage with buffer ON                                                                         | 0.2 | -   | -                        | ٧    | It gives the maximum output excursion of the DAC. It corresponds to 12-bit input code (0x0E0) to (0xF1C) at V <sub>REF+</sub> = |  |

| DAC_OUT max <sup>(2)</sup>        | Higher DAC_OUT voltage with buffer ON                                                                        | -   | -   | V <sub>DDA</sub> – 0.2   | ٧    | 3.6 V and (0x1C7) to (0xE38) at V <sub>REF+</sub> = 1.8 V                                                                       |  |

| DAC_OUT min <sup>(2)</sup>        | Lower DAC_OUT voltage with buffer OFF                                                                        | -   | 0.5 | -                        | mV   | It gives the maximum output                                                                                                     |  |

| DAC_OUT max <sup>(2)</sup>        | Higher DAC_OUT voltage with buffer OFF                                                                       | -   | -   | V <sub>REF+</sub> – 1LSB | ٧    | excursion of the DAC.                                                                                                           |  |

| (4)                               | DAC DC V <sub>REF</sub> current consumption in quiescent                                                     | -   | 170 | 240                      |      | With no load, worst code (0x800) at V <sub>REF+</sub> = 3.6 V in terms of DC consumption on the inputs                          |  |

| I <sub>VREF+</sub> <sup>(4)</sup> | mode (Standby mode)                                                                                          | -   | 50  | 75                       | μА   | With no load, worst code (0xF1C) at V <sub>REF+</sub> = 3.6 V in terms of DC consumption on the inputs                          |  |

|                                   | DAC DC VDDA current                                                                                          | -   | 280 | 380                      | μA   | With no load, middle code (0x800) on the inputs                                                                                 |  |

| I <sub>DDA</sub> <sup>(4)</sup>   | consumption in quiescent mode <sup>(3)</sup>                                                                 | -   | 475 | 625                      | μA   | With no load, worst code (0xF1C) at V <sub>REF+</sub> = 3.6 V in terms of DC consumption on the inputs                          |  |

| DNL <sup>(4)</sup>                | Differential non linearity Difference between two                                                            | -   | -   | ±0.5                     | LSB  | Given for the DAC in 10-bit configuration.                                                                                      |  |

|                                   | consecutive code-1LSB)                                                                                       | -   | -   | ±2                       | LSB  | Given for the DAC in 12-bit configuration.                                                                                      |  |

|                                   | Integral non linearity<br>(difference between                                                                | -   | -   | ±1                       | LSB  | Given for the DAC in 10-bit configuration.                                                                                      |  |

| INL <sup>(4)</sup>                | measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) | -   | -   | ±4                       | LSB  | Given for the DAC in 12-bit configuration.                                                                                      |  |

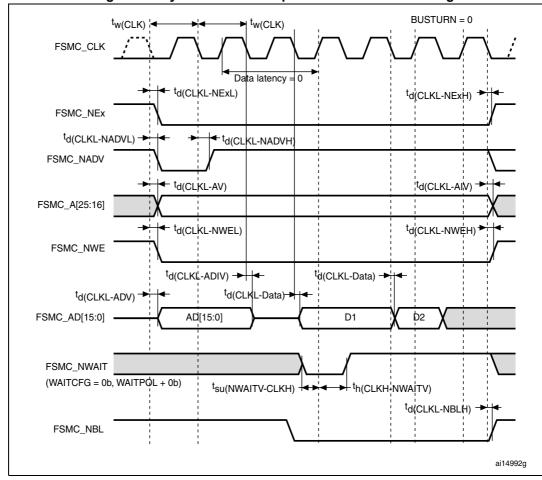

Figure 59. Synchronous multiplexed PSRAM write timings

Table 80. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                     | Parameter                                    | Min                | Max | Unit |

|----------------------------|----------------------------------------------|--------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                              | 2T <sub>HCLK</sub> | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)          | -                  | 1   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02)        | 1                  | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low                | -                  | 0   | ns   |

| t <sub>d(CLKL</sub> -      | FSMC_CLK low to FSMC_NADV high               | 0                  | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)       | -                  | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625)     | 8                  | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>  | FSMC_CLK low to FSMC_NWE low                 | -                  | 0.5 | ns   |

| t <sub>d(CLKL-NWEH)</sub>  | FSMC_CLK low to FSMC_NWE high                | 0                  | -   | ns   |

| t <sub>d(CLKL-ADIV)</sub>  | FSMC_CLK low to FSMC_AD[15:0] invalid        | 0                  | -   | ns   |

| t <sub>d(CLKL-DATA)</sub>  | FSMC_A/D[15:0] valid data after FSMC_CLK low | -                  | 3   | ns   |

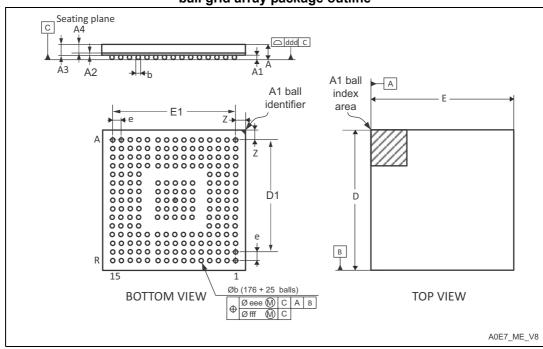

# 6.5 UFBGA176+25 package information

Figure 87. UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

Table 95. UFBGA176+25 ball,  $10 \times 10 \times 0.65$  mm pitch, ultra thin fine pitch ball grid array mechanical data

| ban gira array moonamoar aaa |             |        |        |                       |        |        |  |

|------------------------------|-------------|--------|--------|-----------------------|--------|--------|--|

| Cumbal                       | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

| Symbol                       | Min         | Тур    | Max    | Min                   | Тур    | Max    |  |

| Α                            | -           | -      | 0.600  | -                     | -      | 0.0236 |  |

| A1                           | -           | -      | 0.110  | -                     | -      | 0.0043 |  |

| A2                           | -           | 0.130  | -      | -                     | 0.0051 | -      |  |

| A3                           | -           | 0.450  | -      | -                     | 0.0177 | -      |  |

| A4                           | -           | 0.320  | -      | -                     | 0.0126 | -      |  |

| b                            | 0.240       | 0.290  | 0.340  | 0.0094                | 0.0114 | 0.0134 |  |

| D                            | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |  |

| D1                           | -           | 9.100  | -      | -                     | 0.3583 | -      |  |

| E                            | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |  |

| E1                           | -           | 9.100  | -      | -                     | 0.3583 | -      |  |

| е                            |             | 0.650  | -      | -                     | 0.0256 |        |  |

| Z                            | -           | 0.450  | -      | -                     | 0.0177 | -      |  |

| ddd                          | -           | -      | 0.080  | -                     | -      | 0.0031 |  |

Table 100. Document revision history (continued)

| Updated Figure 87: UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package outline Updated Table 95: UFBGA176+25 ball, 10 x 10 x 0.65 mm pitch, ultra thin fine pitch ball grid array mechanical data Updated Figure 5: STM32F41xxx block diagram Updated Section 2: Description Updated Section 2: Description Updated Figure 3: Compatible board design between STM32F41xxx for LQFP144 package Updated Figure 4: Compatible board design between STM32F2 and STM32F41xxx for LQFP144 package Updated Figure 4: Compatible board design between STM32F2 and STM32F41xxx for LQFP176 and BGA176 packages Updated Section 2.2.14: Power supply schemes Updated Section 2.2.15: Power supply supervisor Updated Section 2.2.16: Voltage regulator, including figures. Updated Table 14: General operating conditions, including footnote (2). Updated Table 14: General operating conditions, including footnote (2). Updated Table 15: Limitations depending on the operating power supply range, including footnote (3). Updated footnote (1) in Table 67: ADC characteristics. Updated footnote (2) in Table 68: ADC accuracy at IADC = 30 MHz. Updated Figure 9: Regulator OFF. Updated Figure 9: Regulator OFF. Added Section 2.2.17: Regulator ON/OFF and internal reset ON/OFF availability. Updated Figure 9: Power supply supervisor interconnection with internal reset OFF. Added Section 2.2.17: Regulator ON/OFF and internal reset ON/OFF availability. Updated footnote (2) of Figure 21: Power supply scheme. Replaced respectively "12S3S_WS" by "12S3_WS", "12S3S_CK" by "12S3_CK" and "FSMC_BLN1" by "FSMC_NBL1" in Table 9: Alternate function mapping Replaced "DCM_12" by "DCMI_D12" in Table 7: STM32F41xxx pin and ball definitions. Removed the following sentence from Section : 12C interface | Date Rev    | vision   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |