Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 140                                                                                       |

| Program Memory Size        | 1MB (1M × 8)                                                                              |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192К х 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 201-UFBGA                                                                                 |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f417igh6w                    |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.1 Full compatibility throughout the family

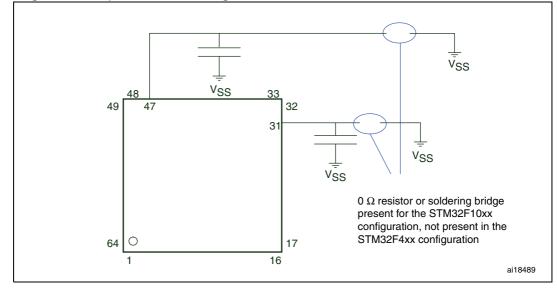

The STM32F415xx and STM32F417xx are part of the STM32F4 family. They are fully pinto-pin, software and feature compatible with the STM32F2xx devices, allowing the user to try different memory densities, peripherals, and performances (FPU, higher frequency) for a greater degree of freedom during the development cycle.

The STM32F415xx and STM32F417xx devices maintain a close compatibility with the whole STM32F10xxx family. All functional pins are pin-to-pin compatible. The STM32F415xx and STM32F417xx, however, are not drop-in replacements for the STM32F10xxx devices: the two families do not have the same power scheme, and so their power pins are different. Nonetheless, transition from the STM32F10xxx to the STM32F41xxx family remains simple as only a few pins are impacted.

*Figure 4*, *Figure 3*, *Figure 2*, and *Figure 1* give compatible board designs between the STM32F41xxx, STM32F2, and STM32F10xxx families.

Figure 1. Compatible board design between STM32F10xx/STM32F41xxx for LQFP64

# 2.2.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 2.2.6 Embedded SRAM

All STM32F41xxx products embed:

• Up to 192 Kbytes of system SRAM including 64 Kbytes of CCM (core coupled memory) data RAM

RAM memory is accessed (read/write) at CPU clock speed with 0 wait states.

• 4 Kbytes of backup SRAM

This area is accessible only from the CPU. Its content is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

## 2.2.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS) and the slaves (Flash memory, RAM, FSMC, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

### General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F41xxx devices (see *Table 4* for differences).

### • TIM2, TIM3, TIM4, TIM5

The STM32F41xxx include 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-

bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

### • TIM9, TIM10, TIM11, TIM12, TIM13, and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13, and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

TIM6 and TIM7 support independent DMA request generation.

### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

### SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

## 2.2.22 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to three I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support the Standard-mode (up to 100 kHz) and Fast-mode (up to 400 kHz). They support the 7/10-bit addressing mode and the 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

### 2.2.23 Universal synchronous/asynchronous receiver transmitters (USART)

The STM32F415xx and STM32F417xx embed four universal synchronous/asynchronous receiver transmitters (USART1, USART2, USART3 and USART6) and two universal asynchronous receiver transmitters (UART4 and UART5).

These six interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to communicate at speeds of up to 10.5 Mbit/s. The other available interfaces communicate at up to 5.25 Mbit/s.

USART1, USART2, USART3 and USART6 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller.

|        | I       | Pin r   | numb    | er       |         |                                                      |                                          |                 |       |                                                                                                            |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|------------------------------------------|-----------------|-------|------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type                                 | I / O structure | Notes | Alternate functions                                                                                        | Additional<br>functions |

| 29     | H4      | 47      | 69      | R12      | 79      | PB10                                                 | I/O                                      | FT              | -     | SPI2_SCK / I2S2_CK /<br>I2C2_SCL/ USART3_TX /<br>OTG_HS_ULPI_D3 /<br>ETH_MII_RX_ER /<br>TIM2_CH3/ EVENTOUT | _                       |

| 30     | J4      | 48      | 70      | R13      | 80      | PB11                                                 | I/O                                      | FT              | -     | I2C2_SDA/USART3_RX/<br>OTG_HS_ULPI_D4 /<br>ETH_RMII_TX_EN/<br>ETH_MII_TX_EN /<br>TIM2_CH4/ EVENTOUT        | -                       |

| 31     | F4      | 49      | 71      | M10      | 81      | V <sub>CAP_1</sub>                                   | S                                        |                 | -     | -                                                                                                          | _                       |

| 32     | -       | 50      | 72      | N10      | 82      | V <sub>DD</sub>                                      | S                                        |                 | -     | -                                                                                                          | -                       |

| -      | -       | -       | -       | M11      | 83      | PH6                                                  | I/O                                      | FT              | -     | I2C2_SMBA / TIM12_CH1 /<br>ETH_MII_RXD2/<br>EVENTOUT                                                       | -                       |

| -      | -       | -       | -       | N12      | 84      | PH7                                                  | I/O                                      | FT              | -     | I2C3_SCL /<br>ETH_MII_RXD3/<br>EVENTOUT                                                                    | -                       |

| -      | -       | -       | -       | M12      | 85      | PH8                                                  | I/O                                      | FT              | -     | I2C3_SDA /<br>DCMI_HSYNC/<br>EVENTOUT                                                                      | -                       |

| -      | -       | -       | -       | M13      | 86      | PH9                                                  | I/O                                      | FT              | -     | I2C3_SMBA / TIM12_CH2/<br>DCMI_D0/ EVENTOUT                                                                | -                       |

| -      | -       | -       | -       | L13      | 87      | PH10                                                 | I/O FT - TIM5_CH1 / DCMI_D1/<br>EVENTOUT |                 | -     |                                                                                                            |                         |

| -      | -       | -       | -       | L12      | 88      | PH11                                                 | I/O FT - TIM5_CH2 / DCMI_D2/<br>EVENTOUT |                 | -     |                                                                                                            |                         |

| -      | -       | -       | -       | K12      | 89      | PH12                                                 | I/O FT - TIM5_CH3 / DCMI_D3/<br>EVENTOUT |                 | -     |                                                                                                            |                         |

| -      | -       | -       | -       | H12      | 90      | $V_{SS}$                                             | S                                        |                 | -     | -                                                                                                          |                         |

| -      | -       | -       | -       | J12      | 91      | $V_{DD}$                                             | S                                        | -               | -     | -                                                                                                          | -                       |

Table 7. STM32F41xxx pin and ball definitions (continued)

Г

|        | I       | Pin r   | numb    | er       |         |                                                      |          |                 |       |                                                                                  |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|----------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                              | Additional<br>functions |

| -      | -       | 60      | 82      | M15      | 101     | PD13                                                 | I/O      | FT              | -     | FSMC_A18/TIM4_CH2/<br>EVENTOUT                                                   | -                       |

| -      | -       | -       | 83      | -        | 102     | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                | -                       |

| -      | -       | -       | 84      | J13      | 103     | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                | -                       |

| -      | F2      | 61      | 85      | M14      | 104     | PD14                                                 | I/O      | FT              | -     | FSMC_D0/TIM4_CH3/<br>EVENTOUT/ EVENTOUT                                          | -                       |

| -      | F1      | 62      | 86      | L14      | 105     | PD15                                                 | I/O      | FT              | -     | FSMC_D1/TIM4_CH4/<br>EVENTOUT                                                    | -                       |

| -      | -       | -       | 87      | L15      | 106     | PG2                                                  | I/O      | FT              | -     | FSMC_A12/ EVENTOUT                                                               | -                       |

| -      | -       | -       | 88      | K15      | 107     | PG3                                                  | I/O      | FT              | -     | FSMC_A13/ EVENTOUT                                                               | -                       |

| -      | -       | -       | 89      | K14      | 108     | PG4                                                  | I/O      | FT              | -     | FSMC_A14/ EVENTOUT                                                               | -                       |

| -      | -       | -       | 90      | K13      | 109     | PG5                                                  | I/O      | FT              | -     | FSMC_A15/ EVENTOUT                                                               | -                       |

| -      | -       | -       | 91      | J15      | 110     | PG6                                                  | I/O      | FT              | -     | FSMC_INT2/ EVENTOUT                                                              | -                       |

| -      | -       | -       | 92      | J14      | 111     | PG7                                                  | I/O      | FT              | -     | FSMC_INT3/USART6_CK/<br>EVENTOUT                                                 | -                       |

| -      | -       | -       | 93      | H14      | 112     | PG8                                                  | I/O      | FT              | -     | USART6_RTS /<br>ETH_PPS_OUT/<br>EVENTOUT                                         | -                       |

| -      | -       | -       | 94      | G12      | 113     | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                | -                       |

| -      | -       | -       | 95      | H13      | 114     | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                | -                       |

| 37     | F3      | 63      | 96      | H15      | 115     | PC6                                                  | I/O      | FT              | -     | I2S2_MCK /<br>TIM8_CH1/SDIO_D6 /<br>USART6_TX /<br>DCMI_D0/TIM3_CH1/<br>EVENTOUT | -                       |

| 38     | E1      | 64      | 97      | G15      | 116     | PC7                                                  | I/O      | FT              | -     | I2S3_MCK /<br>TIM8_CH2/SDIO_D7 /<br>USART6_RX /<br>DCMI_D1/TIM3_CH2/<br>EVENTOUT | -                       |

| 39     | E2      | 65      | 98      | G14      | 117     | PC8                                                  | I/O      | FT              | -     | TIM8_CH3/SDIO_D0<br>/TIM3_CH3/ USART6_CK /<br>DCMI_D2/ EVENTOUT                  | -                       |

| Table | 7. STM32F41xxx | pin | and | ball ( | definitions | (continued) |

|-------|----------------|-----|-----|--------|-------------|-------------|

|       |                |     |     |        |             |             |

|        | Table 7. STM32F41xxx pin and ball definitions (continued)         Pin number |         |         |          |         |                                                      |                                                                               |                 |       |                                                                          |                         |  |

|--------|------------------------------------------------------------------------------|---------|---------|----------|---------|------------------------------------------------------|-------------------------------------------------------------------------------|-----------------|-------|--------------------------------------------------------------------------|-------------------------|--|

| LQFP64 | WLCSP90                                                                      | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type                                                                      | I / O structure | Notes | Alternate functions                                                      | Additional<br>functions |  |

| -      | A4                                                                           | 85      | 118     | D10      | 146     | PD4                                                  | I/O                                                                           | FT              | -     | FSMC_NOE/<br>USART2_RTS/<br>EVENTOUT                                     | -                       |  |

| -      | C6                                                                           | 86      | 119     | C11      | 147     | PD5                                                  | I/O                                                                           | FT              | -     | FSMC_NWE/USART2_TX/<br>EVENTOUT                                          | -                       |  |

| -      | -                                                                            | -       | 120     | D8       | 148     | V <sub>SS</sub>                                      | S                                                                             | -               | -     | -                                                                        | -                       |  |

| -      | -                                                                            | -       | 121     | C8       | 149     | V <sub>DD</sub>                                      | S                                                                             | -               | -     | -                                                                        | -                       |  |

| -      | B5                                                                           | 87      | 122     | B11      | 150     | PD6                                                  | I/O                                                                           | FT              | -     | FSMC_NWAIT/<br>USART2_RX/ EVENTOUT                                       | -                       |  |

| -      | A5                                                                           | 88      | 123     | A11      | 151     | PD7                                                  | I/O                                                                           | FT              | -     | USART2_CK/FSMC_NE1/<br>FSMC_NCE2/ EVENTOUT                               | -                       |  |

| -      | -                                                                            | -       | 124     | C10      | 152     | PG9                                                  | I/O                                                                           | FT              | -     | USART6_RX /<br>FSMC_NE2/FSMC_NCE3/<br>EVENTOUT                           | -                       |  |

| -      | -                                                                            | -       | 125     | B10      | 153     | PG10                                                 | I/O                                                                           | FT              | -     | FSMC_NCE4_1/<br>FSMC_NE3/ EVENTOUT                                       | -                       |  |

| -      | -                                                                            | -       | 126     | В9       | 154     | PG11                                                 | I/O                                                                           | FT              | -     | FSMC_NCE4_2 /<br>ETH_MII_TX_EN/<br>ETH_RMII_TX_EN/<br>EVENTOUT           | -                       |  |

| -      | -                                                                            | -       | 127     | B8       | 155     | PG12                                                 | I/O                                                                           | FT              | -     | FSMC_NE4 /<br>USART6_RTS/<br>EVENTOUT                                    | -                       |  |

| -      | -                                                                            | -       | 128     | A8       | 156     | PG13                                                 | I/O                                                                           | FT              | -     | FSMC_A24 /<br>USART6_CTS<br>/ETH_MII_TXD0/<br>ETH_RMII_TXD0/<br>EVENTOUT | -                       |  |

| -      | -                                                                            | -       | 129     | A7       | 157     | PG14                                                 | I/O FT - FSMC_A25 / USART6_TX<br>/ETH_MII_TXD1/<br>ETH_RMII_TXD1/<br>EVENTOUT |                 | -     |                                                                          |                         |  |

| -      | E8                                                                           | -       | 130     | D7       | 158     | V <sub>SS</sub>                                      | S                                                                             |                 | -     |                                                                          |                         |  |

| -      | F7                                                                           | -       | 131     | C7       | 159     | V <sub>DD</sub>                                      | S                                                                             |                 | -     | _                                                                        |                         |  |

| -      | -                                                                            | -       | 132     | B7       | 160     | PG15                                                 | I/O                                                                           | FT              | -     | USART6_CTS /<br>DCMI_D13/ EVENTOUT                                       | -                       |  |

Table 7. STM32F41xxx pin and ball definitions (continued)

70/206

DocID022063 Rev 8

|        |      |     |        |          |                  |               |                                | I                    |                        |                    | -                         |                   |      |                      |          |      |          |

|--------|------|-----|--------|----------|------------------|---------------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|-------------------|------|----------------------|----------|------|----------|

|        |      | AF0 | AF1    | AF2      | AF3              | AF4           | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10              | AF11 | AF12                 | AF13     |      |          |

| Po     | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3      | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS | ЕТН  | FSMC/SDIO<br>/OTG_FS | DCMI     | AF14 | AF15     |

|        | PF0  | -   | -      | -        | -                | I2C2_SDA      | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A0              | -        | -    | EVENTOUT |

|        | PF1  | -   | -      | -        | -                | I2C2_SCL      | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A1              | -        | -    | EVENTOUT |

|        | PF2  | -   | -      | -        | -                | I2C2_<br>SMBA | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A2              | -        | -    | EVENTOUT |

|        | PF3  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A3              | -        | -    | EVENTOUT |

|        | PF4  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A4              | -        | -    | EVENTOUT |

|        | PF5  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A5              | -        | -    | EVENTOUT |

|        | PF6  | -   | -      | -        | TIM10_CH1        | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_NIORD           | -        | -    | EVENTOUT |

| Port F | PF7  | -   | -      | -        | TIM11_CH1        | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_NREG            | -        | -    | EVENTOUT |

| Ροπι   | PF8  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | TIM13_CH1                 | -                 | -    | FSMC_<br>NIOWR       | -        | -    | EVENTOUT |

|        | PF9  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | TIM14_CH1                 | -                 | -    | FSMC_CD              | -        | -    | EVENTOUT |

|        | PF10 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_INTR            | -        | -    | EVENTOUT |

|        | PF11 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    |                      | DCMI_D12 | -    | EVENTOUT |

|        | PF12 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A6              | -        | -    | EVENTOUT |

|        | PF13 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A7              | -        | -    | EVENTOUT |

|        | PF14 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A8              | -        | -    | EVENTOUT |

|        | PF15 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A9              | -        | -    | EVENTOUT |

Table 9. Alternate function mapping (continued)

|        |      |     | 1   | 1   | 1   | Tac | DIE 9. AIT | ernate fi | inction m | apping         | (contin          | uea)     | 1                                     | 1                            |                        | 1                  | 1                         |                   |     |                      |      |      |      |

|--------|------|-----|-----|-----|-----|-----|------------|-----------|-----------|----------------|------------------|----------|---------------------------------------|------------------------------|------------------------|--------------------|---------------------------|-------------------|-----|----------------------|------|------|------|

|        |      | AF0 | AF1 | AF2 | AF3 | AF4 | AF5        | AF6       | AF7       | AF8            | AF9              | AF10     | AF11                                  | AF12                         | AF13                   |                    |                           |                   |     |                      |      |      |      |

| Port   |      | SYS | SYS | SYS | SYS | SYS | SYS        | SYS       | TIM1/2    | TIM3/4/5       | TIM8/9/10<br>/11 | I2C1/2/3 | SPI1/SPI2/<br>I2S2/I2S2e<br>xt        | SPI3/I2Sext<br>/I2S3         | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS | ЕТН | FSMC/SDIO<br>/OTG_FS | DCMI | AF14 | AF15 |

|        | PG0  | -   | -   | -   | -   | -   | -          | -         | -         | -              | -                | -        | -                                     | FSMC_A10                     | -                      | -                  | EVENT                     |                   |     |                      |      |      |      |

|        | PG1  | -   | -   | -   | -   | -   | -          | -         | -         | -              | -                | -        | -                                     | FSMC_A11                     | -                      | -                  | EVEN                      |                   |     |                      |      |      |      |

|        | PG2  | -   | -   | -   | -   | -   | -          | -         | -         | -              | -                | -        | -                                     | FSMC_A12                     | -                      | -                  | EVEN                      |                   |     |                      |      |      |      |

|        | PG3  | -   | -   | -   | -   | -   | -          | -         | -         | -              | -                | -        | -                                     | FSMC_A13                     | -                      | -                  | EVEN                      |                   |     |                      |      |      |      |

|        | PG4  | -   | -   | -   | -   | -   | -          | -         | -         | -              | -                | -        | -                                     | FSMC_A14                     | -                      | -                  | EVEN                      |                   |     |                      |      |      |      |

|        | PG5  | -   | -   | -   | -   | -   | -          | -         | -         | -              | -                | -        | -                                     | FSMC_A15                     | -                      | -                  | EVEN                      |                   |     |                      |      |      |      |

|        | PG6  | -   | -   | -   | -   | -   | -          | -         | -         | -              | -                | -        | -                                     | FSMC_INT2                    | -                      | -                  | EVEN                      |                   |     |                      |      |      |      |

|        | PG7  | -   | -   | -   | -   | -   | -          | -         | -         | USART6_CK      | -                | -        | -                                     | FSMC_INT3                    | -                      | -                  | EVEN                      |                   |     |                      |      |      |      |

|        | PG8  | -   | -   | -   | -   | -   | -          | -         | -         | USART6_<br>RTS | -                | -        | ETH_PPS_OUT                           | -                            | -                      | -                  | EVEN                      |                   |     |                      |      |      |      |

| Port G | PG9  | -   | -   | -   | -   | -   | -          | -         | -         | USART6_RX      | -                | -        | -                                     | FSMC_NE2/<br>FSMC_NCE3       | -                      | -                  | EVEN                      |                   |     |                      |      |      |      |

|        | PG10 | -   | -   | -   | -   | -   | -          | -         | -         | -              | -                | -        | -                                     | FSMC_<br>NCE4_1/<br>FSMC_NE3 | -                      | -                  | EVEN                      |                   |     |                      |      |      |      |

|        | PG11 | -   | -   | -   | -   | -   | -          | -         | -         | -              | -                | -        | ETH _MII_TX_EN<br>ETH _RMII_<br>TX_EN | FSMC_NCE4_<br>2              | -                      | -                  | EVEN                      |                   |     |                      |      |      |      |

|        | PG12 | -   | -   | -   | -   | -   | -          | -         | -         | USART6_<br>RTS | -                | -        | -                                     | FSMC_NE4                     | -                      | -                  | EVE                       |                   |     |                      |      |      |      |

|        | PG13 | -   | -   | -   | -   | -   | -          | -         | -         | UART6_CTS      | -                | -        | ETH _MII_TXD0<br>ETH _RMII_TXD0       | FSMC_A24                     | -                      | -                  | EVE                       |                   |     |                      |      |      |      |

|        | PG14 | -   | -   | -   | -   | -   | -          | -         | -         | USART6_TX      | -                | -        | ETH _MII_TXD1<br>ETH _RMII_TXD1       | FSMC_A25                     | -                      | -                  | EVE                       |                   |     |                      |      |      |      |

|        | PG15 | -   | -   | -   | -   | -   | -          | -         | -         | USART6_<br>CTS | -                | -        | -                                     | -                            | DCMI_D13               | -                  | EVE                       |                   |     |                      |      |      |      |

### Table 9. Alternate function mapping (continued)

5

DocID022063 Rev 8

71/206

Pinouts and pin description

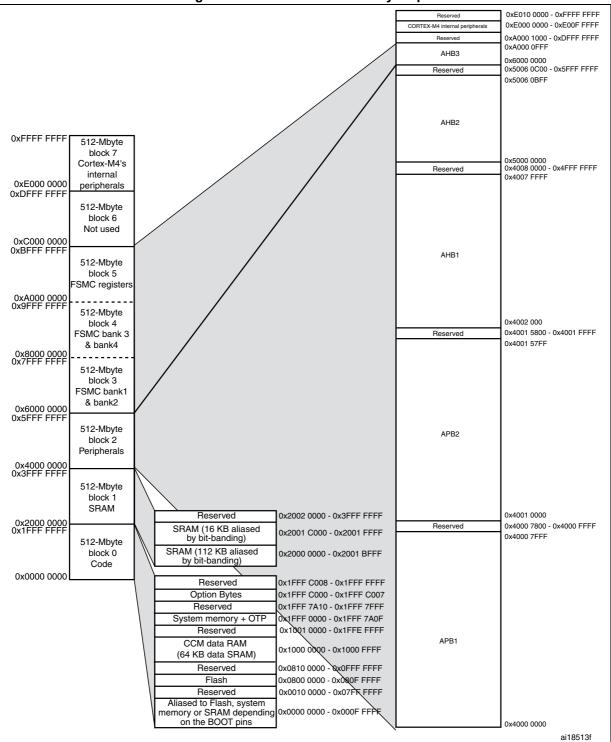

# 4 Memory mapping

The memory map is shown in *Figure 18*.

DocID022063 Rev 8

| Bus  | Boundary address          | Peripheral               |

|------|---------------------------|--------------------------|

|      | 0x4004 0000 - 0x4007 FFFF | USB OTG HS               |

|      | 0x4002 9400 - 0x4003 FFFF | Reserved                 |

|      | 0x4002 9000 - 0x4002 93FF |                          |

|      | 0x4002 8C00 - 0x4002 8FFF |                          |

|      | 0x4002 8800 - 0x4002 8BFF | ETHERNET MAC             |

|      | 0x4002 8400 - 0x4002 87FF |                          |

|      | 0x4002 8000 - 0x4002 83FF |                          |

|      | 0x4002 6800 - 0x4002 7FFF | Reserved                 |

|      | 0x4002 6400 - 0x4002 67FF | DMA2                     |

|      | 0x4002 6000 - 0x4002 63FF | DMA1                     |

|      | 0x4002 5000 - 0x4002 5FFF | Reserved                 |

|      | 0x4002 4000 - 0x4002 4FFF | BKPSRAM                  |

| AHB1 | 0x4002 3C00 - 0x4002 3FFF | Flash interface register |

| ANDI | 0x4002 3800 - 0x4002 3BFF | RCC                      |

|      | 0x4002 3400 - 0x4002 37FF | Reserved                 |

|      | 0x4002 3000 - 0x4002 33FF | CRC                      |

|      | 0x4002 2400 - 0x4002 2FFF | Reserved                 |

|      | 0x4002 2000 - 0x4002 23FF | GPIOI                    |

|      | 0x4002 1C00 - 0x4002 1FFF | GPIOH                    |

|      | 0x4002 1800 - 0x4002 1BFF | GPIOG                    |

|      | 0x4002 1400 - 0x4002 17FF | GPIOF                    |

|      | 0x4002 1000 - 0x4002 13FF | GPIOE                    |

|      | 0x4002 0C00 - 0x4002 0FFF | GPIOD                    |

|      | 0x4002 0800 - 0x4002 0BFF | GPIOC                    |

|      | 0x4002 0400 - 0x4002 07FF | GPIOB                    |

|      | 0x4002 0000 - 0x4002 03FF | GPIOA                    |

|      | 0x4001 5800- 0x4001 FFFF  | Reserved                 |

Table 10. STM32F41x register boundary addresses (continued)

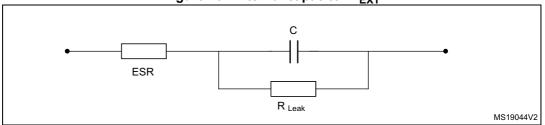

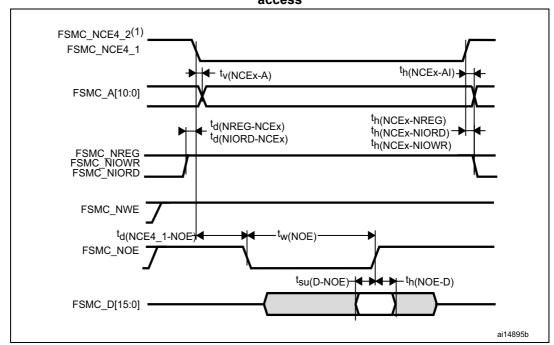

# 5.3.2 V<sub>CAP\_1</sub>/V<sub>CAP\_2</sub> external capacitor

Stabilization for the main regulator is achieved by connecting an external capacitor  $C_{EXT}$  to the  $V_{CAP\_2}$  pins.  $C_{EXT}$  is specified in *Table 16*.

1. Legend: ESR is the equivalent series resistance.

Table 16.  $V_{CAP}$   $_1/V_{CAP}$   $_2$  operating conditions<sup>(1)</sup>

| Symbol | Parameter                         | Conditions |

|--------|-----------------------------------|------------|

| CEXT   | Capacitance of external capacitor | 2.2 µF     |

| ESR    | ESR of external capacitor         | < 2 Ω      |

1. When bypassing the voltage regulator, the two 2.2  $\mu$ F V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

# 5.3.3 Operating conditions at power-up / power-down (regulator ON)

Subject to general operating conditions for  $T_A$ .

| Table 17. Operating conditions at power-up | / power-down (regulator ON) |

|--------------------------------------------|-----------------------------|

|--------------------------------------------|-----------------------------|

| Symbol           | Parameter                      | Min | Мах | Unit  |

|------------------|--------------------------------|-----|-----|-------|

|                  | V <sub>DD</sub> rise time rate | 20  | ∞   | µs/V  |

| <sup>L</sup> VDD | V <sub>DD</sub> fall time rate | 20  | ∞   | μ3/ ν |

# 5.3.4 Operating conditions at power-up / power-down (regulator OFF)

Subject to general operating conditions for T<sub>A</sub>.

### Table 18. Operating conditions at power-up / power-down (regulator OFF)<sup>(1)</sup>

| Symbol            | Parameter                                    | Conditions | Min | Max | Unit |

|-------------------|----------------------------------------------|------------|-----|-----|------|

| +                 | V <sub>DD</sub> rise time rate               | Power-up   | 20  | ∞   |      |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate               | Power-down | 20  | ∞   |      |

| +                 | $V_{CAP\_1}$ and $V_{CAP\_2}$ rise time rate | Power-up   | 20  | 8   | µs/V |

| t <sub>VCAP</sub> | $V_{CAP\_1}$ and $V_{CAP\_2}$ fall time rate | Power-down | 20  | 8   |      |

1. To reset the internal logic at power-down, a reset must be applied on pin PA0 when  $V_{DD}$  reach below minimum value of  $V_{12}$ .

|                 |                                                                                                                                                           | om Flash memory (ART a                                                    |                       | Тур                       | Max <sup>(2)</sup>        |                            |      |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter                                                                                                                                                 | Conditions                                                                | f <sub>HCLK</sub>     | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                                                                                                                                                           |                                                                           | 168 MHz               | 87                        | 102                       | 109                        |      |

|                 |                                                                                                                                                           |                                                                           | 144 MHz               | 67                        | 80                        | 86                         |      |

|                 |                                                                                                                                                           |                                                                           | 120 MHz               | 56                        | 69                        | 75                         |      |

|                 |                                                                                                                                                           |                                                                           | 90 MHz                | 44                        | 56                        | 62                         |      |

|                 |                                                                                                                                                           | - (2)                                                                     | 60 MHz                | 30                        | 42                        | 49                         |      |

|                 |                                                                                                                                                           | External clock <sup>(3)</sup> , all peripherals enabled <sup>(4)(5)</sup> | 30 MHz                | 16                        | 28                        | 35                         |      |

|                 |                                                                                                                                                           |                                                                           | 25 MHz                | 12                        | 24                        | 31                         |      |

|                 | 16 MHz <sup>(6)</sup> 9<br>8 MHz 5                                                                                                                        | 9                                                                         | 20                    | 28                        |                           |                            |      |

|                 |                                                                                                                                                           |                                                                           | 8 MHz                 | 5                         | 17                        | 24                         | - mA |

|                 |                                                                                                                                                           |                                                                           | 4 MHz                 | 3                         | 15                        | 22                         |      |

|                 | Supply current in                                                                                                                                         |                                                                           | 2 MHz                 | 2                         | 14                        | 21                         |      |

| I <sub>DD</sub> | Run mode                                                                                                                                                  |                                                                           | 168 MHz               | 40                        | 54                        | 61                         |      |

|                 |                                                                                                                                                           |                                                                           | 144 MHz               | 31                        | 43                        | 50                         |      |

|                 |                                                                                                                                                           |                                                                           | 120 MHz               | 26                        | 38                        | 45                         |      |

|                 | Sector         90 MHz         20           60 MHz         14           Beripherals disabled <sup>(4)(5)</sup> 30 MHz         8           25 MHz         6 | 20                                                                        | 32                    | 39                        |                           |                            |      |

|                 |                                                                                                                                                           | 60 MHz                                                                    | 14                    | 26                        | 33                        | 1                          |      |

|                 |                                                                                                                                                           |                                                                           |                       | 8                         | 20                        | 27                         |      |

|                 |                                                                                                                                                           |                                                                           | 25 MHz                | 6                         | 18                        | 25                         |      |

|                 |                                                                                                                                                           |                                                                           | 16 MHz <sup>(6)</sup> | 5                         | 16                        | 24                         |      |

|                 |                                                                                                                                                           |                                                                           | 8 MHz                 | 3                         | 15                        | 22                         |      |

|                 |                                                                                                                                                           |                                                                           | 4 MHz                 | 2                         | 14                        | 21                         |      |

|                 |                                                                                                                                                           |                                                                           | 2 MHz                 | 2                         | 14                        | 21                         |      |

# Table 20. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator enabled) or RAM <sup>(1)</sup>

1. Code and data processing running from SRAM1 using boot pins.

2. Guaranteed by characterization, tested in production at V<sub>DD</sub> max and f<sub>HCLK</sub> max with peripherals enabled.

3. External clock is 4 MHz and PLL is on when  $f_{HCLK}$  > 25 MHz.

4. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

5. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

6. In this case HCLK = system clock/2.

### **Electrical characteristics**

| Symbol            | Parameter                                                   | Conditions <sup>(1)</sup>     | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур  | Unit |

|-------------------|-------------------------------------------------------------|-------------------------------|----------------------------------------------|------|------|

|                   |                                                             |                               | 2 MHz                                        | 0.02 |      |

|                   | $V_{DD} = 3.3 V^{(2)}$ 8 MHz<br>C = C <sub>INT</sub> 25 MHz | 0.14                          |                                              |      |      |

|                   |                                                             | 0.51                          |                                              |      |      |

|                   |                                                             |                               | 50 MHz                                       | 0.86 |      |

|                   |                                                             |                               | 60 MHz                                       | 1.30 |      |

|                   |                                                             |                               | 2 MHz                                        | 0.10 |      |

|                   |                                                             | V <sub>DD</sub> = 3.3 V       | 8 MHz                                        | 0.38 |      |

|                   |                                                             | C <sub>EXT</sub> = 0 pF       | 25 MHz                                       | 1.18 |      |

|                   |                                                             | $C = C_{INT} + C_{EXT} + C_S$ | 50 MHz                                       | 2.47 |      |

|                   |                                                             |                               | 60 MHz                                       | 2.86 |      |

|                   |                                                             |                               | 2 MHz                                        | 0.17 |      |

|                   | I/O switching                                               | V <sub>DD</sub> = 3.3 V       | 8 MHz                                        | 0.66 |      |

| I <sub>DDIO</sub> | current                                                     | C <sub>EXT</sub> = 10 pF      | 25 MHz                                       | 1.70 | mA   |

|                   |                                                             | $C = C_{INT} + C_{EXT} + C_S$ | 50 MHz                                       | 2.65 |      |

|                   |                                                             |                               | 60 MHz                                       | 3.48 |      |

|                   |                                                             |                               | 2 MHz                                        | 0.23 |      |

|                   |                                                             | V <sub>DD</sub> = 3.3 V       | 8 MHz                                        | 0.95 |      |

|                   |                                                             | C <sub>EXT</sub> = 22 pF      | 25 MHz                                       | 3.20 |      |

|                   |                                                             | $C = C_{INT} + C_{EXT} + C_S$ | 50 MHz                                       | 4.69 |      |

|                   |                                                             |                               | 60 MHz                                       | 8.06 |      |

|                   |                                                             |                               | 2 MHz                                        | 0.30 |      |

|                   |                                                             | V <sub>DD</sub> = 3.3 V       | 8 MHz                                        | 1.22 |      |

|                   |                                                             | C <sub>EXT</sub> = 33 pF      | 25 MHz                                       | 3.90 |      |

|                   |                                                             | $C = C_{INT} + C_{EXT} + C_S$ | 50 MHz                                       | 8.82 |      |

|                   |                                                             |                               | 60 MHz                                       | _(3) | 1    |

1.  $C_S$  is the PCB board capacitance including the pad pin.  $C_S$  = 7 pF (estimated value).

2. This test is performed by cutting the LQFP package pin (pad removal).

3. At 60 MHz, C maximum load is specified 30 pF.

| Symbol                 | Parameter                                                         | Conditions                                                      | Min  | Мах                     | Unit                 |

|------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------|------|-------------------------|----------------------|

|                        |                                                                   | AHB/APB2                                                        | 1    | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time                                             | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>168 MHz | 5.95 | -                       | ns                   |

|                        |                                                                   | AHB/APB2                                                        | 1    | -                       | t <sub>TIMxCLK</sub> |

|                        |                                                                   | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 84 MHz                 | 11.9 | -                       | ns                   |

|                        | Timer external clock                                              |                                                                 | 0    | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>       | frequency on CH1 to<br>CH4                                        |                                                                 | 0    | 84                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                                                  | f <sub>TIMxCLK</sub> =<br>168 MHz                               | -    | 16                      | bit                  |

| t <sub>COUNTER</sub>   | 16-bit counter clock<br>period when internal<br>clock is selected | APB2 = 84 MHz                                                   | 1    | 65536                   | t <sub>TIMxCLK</sub> |

| t <sub>MAX_COUNT</sub> | Maximum possible count                                            |                                                                 | -    | 32768                   | t <sub>TIMxCLK</sub> |

Table 53. Characteristics of TIMx connected to the APB2 domain<sup>(1)</sup>

1. TIMx is used as a general term to refer to the TIM1, TIM8, TIM9, TIM10, and TIM11 timers.

# 5.3.19 Communications interfaces

# I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to RM0090 reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present. Refer to Section 5.3.16: I/O port characteristics for more details on the I<sup>2</sup>C I/O characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

| Symbol          | Parameter                                                                    | Min               | Мах                | Unit |

|-----------------|------------------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes<br>that are suppressed by the analog<br>filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

Table 54. I2C analog filter characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

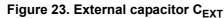

Figure 41. SPI timing diagram - master mode

## PC Card/CompactFlash controller waveforms and timings

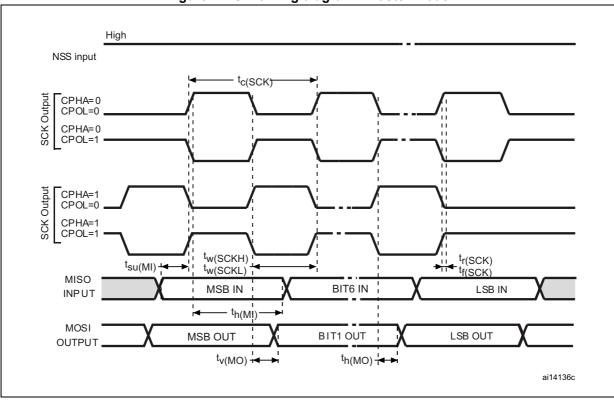

*Figure 62* through *Figure 67* represent synchronous waveforms, and *Table 83* and *Table 84* provide the corresponding timings. The results shown in this table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x04;

- COM.FSMC\_WaitSetupTime = 0x07;

- COM.FSMC\_HoldSetupTime = 0x04;

- COM.FSMC\_HiZSetupTime = 0x00;

- ATT.FSMC\_SetupTime = 0x04;

- ATT.FSMC\_WaitSetupTime = 0x07;

- ATT.FSMC\_HoldSetupTime = 0x04;

- ATT.FSMC\_HiZSetupTime = 0x00;

- IO.FSMC\_SetupTime = 0x04;

- IO.FSMC\_WaitSetupTime = 0x07;

- IO.FSMC\_HoldSetupTime = 0x04;

- IO.FSMC\_HiZSetupTime = 0x00;

- TCLRSetupTime = 0;

- TARSetupTime = 0.

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

# Figure 62. PC Card/CompactFlash controller waveforms for common memory read access

#### 1. FSMC\_NCE4\_2 remains high (inactive during 8-bit access.

|                   |       | расказ      | je mechanic |        |                       |        |

|-------------------|-------|-------------|-------------|--------|-----------------------|--------|

| Symbol            |       | millimeters |             |        | inches <sup>(1)</sup> |        |

| Symbol            | Min   | Тур         | Мах         | Min    | Тур                   | Max    |

| А                 | 0.540 | 0.570       | 0.600       | 0.0213 | 0.0224                | 0.0236 |

| A1                | -     | 0.190       | -           | -      | 0.0075                | -      |

| A2                | -     | 0.380       | -           | -      | 0.0150                | -      |

| A3 <sup>(2)</sup> | -     | 0.025       | -           | -      | 0.0010                | -      |

| b <sup>(3)</sup>  | 0.240 | 0.270       | 0.300       | 0.0094 | 0.0106                | 0.0118 |

| D                 | 4.188 | 4.223       | 4.258       | 0.1649 | 0.1663                | 0.1676 |

| E                 | 3.934 | 3.969       | 4.004       | 0.1549 | 0.1563                | 0.1576 |

| е                 | -     | 0.400       | -           | -      | 0.0157                | -      |

| e1                | -     | 3.600       | -           | -      | 0.1417                | -      |

| e2                | -     | 3.200       | -           | -      | 0.1260                | -      |

| F                 | -     | 0.3115      | -           | -      | 0.0123                | -      |

| G                 | -     | 0.3845      | -           | -      | 0.0151                | -      |

| aaa               | -     | 0.100       | -           | -      | 0.0039                | -      |

| bbb               | -     | 0.100       | -           | -      | 0.0039                | -      |

| ссс               | -     | 0.100       | -           | -      | 0.0039                | -      |

| ddd               | -     | 0.050       | -           | -      | 0.0020                | -      |

| eee               | -     | 0.050       | -           | -      | 0.0020                | -      |

# Table 90. WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch wafer level chip scale package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

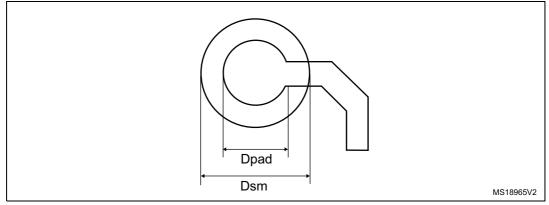

# Figure 76. WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch wafer level chip scale recommended footprint

| Date                | Revision                     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date<br>24-Jan-2012 | Revision<br>2<br>(continued) | Changes         Added V <sub>12</sub> in Table 19: Embedded reset and power control block characteristics.         Updated Table 21: Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled) and Table 20: Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator enabled) or RAM. Added Figure , Figure 25, Figure 26, and Figure 27.         Updated Table 22: Typical and maximum current consumption in Sleep mode and removed Note 1.         Updated Table 23: Typical and maximum current consumptions in Stop mode and Table 24: Typical and maximum current consumptions in Stop mode and Table 25: Typical and maximum current consumptions in Standby mode, Table 25: Typical and maximum current consumptions in Standby mode, Table 25: Typical and maximum current consumptions in Standby mode, and Table 27: Switching output I/O current consumption.         Section : On-chip peripheral current consumption: modified conditions, and updated Table 28: Peripheral current consumption and Note 2.         Changed f <sub>HSE_ext</sub> to 50 MHz and t <sub>r(HSE)</sub> /t <sub>f(HSE)</sub> maximum value in Table 30: High-speed external user clock characteristics.         Added C <sub>in(LSE)</sub> in Table 31: Low-speed external user clock characteristics.         Updated maximum PLL input clock frequency, removed related note, and deleted jitter for MCO for RMII Ethernet typical value in Table 36: Main PLL characteristics. Updated maximum PLLI2S input clock frequency and removed related note in Table 37: PLLI2S (audio PLL) characteristics.         Updated Section : Flash memory to specify that the devices are shipped to customers with the Flash memory erased. Updated Table 39: Fl |

Table 100. Document revision history (continued)

| Date |

|------|

| Date |