Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betano                     |                                                                                           |

|----------------------------|-------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                    |

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 140                                                                                       |

| Program Memory Size        | 1MB (1M × 8)                                                                              |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 176-LQFP                                                                                  |

| Supplier Device Package    | -                                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f417igt6                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 8- to 14-bit parallel camera interface up to 54 Mbytes/s

- Cryptographic acceleration: hardware acceleration for AES 128, 192, 256, Triple DES, HASH (MD5, SHA-1), and HMAC

- True random number generator

- CRC calculation unit

- 96-bit unique ID

- RTC: subsecond accuracy, hardware calendar

| Reference   | Part number                                                                  |

|-------------|------------------------------------------------------------------------------|

| STM32F415xx | STM32F415RG, STM32F415VG, STM32F415ZG, STM32F415OG                           |

| STM32F417xx | STM32F417VG, STM32F417IG, STM32F417ZG, STM32F417VE, STM32F417ZE, STM32F417IE |

# Table 1. Device summary

# 2.2.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core with FPU and embedded Flash and SRAM

The ARM Cortex-M4 processor with FPU is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM Cortex-M4 32-bit RISC processor with FPU features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F415xx and STM32F417xx family is compatible with all ARM tools and software.

*Figure 5* shows the general block diagram of the STM32F41xxx family.

Note: Cortex-M4 with FPU is binary compatible with Cortex-M3.

# 2.2.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processors. It balances the inherent performance advantage of the ARM Cortex-M4 with FPU over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor full 210 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 168 MHz.

# 2.2.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

# 2.2.4 Embedded Flash memory

The STM32F41xxx devices embed a Flash memory of 512 Kbytes or 1 Mbytes available for storing programs and data.

DocID022063 Rev 8

#### General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F41xxx devices (see *Table 4* for differences).

#### • TIM2, TIM3, TIM4, TIM5

The STM32F41xxx include 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-

bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

#### • TIM9, TIM10, TIM11, TIM12, TIM13, and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13, and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

#### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

TIM6 and TIM7 support independent DMA request generation.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

|        |      |     | 1      | 1        | 1                | Tac      | DIE 9. AIT                     | ernate fi            | inction m              | apping             | (contin                   | uea)              | 1                                     | 1                            |          | 1    | 1     |

|--------|------|-----|--------|----------|------------------|----------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|-------------------|---------------------------------------|------------------------------|----------|------|-------|

|        |      | AF0 | AF1    | AF2      | AF3              | AF4      | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10              | AF11                                  | AF12                         | AF13     |      |       |

| Port   | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3 | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS | ЕТН                                   | FSMC/SDIO<br>/OTG_FS         | DCMI     | AF14 | AF1   |

|        | PG0  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_A10                     | -        | -    | EVENT |

|        | PG1  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_A11                     | -        | -    | EVEN  |

|        | PG2  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_A12                     | -        | -    | EVEN  |

|        | PG3  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_A13                     | -        | -    | EVEN  |

|        | PG4  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_A14                     | -        | -    | EVEN  |

|        | PG5  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_A15                     | -        | -    | EVEN  |

|        | PG6  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_INT2                    | -        | -    | EVEN  |

|        | PG7  | -   | -      | -        | -                | -        | -                              | -                    | -                      | USART6_CK          | -                         | -                 | -                                     | FSMC_INT3                    | -        | -    | EVEN  |

|        | PG8  | -   | -      | -        | -                | -        | -                              | -                    | -                      | USART6_<br>RTS     | -                         | -                 | ETH_PPS_OUT                           | -                            | -        | -    | EVEN  |

| Port G | PG9  | -   | -      | -        | -                | -        | -                              | -                    | -                      | USART6_RX          | -                         | -                 | -                                     | FSMC_NE2/<br>FSMC_NCE3       | -        | -    | EVEN  |

|        | PG10 | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_<br>NCE4_1/<br>FSMC_NE3 | -        | -    | EVEN  |

|        | PG11 | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | ETH _MII_TX_EN<br>ETH _RMII_<br>TX_EN | FSMC_NCE4_<br>2              | -        | -    | EVEN  |

|        | PG12 | -   | -      | -        | -                | -        | -                              | -                    | -                      | USART6_<br>RTS     | -                         | -                 | -                                     | FSMC_NE4                     | -        | -    | EVE   |

|        | PG13 | -   | -      | -        | -                | -        | -                              | -                    | -                      | UART6_CTS          | -                         | -                 | ETH _MII_TXD0<br>ETH _RMII_TXD0       | FSMC_A24                     | -        | -    | EVE   |

|        | PG14 | -   | -      | -        | -                | -        | -                              | -                    | -                      | USART6_TX          | -                         | -                 | ETH _MII_TXD1<br>ETH _RMII_TXD1       | FSMC_A25                     | -        | -    | EVE   |

|        | PG15 | -   | -      | -        | -                | -        | -                              | -                    | -                      | USART6_<br>CTS     | -                         | -                 | -                                     | -                            | DCMI_D13 | -    | EVE   |

#### Table 9. Alternate function mapping (continued)

5

DocID022063 Rev 8

71/206

Pinouts and pin description

| Bus  | Boundary address          | Peripheral          |

|------|---------------------------|---------------------|

|      | 0x4000 7800 - 0x4000 7FFF | Reserved            |

|      | 0x4000 7400 - 0x4000 77FF | DAC                 |

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |

|      | 0x4000 6C00 - 0x4000 6FFF | Reserved            |

|      | 0x4000 6800 - 0x4000 6BFF | CAN2                |

|      | 0x4000 6400 - 0x4000 67FF | CAN1                |

|      | 0x4000 6000 - 0x4000 63FF | Reserved            |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |

|      | 0x4000 5800 - 0x4000 5BFF | 12C2                |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |

|      | 0x4000 5000 - 0x4000 53FF | UART5               |

|      | 0x4000 4C00 - 0x4000 4FFF | UART4               |

|      | 0x4000 4800 - 0x4000 4BFF | USART3              |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |

|      | 0x4000 4000 - 0x4000 43FF | I2S3ext             |

| APB1 | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |

|      | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |

|      | 0x4000 3400 - 0x4000 37FF | I2S2ext             |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |

|      | 0x4000 2400 - 0x4000 27FF | Reserved            |

|      | 0x4000 2000 - 0x4000 23FF | TIM14               |

|      | 0x4000 1C00 - 0x4000 1FFF | TIM13               |

|      | 0x4000 1800 - 0x4000 1BFF | TIM12               |

|      | 0x4000 1400 - 0x4000 17FF | TIM7                |

|      | 0x4000 1000 - 0x4000 13FF | TIM6                |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |

|      | 0x4000 0400 - 0x4000 07FF | TIM3                |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |

Table 10. STM32F41x register boundary addresses (continued)

# 5 Electrical characteristics

# 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

# 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

# 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25 \text{ °C}$ ,  $V_{DD} = 3.3 \text{ V}$  (for the 1.8 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

# 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 5.1.4 Loading capacitor

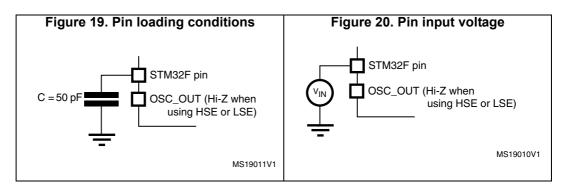

The loading conditions used for pin parameter measurement are shown in *Figure 19*.

#### 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 20*.

| Cumhal           | Devenueter     | Conditions                      | 4                 | Тур                    | Ма                     | ax <sup>(1)</sup>       | Unit |    |    |  |

|------------------|----------------|---------------------------------|-------------------|------------------------|------------------------|-------------------------|------|----|----|--|

| Symbol Parameter |                | Conditions                      | f <sub>HCLK</sub> | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |    |    |  |

|                  |                |                                 | 168 MHz           | 93                     | 109                    | 117                     |      |    |    |  |

|                  |                |                                 | 144 MHz           | 76                     | 89                     | 96                      |      |    |    |  |

|                  |                |                                 | 120 MHz           | 67                     | 79                     | 86                      |      |    |    |  |

|                  |                |                                 | 90 MHz            | 53                     | 65                     | 73                      |      |    |    |  |

|                  |                | External clock <sup>(2)</sup> , | 60 MHz            | 37                     | 49                     | 56                      |      |    |    |  |

|                  |                | all peripherals                 | 30 MHz            | 20                     | 32                     | 39                      |      |    |    |  |

|                  |                | enabled <sup>(3)(4)</sup>       | 25 MHz            | 16                     | 27                     | 35                      |      |    |    |  |

|                  |                |                                 |                   |                        |                        | 16 MHz                  | 11   | 23 | 30 |  |

|                  |                |                                 |                   | 8 MHz                  | 6                      | 18                      | 25   |    |    |  |

|                  |                |                                 | 4 MHz             | 4                      | 16                     | 23                      |      |    |    |  |

|                  | Supply current |                                 | 2 MHz             | 3                      | 15                     | 22                      | m 4  |    |    |  |

| I <sub>DD</sub>  | in Run mode    |                                 | 168 MHz           | 46                     | 61                     | 69                      | mA   |    |    |  |

|                  |                |                                 | 144 MHz           | 40                     | 52                     | 60                      |      |    |    |  |

|                  |                |                                 | 120 MHz           | 37                     | 48                     | 56                      |      |    |    |  |

|                  |                |                                 | 90 MHz            | 30                     | 42                     | 50                      |      |    |    |  |

|                  |                | External clock <sup>(2)</sup> , | 60 MHz            | 22                     | 33                     | 41                      |      |    |    |  |

|                  |                | all peripherals                 | 30 MHz            | 12                     | 24                     | 31                      |      |    |    |  |

|                  |                | disabled <sup>(3)(4)</sup>      | 25 MHz            | 10                     | 21                     | 29                      |      |    |    |  |

|                  |                |                                 | 16 MHz            | 7                      | 19                     | 26                      |      |    |    |  |

|                  |                |                                 | 8 MHz             | 4                      | 16                     | 23                      |      |    |    |  |

|                  |                |                                 | 4 MHz             | 3                      | 15                     | 22                      |      |    |    |  |

|                  |                |                                 | 2 MHz             | 2                      | 14                     | 21                      |      |    |    |  |

# Table 21. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled)

1. Guaranteed by characterization, tested in production at  $V_{\text{DD}}$  max and  $f_{\text{HCLK}}$  max with peripherals enabled.

2. External clock is 4 MHz and PLL is on when  $f_{HCLK}$  > 25 MHz.

3. When analog peripheral blocks such as (ADCs, DACs, HSE, LSE, HSI,LSI) are on, an additional power consumption should be considered.

4. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

|                                               |                                                                                                                                     |                                                                                                                                                  | Тур                       |                           | Max                       |                            |      |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol                                        | Parameter                                                                                                                           | Conditions                                                                                                                                       | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                                               | Supply<br>current in<br>Stop mode                                                                                                   | Flash in Stop mode, low-speed and high-<br>speed internal RC oscillators and high-speed<br>oscillator OFF (no independent watchdog)              | 0.45                      | 1.5                       | 11.00                     | 20.00                      |      |

|                                               | with main<br>regulator in<br>Run mode                                                                                               | Flash in Deep power-down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.40                      | 1.5                       | 11.00                     | 20.00                      | mA   |

| IDD_STOP<br>Supply<br>current in<br>Stop mode | Flash in Stop mode, low-speed and high-<br>speed internal RC oscillators and high-speed<br>oscillator OFF (no independent watchdog) | 0.31                                                                                                                                             | 1.1                       | 8.00                      | 15.00                     | ША                         |      |

|                                               | with main<br>regulator in<br>Low-power<br>mode                                                                                      | Flash in Deep power-down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.28                      | 1.1                       | 8.00                      | 15.00                      |      |

| Table 23. Typical and maximum current consumptions in Stop mod |

|----------------------------------------------------------------|

|----------------------------------------------------------------|

# Table 24. Typical and maximum current consumptions in Standby mode

|          |                           |                                                      | Тур                        |                            |                            | Ма                        |                            |      |

|----------|---------------------------|------------------------------------------------------|----------------------------|----------------------------|----------------------------|---------------------------|----------------------------|------|

| Symbol   | Parameter                 | Conditions                                           | T <sub>A</sub> = 25 °C     |                            |                            | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|          |                           |                                                      | V <sub>DD</sub> =<br>1.8 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V <sub>DD</sub> =         | = 3.6 V                    |      |

|          |                           | Backup SRAM ON, low-<br>speed oscillator and RTC ON  | 3.0                        | 3.4                        | 4.0                        | 20                        | 36                         |      |

|          | Supply current in Standby | Backup SRAM OFF, low-<br>speed oscillator and RTC ON | 2.4                        | 2.7                        | 3.3                        | 16                        | 32                         |      |

| IDD_STBY | mode                      | Backup SRAM ON, RTC<br>OFF                           | 2.4                        | 2.6                        | 3.0                        | 12.5                      | 24.8                       | μA   |

|          |                           | Backup SRAM OFF, RTC<br>OFF                          | 1.7                        | 1.9                        | 2.2                        | 9.8                       | 19.2                       |      |

1. Guaranteed by characterization.

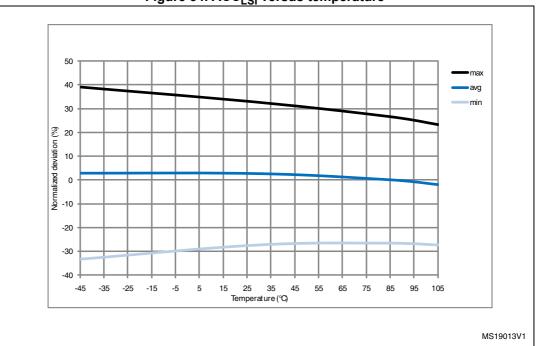

Figure 34. ACC<sub>LSI</sub> versus temperature

# 5.3.10 PLL characteristics

The parameters given in *Table 36* and *Table 37* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                 | Parameter                             | Conditions         | Min                 | Тур | Max  | Unit |

|------------------------|---------------------------------------|--------------------|---------------------|-----|------|------|

| f <sub>PLL_IN</sub>    | PLL input clock <sup>(1)</sup>        | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 | MHz  |

| f <sub>PLL_OUT</sub>   | PLL multiplier output clock           | -                  | 24                  | -   | 168  | MHz  |

| f <sub>PLL48_OUT</sub> | 48 MHz PLL multiplier output<br>clock | -                  | -                   | 48  | 75   | MHz  |

| f <sub>VCO_OUT</sub>   | PLL VCO output                        | -                  | 100                 | -   | 432  | MHz  |

| t                      | PLL lock time                         | VCO freq = 100 MHz | 75                  | -   | 200  | μs   |

| t <sub>LOCK</sub>      |                                       | VCO freq = 432 MHz | 100                 | -   | 300  | μο   |

Table 36. Main PLL characteristics

# 5.3.18 TIM timer characteristics

The parameters given in Table 52 and Table 53 are guaranteed by design.

Refer to *Section 5.3.16: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                 | Conditions                                                     | Min    | Мах                     | Unit                 |

|------------------------|-------------------------------------------|----------------------------------------------------------------|--------|-------------------------|----------------------|

|                        |                                           | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time                     | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>84 MHz | 11.9   | -                       | ns                   |

|                        |                                           | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                           | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 42 MHz                | 23.8   | -                       | ns                   |

| f                      | Timer external clock                      |                                                                | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>       | frequency on CH1 to CH4                   |                                                                | 0      | 42                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                          |                                                                | -      | 16/32                   | bit                  |

|                        | 16-bit counter clock                      |                                                                | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| t                      | period when internal clock is selected    | f <sub>TIMxCLK</sub> = 84 MHz<br>APB1= 42 MHz                  | 0.0119 | 780                     | μs                   |

| <sup>t</sup> COUNTER   | 32-bit counter clock                      |                                                                | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        | period when internal clock<br>is selected |                                                                | 0.0119 | 51130563                | μs                   |

| +                      | Maximum possible count                    |                                                                | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| <sup>t</sup> MAX_COUNT | Maximum possible count                    |                                                                | -      | 51.1                    | S                    |

Table 52. Characteristics of TIMx connected to the APB1 domain<sup>(1)</sup>

1. TIMx is used as a general term to refer to the TIM2, TIM3, TIM4, TIM5, TIM6, TIM7, and TIM12 timers.

# SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 55* for SPI are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14* with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 V<sub>DD</sub>

Refer to Section 5.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                | Parameter                            | Conditions                                              | Min | Тур | Мах | Unit |

|-----------------------|--------------------------------------|---------------------------------------------------------|-----|-----|-----|------|

| f                     |                                      | Master mode, SPI1,<br>2.7V < V <sub>DD</sub> < 3.6V     |     |     | 42  |      |

| f <sub>SCK</sub>      | SPI clock frequency                  | Slave mode, SPI1,<br>2.7V < V <sub>DD</sub> < 3.6V      | -   | -   | 42  | MHz  |

| 1/+                   | SPI Clock inequency                  | Master mode, SPI1/2/3,<br>1.7V < V <sub>DD</sub> < 3.6V |     | _   | 21  |      |

| 1/t <sub>c(SCK)</sub> |                                      | Slave mode, SPI1/2/3,<br>1.7V < V <sub>DD</sub> < 3.6V  | _   | -   | 21  |      |

| Duty(SCK)             | Duty cycle of SPI clock<br>frequency | Slave mode                                              | 30  | 50  | 70  | %    |

# Table 55. SPI dynamic characteristics<sup>(1)</sup>

# **USB OTG FS characteristics**

This interface is present in both the USB OTG HS and USB OTG FS controllers.

| Symbol                              | Parameter                           | Мах | Unit |

|-------------------------------------|-------------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG FS transceiver startup time | 1   | μs   |

Table 57. USB OTG FS startup time

1. Guaranteed by design.

| Sym             | bol                            | Parameter                                                 | Conditions                                                       | Min. <sup>(1)</sup> | Тур. | Max. <sup>(1)</sup> | Unit |

|-----------------|--------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|---------------------|------|---------------------|------|

| V <sub>DD</sub> |                                | USB OTG FS operating<br>voltage                           | -                                                                | 3.0 <sup>(2)</sup>  | -    | 3.6                 | V    |

| Input           | $V_{DI}^{(3)}$                 | Differential input sensitivity                            | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)                                 | 0.2                 | -    | -                   |      |

| levels          | V <sub>CM</sub> <sup>(3)</sup> | Differential common mode range                            | Includes V <sub>DI</sub> range                                   | 0.8                 | -    | 2.5                 | V    |

|                 | $V_{SE}^{(3)}$                 | Single ended receiver threshold                           | -                                                                | 1.3                 | -    | 2.0                 |      |

| Output          | V <sub>OL</sub>                | Static output level low                                   | ${\sf R}_{\sf L}$ of 1.5 k\Omega to 3.6 V $^{(4)}$               | -                   | -    | 0.3                 | V    |

| levels          | V <sub>OH</sub>                | Static output level high                                  | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(4)}$ | 2.8                 | -    | 3.6                 | v    |

| Б               |                                | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | V - V                                                            | 17                  | 21   | 24                  |      |

| R <sub>PD</sub> |                                | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>DD</sub>                                | 0.65                | 1.1  | 2.0                 | kΩ   |

| R <sub>PU</sub> |                                | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP)                      | V <sub>IN</sub> = V <sub>SS</sub>                                | 1.5                 | 1.8  | 2.1                 |      |

|                 |                                | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>                                | 0.25                | 0.37 | 0.55                |      |

#### Table 58. USB OTG FS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. The STM32F415xx and STM32F417xx USB OTG FS functionality is ensured down to 2.7 V but not the full USB OTG FS electrical characteristics which are degraded in the 2.7-to-3.0 V  $V_{DD}$  voltage range.

3. Guaranteed by design.

4.  $\ensuremath{\,\mathsf{R}_{\mathsf{L}}}$  is the load connected on the USB OTG FS drivers

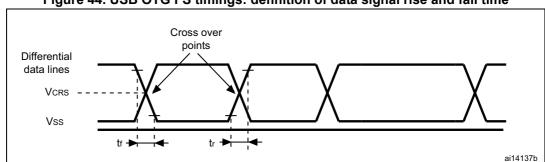

#### Figure 44. USB OTG FS timings: definition of data signal rise and fall time

### Table 59. USB OTG FS electrical characteristics<sup>(1)</sup>

|                  | Driver characteristics          |                                |     |     |      |  |  |

|------------------|---------------------------------|--------------------------------|-----|-----|------|--|--|

| Symbol           | Parameter                       | Conditions                     | Min | Max | Unit |  |  |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>f</sub>   | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>rfm</sub> | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |

| V <sub>CRS</sub> | Output signal crossover voltage | -                              | 1.3 | 2.0 | V    |  |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

### **USB HS characteristics**

Unless otherwise specified, the parameters given in *Table 62* for ULPI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency summarized in *Table 61* and  $V_{DD}$  supply voltage conditions summarized in *Table 60*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>.

Refer to Section Section 5.3.16: I/O port characteristics for more details on the input/output characteristics.

| Symbol      |                 | Parameter                    | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |  |

|-------------|-----------------|------------------------------|---------------------|---------------------|------|--|

| Input level | V <sub>DD</sub> | USB OTG HS operating voltage | 2.7                 | 3.6                 | V    |  |

#### Table 60. USB HS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

| Table 61. | USB HS | clock timin | g parameters <sup>(1)</sup> |

|-----------|--------|-------------|-----------------------------|

|           |        |             | y parameters.               |

| Parameter                                                     | Symbol | Min                     | Nominal | Мах | Unit |     |

|---------------------------------------------------------------|--------|-------------------------|---------|-----|------|-----|

| f <sub>HCLK</sub> value to guarantee prop<br>USB HS interface | -      | 30                      | -       | -   | MHz  |     |

| Frequency (first transition) 8-bit ±10%                       |        | F <sub>START_8BIT</sub> | 54      | 60  | 66   | MHz |

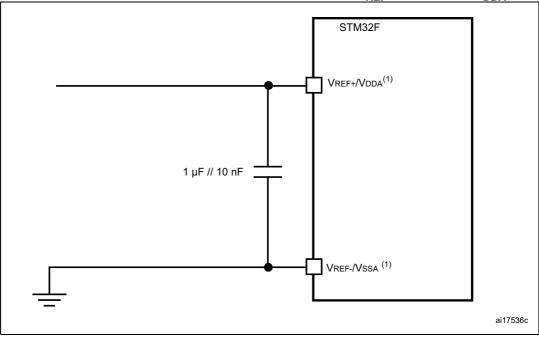

Figure 52. Power supply and reference decoupling (V<sub>REF+</sub> connected to V<sub>DDA</sub>)

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are both available on UFBGA176.  $V_{REF+}$  is also available on LQFP100, LQFP144, and LQFP176. When  $V_{REF+}$  and  $V_{REF-}$  are not available, they are internally connected to  $V_{DDA}$  and  $V_{SSA}$ .

# 5.3.22 Temperature sensor characteristics

| Table 69 | . Temperature | sensor | characteristics |

|----------|---------------|--------|-----------------|

|----------|---------------|--------|-----------------|

| Symbol                             | Parameter                                                      | Min | Тур  | Max | Unit  |

|------------------------------------|----------------------------------------------------------------|-----|------|-----|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature                  | -   | ±1   | ±2  | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                                  | -   | 2.5  |     | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>     | Voltage at 25 °C                                               | -   | 0.76 |     | V     |

| t <sub>START</sub> <sup>(2)</sup>  | Startup time                                                   | -   | 6    | 10  | μs    |

| T <sub>S_temp</sub> <sup>(2)</sup> | ADC sampling time when reading the temperature (1 °C accuracy) | 10  | -    | -   | μs    |

1. Guaranteed by characterization.

2. Guaranteed by design.

| Symbol  | Parameter                                                                          | Memory address            |

|---------|------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1 | TS ADC raw data acquired at temperature of 30 $^\circ$ C, V <sub>DDA</sub> =3.3 V  | 0x1FFF 7A2C - 0x1FFF 7A2D |

| TS_CAL2 | TS ADC raw data acquired at temperature of 110 $^\circ$ C, V <sub>DDA</sub> =3.3 V | 0x1FFF 7A2E - 0x1FFF 7A2F |

# Table 70. Temperature sensor calibration values

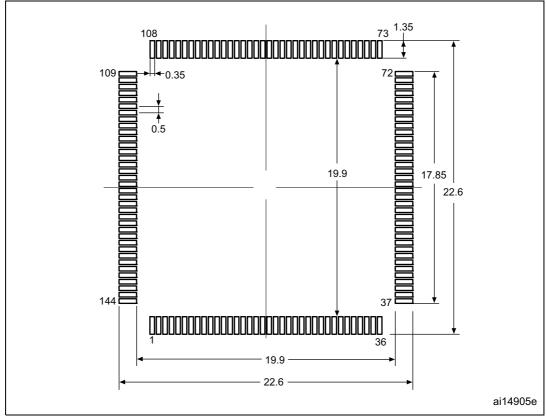

1. Dimensions are in millimeters.

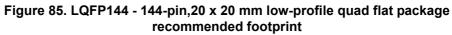

# 6.5 UFBGA176+25 package information

Figure 87. UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

# Table 95. UFBGA176+25 ball, 10 × 10 × 0.65 mm pitch, ultra thin fine pitchball grid array mechanical data

| Cumhal |       | millimeters |        |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|--------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Мах    | Min    | Тур                   | Мах    |

| А      | -     | -           | 0.600  | -      | -                     | 0.0236 |

| A1     | -     | -           | 0.110  | -      | -                     | 0.0043 |

| A2     | -     | 0.130       | -      | -      | 0.0051                | -      |

| A3     | -     | 0.450       | -      | -      | 0.0177                | -      |

| A4     | -     | 0.320       | -      | -      | 0.0126                | -      |

| b      | 0.240 | 0.290       | 0.340  | 0.0094 | 0.0114                | 0.0134 |

| D      | 9.850 | 10.000      | 10.150 | 0.3878 | 0.3937                | 0.3996 |

| D1     | -     | 9.100       | -      | -      | 0.3583                | -      |

| E      | 9.850 | 10.000      | 10.150 | 0.3878 | 0.3937                | 0.3996 |

| E1     | -     | 9.100       | -      | -      | 0.3583                | -      |

| е      | -     | 0.650       | -      | -      | 0.0256                | -      |

| Z      | -     | 0.450       | -      | -      | 0.0177                | -      |

| ddd    | -     | -           | 0.080  | -      | -                     | 0.0031 |

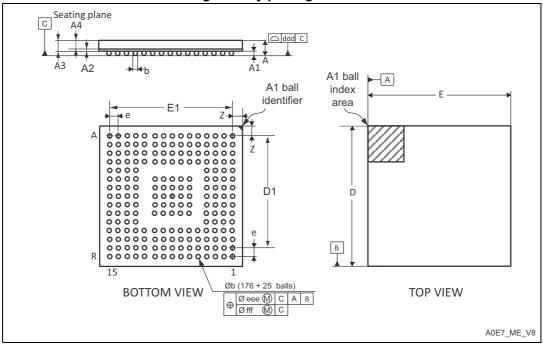

#### **Device marking for LQFP176**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

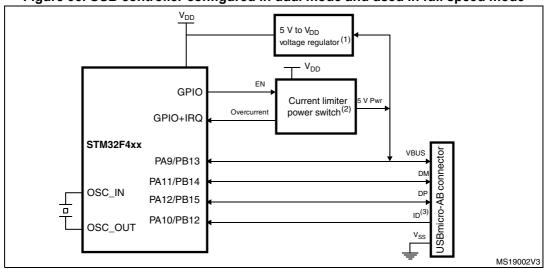

Figure 95. USB controller configured in dual mode and used in full speed mode

- 1. External voltage regulator only needed when building a  $V_{\mbox{BUS}}$  powered device.

- The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

- 3. The ID pin is required in dual role only.

- 4. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.

Table 100. Document revision history (continued)

|      | Table 100. Document revision history (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date | Revision                                         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Date |                                                  | Changes           Modified Note 1 below Table 2: STM32F415xx and STM32F417xx:<br>features and peripheral counts.           Updated Figure 4 title.           Updated Note 3 below Figure 21: Power supply scheme.           Changed simplex mode into half-duplex mode in Section 2.2.25: Inter-<br>integrated sound (I2S).           Replaced DAC1_OUT and DAC2_OUT by DAC_OUT1 and<br>DAC_OUT2, respectively.           Updated pin 36 signal in Figure 15: STM32F41xxx LQFP176 pinout.           Changed pin number from F8 to D4 for PA13 pin in Table 7:<br>STM32F41xxx pin and ball definitions.           Replaced TIM2_CH1/TIM2_ETR by TIM2_CH1_ETR for PA0 and PA5<br>pins in Table 9: Alternate function mapping.           Changed system memory into System memory + OTP in Figure 18:<br>STM32F41xxx memory map.           Added Note 1 below Table 16: VCAP_1/VCAP_2 operating conditions.           Updated I <sub>DDA</sub> description in Table 74: DAC characteristics.           Removed PA9/PB13 connection to VBUS in Figure 93: USB controller<br>configured as peripheral-only and used in Full speed mode and<br>Figure 94: USB controller configured as host-only and used in full<br>speed mode.           Updated SPI throughput on front page and Section 2.2.24: Serial<br>peripheral interface (SPI)           Updated operating voltages in Table 2: STM32F415xx and<br>STM32F417xx: features and peripheral counts           Updated Section 2.2.15: Power supply schemes           Updated operating voltages in Table 2: STM32F415xx and<br>STM32F417xx: features and peripheral counts           Updated Table 18: Section 2.2.19: Low-power |  |  |

|      |                                                  | Updated Table 44: EMI characteristics<br>Updated Table 49: Output voltage characteristics<br>Updated Table 51: NRST pin characteristics<br>Updated Table 55: SPI dynamic characteristics<br>Updated Table 56: I2S dynamic characteristics<br>Deleted Table 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|      |                                                  | Updated Table 62: ULPI timing<br>Updated Figure 46: Ethernet SMI timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

Table 100. Document revision history (continued)