Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 140                                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                                              |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 176-LQFP                                                                                  |

| Supplier Device Package    | 176-LQFP (24x24)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f417igt7                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The STM32F415xx and STM32F417xx family is based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 168 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all ARM single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32F415xx and STM32F417xx family incorporates high-speed embedded memories (Flash memory up to 1 Mbyte, up to 192 Kbytes of SRAM), up to 4 Kbytes of backup SRAM, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, three AHB buses and a 32-bit multi-AHB bus matrix.

All devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve general-purpose 16-bit timers including two PWM timers for motor control, two general-purpose 32-bit timers. a true random number generator (RNG), and a cryptographic acceleration cell. They also feature standard and advanced communication interfaces.

- Up to three I<sup>2</sup>Cs

- Three SPIs, two I<sup>2</sup>Ss full duplex. To achieve audio class accuracy, the I2S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization.

- Four USARTs plus two UARTs

- An USB OTG full-speed and a USB OTG high-speed with full-speed capability (with the ULPI),

- Two CANs

- An SDIO/MMC interface

- Ethernet and the camera interface available on STM32F417xx devices only.

New advanced peripherals include an SDIO, an enhanced flexible static memory control (FSMC) interface (for devices offered in packages of 100 pins and more), a camera interface for CMOS sensors and a cryptographic acceleration cell. Refer to *Table 2: STM32F415xx and STM32F417xx: features and peripheral counts* for the list of peripherals available on each part number.

The STM32F415xx and STM32F417xx family operates in the –40 to +105 °C temperature range from a 1.8 to 3.6 V power supply. The supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor: refer to *Section : Internal reset OFF*. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F415xx and STM32F417xx family offers devices in various packages ranging from 64 pins to 176 pins. The set of included peripherals changes with the device chosen.

These features make the STM32F415xx and STM32F417xx microcontroller family suitable for a wide range of applications:

- Motor drive and application control

- Medical equipment

- Industrial applications: PLC, inverters, circuit breakers

- Printers, and scanners

- Alarm systems, video intercom, and HVAC

- Home audio appliances

DocID022063 Rev 8

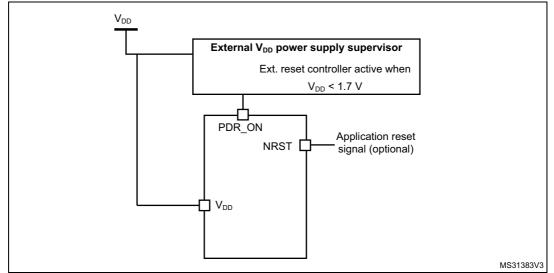

Figure 7. Power supply supervisor interconnection with internal reset OFF

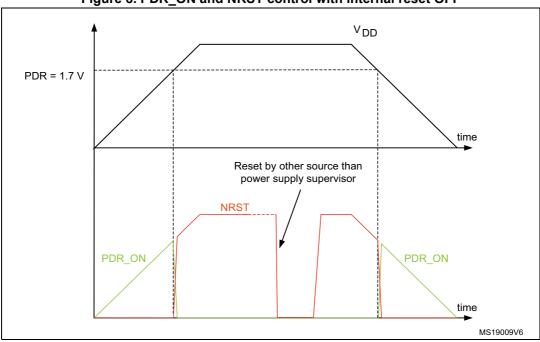

1. PDR = 1.7 V for reduce temperature range; PDR = 1.8 V for all temperature range.

The V<sub>DD</sub> specified threshold, below which the device must be maintained under reset, is 1.8 V (see *Figure 7*). This supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range.

A comprehensive set of power-saving mode allows to design low-power applications.

When the internal reset is OFF, the following integrated features are no more supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled

- The brownout reset (BOR) circuitry is disabled

- The embedded programmable voltage detector (PVD) is disabled

- V<sub>BAT</sub> functionality is no more available and V<sub>BAT</sub> pin should be connected to V<sub>DD</sub>

All packages, except for the LQFP64 and LQFP100, allow to disable the internal reset through the PDR\_ON signal.

Figure 8. PDR\_ON and NRST control with internal reset OFF

# 2.2.16 Voltage regulator

The regulator has four operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low-power regulator (LPR)

- Power-down

- Regulator OFF

## **Regulator ON**

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when regulator is ON:

- MR is used in the nominal regulation mode (With different voltage scaling in Run) In Main regulator mode (MR mode), different voltage scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption. Refer to *Table 14: General operating conditions*.

- LPR is used in the Stop modes

The LP regulator mode is configured by software when entering Stop mode.

- Power-down is used in Standby mode.

- The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost)

## 2.2.26 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S application. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an  $I^2S$  sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the  $I^2S$  flow with an external PLL (or Codec output).

# 2.2.27 Secure digital input/output interface (SDIO)

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 48 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

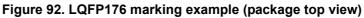

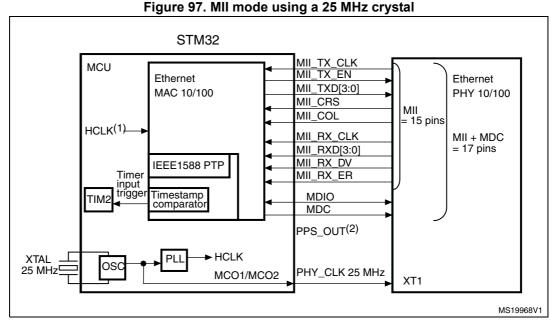

## 2.2.28 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

Peripheral available only on the STM32F417xx devices.

The STM32F417xx devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard mediumindependent interface (MII) or a reduced medium-independent interface (RMII). The STM32F417xx requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). the PHY is connected to the STM32F417xx MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) from the STM32F417xx.

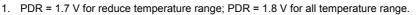

#### Figure 14. STM32F41xxx LQFP144 pinout

1. The above figure shows the package top view.

|        | 1       | Pin r   | numb    |          |         |                                                      |          | unu             |       | definitions (continued)                                                               |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|---------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                   | Additional<br>functions |

| 40     | E3      | 66      | 99      | F14      | 118     | PC9                                                  | I/O      | FT              | -     | I2S_CKIN/ MCO2 /<br>TIM8_CH4/SDIO_D1 /<br>/I2C3_SDA / DCMI_D3 /<br>TIM3_CH4/ EVENTOUT | -                       |

| 41     | D1      | 67      | 100     | F15      | 119     | PA8                                                  | I/O      | FT              | -     | MCO1 / USART1_CK/<br>TIM1_CH1/ I2C3_SCL/<br>OTG_FS_SOF/<br>EVENTOUT                   | -                       |

| 42     | D2      | 68      | 101     | E15      | 120     | PA9                                                  | I/O      | FT              | -     | USART1_TX/ TIM1_CH2 /<br>I2C3_SMBA / DCMI_D0/<br>EVENTOUT                             | OTG_FS_VBUS             |

| 43     | D3      | 69      | 102     | D15      | 121     | PA10                                                 | I/O      | FT              | -     | USART1_RX/ TIM1_CH3/<br>OTG_FS_ID/DCMI_D1/<br>EVENTOUT                                | -                       |

| 44     | C1      | 70      | 103     | C15      | 122     | PA11                                                 | I/O      | FT              | -     | USART1_CTS / CAN1_RX<br>/ TIM1_CH4 /<br>OTG_FS_DM/ EVENTOUT                           | -                       |

| 45     | C2      | 71      | 104     | B15      | 123     | PA12                                                 | I/O      | FT              | -     | USART1_RTS/CAN1_TX/<br>TIM1_ETR/OTG_FS_DP/<br>EVENTOUT                                | -                       |

| 46     | D4      | 72      | 105     | A15      | 124     | PA13<br>(JTMS-SWDIO)                                 | I/O      | FT              | -     | JTMS-SWDIO/ EVENTOUT                                                                  | -                       |

| 47     | B1      | 73      | 106     | F13      | 125     | V <sub>CAP_2</sub>                                   | S        | -               | -     | -                                                                                     | -                       |

| -      | E7      | 74      | 107     | F12      | 126     | V <sub>SS</sub>                                      | S        | -               | -     | -                                                                                     | -                       |

| 48     | E6      | 75      | 108     | G13      | 127     | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                     | -                       |

| -      | -       | -       | -       | E12      | 128     | PH13                                                 | I/O      | FT              | -     | TIM8_CH1N / CAN1_TX/<br>EVENTOUT                                                      | -                       |

| -      | -       | -       | -       | E13      | 129     | PH14                                                 | I/O      | FT              | -     | TIM8_CH2N / DCMI_D4/<br>EVENTOUT                                                      | -                       |

| -      | -       | -       | -       | D13      | 130     | PH15                                                 | I/O      | FT              | -     | TIM8_CH3N / DCMI_D11/<br>EVENTOUT                                                     | -                       |

| -      | C3      | -       | -       | E14      | 131     | PI0                                                  | I/O      | FT              | -     | TIM5_CH4 / SPI2_NSS /<br>I2S2_WS / DCMI_D13/<br>EVENTOUT                              | -                       |

| -      | B2      | -       | -       | D14      | 132     | PI1                                                  | I/O      | FT              | -     | SPI2_SCK / I2S2_CK /<br>DCMI_D8/ EVENTOUT                                             | -                       |

Table 7. STM32F41xxx pin and ball definitions (continued)

72/206

DocID022063 Rev 8

|        |      |     |        |          |                  | Tab           | ole 9. Alt                     | ernate fu            | unction m              | apping             | (contin                   | ued)                |               |                      |                |      |          |

|--------|------|-----|--------|----------|------------------|---------------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|---------------------|---------------|----------------------|----------------|------|----------|

|        |      | AF0 | AF1    | AF2      | AF3              | AF4           | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10                | AF11          | AF12                 | AF13           |      |          |

| Po     | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3      | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS   | ETH           | FSMC/SDIO<br>/OTG_FS | DCMI           | AF14 | AF15     |

|        | PH0  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -             | -                    | -              | -    | EVENTOUT |

|        | PH1  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -             | -                    | -              | -    | EVENTOUT |

|        | PH2  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | ETH _MII_CRS  | -                    | -              | -    | EVENTOUT |

|        | PH3  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | ETH_MILCOL    | -                    | -              | -    | EVENTOUT |

|        | PH4  | -   | -      | -        | -                | I2C2_SCL      | -                              | -                    | -                      | -                  | -                         | OTG_HS_ULPI_<br>NXT | -             | -                    | -              | -    | EVENTOUT |

|        | PH5  | -   | -      | -        | -                | I2C2_SDA      | -                              | -                    | -                      | -                  | -                         | -                   | -             | -                    | -              | -    | EVENTOUT |

|        | PH6  | -   | -      | -        | -                | I2C2_<br>SMBA | -                              | -                    | -                      | -                  | TIM12_CH1                 | -                   | ETH _MII_RXD2 | -                    | -              | -    | EVENTOUT |

| Port H | PH7  | -   | -      | -        | -                | I2C3_SCL      | -                              | -                    | -                      | -                  | -                         | -                   | ETH_MII_RXD3  | -                    | -              | -    | EVENTOUT |

| POILH  | PH8  | -   | -      | -        | -                | I2C3_SDA      | -                              | -                    | -                      | -                  | -                         | -                   | -             | -                    | DCMI_<br>HSYNC | -    | EVENTOUT |

|        | PH9  | -   | -      | -        | -                | I2C3_<br>SMBA | -                              | -                    | -                      | -                  | TIM12_CH2                 | -                   | -             | -                    | DCMI_D0        | -    | EVENTOUT |

|        | PH10 | -   | -      | TIM5_CH1 | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -             | -                    | DCMI_D1        | -    | EVENTOUT |

|        | PH11 | -   | -      | TIM5_CH2 | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -             | -                    | DCMI_D2        | -    | EVENTOUT |

|        | PH12 | -   | -      | TIM5_CH3 | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -             | -                    | DCMI_D3        | -    | EVENTOUT |

|        | PH13 | -   | -      | -        | TIM8_CH1N        | -             | -                              | -                    | -                      | -                  | CAN1_TX                   | -                   | -             | -                    | -              | -    | EVENTOUT |

|        | PH14 | -   | -      | -        | TIM8_CH2N        | -             | -                              | -                    | -                      | -                  | -                         | -                   | -             | -                    | DCMI_D4        | -    | EVENTOUT |

|        | PH15 | -   | -      | -        | TIM8_CH3N        | -             | -                              | -                    | -                      | -                  | -                         | -                   | -             | -                    | DCMI_D11       | -    | EVENTOUT |

Pinouts and pin description

577

| Symbol                               | Ratings                                                                 | Max.  | Unit |  |  |  |  |  |  |

|--------------------------------------|-------------------------------------------------------------------------|-------|------|--|--|--|--|--|--|

| I <sub>VDD</sub>                     | Total current into $V_{DD}$ power lines (source) <sup>(1)</sup>         | 240   |      |  |  |  |  |  |  |

| I <sub>VSS</sub>                     | Total current out of $V_{SS}$ ground lines (sink) <sup>(1)</sup>        | 240   | 1    |  |  |  |  |  |  |

| 1                                    | Output current sunk by any I/O and control pin                          | 25    | 1    |  |  |  |  |  |  |

| I <sub>IO</sub>                      | Output current source by any I/Os and control pin                       | 25    | mA   |  |  |  |  |  |  |

| . (2)                                | Injected current on five-volt tolerant I/O <sup>(3)</sup>               | -5/+0 |      |  |  |  |  |  |  |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                        | ±5    | 1    |  |  |  |  |  |  |

| $\Sigma I_{\rm INJ(PIN)}^{(4)}$      | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ±25   |      |  |  |  |  |  |  |

#### Table 12. Current characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. Negative injection disturbs the analog performance of the device. See note in Section 5.3.21: 12-bit ADC characteristics.

3. Positive injection is not possible on these I/Os. A negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 11* for the values of the maximum allowed input voltage.

4. A positive injection is induced by  $V_{IN}$  >  $V_{DD}$  while a negative injection is induced by  $V_{IN}$  <  $V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 11* for the values of the maximum allowed input voltage.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 13. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 125         | °C   |

# 5.3 Operating conditions

# 5.3.1 General operating conditions

#### Table 14. General operating conditions

| Symbol                             | Parameter                                                  | Conditions                             | Min                | Тур | Max | Unit |  |

|------------------------------------|------------------------------------------------------------|----------------------------------------|--------------------|-----|-----|------|--|

| fHCLK                              | Internal AHB clock frequency                               | VOS bit in PWR_CR register = $0^{(1)}$ | 0                  | -   | 144 |      |  |

|                                    |                                                            | VOS bit in PWR_CR register= 1          | 0                  | -   | 168 | MHz  |  |

| f <sub>PCLK1</sub>                 | Internal APB1 clock frequency                              | -                                      | 0                  | -   | 42  |      |  |

| f <sub>PCLK2</sub>                 | Internal APB2 clock frequency                              | Must be the same potential as          | 0                  | -   | 84  |      |  |

| V <sub>DD</sub>                    | Standard operating voltage                                 | -                                      | 1.8 <sup>(2)</sup> | -   | 3.6 | V    |  |

| V <sub>DDA</sub> <sup>(3)(4)</sup> | Analog operating voltage<br>(ADC limited to 1.2 M samples) |                                        | 1.8 <sup>(2)</sup> | -   | 2.4 | V    |  |

| * ADD *                            | Analog operating voltage<br>(ADC limited to 1.4 M samples) | V <sub>DD</sub> <sup>(5)</sup>         | 2.4                | -   | 3.6 | v    |  |

| V <sub>BAT</sub>                   | Backup operating voltage                                   | -                                      | 1.65               | -   | 3.6 | V    |  |

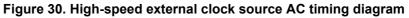

## Low-speed external user clock generated from an external source

The characteristics given in *Table 31* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                     | Parameter                                              | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------|--------------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                                  | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                  | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                                  | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              | -                                | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             | -                                | 30                 | -      | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage current                         | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

| Table 31. Low-speed external user clock characteristic | s        |

|--------------------------------------------------------|----------|

|                                                        | <u> </u> |

1. Guaranteed by design.

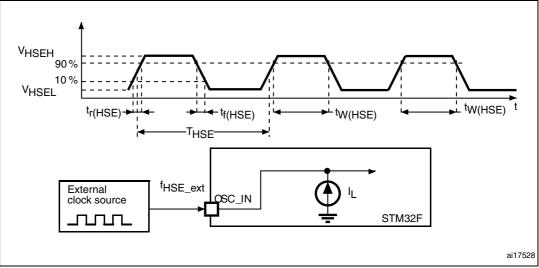

Figure 34. ACC<sub>LSI</sub> versus temperature

# 5.3.10 PLL characteristics

The parameters given in *Table 36* and *Table 37* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                 | Parameter                             | Conditions         | Min                 | Тур | Max  | Unit |  |

|------------------------|---------------------------------------|--------------------|---------------------|-----|------|------|--|

| f <sub>PLL_IN</sub>    | PLL input clock <sup>(1)</sup>        | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 | MHz  |  |

| f <sub>PLL_OUT</sub>   | PLL multiplier output clock           | -                  | 24                  | -   | 168  | MHz  |  |

| f <sub>PLL48_OUT</sub> | 48 MHz PLL multiplier output<br>clock | -                  | -                   | 48  | 75   | MHz  |  |

| f <sub>VCO_OUT</sub>   | PLL VCO output                        | -                  | 100                 | -   | 432  | MHz  |  |

|                        | PLL lock time                         | VCO freq = 100 MHz | 75                  | -   | 200  | μs   |  |

| t <sub>LOCK</sub>      |                                       | VCO freq = 432 MHz | 100                 | -   | 300  |      |  |

Table 36. Main PLL characteristics

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14 and PC15 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 12*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 12*).

### Output voltage levels

Unless otherwise specified, the parameters given in *Table 49* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*. All I/Os are CMOS and TTL compliant.

| Symbol                            | DI Parameter Conditions Min |                                                            | Min                  | Max | Unit |  |

|-----------------------------------|-----------------------------|------------------------------------------------------------|----------------------|-----|------|--|

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage    | CMOS port                                                  | -                    | 0.4 |      |  |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage   | I <sub>IO</sub> = +8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | V <sub>DD</sub> -0.4 | -   | V    |  |

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage    | TTL port                                                   | -                    | 0.4 |      |  |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage   | I <sub>IO</sub> =+ 8mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | 2.4                  | -   | V    |  |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage    | I <sub>IO</sub> = +20 mA                                   | -                    | 1.3 | v    |  |

| V <sub>OH</sub> <sup>(3)(4)</sup> |                             | 2.7 V < V <sub>DD</sub> < 3.6 V                            | V <sub>DD</sub> -1.3 | -   | v    |  |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage    | I <sub>IO</sub> = +6 mA                                    | -                    | 0.4 | v    |  |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage   | 2 V < V <sub>DD</sub> < 2.7 V                              | V <sub>DD</sub> -0.4 | -   | v    |  |

Table 49. Output voltage characteristics<sup>(1)</sup>

1. PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these I/Os must not be used as a current source (e.g. to drive an LED).

2. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in Table 12 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 12* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Guaranteed by characterization.

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 37* and *Table 50*, respectively.

Unless otherwise specified, the parameters given in *Table 50* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                                  | Min | Тур | Мах                | Unit |  |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|--------------------|------|--|

|                                               |                                                  |                                                                                 | $C_L$ = 50 pF, $V_{DD}$ > 2.70 V                            | -   | -   | 4                  |      |  |

|                                               | f                                                | Maximum frequency $^{(3)}$                                                      | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 2                  | MHz  |  |

|                                               | 'max(IO)out                                      | t Maximum frequency <sup>(3)</sup>                                              | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 8                  |      |  |

| 00                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 4                  |      |  |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.8 V to<br>3.6 V | -   | -   | 100                | ns   |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 25                 |      |  |

|                                               | f                                                | t Maximum frequency <sup>(3)</sup>                                              | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 12.5               | MHz  |  |

|                                               | 'max(IO)out                                      |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 50 <sup>(4)</sup>  |      |  |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 20                 |      |  |

| 01                                            | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> >2.7 V              | -   | -   | 10                 | ns   |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> > 1.8 V             | -   | -   | 20                 |      |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 6                  | 115  |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 10                 |      |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 50 <sup>(4)</sup>  |      |  |

|                                               | f                                                | Maximum frequency $^{(3)}$                                                      | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 25                 | MHz  |  |

|                                               | Imax(IO)out                                      | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 100 <sup>(4)</sup> |      |  |

| 10                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 50 <sup>(4)</sup>  |      |  |

| 10                                            |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 6                  |      |  |

|                                               | t <sub>f(IO)out</sub> /                          | Output high to low level fall time and output low to high                       | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 10                 | ns   |  |

|                                               | t <sub>r(IO)out</sub>                            | level rise time                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 4                  |      |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 6                  |      |  |

Table 50. I/O AC characteristics<sup>(1)(2)</sup>

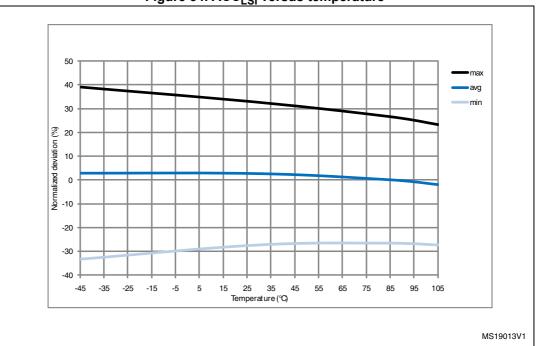

## 5.3.17 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 48*).

Unless otherwise specified, the parameters given in *Table 51* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                               | Parameter                                       | Conditions                        | Min         | Тур | Max                | Unit |

|--------------------------------------|-------------------------------------------------|-----------------------------------|-------------|-----|--------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | TTL ports                         | -           | -   | 0.8                |      |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | 2.7 V ≤V <sub>DD</sub> ≤<br>3.6 V | 2           | -   | -                  | v    |

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | CMOS ports                        | -           | -   | 0.3V <sub>DD</sub> | v    |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | 1.8 V ≤V <sub>DD</sub> ≤<br>3.6 V | $0.7V_{DD}$ | -   | -                  |      |

| V <sub>hys(NRST)</sub>               | NRST Schmitt trigger voltage<br>hysteresis      | -                                 | -           | 200 | -                  | mV   |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$                 | 30          | 40  | 50                 | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>  | NRST Input filtered pulse                       |                                   | -           | -   | 100                | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V           | 300         | -   | -                  | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal<br>Reset source          | 20          | -   | -                  | μs   |

Table 51. NRST pin characteristics

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

#### Figure 38. Recommended NRST pin protection

- 1. The reset network protects the device against parasitic resets.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 51. Otherwise the reset is not taken into account by the device.

# 5.3.18 TIM timer characteristics

The parameters given in Table 52 and Table 53 are guaranteed by design.

Refer to *Section 5.3.16: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                              | Conditions                                                     | Min    | Мах                     | Unit                 |

|------------------------|----------------------------------------|----------------------------------------------------------------|--------|-------------------------|----------------------|

|                        |                                        | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time                  | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>84 MHz | 11.9   | -                       | ns                   |

|                        |                                        | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                        | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 42 MHz                | 23.8   | -                       | ns                   |

| f                      | Timer external clock                   |                                                                | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>       | frequency on CH1 to CH4                |                                                                | 0      | 42                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                       |                                                                | -      | 16/32                   | bit                  |

|                        | 16-bit counter clock                   |                                                                | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| t                      | period when internal clock is selected | f <sub>TIMxCLK</sub> = 84 MHz<br>APB1= 42 MHz                  | 0.0119 | 780                     | μs                   |

| <sup>t</sup> COUNTER   | 32-bit counter clock                   |                                                                | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        | period when internal clock is selected |                                                                | 0.0119 | 51130563                | μs                   |

| +                      | Maximum possible count                 |                                                                | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| <sup>t</sup> MAX_COUNT | Maximum possible count                 |                                                                | -      | 51.1                    | S                    |

Table 52. Characteristics of TIMx connected to the APB1 domain<sup>(1)</sup>

1. TIMx is used as a general term to refer to the TIM2, TIM3, TIM4, TIM5, TIM6, TIM7, and TIM12 timers.

2. Guaranteed by characterization.

### Synchronous waveforms and timings

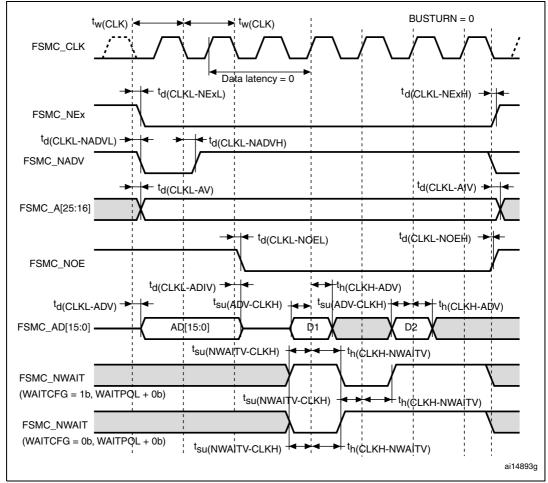

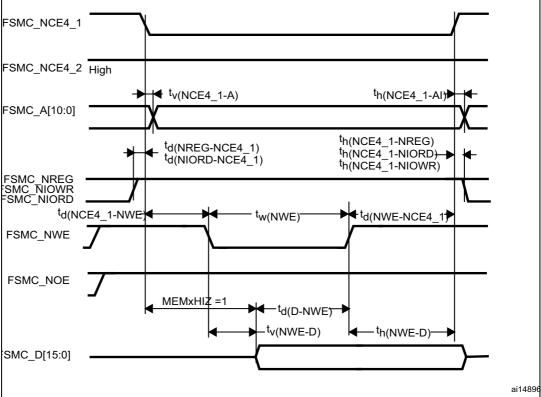

*Figure 58* through *Figure 61* represent synchronous waveforms and *Table 80* through *Table 82* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- BurstAccessMode = FSMC\_BurstAccessMode\_Enable;

- MemoryType = FSMC\_MemoryType\_CRAM;

- WriteBurst = FSMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F40xxx/41xxx reference manual)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period (with maximum FSMC\_CLK = 60 MHz).

| Symbol                  | Parameter Min                                           |                       | Мах                    | Unit |

|-------------------------|---------------------------------------------------------|-----------------------|------------------------|------|

| t <sub>w(NWE)</sub>     | FSMC_NWE low width                                      | 4T <sub>HCLK</sub> –1 | 4T <sub>HCLK</sub> + 3 | ns   |

| t <sub>v(NWE-D)</sub>   | FSMC_NWE low to FSMC_D[15-0] valid                      | -                     | 0                      | ns   |

| t <sub>h(NWE-D)</sub>   | FSMC_NWE high to FSMC_D[15-0] invalid                   | 3T <sub>HCLK</sub> –2 | -                      | ns   |

| t <sub>d(D-NWE)</sub>   | FSMC_D[15-0] valid before FSMC_NWE high                 | 5T <sub>HCLK</sub> –3 | -                      | ns   |

| t <sub>d(ALE-NWE)</sub> | FSMC_ALE valid before FSMC_NWE low                      | -                     | 3T <sub>HCLK</sub>     | ns   |

| t <sub>h(NWE-ALE)</sub> | FSMC_NWE high to FSMC_ALE invalid 3T <sub>HCLK</sub> -2 |                       | -                      | ns   |

Table 86. Switching characteristics for NAND Flash write cycles<sup>(1)</sup>

1. C<sub>L</sub> = 30 pF.

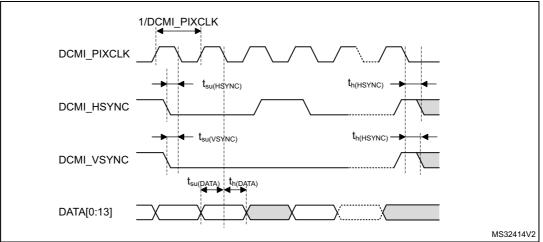

# 5.3.27 Camera interface (DCMI) timing specifications

Unless otherwise specified, the parameters given in *Table 87* for DCMI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage summarized in *Table 13*, with the following configuration:

- PCK polarity: falling

- VSYNC and HSYNC polarity: high

- Data format: 14 bits

| Symbol             | Parameter                                     | Min | Max | Unit |

|--------------------|-----------------------------------------------|-----|-----|------|

|                    | Frequency ratio DCMI_PIXCLK/f <sub>HCLK</sub> | -   | 0.4 |      |

| DCMI_PIXCLK        | Pixel clock input                             | -   | 54  | MHz  |

| D <sub>pixel</sub> | Pixel clock input duty cycle                  | 30  | 70  | %    |

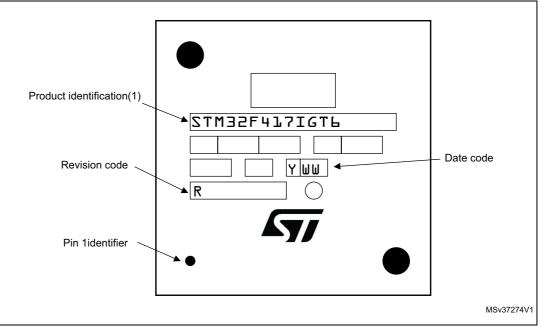

### **Device marking for LQFP176**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# A.3 Ethernet interface solutions

1. f<sub>HCLK</sub> must be greater than 25 MHz.

2. Pulse per second when using IEEE1588 PTP optional signal.

#### Figure 98. RMII with a 50 MHz oscillator

1. f<sub>HCLK</sub> must be greater than 25 MHz.

| Date |

|------|

| Date |