# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 82                                                                                        |

| Program Memory Size        | 512KB (512K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192K × 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 100-LQFP                                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f417vet6                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |      | 2.2.30    | Universal serial bus on-the-go full-speed (OTG_FS)              |

|---|------|-----------|-----------------------------------------------------------------|

|   |      | 2.2.31    | Universal serial bus on-the-go high-speed (OTG_HS)40            |

|   |      | 2.2.32    | Digital camera interface (DCMI)40                               |

|   |      | 2.2.33    | Cryptographic acceleration41                                    |

|   |      | 2.2.34    | Random number generator (RNG)41                                 |

|   |      | 2.2.35    | General-purpose input/outputs (GPIOs)41                         |

|   |      | 2.2.36    | Analog-to-digital converters (ADCs)41                           |

|   |      | 2.2.37    | Temperature sensor                                              |

|   |      | 2.2.38    | Digital-to-analog converter (DAC)42                             |

|   |      | 2.2.39    | Serial wire JTAG debug port (SWJ-DP)42                          |

|   |      | 2.2.40    | Embedded Trace Macrocell™43                                     |

| 3 | Pino | uts and   | pin description 44                                              |

| 4 | Mem  | lory maj  | oping                                                           |

| 5 | Elec | trical ch | aracteristics                                                   |

|   | 5.1  | Param     | eter conditions                                                 |

|   |      | 5.1.1     | Minimum and maximum values79                                    |

|   |      | 5.1.2     | Typical values                                                  |

|   |      | 5.1.3     | Typical curves                                                  |

|   |      | 5.1.4     | Loading capacitor                                               |

|   |      | 5.1.5     | Pin input voltage                                               |

|   |      | 5.1.6     | Power supply scheme                                             |

|   |      | 5.1.7     | Current consumption measurement81                               |

|   | 5.2  | Absolu    | te maximum ratings 81                                           |

|   | 5.3  | Operat    | ing conditions                                                  |

|   |      | 5.3.1     | General operating conditions82                                  |

|   |      | 5.3.2     | VCAP_1/VCAP_2 external capacitor                                |

|   |      | 5.3.3     | Operating conditions at power-up / power-down (regulator ON)85  |

|   |      | 5.3.4     | Operating conditions at power-up / power-down (regulator OFF)85 |

|   |      | 5.3.5     | Embedded reset and power control block characteristics          |

|   |      | 5.3.6     | Supply current characteristics                                  |

|   |      | 5.3.7     | Wakeup time from low-power mode                                 |

|   |      | 5.3.8     | External clock source characteristics                           |

|   |      | 5.3.9     | Internal clock source characteristics                           |

|   |      | 5.3.10    | PLL characteristics                                             |

|            | recommended footprint                                                       | 79 |

|------------|-----------------------------------------------------------------------------|----|

| Figure 86. | LQFP144 marking example (package top view)1                                 |    |

| Figure 87. | UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch               |    |

| -          | ball grid array package outline                                             | 81 |

| Figure 88. | UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch         |    |

|            | ball grid array recommended footprint 1                                     | 82 |

| Figure 89. | UFBGA176+25 marking example (package top view) 1                            | 83 |

| Figure 90. | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline 1       | 84 |

| Figure 91. | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint 1 | 86 |

| Figure 92. | LQFP176 marking example (package top view)                                  | 87 |

| Figure 93. | USB controller configured as peripheral-only and used                       |    |

|            | in Full speed mode                                                          | 90 |

| Figure 94. | USB controller configured as host-only and used in full speed mode          | 90 |

| Figure 95. | USB controller configured in dual mode and used in full speed mode 1        | 91 |

| Figure 96. | USB controller configured as peripheral, host, or dual-mode                 |    |

|            | and used in high speed mode                                                 | 92 |

| Figure 97. | MII mode using a 25 MHz crystal 1                                           | 93 |

| Figure 98. | RMII with a 50 MHz oscillator                                               | 93 |

| Figure 99. | RMII with a 25 MHz crystal and PHY with PLL 1                               | 94 |

|                              |                        | Table 2. STM3         | 32F415xx and S | TM32F417xx: fe | atures and per                   | ipheral | counts |       |        |       |         |

|------------------------------|------------------------|-----------------------|----------------|----------------|----------------------------------|---------|--------|-------|--------|-------|---------|

| Perip                        | herals                 | STM32F415RG           | STM32F415OG    | STM32F415VG    | STM32F415ZG                      | STM32   | F417Vx | STM32 | F417Zx | STM32 | 2F417lx |

| Flash memory i               | n Kbytes               |                       | 10             | 24             | I                                | 512     | 1024   | 512   | 1024   | 512   | 1024    |

| SRAM in                      | System                 |                       |                |                | 192(112+16+64)                   |         | 1      |       |        |       | и       |

| Kbytes Backup                |                        |                       |                |                | 4                                |         |        |       |        |       |         |

| FSMC memory                  | controller             | No Yes <sup>(1)</sup> |                |                |                                  |         |        |       |        |       |         |

| Ethernet                     |                        |                       | N              | 0              |                                  |         |        | Ye    | s      |       |         |

|                              | General-<br>purpose    |                       |                |                | 10                               |         |        |       |        |       |         |

|                              | Advanced-<br>control   |                       |                |                | 2                                |         |        |       |        |       |         |

| Timers                       | Basic                  | 2                     |                |                |                                  |         |        |       |        |       |         |

|                              | IWDG                   | Yes                   |                |                |                                  |         |        |       |        |       |         |

|                              | WWDG                   |                       | Yes            |                |                                  |         |        |       |        |       |         |

|                              | RTC                    | Yes                   |                |                |                                  |         |        |       |        |       |         |

| Random numbe                 | er generator           |                       |                |                | Yes                              |         |        |       |        |       |         |

|                              | SPI / I <sup>2</sup> S |                       |                | 3              | 8/2 (full duplex) <sup>(2)</sup> |         |        |       |        |       |         |

|                              | l <sup>2</sup> C       |                       | 3              |                |                                  |         |        |       |        |       |         |

| <b>.</b>                     | USART/UART             | 4/2                   |                |                |                                  |         |        |       |        |       |         |

| Communicatio<br>n interfaces | USB OTG FS             | Yes                   |                |                |                                  |         |        |       |        |       |         |

|                              | USB OTG HS             |                       | Yes            |                |                                  |         |        |       |        |       |         |

|                              | CAN                    |                       |                |                | 2                                |         |        |       |        |       |         |

|                              | SDIO                   |                       |                |                | Yes                              |         |        |       |        |       |         |

| Camera interfac              | ce                     |                       | Ν              | 0              |                                  |         |        | Ye    | s      |       |         |

Yes

57

Cryptography

15/206

Description

## 2.1 Full compatibility throughout the family

The STM32F415xx and STM32F417xx are part of the STM32F4 family. They are fully pinto-pin, software and feature compatible with the STM32F2xx devices, allowing the user to try different memory densities, peripherals, and performances (FPU, higher frequency) for a greater degree of freedom during the development cycle.

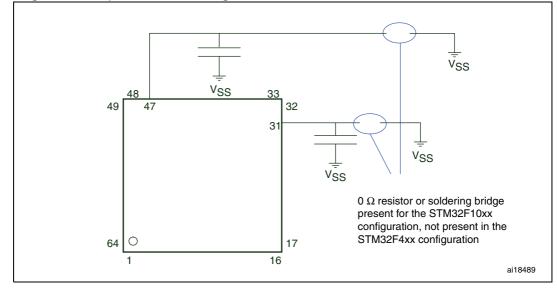

The STM32F415xx and STM32F417xx devices maintain a close compatibility with the whole STM32F10xxx family. All functional pins are pin-to-pin compatible. The STM32F415xx and STM32F417xx, however, are not drop-in replacements for the STM32F10xxx devices: the two families do not have the same power scheme, and so their power pins are different. Nonetheless, transition from the STM32F10xxx to the STM32F41xxx family remains simple as only a few pins are impacted.

*Figure 4*, *Figure 3*, *Figure 2*, and *Figure 1* give compatible board designs between the STM32F41xxx, STM32F2, and STM32F10xxx families.

Figure 1. Compatible board design between STM32F10xx/STM32F41xxx for LQFP64

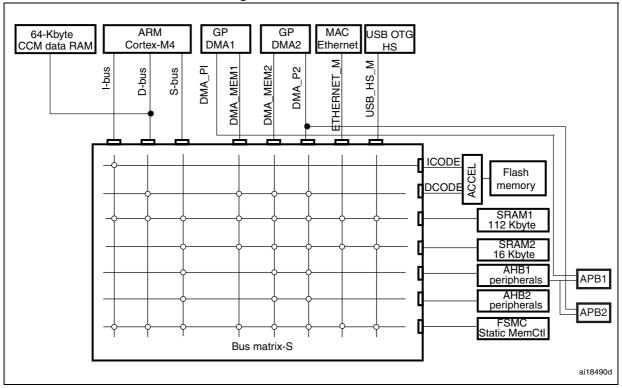

## 2.2.8 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They feature dedicated FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals:

- SPI and I<sup>2</sup>S

- I<sup>2</sup>C

- USART

- General-purpose, basic and advanced-control timers TIMx

- DAC

- SDIO

- Cryptographic acceleration

- Camera interface (DCMI)

- ADC.

### 2.2.9 Flexible static memory controller (FSMC)

The FSMC is embedded in the STM32F415xx and STM32F417xx family. It has four Chip Select outputs supporting the following modes: PCCard/Compact Flash, SRAM, PSRAM, NOR Flash and NAND Flash.

Functionality overview:

- Write FIFO

- Maximum FSMC\_CLK frequency for synchronous accesses is 60 MHz.

#### LCD parallel interface

The FSMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost-effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

## 2.2.10 Nested vectored interrupt controller (NVIC)

The STM32F415xx and STM32F417xx embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 82 maskable interrupt channels plus the 16 interrupt lines of the Cortex<sup>®</sup>-M4 with FPU core.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving, higher-priority interrupts

- Support tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimum interrupt latency.

#### SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

## 2.2.22 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to three I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support the Standard-mode (up to 100 kHz) and Fast-mode (up to 400 kHz). They support the 7/10-bit addressing mode and the 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

#### 2.2.23 Universal synchronous/asynchronous receiver transmitters (USART)

The STM32F415xx and STM32F417xx embed four universal synchronous/asynchronous receiver transmitters (USART1, USART2, USART3 and USART6) and two universal asynchronous receiver transmitters (UART4 and UART5).

These six interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to communicate at speeds of up to 10.5 Mbit/s. The other available interfaces communicate at up to 5.25 Mbit/s.

USART1, USART2, USART3 and USART6 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller.

|        | I       | Pin r   | numb    |          |         |                                                      | - <b>P</b> |                 |       | definitions (continued)                                                                                                                                 |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|------------|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type   | I / O structure | Notes | Alternate functions                                                                                                                                     | Additional<br>functions |

| 33     | J3      | 51      | 73      | P12      | 92      | PB12                                                 | I/O        | FT              | -     | SPI2_NSS / I2S2_WS /<br>I2C2_SMBA/<br>USART3_CK/ TIM1_BKIN /<br>CAN2_RX /<br>OTG_HS_ULPI_D5/<br>ETH_RMII_TXD0 /<br>ETH_MII_TXD0/<br>OTG_HS_ID/ EVENTOUT | -                       |

| 34     | J1      | 52      | 74      | P13      | 93      | PB13                                                 | I/O        | FT              | -     | SPI2_SCK / I2S2_CK /<br>USART3_CTS/<br>TIM1_CH1N /CAN2_TX /<br>OTG_HS_ULPI_D6 /<br>ETH_RMII_TXD1 /<br>ETH_MII_TXD1/<br>EVENTOUT                         | OTG_HS_VBUS             |

| 35     | J2      | 53      | 75      | R14      | 94      | PB14                                                 | I/O        | FT              | -     | SPI2_MISO/ TIM1_CH2N /<br>TIM12_CH1 /<br>OTG_HS_DM/<br>USART3_RTS /<br>TIM8_CH2N/I2S2ext_SD/<br>EVENTOUT                                                | -                       |

| 36     | H1      | 54      | 76      | R15      | 95      | PB15                                                 | I/O        | FT              | -     | SPI2_MOSI / I2S2_SD/<br>TIM1_CH3N / TIM8_CH3N<br>/ TIM12_CH2 /<br>OTG_HS_DP/ EVENTOUT                                                                   | RTC_REFIN               |

| -      | H2      | 55      | 77      | P15      | 96      | PD8                                                  | I/O        | FT              | -     | FSMC_D13 / USART3_TX/<br>EVENTOUT                                                                                                                       | -                       |

| -      | H3      | 56      | 78      | P14      | 97      | PD9                                                  | I/O        | FT              | -     | FSMC_D14 / USART3_RX/<br>EVENTOUT                                                                                                                       | -                       |

| -      | G3      | 57      | 79      | N15      | 98      | PD10                                                 | I/O        | FT              | -     | FSMC_D15/USART3_CK/<br>EVENTOUT                                                                                                                         | -                       |

| -      | G1      | 58      | 80      | N14      | 99      | PD11                                                 | I/O        | FT              | -     | FSMC_CLE /<br>FSMC_A16/USART3_CTS/<br>EVENTOUT                                                                                                          | -                       |

| -      | G2      | 59      | 81      | N13      | 100     | PD12                                                 | I/O        | FT              | -     | FSMC_ALE/<br>FSMC_A17/TIM4_CH1 /<br>USART3_RTS/<br>EVENTOUT                                                                                             | -                       |

| 10.0                    | e zo. Periprieral cui | -                        | · /                       | 1      |  |

|-------------------------|-----------------------|--------------------------|---------------------------|--------|--|

|                         |                       | I <sub>DD</sub> (T       |                           |        |  |

| Perip                   | oheral                | Scale1<br>(up t 168 MHz) | Scale2<br>(up to 144 MHz) | Unit   |  |

|                         | OTG_FS                | 26.45                    | 26.67                     | µA/MHz |  |

|                         | DCMI                  | 5.87                     | 5.35                      |        |  |

| AHB2<br>(up to 168 MHz) | RNG                   | 1.50                     | 1.67                      |        |  |

|                         | Hash                  | 9.73                     | 8.86                      |        |  |

|                         | Crypto                | 2.23                     | 2.08                      |        |  |

| AHB3<br>(up to 168 MHz) | FSMC                  | 12.46                    | 11.31                     | µA/MHz |  |

| Bus m                   | atrix <sup>(2)</sup>  | 13.10                    | 11.81                     | µA/MHz |  |

Table 28. Peripheral current consumption (continued)

|                        |                     | -                        | Гур) <sup>(1)</sup>       |        |  |

|------------------------|---------------------|--------------------------|---------------------------|--------|--|

| Perip                  | bheral              | Scale1<br>(up t 168 MHz) | Scale2<br>(up to 144 MHz) | Unit   |  |

|                        | TIM2                | 16.71                    | 16.50                     |        |  |

|                        | TIM3                | 12.33                    | 11.94                     | -      |  |

|                        | TIM4                | 13.45                    | 12.92                     | -      |  |

|                        | TIM5                | 17.14                    | 16.58                     | -      |  |

|                        | TIM6                | 2.43                     | 3.06                      | -      |  |

|                        | TIM7                | 2.43                     | 2.22                      | -      |  |

|                        | TIM12               | 6.62                     | 6.83                      |        |  |

|                        | TIM13               | 5.05                     | 5.47                      |        |  |

|                        | TIM14               | 5.26                     | 5.61                      |        |  |

|                        | PWR                 | 1.00                     | 0.56                      |        |  |

|                        | USART2              | 2.69                     | 2.78                      |        |  |

|                        | USART3              | 2.74                     | 2.78                      |        |  |

| APB1<br>(up to 42 MHz) | UART4               | 3.24                     | 3.33                      | µA/MHz |  |

| (up to +2 mil2)        | UART5               | 2.69                     | 2.78                      |        |  |

|                        | I2C1                | 2.67                     | 2.50                      |        |  |

|                        | I2C2                | 2.83                     | 2.78                      |        |  |

|                        | I2C3                | 2.81                     | 2.78                      |        |  |

|                        | SPI2                | 2.43                     | 2.22                      |        |  |

|                        | SPI3                | 2.43                     | 2.22                      |        |  |

|                        | I2S2 <sup>(3)</sup> | 2.43                     | 2.22                      |        |  |

|                        | I2S3 <sup>(3)</sup> | 2.26                     | 2.22                      |        |  |

|                        | CAN1                | 5.12                     | 5.56                      |        |  |

|                        | CAN2                | 4.81                     | 5.28                      |        |  |

|                        | DAC <sup>(4)</sup>  | 1.67                     | 1.67                      |        |  |

|                        | WWDG                | 1.00                     | 0.83                      |        |  |

Table 28. Peripheral current consumption (continued)

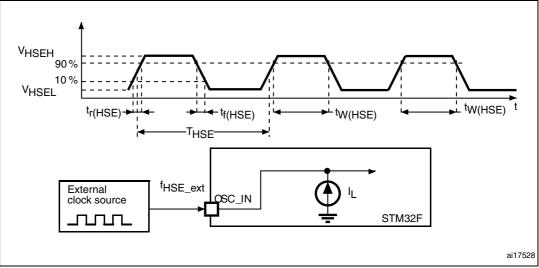

#### Low-speed external user clock generated from an external source

The characteristics given in *Table 31* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                     | Parameter                                              | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------|--------------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                                  | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                  | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                                  | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              | -                                | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             | -                                | 30                 | -      | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage current                         | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

| Table 31. Low-speed external user clock characteristic | s        |

|--------------------------------------------------------|----------|

|                                                        | <u> </u> |

1. Guaranteed by design.

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application, executing EEMBC<sup>?</sup> code, is running. This emission test is compliant with SAE IEC61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                                                     | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ] | Unit                                                                     |               |    |

|------------------|------------|------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------|--------------------------------------------------------------------------|---------------|----|

|                  |            |                                                                                                | inequency band              | 25/168 MHz                                       |                                                                          |               |    |

|                  |            | $V_{1} = 2.2 V_{1} = 25 \circ C_{1} OED 176$                                                   | 0.1 to 30 MHz               | 32                                               |                                                                          |               |    |

|                  |            | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = 25 °C, LQFP176<br>package, conforming to SAE J1752/3 | 30 to 130 MHz               | 25                                               | dBµV                                                                     |               |    |

|                  |            | EEMBC, code running from Flash with ART accelerator enabled                                    | 130 MHz to 1GHz             | 29                                               |                                                                          |               |    |

| 6                | Peak level |                                                                                                | SAE EMI Level               | 4                                                | -                                                                        |               |    |

| S <sub>EMI</sub> |            | reak level                                                                                     | reak level                  | reak level                                       | $V_{DD} = 3.3 \text{ V}, \text{ T}_{A} = 25 \text{ °C}, \text{ LQFP176}$ | 0.1 to 30 MHz | 19 |

|                  |            | package, conforming to SAE J1752/3                                                             | 30 to 130 MHz               | 16                                               | dBµV                                                                     |               |    |

|                  |            | EEMBC, code running from Flash with ART accelerator and PLL spread                             | 130 MHz to 1GHz             | 18                                               |                                                                          |               |    |

|                  |            | spectrum enabled                                                                               | SAE EMI level               | 3.5                                              | -                                                                        |               |    |

| Table 44. EMI characteris |

|---------------------------|

|---------------------------|

#### 5.3.14 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                | Ratings                                                     | Conditions                                                 | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------------|------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge<br>voltage (human body<br>model)    | $T_A = +25 \text{ °C conforming to JESD22-A114}$           | 2     | 2000 <sup>(2)</sup>             | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge<br>voltage (charge device<br>model) | T <sub>A</sub> = +25 °C conforming to<br>ANSI/ESD STM5.3.1 | II    | 500                             | v    |

#### Table 45. ESD absolute maximum ratings

1. Guaranteed by characterization.

2. On  $V_{BAT}$  pin,  $V_{ESD(HBM)}$  is limited to 1000 V.

#### Static latchup

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

#### 5.3.15 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibilty to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of 5  $\mu$ A/+0  $\mu$ A range), or other functional failure (for example reset, oscillator frequency deviation).

Negative induced leakage current is caused by negative injection and positive induced leakage current by positive injection.

The test results are given in Table 47.

| Symbol                         | Paran                                                   | neter                                                                   | Conditions                                                      | Min                               | Тур | Max | Unit |

|--------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------|-----|-----|------|

|                                | FT, TTa and NRS<br>hysteresis                           | ST I/O input                                                            | 1.7 V ≤V <sub>DD</sub> ≤3.6 V                                   | 10%V <sub>DD</sub> <sup>(3)</sup> | -   | -   |      |

| V <sub>HYS</sub>               | BOOT0 I/O input                                         | hystoresis                                                              | 1.75 V ≤V <sub>DD</sub> ≤3.6 V<br>-40 °C≤T <sub>A</sub> ≤105 °C | 0.1                               |     |     | V    |

|                                |                                                         | nysteresis                                                              | 1.7 V ≤V <sub>DD</sub> ≤3.6 V<br>0 °C≤T <sub>A</sub> ≤105 °C    | 0.1                               | -   | -   |      |

|                                | I/O input leakage                                       | e current <sup>(4)</sup>                                                | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub>               | -                                 | -   | ±1  |      |

| l <sub>lkg</sub>               | I/O FT input leak                                       | age current <sup>(5)</sup>                                              | V <sub>IN</sub> = 5 V                                           | -                                 | -   | 3   | μA   |

| R <sub>PU</sub>                | Weak pull-up<br>equivalent<br>resistor <sup>(6)</sup>   | All pins<br>except for<br>PA10 and<br>PB12<br>(OTG_FS_ID,<br>OTG_HS_ID) | V <sub>IN</sub> = V <sub>SS</sub>                               | 30                                | 40  | 50  |      |

|                                | 16313101                                                | PA10 and<br>PB12<br>(OTG_FS_ID,<br>OTG_HS_ID)                           | -                                                               | 7                                 | 10  | 14  | kΩ   |

| R <sub>PD</sub>                | Weak pull-down<br>equivalent<br>resistor <sup>(7)</sup> | All pins<br>except for<br>PA10 and<br>PB12                              | $V_{IN} = V_{DD}$                                               | 30                                | 40  | 50  |      |

|                                |                                                         | PA10 and<br>PB12                                                        | -                                                               | 7                                 | 10  | 14  |      |

| C <sub>IO</sub> <sup>(8)</sup> | I/O pin<br>capacitance                                  |                                                                         |                                                                 | -                                 | 5   | -   | pF   |

Table 48. I/O static characteristics (continued)

1. Guaranteed by design.

2. Tested in production.

3. With a minimum of 200 mV.

- 4. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins.Refer to Table 47: I/O current injection susceptibility

- To sustain a voltage higher than V<sub>DD</sub> + 0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 47: I/O current injection susceptibility.

- Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

- 7. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

- 8. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization.

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters.

## 5.3.18 TIM timer characteristics

The parameters given in Table 52 and Table 53 are guaranteed by design.

Refer to *Section 5.3.16: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                              | Conditions                                                     | Min    | Мах                     | Unit                 |

|------------------------|----------------------------------------|----------------------------------------------------------------|--------|-------------------------|----------------------|

|                        |                                        | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time                  | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>84 MHz | 11.9   | -                       | ns                   |

|                        |                                        | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                        | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 42 MHz                | 23.8   | -                       | ns                   |

| f                      | Timer external clock                   |                                                                | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>       | frequency on CH1 to CH4                |                                                                | 0      | 42                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                       |                                                                | -      | 16/32                   | bit                  |

|                        | 16-bit counter clock                   |                                                                | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| t                      | period when internal clock is selected | f <sub>TIMxCLK</sub> = 84 MHz<br>APB1= 42 MHz                  | 0.0119 | 780                     | μs                   |

| <sup>t</sup> COUNTER   | 32-bit counter clock                   |                                                                | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        | period when internal clock is selected |                                                                | 0.0119 | 51130563                | μs                   |

| +                      | Maximum possible count                 |                                                                | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| <sup>t</sup> MAX_COUNT | Maximum possible count                 |                                                                | -      | 51.1                    | S                    |

Table 52. Characteristics of TIMx connected to the APB1 domain<sup>(1)</sup>

1. TIMx is used as a general term to refer to the TIM2, TIM3, TIM4, TIM5, TIM6, TIM7, and TIM12 timers.

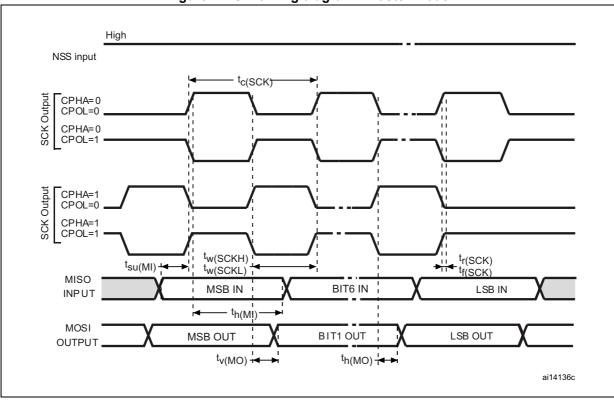

Figure 41. SPI timing diagram - master mode

### I<sup>2</sup>S interface characteristics

Unless otherwise specified, the parameters given in *Table 56* for the  $i^2S$  interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 V<sub>DD</sub>

Refer to Section 5.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CK, SD, WS).

| Symbol                                         | Parameter                                   | Conditions                             | Min         | Max                                 | Unit |

|------------------------------------------------|---------------------------------------------|----------------------------------------|-------------|-------------------------------------|------|

| f <sub>MCK</sub>                               | I <sup>2</sup> S main clock output          | -                                      | 256 x<br>8K | 256 x F <sub>S</sub> <sup>(2)</sup> | MHz  |

| f                                              | I <sup>2</sup> S clock frequency            | Master data: 32 bits                   | -           | 64 x F <sub>S</sub>                 | MHz  |

| f <sub>CK</sub>                                |                                             | Slave data: 32 bits                    | -           | 64 x F <sub>S</sub>                 |      |

| D <sub>CK</sub>                                | I <sup>2</sup> S clock frequency duty cycle | Slave receiver                         | 30          | 70                                  | %    |

| t <sub>v(WS)</sub>                             | WS valid time                               | Master mode                            | 0           | 6                                   |      |

| t <sub>h(WS)</sub>                             | WS hold time                                | Master mode                            | 0           | -                                   |      |

| t <sub>su(WS)</sub>                            | WS setup time                               | Slave mode                             | 1           | -                                   |      |

| t <sub>h(WS)</sub>                             | WS hold time                                | Slave mode                             | 0           | -                                   |      |

| t <sub>su(SD_MR)</sub>                         | Data input setup time                       | Master receiver                        | 7.5         | -                                   |      |

| t <sub>su(SD_SR)</sub>                         |                                             | Slave receiver                         | 2           | -                                   | ns   |

| t <sub>h(SD_MR)</sub>                          | Data input hold time                        | Master receiver                        | 0           | -                                   |      |

| t <sub>h(SD_SR)</sub>                          |                                             | Slave receiver                         | 0           | -                                   |      |

| t <sub>v(SD_ST)</sub><br>t <sub>h(SD_ST)</sub> | Data output valid time                      | Slave transmitter (after enable edge)  | -           | 27                                  |      |

| t <sub>v(SD_MT)</sub>                          |                                             | Master transmitter (after enable edge) | -           | 20                                  |      |

| t <sub>h(SD_MT)</sub>                          | Data output hold time                       | Master transmitter (after enable edge) | 2.5         | -                                   |      |

1. Guaranteed by characterization.

2. The maximum value of 256 x  $F_S$  is 42 MHz (APB1 maximum frequency).

Note: Refer to the  $l^2S$  section of RM0090 reference manual for more details on the sampling frequency ( $F_S$ ).  $f_{MCK}$ ,  $f_{CK}$ , and  $D_{CK}$  values reflect only the digital peripheral behavior. The value of these parameters might be slightly impacted by the source clock accuracy.  $D_{CK}$ depends mainly on the value of ODD bit. The digital contribution leads to a minimum value of I2SDIV / (2 x I2SDIV + ODD) and a maximum value of (I2SDIV + ODD) / (2 x I2SDIV + ODD).  $F_S$  maximum value is supported for each mode/condition.

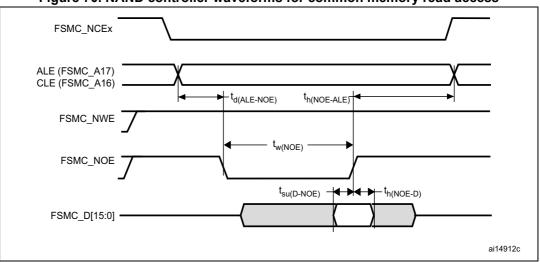

Figure 70. NAND controller waveforms for common memory read access

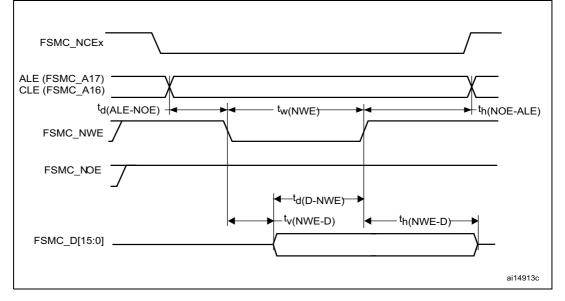

Figure 71. NAND controller waveforms for common memory write access

Table 85. Switching characteristics for NAND Flash read cycles<sup>(1)</sup>

| Symbol                  | Parameter                                    | Min                         | Max                    | Unit |

|-------------------------|----------------------------------------------|-----------------------------|------------------------|------|

| t <sub>w(NOE)</sub>     | FSMC_NOE low width                           | 4T <sub>HCLK</sub> –<br>0.5 | 4T <sub>HCLK</sub> + 3 | ns   |

| t <sub>su(D-NOE)</sub>  | FSMC_D[15-0] valid data before FSMC_NOE high | 10                          | -                      | ns   |

| t <sub>h(NOE-D)</sub>   | FSMC_D[15-0] valid data after FSMC_NOE high  | 0                           | -                      | ns   |

| t <sub>d(ALE-NOE)</sub> | FSMC_ALE valid before FSMC_NOE low           | -                           | 3T <sub>HCLK</sub>     | ns   |

| t <sub>h(NOE-ALE)</sub> | FSMC_NWE high to FSMC_ALE invalid            | 3T <sub>HCLK</sub> – 2      | -                      | ns   |

1. C<sub>L</sub> = 30 pF.

| Date                | Revision                     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date<br>24-Jan-2012 | Revision<br>2<br>(continued) | Changes         Added V <sub>12</sub> in Table 19: Embedded reset and power control block characteristics.         Updated Table 21: Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled) and Table 20: Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator enabled) or RAM. Added Figure , Figure 25, Figure 26, and Figure 27.         Updated Table 22: Typical and maximum current consumption in Sleep mode and removed Note 1.         Updated Table 23: Typical and maximum current consumptions in Stop mode and Table 24: Typical and maximum current consumptions in Stop mode and Table 25: Typical and maximum current consumptions in Standby mode, Table 25: Typical and maximum current consumptions in Standby mode, Table 25: Typical and maximum current consumptions in Standby mode, and Table 27: Switching output I/O current consumption.         Section : On-chip peripheral current consumption: modified conditions, and updated Table 28: Peripheral current consumption and Note 2.         Changed f <sub>HSE_ext</sub> to 50 MHz and t <sub>r(HSE)</sub> /t <sub>f(HSE)</sub> maximum value in Table 30: High-speed external user clock characteristics.         Added C <sub>in(LSE)</sub> in Table 31: Low-speed external user clock characteristics.         Updated maximum PLL input clock frequency, removed related note, and deleted jitter for MCO for RMII Ethernet typical value in Table 36: Main PLL characteristics. Updated maximum PLLI2S input clock frequency and removed related note in Table 37: PLLI2S (audio PLL) characteristics.         Updated Section : Flash memory to specify that the devices are shipped to customers with the Flash memory erased. Updated Table 39: Fl |

Table 100. Document revision history (continued)

|             | lable 1     | 100. Document revision history (continued)                                                                |

|-------------|-------------|-----------------------------------------------------------------------------------------------------------|

| Date        | Revision    | Changes                                                                                                   |

|             |             | Updated Figure 6: Multi-AHB matrix.                                                                       |

|             |             | Updated Figure 7: Power supply supervisor interconnection with internal reset OFF                         |

|             |             | Changed 1.2 V to V <sub>12</sub> in <i>Section : Regulator OFF</i>                                        |

|             |             | Updated LQFP176 pin 48.                                                                                   |

|             |             | Updated Section 1: Introduction.                                                                          |

|             |             | Updated Section 2: Description.                                                                           |

|             |             | Updated operating voltage in <i>Table 2:</i> STM32F415xx and STM32F417xx: features and peripheral counts. |

|             |             | Updated Note 1.                                                                                           |

|             |             | Updated Section 2.2.15: Power supply supervisor.                                                          |

|             |             | Updated Section 2.2.16: Voltage regulator.                                                                |

|             |             | Updated Figure 9: Regulator OFF.                                                                          |

|             |             | Updated Table 3: Regulator ON/OFF and internal reset ON/OFF availability.                                 |

|             |             | Updated Section 2.2.19: Low-power modes.                                                                  |

|             |             | Updated Section 2.2.20: VBAT operation.                                                                   |

|             |             | Updated Section 2.2.22: Inter-integrated circuit interface (I <sup>2</sup> C)                             |

|             |             | Updated pin 48 in Figure 15: STM32F41xxx LQFP176 pinout.                                                  |

|             |             | Updated Table 6: Legend/abbreviations used in the pinout table.                                           |

|             |             | Updated Table 7: STM32F41xxx pin and ball definitions.                                                    |

|             |             | Updated Table 14: General operating conditions.                                                           |

| 04 Jun 2012 | 4           | Updated Table 15: Limitations depending on the operating power                                            |

| 04-Jun-2013 | (continued) | supply range                                                                                              |

|             |             | Updated Section 5.3.7: Wakeup time from low-power mode.                                                   |

|             |             | Updated Table 34: HSI oscillator characteristics.                                                         |

|             |             | Updated Section 5.3.15: I/O current injection characteristics.                                            |

|             |             | Updated Table 48: I/O static characteristics.                                                             |

|             |             | Updated Table 51: NRST pin characteristics.                                                               |

|             |             | Updated Table 56: I <sup>2</sup> C characteristics.                                                       |

|             |             | Updated Figure 39: I <sup>2</sup> C bus AC waveforms and measurement circuit.                             |

|             |             | Updated Section 5.3.19: Communications interfaces.                                                        |

|             |             | Updated Table 67: ADC characteristics.                                                                    |

|             |             | Added Table 70: Temperature sensor calibration values.                                                    |

|             |             | Added Table 73: Internal reference voltage calibration values.                                            |

|             |             | Updated Section 5.3.26: FSMC characteristics.                                                             |

|             |             | Updated Section 5.3.28: SD/SDIO MMC card host interface (SDIO) characteristics.                           |

|             |             | Updated Table 23: Typical and maximum current consumptions in Stop mode.                                  |

|             |             | Updated Section : SPI interface characteristics included Table 55.                                        |

|             |             | Updated Section : I2S interface characteristics included Table 56.                                        |

|             |             | Updated Table 64: Dynamic characteristics: Eternity MAC signals for SMI.                                  |

|             |             | Updated Table 66: Dynamic characteristics: Ethernet MAC signals for MII.                                  |

| Table 100. Document revision history (continued) |

|--------------------------------------------------|

|--------------------------------------------------|