## STMicroelectronics - STM32F417VET6TR Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 82                                                                                        |

| Program Memory Size        | 512KB (512K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192К х 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 100-LQFP                                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f417vet6tr                   |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The STM32F415xx and STM32F417xx family is based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 168 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all ARM single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32F415xx and STM32F417xx family incorporates high-speed embedded memories (Flash memory up to 1 Mbyte, up to 192 Kbytes of SRAM), up to 4 Kbytes of backup SRAM, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, three AHB buses and a 32-bit multi-AHB bus matrix.

All devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve general-purpose 16-bit timers including two PWM timers for motor control, two general-purpose 32-bit timers. a true random number generator (RNG), and a cryptographic acceleration cell. They also feature standard and advanced communication interfaces.

- Up to three I<sup>2</sup>Cs

- Three SPIs, two I<sup>2</sup>Ss full duplex. To achieve audio class accuracy, the I2S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization.

- Four USARTs plus two UARTs

- An USB OTG full-speed and a USB OTG high-speed with full-speed capability (with the ULPI),

- Two CANs

- An SDIO/MMC interface

- Ethernet and the camera interface available on STM32F417xx devices only.

New advanced peripherals include an SDIO, an enhanced flexible static memory control (FSMC) interface (for devices offered in packages of 100 pins and more), a camera interface for CMOS sensors and a cryptographic acceleration cell. Refer to *Table 2: STM32F415xx and STM32F417xx: features and peripheral counts* for the list of peripherals available on each part number.

The STM32F415xx and STM32F417xx family operates in the –40 to +105 °C temperature range from a 1.8 to 3.6 V power supply. The supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor: refer to *Section : Internal reset OFF*. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F415xx and STM32F417xx family offers devices in various packages ranging from 64 pins to 176 pins. The set of included peripherals changes with the device chosen.

These features make the STM32F415xx and STM32F417xx microcontroller family suitable for a wide range of applications:

- Motor drive and application control

- Medical equipment

- Industrial applications: PLC, inverters, circuit breakers

- Printers, and scanners

- Alarm systems, video intercom, and HVAC

- Home audio appliances

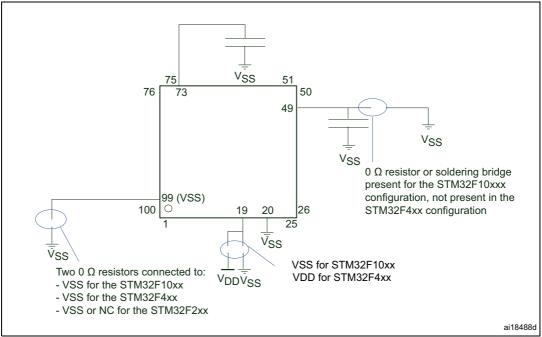

DocID022063 Rev 8

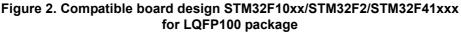

Figure 3. Compatible board design between STM32F10xx/STM32F2/STM32F41xxx for LQFP144 package

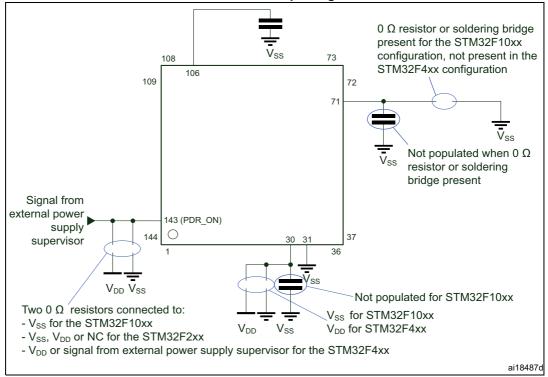

Figure 11. Startup in regulator OFF mode: fast  $V_{DD}$  slope - power-down reset risen before  $V_{CAP}$  <sub>1</sub>/ $V_{CAP}$  <sub>2</sub> stabilization

1. This figure is valid both whatever the internal reset mode (ON or OFF).

2. PDR = 1.7 V for a reduced temperature range; PDR = 1.8 V for all temperature ranges.

## 2.2.17 Regulator ON/OFF and internal reset ON/OFF availability

|                                | Regulator ON                                | Regulator OFF                               | Internal reset ON                       | Internal reset<br>OFF                                            |

|--------------------------------|---------------------------------------------|---------------------------------------------|-----------------------------------------|------------------------------------------------------------------|

| LQFP64<br>LQFP100              | Yes                                         | No                                          | Yes                                     | No                                                               |

| LQFP144                        |                                             |                                             |                                         | Yes                                                              |

| WLCSP90<br>UFBGA176<br>LQFP176 | Yes<br>BYPASS_REG set<br>to V <sub>SS</sub> | Yes<br>BYPASS_REG set<br>to V <sub>DD</sub> | Yes<br>PDR_ON set to<br>V <sub>DD</sub> | PDR_ON<br>connected to an<br>external power<br>supply supervisor |

Table 3. Regulator ON/OFF and internal reset ON/OFF availability

# 2.2.18 Real-time clock (RTC), backup SRAM and backup registers

The backup domain of the STM32F415xx and STM32F417xx includes:

- The real-time clock (RTC)

- 4 Kbytes of backup SRAM

- 20 backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Dedicated registers contain the second, minute, hour (in 12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day of the month are performed automatically. The RTC provides a programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby modes. The sub-seconds value is also available in binary format.

It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-speed RC

### General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F41xxx devices (see *Table 4* for differences).

#### • TIM2, TIM3, TIM4, TIM5

The STM32F41xxx include 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-

bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

### • TIM9, TIM10, TIM11, TIM12, TIM13, and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13, and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

TIM6 and TIM7 support independent DMA request generation.

### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

## 2.2.31 Universal serial bus on-the-go high-speed (OTG\_HS)

The STM32F415xx and STM32F417xx devices embed a USB OTG high-speed (up to 480 Mb/s) device/host/OTG peripheral. The USB OTG HS supports both full-speed and high-speed operations. It integrates the transceivers for full-speed operation (12 MB/s) and features a UTMI low-pin interface (ULPI) for high-speed operation (480 MB/s). When using the USB OTG HS in HS mode, an external PHY device connected to the ULPI is required.

The USB OTG HS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator.

The major features are:

- Combined Rx and Tx FIFO size of 1 Kbit × 35 with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 6 bidirectional endpoints

- 12 host channels with periodic OUT support

- Internal FS OTG PHY support

- External HS or HS OTG operation supporting ULPI in SDR mode. The OTG PHY is connected to the microcontroller ULPI port through 12 signals. It can be clocked using the 60 MHz output.

- Internal USB DMA

- HNP/SNP/IP inside (no need for any external resistor)

- for OTG/Host modes, a power switch is needed in case bus-powered devices are connected

## 2.2.32 Digital camera interface (DCMI)

The camera interface is *not* available in STM32F415xx devices.

STM32F417xx products embed a camera interface that can connect with camera modules and CMOS sensors through an 8-bit to 14-bit parallel interface, to receive video data. The camera interface can sustain a data transfer rate up to 54 Mbyte/s at 54 MHz. It features:

- Programmable polarity for the input pixel clock and synchronization signals

- Parallel data communication can be 8-, 10-, 12- or 14-bit

- Supports 8-bit progressive video monochrome or raw bayer format, YCbCr 4:2:2 progressive video, RGB 565 progressive video or compressed data (like JPEG)

- Supports continuous mode or snapshot (a single frame) mode

- Capability to automatically crop the image

|                     |       |                    | FSMC          |             |                        |                |

|---------------------|-------|--------------------|---------------|-------------|------------------------|----------------|

| Pins <sup>(1)</sup> | CF    | NOR/PSRAM/<br>SRAM | NOR/PSRAM Mux | NAND 16 bit | LQFP100 <sup>(2)</sup> | WLCSP90<br>(2) |

| PF1                 | A1    | A1                 | -             | -           | -                      | -              |

| PF2                 | A2    | A2                 | -             | -           | -                      | -              |

| PF3                 | A3    | A3                 | -             | -           | -                      | -              |

| PF4                 | A4    | A4                 | -             | -           | -                      | -              |

| PF5                 | A5    | A5                 | -             | -           | -                      | -              |

| PF6                 | NIORD | -                  | -             | -           | -                      | -              |

| PF7                 | NREG  | -                  | -             | -           | -                      | -              |

| PF8                 | NIOWR | -                  | -             | -           | -                      | -              |

| PF9                 | CD    | -                  | -             | -           | -                      | -              |

| PF10                | INTR  | -                  | -             | -           | -                      | -              |

| PF12                | A6    | A6                 | -             | -           | -                      | -              |

| PF13                | A7    | A7                 | -             | -           | -                      | -              |

| PF14                | A8    | A8                 | -             | -           | -                      | -              |

| PF15                | A9    | A9                 | -             | -           | -                      | -              |

| PG0                 | A10   | A10                | -             | -           | -                      | -              |

| PG1                 |       | A11                | -             | -           | -                      | -              |

| PE7                 | D4    | D4                 | DA4           | D4          | Yes                    | Yes            |

| PE8                 | D5    | D5                 | DA5           | D5          | Yes                    | Yes            |

| PE9                 | D6    | D6                 | DA6           | D6          | Yes                    | Yes            |

| PE10                | D7    | D7                 | DA7           | D7          | Yes                    | Yes            |

| PE11                | D8    | D8                 | DA8           | D8          | Yes                    | Yes            |

| PE12                | D9    | D9                 | DA9           | D9          | Yes                    | Yes            |

| PE13                | D10   | D10                | DA10          | D10         | Yes                    | Yes            |

| PE14                | D11   | D11                | DA11          | D11         | Yes                    | Yes            |

| PE15                | D12   | D12                | DA12          | D12         | Yes                    | Yes            |

| PD8                 | D13   | D13                | DA13          | D13         | Yes                    | Yes            |

| PD9                 | D14   | D14                | DA14          | D14         | Yes                    | Yes            |

| PD10                | D15   | D15                | DA15          | D15         | Yes                    | Yes            |

| PD11                | -     | A16                | A16           | CLE         | Yes                    | Yes            |

| PD12                | -     | A17                | A17           | ALE         | Yes                    | Yes            |

| PD13                | -     | A18                | A18           | -           | Yes                    | -              |

| PD14                | D0    | D0                 | DA0           | D0          | Yes                    | Yes            |

| PD15                | D1    | D1                 | DA1           | D1          | Yes                    | Yes            |

Table 8. FSMC pin definition (continued)

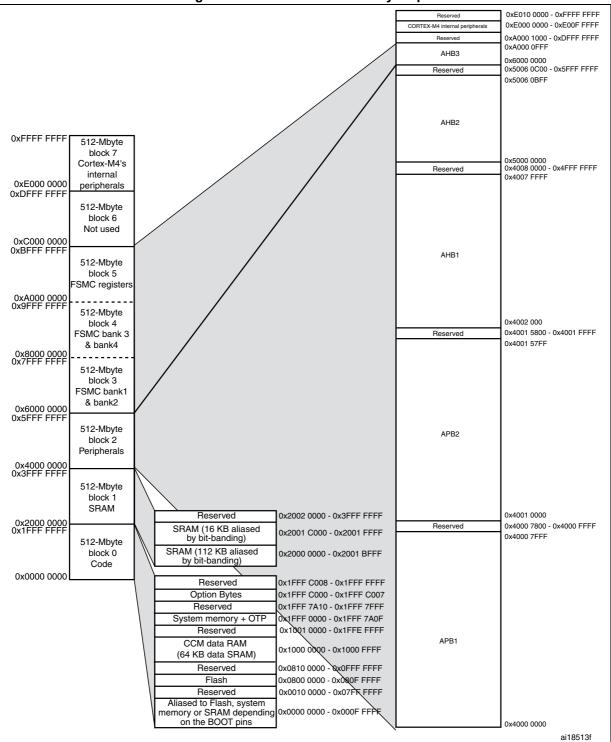

# 4 Memory mapping

The memory map is shown in *Figure 18*.

DocID022063 Rev 8

# 5 Electrical characteristics

# 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

## 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25 \text{ °C}$ ,  $V_{DD} = 3.3 \text{ V}$  (for the 1.8 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

## 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 5.1.4 Loading capacitor

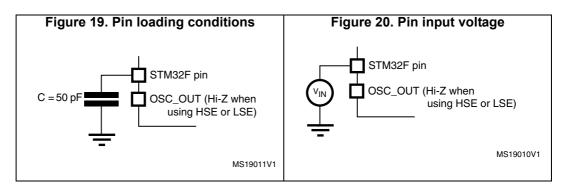

The loading conditions used for pin parameter measurement are shown in *Figure 19*.

### 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 20*.

## Low-speed external user clock generated from an external source

The characteristics given in *Table 31* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                     | Parameter                                              | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------|--------------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                                  | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                  | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                                  | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              | -                                | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             | -                                | 30                 | -      | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage current                         | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

| Table 31. Low-speed external user clock characteristic | s        |

|--------------------------------------------------------|----------|

|                                                        | <u> </u> |

1. Guaranteed by design.

|                          |                                                 |                                          |              | , a, |              |      |

|--------------------------|-------------------------------------------------|------------------------------------------|--------------|------|--------------|------|

| Symbol                   | Parameter                                       | Conditions                               | Min          | Тур  | Max          | Unit |

| I <sub>DD(PLLI2S)</sub>  | ) PLLI2S power consumption on V <sub>DD</sub>   | VCO freq = 100 MHz<br>VCO freq = 432 MHz | 0.15<br>0.45 | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLI2S)</sub> | +) PLLI2S power consumption on V <sub>DDA</sub> | VCO freq = 100 MHz<br>VCO freq = 432 MHz | 0.30<br>0.55 | -    | 0.40<br>0.85 | mA   |

#### Table 37. PLLI2S (audio PLL) characteristics (continued)

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization.

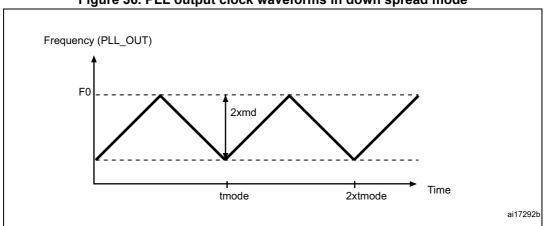

## 5.3.11 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 44: EMI characteristics*). It is available only on the main PLL.

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|-----------------------|------|-----|--------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                 | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                  | %    |

| MODEPER * INCSTEP |                       | -    | -   | 2 <sup>15</sup> –1 | -    |

## Table 38. SSCG parameters constraint

1. Guaranteed by design.

Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

$MODEPER = round[f_{PLL \ IN}/ \ (4 \times f_{Mod})]$

$f_{\text{PLL}\ \text{IN}}$  and  $f_{\text{Mod}}$  must be expressed in Hz.

As an example:

If  $f_{PLL_IN} = 1$  MHz, and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round[ $10^{6}$ / (4 × 10<sup>3</sup>)] = 250

### Equation 2

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[( $(2^{15}-1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$ ]

f<sub>VCO OUT</sub> must be expressed in MHz.

Figure 36. PLL output clock waveforms in down spread mode

## 5.3.12 Memory characteristics

## Flash memory

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified. The devices are shipped to customers with the Flash memory erased.

| Symbol          | Parameter      | Conditions                                  | Min | Тур | Мах | Unit |

|-----------------|----------------|---------------------------------------------|-----|-----|-----|------|

|                 |                | Write / Erase 8-bit mode, $V_{DD}$ = 1.8 V  | -   | 5   | -   |      |

| I <sub>DD</sub> | Supply current | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V | -   | 8   | -   | mA   |

|                 |                | Write / Erase 32-bit mode, $V_{DD}$ = 3.3 V | -   | 12  | -   |      |

Table 39. Flash memory characteristics

| Symbol                 | Parameter                 | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|------------------------|---------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>      | Word programming time     | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |

|                        |                           | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 400  | 800                |      |

| t <sub>ERASE16KB</sub> | Sector (16 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 300  | 600                | ms   |

|                        |                           | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |

|                        |                           | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |

| t <sub>ERASE64KB</sub> | Sector (64 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 700  | 1400               | ms   |

|                        |                           | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |

Table 40. Flash memory programming

|                                 |                                                                                                                                                                                                                                                           | Functional s       | usceptibility      |      |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol                          | Description                                                                                                                                                                                                                                               | Negative injection | Positive injection | Unit |

|                                 | Injected current on BOOT0 pin                                                                                                                                                                                                                             | - 0                | NA                 |      |

|                                 | Injected current on NRST pin                                                                                                                                                                                                                              | - 0                | NA                 |      |

| I <sub>INJ</sub> <sup>(1)</sup> | Injected current on PE2, PE3, PE4, PE5, PE6,<br>PI8, PC13, PC14, PC15, PI9, PI10, PI11, PF0,<br>PF1, PF2, PF3, PF4, PF5, PF10, PH0/OSC_IN,<br>PH1/OSC_OUT, PC0, PC1, PC2, PC3, PB6,<br>PB7, PB8, PB9, PE0, PE1, PI4, PI5, PI6, PI7,<br>PDR_ON, BYPASS_REG | - 0                | NA                 | mA   |

|                                 | Injected current on all FT pins                                                                                                                                                                                                                           | - 5                | NA                 |      |

|                                 | Injected current on any other pin                                                                                                                                                                                                                         | - 5                | +5                 | 1    |

## Table 47. I/O current injection susceptibility

1. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

# 5.3.16 I/O port characteristics

## General input/output characteristics

Unless otherwise specified, the parameters given in *Table 48* are derived from tests performed under the conditions summarized in *Table 14*. All I/Os are CMOS and TTL compliant.

| Symbol          | Parameter                      | Conditions                                                      | Min                                     | Тур | Мах                                     | Unit |

|-----------------|--------------------------------|-----------------------------------------------------------------|-----------------------------------------|-----|-----------------------------------------|------|

|                 | FT, TTa and NRST I/O input low | 1.7 V ≤V <sub>DD</sub> ≤3.6 V                                   | -                                       | -   | 0.3V <sub>DD</sub> -0.04 <sup>(1)</sup> |      |

|                 | level voltage                  | 1.7 V ≤V <sub>DD</sub> ≤3.0 V                                   | -                                       | -   | 0.3V <sub>DD</sub> <sup>(2)</sup>       |      |

| V <sub>IL</sub> | BOOT0 I/O input low level      | 1.75 V ≤V <sub>DD</sub> ≤3.6 V<br>-40 °C≤T <sub>A</sub> ≤105 °C | -                                       | -   | 0.1V <sub>DD</sub> -+0.1 <sup>(1)</sup> |      |

|                 | voltage                        | 1.7 V ≤V <sub>DD</sub> ≤3.6 V<br>0 °C≤T <sub>A</sub> ≤105 °C    | -                                       | -   | 0.1VDD-+0.1                             | v    |

|                 | FT, TTa and NRST I/O input low | 1.7 V ≤V <sub>DD</sub> ≤3.6 V                                   | $0.45V_{DD}$ + $0.3^{(1)}$              | -   | -                                       | V    |

|                 | level voltage                  | 1.7 V ≤VDD ≤0.0 V                                               | 0.7V <sub>DD</sub> <sup>(2)</sup>       | -   | -                                       |      |

| V <sub>IH</sub> | BOOT0 I/O input low level      | 1.75 V ≤V <sub>DD</sub> ≤3.6 V<br>-40 °C≤T <sub>A</sub> ≤105 °C | 0.17V <sub>DD</sub> +0.7 <sup>(1)</sup> | -   | -                                       |      |

|                 | voltage                        | 1.7 V ≤V <sub>DD</sub> ≤3.6 V<br>0 °C≤T <sub>A</sub> ≤105 °C    | 0.17 VDD+0.7 V                          | -   | -                                       |      |

| Table 48. I/O static characteristics |

|--------------------------------------|

|--------------------------------------|

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 37* and *Table 50*, respectively.

Unless otherwise specified, the parameters given in *Table 50* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                                  | Min | Тур | Мах                | Unit |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|--------------------|------|

|                                               |                                                  |                                                                                 | $C_L$ = 50 pF, $V_{DD}$ > 2.70 V                            | -   | -   | 4                  |      |

|                                               | f                                                | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 2                  | MHz  |

|                                               | 'max(IO)out                                      |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 8                  |      |

| 00                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 4                  |      |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.8 V to<br>3.6 V | -   | -   | 100                | ns   |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 25                 |      |

|                                               | f                                                | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 12.5               | MHz  |

|                                               | 'max(IO)out                                      |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 50 <sup>(4)</sup>  |      |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 20                 |      |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> >2.7 V              | -   | -   | 10                 |      |

|                                               | t <sub>f(IO)out</sub> /                          | Output high to low level fall time and output low to high                       | C <sub>L</sub> = 50 pF, V <sub>DD</sub> > 1.8 V             | -   | -   | 20                 | ns   |

|                                               | t <sub>r(IO)out</sub>                            | level rise time                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 6                  | 115  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 10                 |      |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 50 <sup>(4)</sup>  |      |

|                                               | f                                                | Maximum frequency $^{(3)}$                                                      | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 25                 | MHz  |

|                                               | Imax(IO)out                                      | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 100 <sup>(4)</sup> |      |

| 10                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 50 <sup>(4)</sup>  |      |

| 10                                            |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 6                  |      |

|                                               | t <sub>f(IO)out</sub> /                          | Output high to low level fall time and output low to high                       | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 10                 | ns   |

|                                               | t <sub>r(IO)out</sub>                            | level rise time                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 4                  | 115  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 6                  |      |

Table 50. I/O AC characteristics<sup>(1)(2)</sup>

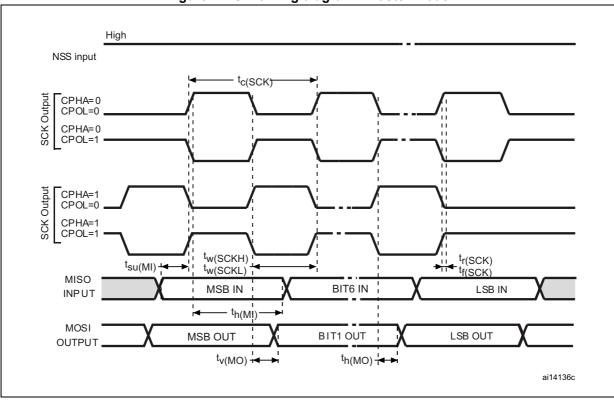

Figure 41. SPI timing diagram - master mode

| Symbol                           | Parameter                                                                          | Conditions                                           | Min                 | Тур       | Max              | Unit               |

|----------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------|---------------------|-----------|------------------|--------------------|

| t <sub>lat</sub> (4)             | Injection trigger conversion                                                       | f <sub>ADC</sub> = 30 MHz                            | -                   | -         | 0.100            | μs                 |

| <sup>l</sup> lat <sup>1</sup>    | latency                                                                            |                                                      | -                   | -         | 3 <sup>(7)</sup> | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (4)            | Regular trigger conversion                                                         | f <sub>ADC</sub> = 30 MHz                            | -                   | -         | 0.067            | μs                 |

| 4atr 1                           | latency                                                                            |                                                      | -                   | -         | 2 <sup>(7)</sup> | 1/f <sub>ADC</sub> |

| ts <sup>(4)</sup>                | Sampling time                                                                      | f <sub>ADC</sub> = 30 MHz                            | 0.100               | -         | 16               | μs                 |

| C C                              |                                                                                    | -                                                    | 3                   | -         | 480              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(4)</sup> | Power-up time                                                                      | -                                                    | -                   | 2         | 3                | μs                 |

|                                  |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution       | 0.50                | -         | 16.40            | μs                 |

|                                  |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution       | 0.43                | -         | 16.34            | μs                 |

| t <sub>CONV</sub> <sup>(4)</sup> | Total conversion time (including sampling time)                                    | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution        | 0.37                | -         | 16.27            | μs                 |

|                                  |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution        | 0.30                | -         | 16.20            | μs                 |

|                                  |                                                                                    | 9 to 492 (t <sub>S</sub> for sampling approximation) | +n-bit resolution f | or succes | ssive            | 1/f <sub>ADC</sub> |

|                                  |                                                                                    | 12-bit resolution<br>Single ADC                      | -                   | -         | 2                | Msps               |

| f <sub>S</sub> <sup>(4)</sup>    | Sampling rate<br>(f <sub>ADC</sub> = 30 MHz, and<br>t <sub>S</sub> = 3 ADC cycles) | 12-bit resolution<br>Interleave Dual ADC<br>mode     | -                   | -         | 3.75             | Msps               |

|                                  |                                                                                    | 12-bit resolution<br>Interleave Triple ADC<br>mode   | -                   | -         | 6                | Msps               |

| I <sub>VREF+</sub> (4)           | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode               | -                                                    | -                   | 300       | 500              | μA                 |

| I <sub>VDDA</sub> <sup>(4)</sup> | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode               | -                                                    | -                   | 1.6       | 1.8              | mA                 |

#### Table 67. ADC characteristics (continued)

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to *Section : Internal reset OFF*).

2. It is recommended to maintain the voltage difference between V\_{REF+} and V\_{DDA} below 1.8 V.

3.  $V_{DDA} - V_{REF+} < 1.2 V.$

4. Guaranteed by characterization.

5.  $V_{REF+}$  is internally connected to  $V_{DDA}$  and  $V_{REF-}$  is internally connected to  $V_{SSA}$ .

6.  $R_{ADC}$  maximum value is given for V<sub>DD</sub>=1.8 V, and minimum value for V<sub>DD</sub>=3.3 V.

7. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in *Table* 67.

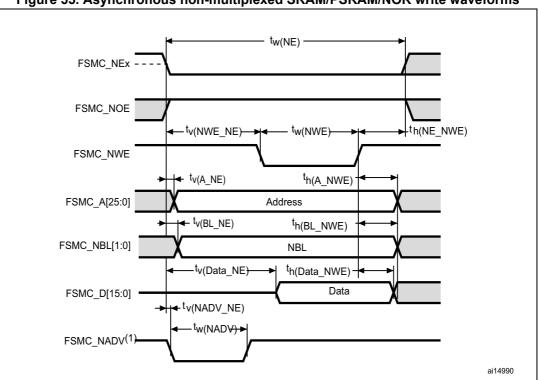

Figure 55. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

| Table 76. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings <sup>(1)(2)</sup> |

|---------------------------------------------------------------------------------------|

| Table To. Asynchronous non-multiplexed Strawn Strawnort write unings                  |

| Symbol                   | Parameter                               | Min                    | Мах                    | Unit |

|--------------------------|-----------------------------------------|------------------------|------------------------|------|

| t <sub>w(NE)</sub>       | FSMC_NE low time                        | 3T <sub>HCLK</sub>     | 3T <sub>HCLK</sub> + 4 | ns   |

| t <sub>v(NWE_NE)</sub>   | FSMC_NEx low to FSMC_NWE low            | T <sub>HCLK</sub> –0.5 | T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NWE)</sub>      | FSMC_NWE low time                       | T <sub>HCLK</sub> –1   | T <sub>HCLK</sub> +2   | ns   |

| t <sub>h(NE_NWE)</sub>   | FSMC_NWE high to FSMC_NE high hold time | T <sub>HCLK</sub> –1   | -                      | ns   |

| t <sub>v(A_NE)</sub>     | FSMC_NEx low to FSMC_A valid            | -                      | 0                      | ns   |

| t <sub>h(A_NWE)</sub>    | Address hold time after FSMC_NWE high   | T <sub>HCLK</sub> – 2  | -                      | ns   |

| t <sub>v(BL_NE)</sub>    | FSMC_NEx low to FSMC_BL valid           | -                      | 1.5                    | ns   |

| t <sub>h(BL_NWE)</sub>   | FSMC_BL hold time after FSMC_NWE high   | T <sub>HCLK</sub> – 1  | -                      | ns   |

| t <sub>v(Data_NE)</sub>  | Data to FSMC_NEx low to Data valid      | -                      | T <sub>HCLK</sub> +3   | ns   |

| t <sub>h(Data_NWE)</sub> | Data hold time after FSMC_NWE high      | T <sub>HCLK</sub> –1   | -                      | ns   |

| t <sub>v(NADV_NE)</sub>  | FSMC_NEx low to FSMC_NADV low           | -                      | 2                      | ns   |

| t <sub>w(NADV)</sub>     | FSMC_NADV low time                      | -                      | T <sub>HCLK</sub> +0.5 | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

### **Device marking for LQFP64**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 80. LPQF64 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

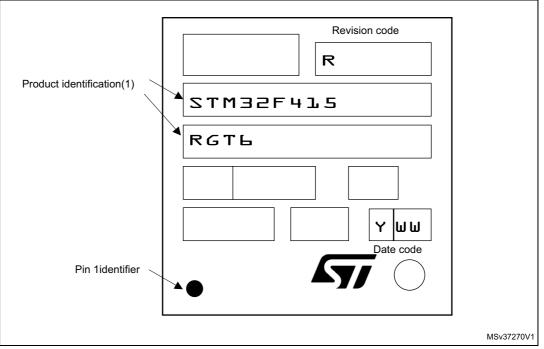

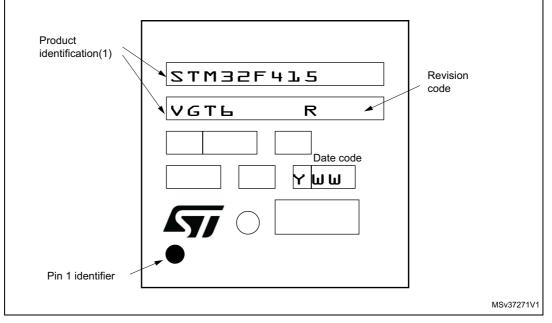

## **Device marking for LFP100**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| Date                | Revision                     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date<br>31-May-2012 | Revision<br>3<br>(continued) | Removed $f_{HSE\_ext}$ typical value in <i>Table 30: High-speed external user clock characteristics</i> . Updated <i>Table 32: HSE 4-26 MHz oscillator characteristics</i> and <i>Table 33: LSE oscillator characteristics (fLSE = 32.768 kHz)</i> .<br>Added $f_{PLL48\_OUT}$ maximum value in <i>Table 36: Main PLL characteristics</i> .<br>Modified equation 1 and 2 in <i>Section 5.3.11: PLL spread spectrum clock generation (SSCG) characteristics</i> .<br>Updated <i>Table 39: Flash memory characteristics, Table 40: Flash memory programming,</i> and <i>Table 41: Flash memory programming with VPP</i> .<br>Updated <i>Section : Output driving current</i> .<br><i>Table 56: I<sup>2</sup>C characteristics: Note 4</i> updated and applied to $t_{h(SDA)}$ in Fast mode, and removed note 4 related to $t_{h(SDA)}$ minimum value.<br>Updated <i>Table 67: ADC characteristics</i> . Updated note concerning ADC accuracy vs. negative injection current below <i>Table 68: ADC accuracy</i> |

|                     |                              | at fADC = 30 MHz.<br>Added WLCSP90 thermal resistance in Table 98: Package thermal<br>characteristics.<br>Updated Table 90: WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch<br>wafer level chip scale package mechanical data.<br>Updated Figure 87: UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch,<br>ultra fine pitch ball grid array package outline and Table 95:<br>UFBGA176+25 ball, 10 × 10 × 0.65 mm pitch, ultra thin fine pitch ball<br>grid array mechanical data.<br>Added Figure 91: LQFP176 - 176-pin, 24 x 24 mm low profile quad flat<br>recommended footprint.<br>Removed 256 and 768 Kbyte Flash memory density from Table 99:<br>Ordering information scheme.                                                                                                                                                                                                                                                                                                                                     |

Table 100. Document revision history (continued)

|             | lable 1     | 100. Document revision history (continued)                                                                |

|-------------|-------------|-----------------------------------------------------------------------------------------------------------|

| Date        | Revision    | Changes                                                                                                   |

|             |             | Updated Figure 6: Multi-AHB matrix.                                                                       |

|             |             | Updated Figure 7: Power supply supervisor interconnection with internal reset OFF                         |

|             |             | Changed 1.2 V to V <sub>12</sub> in <i>Section : Regulator OFF</i>                                        |

|             |             | Updated LQFP176 pin 48.                                                                                   |

|             |             | Updated Section 1: Introduction.                                                                          |

|             |             | Updated Section 2: Description.                                                                           |

|             |             | Updated operating voltage in <i>Table 2:</i> STM32F415xx and STM32F417xx: features and peripheral counts. |

|             |             | Updated Note 1.                                                                                           |

|             |             | Updated Section 2.2.15: Power supply supervisor.                                                          |

|             |             | Updated Section 2.2.16: Voltage regulator.                                                                |

|             |             | Updated Figure 9: Regulator OFF.                                                                          |

|             |             | Updated Table 3: Regulator ON/OFF and internal reset ON/OFF availability.                                 |

|             |             | Updated Section 2.2.19: Low-power modes.                                                                  |

|             |             | Updated Section 2.2.20: VBAT operation.                                                                   |

|             |             | Updated Section 2.2.22: Inter-integrated circuit interface (I <sup>2</sup> C)                             |

|             |             | Updated pin 48 in Figure 15: STM32F41xxx LQFP176 pinout.                                                  |

|             |             | Updated Table 6: Legend/abbreviations used in the pinout table.                                           |

|             |             | Updated Table 7: STM32F41xxx pin and ball definitions.                                                    |

|             |             | Updated Table 14: General operating conditions.                                                           |

| 04 Jun 2012 | 4           | Updated Table 15: Limitations depending on the operating power                                            |

| 04-Jun-2013 | (continued) | supply range                                                                                              |

|             |             | Updated Section 5.3.7: Wakeup time from low-power mode.                                                   |

|             |             | Updated Table 34: HSI oscillator characteristics.                                                         |

|             |             | Updated Section 5.3.15: I/O current injection characteristics.                                            |

|             |             | Updated Table 48: I/O static characteristics.                                                             |

|             |             | Updated Table 51: NRST pin characteristics.                                                               |

|             |             | Updated Table 56: I <sup>2</sup> C characteristics.                                                       |

|             |             | Updated Figure 39: I <sup>2</sup> C bus AC waveforms and measurement circuit.                             |

|             |             | Updated Section 5.3.19: Communications interfaces.                                                        |

|             |             | Updated Table 67: ADC characteristics.                                                                    |

|             |             | Added Table 70: Temperature sensor calibration values.                                                    |

|             |             | Added Table 73: Internal reference voltage calibration values.                                            |

|             |             | Updated Section 5.3.26: FSMC characteristics.                                                             |

|             |             | Updated Section 5.3.28: SD/SDIO MMC card host interface (SDIO) characteristics.                           |

|             |             | Updated Table 23: Typical and maximum current consumptions in Stop mode.                                  |

|             |             | Updated Section : SPI interface characteristics included Table 55.                                        |

|             |             | Updated Section : I2S interface characteristics included Table 56.                                        |

|             |             | Updated Table 64: Dynamic characteristics: Eternity MAC signals for SMI.                                  |

|             |             | Updated Table 66: Dynamic characteristics: Ethernet MAC signals for MII.                                  |

| Table 100. Document revision history (continued) |

|--------------------------------------------------|

|--------------------------------------------------|