# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 82                                                                                        |

| Program Memory Size        | 1MB (1M x 8)                                                                              |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                |                                                                                           |

| RAM Size                   | 192K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 100-LQFP                                                                                  |

| Supplier Device Package    | -                                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f417vgt6                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 8- to 14-bit parallel camera interface up to 54 Mbytes/s

- Cryptographic acceleration: hardware acceleration for AES 128, 192, 256, Triple DES, HASH (MD5, SHA-1), and HMAC

- True random number generator

- CRC calculation unit

- 96-bit unique ID

- RTC: subsecond accuracy, hardware calendar

| Reference   | Part number                                                                  |

|-------------|------------------------------------------------------------------------------|

| STM32F415xx | STM32F415RG, STM32F415VG, STM32F415ZG, STM32F415OG                           |

| STM32F417xx | STM32F417VG, STM32F417IG, STM32F417ZG, STM32F417VE, STM32F417ZE, STM32F417IE |

#### Table 1. Device summary

#### 2.2.8 DMA controller (DMA)

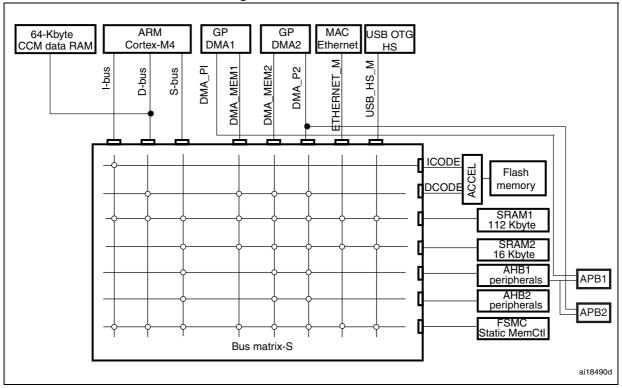

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They feature dedicated FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

#### 2.2.26 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S application. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an  $I^2S$  sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the  $I^2S$  flow with an external PLL (or Codec output).

#### 2.2.27 Secure digital input/output interface (SDIO)

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 48 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

#### 2.2.28 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

Peripheral available only on the STM32F417xx devices.

The STM32F417xx devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard mediumindependent interface (MII) or a reduced medium-independent interface (RMII). The STM32F417xx requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). the PHY is connected to the STM32F417xx MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) from the STM32F417xx.

The STM32F417xx includes the following features:

- Supports 10 and 100 Mbit/s rates

- Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors (see the STM32F40xxx/41xxx reference manual for details)

- Tagged MAC frame support (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes.

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 2008 (PTP V2) with the time stamp comparator connected to the TIM2 input

- Triggers interrupt when system time becomes greater than target time

#### 2.2.29 Controller area network (bxCAN)

The two CANs are compliant with the 2.0A and B (active) specifications with a bitrate up to 1 Mbit/s. They can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Each CAN has three transmit mailboxes, two receive FIFOS with 3 stages and 28 shared scalable filter banks (all of them can be used even if one CAN is used). 256 bytes of SRAM are allocated for each CAN.

#### 2.2.30 Universal serial bus on-the-go full-speed (OTG\_FS)

The STM32F415xx and STM32F417xx embed an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The major features are:

- Combined Rx and Tx FIFO size of 320 × 35 bits with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 4 bidirectional endpoints

- 8 host channels with periodic OUT support

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

|        | F       | Pin r   | numb    | er       |         |                                                      |          |                 |       |                                                                                                         |                                    |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|---------------------------------------------------------------------------------------------------------|------------------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                     | Additional<br>functions            |

| 11     | E9      | 18      | 29      | M5       | 35      | PC3                                                  | I/O      | FT              | (4)   | SPI2_MOSI / I2S2_SD /<br>OTG_HS_ULPI_NXT /<br>ETH_MII_TX_CLK/<br>EVENTOUT                               | ADC123_IN13                        |

| -      | -       | 19      | 30      | -        | 36      | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                                       | -                                  |

| 12     | H10     | 20      | 31      | M1       | 37      | V <sub>SSA</sub>                                     | S        | -               | -     | -                                                                                                       | -                                  |

| -      | -       | -       | -       | N1       | -       | V <sub>REF-</sub>                                    | S        | I               | -     | -                                                                                                       | -                                  |

| -      | -       | 21      | 32      | P1       | 38      | V <sub>REF+</sub>                                    | S        | -               | -     | -                                                                                                       | -                                  |

| 13     | G9      | 22      | 33      | R1       | 39      | V <sub>DDA</sub>                                     | S        | -               | -     | -                                                                                                       | -                                  |

| 14     | C10     | 23      | 34      | N3       | 40      | PA0/WKUP<br>(PA0)                                    | I/O      | FT              | (5)   | USART2_CTS/<br>UART4_TX/<br>ETH_MII_CRS /<br>TIM2_CH1_ETR/<br>TIM5_CH1 / TIM8_ETR/<br>EVENTOUT          | ADC123_IN0/WKU<br>P <sup>(4)</sup> |

| 15     | F8      | 24      | 35      | N2       | 41      | PA1                                                  | I/O      | FT              | (4)   | USART2_RTS /<br>UART4_RX/<br>ETH_RMII_REF_CLK /<br>ETH_MII_RX_CLK /<br>TIM5_CH2 / TIM2_CH2/<br>EVENTOUT | ADC123_IN1                         |

| 16     | J10     | 25      | 36      | P2       | 42      | PA2                                                  | I/O      | FT              | (4)   | USART2_TX/TIM5_CH3 /<br>TIM9_CH1 / TIM2_CH3 /<br>ETH_MDIO/ EVENTOUT                                     | ADC123_IN2                         |

| -      | -       | -       | -       | F4       | 43      | PH2                                                  | I/O      | FT              | -     | ETH_MII_CRS/EVENTOUT                                                                                    | -                                  |

| -      | -       | -       | -       | G4       | 44      | PH3                                                  | I/O      | FT              | -     | ETH_MII_COL/EVENTOUT                                                                                    | -                                  |

| -      | -       | -       | -       | H4       | 45      | PH4                                                  | I/O      | FT              | -     | I2C2_SCL /<br>OTG_HS_ULPI_NXT/<br>EVENTOUT                                                              | -                                  |

| -      | -       | -       | -       | J4       | 46      | PH5                                                  | I/O      | FT              | -     | I2C2_SDA/ EVENTOUT                                                                                      | -                                  |

| 17     | H9      | 26      | 37      | R2       | 47      | PA3                                                  | I/O      | FT              | (4)   | USART2_RX/TIM5_CH4 /<br>TIM9_CH2 / TIM2_CH4 /<br>OTG_HS_ULPI_D0 /<br>ETH_MII_COL/<br>EVENTOUT           | ADC123_IN3                         |

| 18     | E5      | 27      | 38      | -        | -       | V <sub>SS</sub>                                      | S        | -               | -     | -                                                                                                       | -                                  |

| Cumhal          | Devenueter     | Parameter Conditions            |                   | Тур                    | Ма                     | ax <sup>(1)</sup>       | Unit |

|-----------------|----------------|---------------------------------|-------------------|------------------------|------------------------|-------------------------|------|

| Symbol          | Parameter      | Conditions                      | f <sub>HCLK</sub> | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                 |                |                                 | 168 MHz           | 93                     | 109                    | 117                     |      |

|                 |                |                                 | 144 MHz           | 76                     | 89                     | 96                      |      |

|                 |                |                                 | 120 MHz           | 67                     | 79                     | 86                      |      |

|                 |                |                                 | 90 MHz            | 53                     | 65                     | 73                      |      |

|                 |                | External clock <sup>(2)</sup> , | 60 MHz            | 37                     | 49                     | 56                      |      |

|                 |                | all peripherals                 | 30 MHz            | 20                     | 32                     | 39                      |      |

|                 |                | enabled <sup>(3)(4)</sup>       | 25 MHz            | 16                     | 27                     | 35                      |      |

|                 | Supply current |                                 | 16 MHz            | 11                     | 23                     | 30                      | - mA |

|                 |                |                                 | 8 MHz             | 6                      | 18                     | 25                      |      |

|                 |                |                                 | 4 MHz             | 4                      | 16                     | 23                      |      |

|                 |                |                                 | 2 MHz             | 3                      | 15                     | 22                      |      |

| I <sub>DD</sub> | in Run mode    |                                 | 168 MHz           | 46                     | 61                     | 69                      |      |

|                 |                |                                 | 144 MHz           | 40                     | 52                     | 60                      |      |

|                 |                |                                 | 120 MHz           | 37                     | 48                     | 56                      |      |

|                 |                |                                 | 90 MHz            | 30                     | 42                     | 50                      |      |

|                 |                | External clock <sup>(2)</sup> , | 60 MHz            | 22                     | 33                     | 41                      |      |

|                 |                | all peripherals                 | 30 MHz            | 12                     | 24                     | 31                      |      |

|                 |                | disabled <sup>(3)(4)</sup>      | 25 MHz            | 10                     | 21                     | 29                      |      |

|                 |                |                                 | 16 MHz            | 7                      | 19                     | 26                      |      |

|                 |                |                                 | 8 MHz             | 4                      | 16                     | 23                      |      |

|                 |                |                                 | 4 MHz             | 3                      | 15                     | 22                      |      |

|                 |                |                                 | 2 MHz             | 2                      | 14                     | 21                      |      |

## Table 21. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled)

1. Guaranteed by characterization, tested in production at  $V_{\text{DD}}$  max and  $f_{\text{HCLK}}$  max with peripherals enabled.

2. External clock is 4 MHz and PLL is on when  $f_{HCLK}$  > 25 MHz.

3. When analog peripheral blocks such as (ADCs, DACs, HSE, LSE, HSI,LSI) are on, an additional power consumption should be considered.

4. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

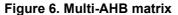

Figure 29. Typical  $V_{BAT}$  current consumption (LSE and RTC ON/backup RAM ON)

Note:

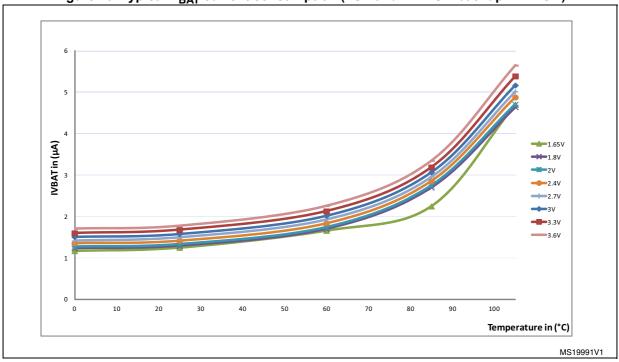

For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <a href="https://www.st.com">www.st.com</a>.

Figure 32. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 33*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                               | Conditions                    | Min | Тур    | Мах  | Unit |

|-------------------------------------|-----------------------------------------|-------------------------------|-----|--------|------|------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency                    | -                             | -   | 32.768 | -    | MHz  |

| R <sub>F</sub>                      | Feedback resistor                       | -                             | -   | 18.4   | -    | MΩ   |

| I <sub>DD</sub>                     | LSE current consumption                 | -                             | -   | -      | 1    | μA   |

| G <sub>m</sub>                      | Oscillator transconductance             | Startup                       | 2.8 | -      | -    |      |

| G <sub>mcritmax</sub>               | Maximum critical crystal G <sub>m</sub> | Startup                       | -   | -      | 0.56 | μΑ/V |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time                            | $V_{\text{DD}}$ is stabilized | -   | 2      | -    | S    |

Table 33. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup>

1. Guaranteed by design.

Guaranteed by characterization. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

Note: For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

A device reset allows normal operations to be resumed.

The test results are given in *Table 43*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                              | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 168 MHz, conforms<br>to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 168 MHz, conforms<br>to IEC 61000-4-2 | 4A              |

#### Table 43. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol                         | Paran                                                   | neter                                                                   | Conditions                                                      | Min                               | Тур | Max | Unit |

|--------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------|-----|-----|------|

|                                | FT, TTa and NRS hysteresis                              | ST I/O input                                                            | 1.7 V ≤V <sub>DD</sub> ≤3.6 V                                   | 10%V <sub>DD</sub> <sup>(3)</sup> | -   | -   |      |

| V <sub>HYS</sub>               |                                                         | hystoresis                                                              | 1.75 V ≤V <sub>DD</sub> ≤3.6 V<br>-40 °C≤T <sub>A</sub> ≤105 °C | 0.1                               |     |     | V    |

|                                | BOOT0 I/O input hysteresis                              |                                                                         | 1.7 V ≤V <sub>DD</sub> ≤3.6 V<br>0 °C≤T <sub>A</sub> ≤105 °C    | 0.1                               | -   | -   |      |

| 1                              | I/O input leakage                                       | e current <sup>(4)</sup>                                                | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub>               | -                                 | -   | ±1  |      |

| l <sub>lkg</sub>               | I/O FT input leak                                       | age current <sup>(5)</sup>                                              | $V_{IN} = 5 V$                                                  | -                                 | -   | 3   | μA   |

| R <sub>PU</sub>                | Weak pull-up<br>equivalent<br>resistor <sup>(6)</sup>   | All pins<br>except for<br>PA10 and<br>PB12<br>(OTG_FS_ID,<br>OTG_HS_ID) | V <sub>IN</sub> = V <sub>SS</sub>                               | 30                                | 40  | 50  |      |

|                                |                                                         | PA10 and<br>PB12<br>(OTG_FS_ID,<br>OTG_HS_ID)                           | -                                                               | 7                                 | 10  | 14  | kΩ   |

| R <sub>PD</sub>                | Weak pull-down<br>equivalent<br>resistor <sup>(7)</sup> | All pins<br>except for<br>PA10 and<br>PB12                              | $V_{IN} = V_{DD}$                                               | 30                                | 40  | 50  |      |

|                                |                                                         | PA10 and PB12                                                           | -                                                               | 7                                 | 10  | 14  |      |

| C <sub>IO</sub> <sup>(8)</sup> | I/O pin<br>capacitance                                  |                                                                         |                                                                 | -                                 | 5   | -   | pF   |

Table 48. I/O static characteristics (continued)

1. Guaranteed by design.

2. Tested in production.

3. With a minimum of 200 mV.

- 4. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins.Refer to Table 47: I/O current injection susceptibility

- To sustain a voltage higher than V<sub>DD</sub> + 0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 47: I/O current injection susceptibility.

- Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

- 7. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

- 8. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization.

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters.

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14 and PC15 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 12*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 12*).

#### Output voltage levels

Unless otherwise specified, the parameters given in *Table 49* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                 | Conditions                                                 | Min                  | Max | Unit |

|-----------------------------------|---------------------------|------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage  | CMOS port                                                  | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage | I <sub>IO</sub> = +8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | V <sub>DD</sub> -0.4 | -   | V    |

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage  | TTL port                                                   | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage | I <sub>IO</sub> =+ 8mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | 2.4                  | -   | V    |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage  | I <sub>IO</sub> = +20 mA                                   | -                    | 1.3 | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> |                           | 2.7 V < V <sub>DD</sub> < 3.6 V                            | V <sub>DD</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage  | I <sub>IO</sub> = +6 mA                                    | -                    | 0.4 | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage | 2 V < V <sub>DD</sub> < 2.7 V                              | V <sub>DD</sub> -0.4 | -   | v    |

Table 49. Output voltage characteristics<sup>(1)</sup>

1. PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these I/Os must not be used as a current source (e.g. to drive an LED).

2. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in Table 12 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 12* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Guaranteed by characterization.

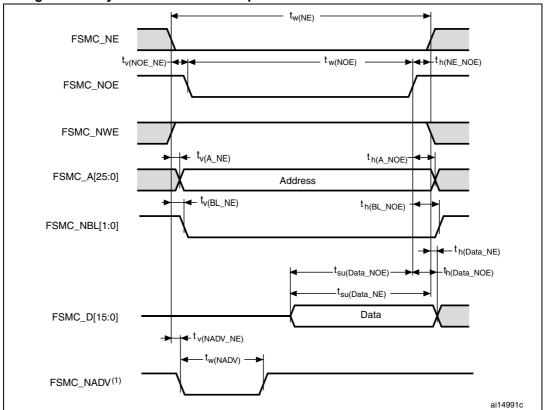

Figure 54. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

#### Table 75. Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                               | Min                     | Max                    | Unit |

|---------------------------|-----------------------------------------|-------------------------|------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                        | 2T <sub>HCLK</sub> -0.5 | 2 T <sub>HCLK</sub> +1 | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low            | 0.5                     | 3                      | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                       | 2T <sub>HCLK</sub> –2   | 2T <sub>HCLK</sub> + 2 | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time | 0                       | -                      | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid            | -                       | 4.5                    | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high   | 4                       | -                      | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid           | -                       | 1.5                    | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL hold time after FSMC_NOE high   | 0                       | -                      | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time        | T <sub>HCLK</sub> +4    | -                      | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOEx high setup time       | T <sub>HCLK</sub> +4    | -                      | ns   |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FSMC_NOE high      | 0                       | -                      | ns   |

| t <sub>h(Data_NE)</sub>   | Data hold time after FSMC_NEx high      | 0                       | -                      | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low           | -                       | 2                      | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                      | -                       | T <sub>HCLK</sub>      | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

| Symbol                      | Parameter                                      | Min                | Max | Unit |

|-----------------------------|------------------------------------------------|--------------------|-----|------|

| t <sub>w(CLK)</sub>         | FSMC_CLK period                                | 2T <sub>HCLK</sub> | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>   | FSMC_CLK low to FSMC_NEx low (x=02)            | -                  | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>   | FSMC_CLK low to FSMC_NEx high (x= 02)          | 2                  | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>  | FSMC_CLK low to FSMC_NADV low                  | -                  | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub>  | FSMC_CLK low to FSMC_NADV high                 | 2                  | -   | ns   |

| t <sub>d(CLKL-AV)</sub>     | FSMC_CLK low to FSMC_Ax valid (x=1625)         | -                  | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>    | FSMC_CLK low to FSMC_Ax invalid (x=1625)       | 0                  | -   | ns   |

| t <sub>d(CLKL-NOEL)</sub>   | FSMC_CLK low to FSMC_NOE low                   | -                  | 0   | ns   |

| t <sub>d(CLKL-NOEH)</sub>   | FSMC_CLK low to FSMC_NOE high                  | 2                  | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>    | FSMC_CLK low to FSMC_AD[15:0] valid            | -                  | 4.5 | ns   |

| t <sub>d(CLKL-ADIV)</sub>   | FSMC_CLK low to FSMC_AD[15:0] invalid          | 0                  | -   | ns   |

| t <sub>su(ADV-CLKH)</sub>   | FSMC_A/D[15:0] valid data before FSMC_CLK high | 6                  | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>    | FSMC_A/D[15:0] valid data after FSMC_CLK high  | 0                  | -   | ns   |

| t <sub>su(NWAIT-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high          | 4                  | -   | ns   |

| t <sub>h(CLKH-NWAIT)</sub>  | FSMC_NWAIT valid after FSMC_CLK high           | 0                  | -   | ns   |

Table 79. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

| Table 84. Switching characteristics for PC Card/CF read and write cycles |

|--------------------------------------------------------------------------|

| in I/O space <sup>(1)(2)</sup>                                           |

| Symbol                       | Parameter                                     | Min                      | Max                      | Unit |

|------------------------------|-----------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NIOWR)</sub>        | FSMC_NIOWR low width                          | 8T <sub>HCLK</sub> –1    | -                        | ns   |

| t <sub>v(NIOWR-D)</sub>      | FSMC_NIOWR low to FSMC_D[15:0] valid          | -                        | 5T <sub>HCLK</sub> – 1   | ns   |

| t <sub>h(NIOWR-D)</sub>      | FSMC_NIOWR high to FSMC_D[15:0] invalid       | 8T <sub>HCLK</sub> – 2   | -                        | ns   |

| t <sub>d(NCE4_1-NIOWR)</sub> | FSMC_NCE4_1 low to FSMC_NIOWR valid           | -                        | 5T <sub>HCLK</sub> + 2.5 | ns   |

| t <sub>h(NCEx-NIOWR)</sub>   | FSMC_NCEx high to FSMC_NIOWR invalid          | 5T <sub>HCLK</sub> –1.5  | -                        | ns   |

| t <sub>d(NIORD-NCEx)</sub>   | FSMC_NCEx low to FSMC_NIORD valid             | -                        | 5T <sub>HCLK</sub> + 2   | ns   |

| t <sub>h(NCEx-NIORD)</sub>   | FSMC_NCEx high to FSMC_NIORD) valid           | 5T <sub>HCLK</sub> – 1.5 | -                        | ns   |

| t <sub>w(NIORD)</sub>        | SMC_NIORD low width 8T <sub>HCLK</sub> =0.5 - |                          | -                        | ns   |

| t <sub>su(D-NIORD)</sub>     | FSMC_D[15:0] valid before FSMC_NIORD high     | 9 -                      |                          | ns   |

| t <sub>d(NIORD-D)</sub>      | FSMC_D[15:0] valid after FSMC_NIORD high      | 0                        | -                        | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

#### NAND controller waveforms and timings

*Figure 68* through *Figure 71* represent synchronous waveforms, and *Table 85* and *Table 86* provide the corresponding timings. The results shown in this table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x01;

- COM.FSMC\_WaitSetupTime = 0x03;

- COM.FSMC\_HoldSetupTime = 0x02;

- COM.FSMC\_HiZSetupTime = 0x01;

- ATT.FSMC\_SetupTime = 0x01;

- ATT.FSMC\_WaitSetupTime = 0x03;

- ATT.FSMC\_HoldSetupTime = 0x02;

- ATT.FSMC\_HiZSetupTime = 0x01;

- Bank = FSMC\_Bank\_NAND;

- MemoryDataWidth = FSMC\_MemoryDataWidth\_16b;

- ECC = FSMC\_ECC\_Enable;

- ECCPageSize = FSMC\_ECCPageSize\_512Bytes;

- TCLRSetupTime = 0;

- TARSetupTime = 0.

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

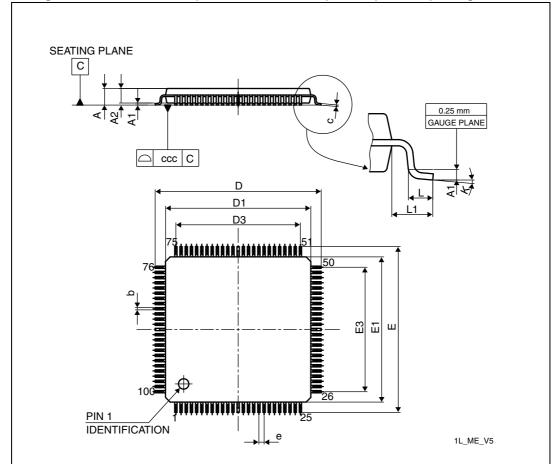

## 6.3 LQPF100 package information

Figure 81. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

Table 93. LQPF100 – 100-pin, 14 x 14 mm low-profile quad flat package mechanical data<sup>(1)</sup>

| Symbol |        | millimeters |        |        | inches |        |  |

|--------|--------|-------------|--------|--------|--------|--------|--|

|        | Min    | Тур         | Мах    | Min    | Тур    | Мах    |  |

| A      | -      | -           | 1.600  | -      | -      | 0.0630 |  |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -      | 0.0059 |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551 | 0.0571 |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087 | 0.0106 |  |

| С      | 0.090  | -           | 0.200  | 0.0035 | -      | 0.0079 |  |

| D      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299 | 0.6378 |  |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512 | 0.5591 |  |

| D3     | -      | 12.000      | -      | -      | 0.4724 | -      |  |

| E      | 15.80  | 16.000      | 16.200 | 0.6220 | 0.6299 | 0.6378 |  |

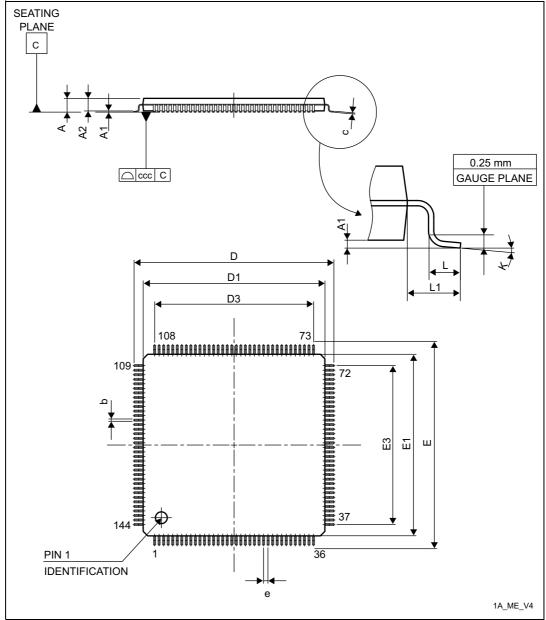

## 6.4 LQFP144 package information

Figure 84. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline

1. Drawing is not to scale.

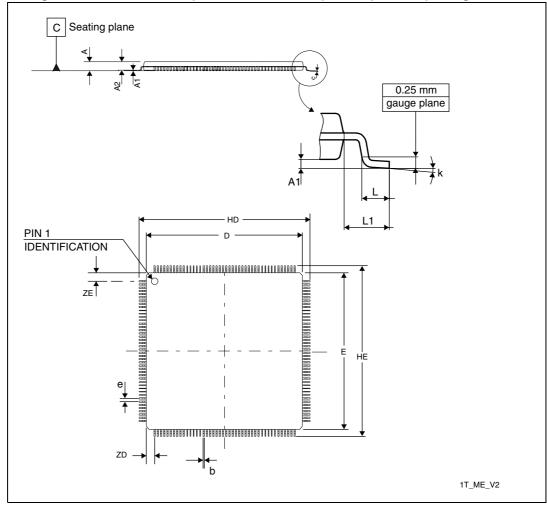

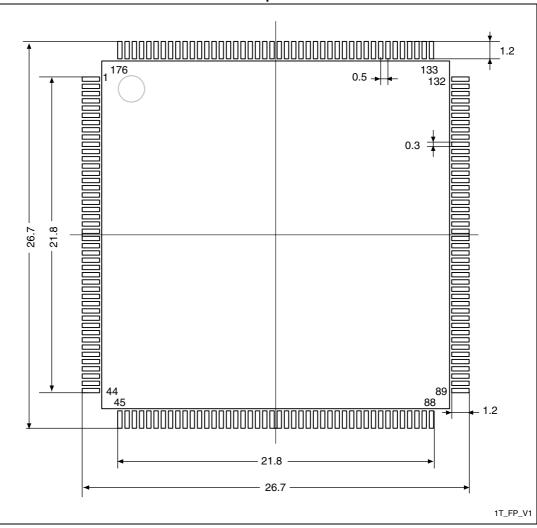

### 6.6 LQFP176 package information

Figure 90. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline

1. Drawing is not to scale.

## Table 97. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat packagemechanical data

| Symbol |        | millimeters |        |        | inches <sup>(1)</sup> |        |  |

|--------|--------|-------------|--------|--------|-----------------------|--------|--|

|        | Min    | Тур         | Мах    | Min    | Тур                   | Max    |  |

| А      | -      | -           | 1.600  | -      | -                     | 0.0630 |  |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |  |

| A2     | 1.350  | -           | 1.450  | 0.0531 | -                     | 0.0571 |  |

| b      | 0.170  | -           | 0.270  | 0.0067 | -                     | 0.0106 |  |

| С      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |  |

| D      | 23.900 | -           | 24.100 | 0.9409 | -                     | 0.9488 |  |

| HD     | 25.900 | -           | 26.100 | 1.0197 | -                     | 1.0276 |  |

Figure 91. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

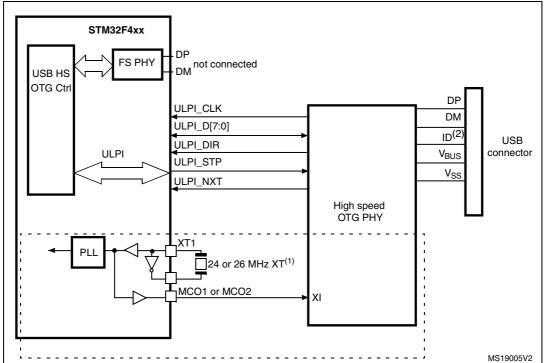

### A.2 USB OTG high speed (HS) interface solutions

Figure 96. USB controller configured as peripheral, host, or dual-mode and used in high speed mode

It is possible to use MCO1 or MCO2 to save a crystal. It is however not mandatory to clock the STM32F41xxx with a 24 or 26 MHz crystal when using USB HS. The above figure only shows an example of a possible connection.

<sup>2.</sup> The ID pin is required in dual role only.

| Table 100. Document revision history (continued) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|--------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Date                                             | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Date                                             |          | Changes           Modified Note 1 below Table 2: STM32F415xx and STM32F417xx:<br>features and peripheral counts.           Updated Figure 4 title.           Updated Note 3 below Figure 21: Power supply scheme.           Changed simplex mode into half-duplex mode in Section 2.2.25: Inter-<br>integrated sound (I2S).           Replaced DAC1_OUT and DAC2_OUT by DAC_OUT1 and<br>DAC_OUT2, respectively.           Updated pin 36 signal in Figure 15: STM32F41xxx LQFP176 pinout.           Changed pin number from F8 to D4 for PA13 pin in Table 7:<br>STM32F41xxx pin and ball definitions.           Replaced TIM2_CH1/TIM2_ETR by TIM2_CH1_ETR for PA0 and PA5<br>pins in Table 9: Alternate function mapping.           Changed system memory into System memory + OTP in Figure 18:<br>STM32F41xxx memory map.           Added Note 1 below Table 16: VCAP_1/VCAP_2 operating conditions.           Updated I <sub>DDA</sub> description in Table 74: DAC characteristics.           Removed PA9/PB13 connection to VBUS in Figure 93: USB controller<br>configured as peripheral-only and used in Full speed mode and<br>Figure 94: USB controller configured as host-only and used in full<br>speed mode.           Updated SPI throughput on front page and Section 2.2.24: Serial<br>peripheral interface (SPI)           Updated operating voltages in Table 2: STM32F415xx and<br>STM32F417xx: features and peripheral counts           Updated Section 2.2.15: Power supply schemes           Updated operating voltages in Table 2: STM32F415xx and<br>STM32F417xx: features and peripheral counts           Updated Table 18: Section 2.2.19: Low-power |  |

|                                                  |          | Updated Table 44: EMI characteristics<br>Updated Table 49: Output voltage characteristics<br>Updated Table 51: NRST pin characteristics<br>Updated Table 55: SPI dynamic characteristics<br>Updated Table 56: I2S dynamic characteristics<br>Deleted Table 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                                                  |          | Updated Table 62: ULPI timing<br>Updated Figure 46: Ethernet SMI timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

Table 100. Document revision history (continued)