# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 82                                                                                        |

| Program Memory Size        | 1MB (1M x 8)                                                                              |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 100-LQFP                                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f417vgt7                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core with FPU and embedded Flash and SRAM

The ARM Cortex-M4 processor with FPU is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM Cortex-M4 32-bit RISC processor with FPU features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F415xx and STM32F417xx family is compatible with all ARM tools and software.

*Figure 5* shows the general block diagram of the STM32F41xxx family.

Note: Cortex-M4 with FPU is binary compatible with Cortex-M3.

### 2.2.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processors. It balances the inherent performance advantage of the ARM Cortex-M4 with FPU over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor full 210 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 168 MHz.

### 2.2.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

### 2.2.4 Embedded Flash memory

The STM32F41xxx devices embed a Flash memory of 512 Kbytes or 1 Mbytes available for storing programs and data.

DocID022063 Rev 8

|        | 1       | Pin r   | numb    |          |         |                                                      |          | unu             |       | definitions (continued)                                                               |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|---------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                   | Additional<br>functions |

| 40     | E3      | 66      | 99      | F14      | 118     | PC9                                                  | I/O      | FT              | -     | I2S_CKIN/ MCO2 /<br>TIM8_CH4/SDIO_D1 /<br>/I2C3_SDA / DCMI_D3 /<br>TIM3_CH4/ EVENTOUT | -                       |

| 41     | D1      | 67      | 100     | F15      | 119     | PA8                                                  | I/O      | FT              | -     | MCO1 / USART1_CK/<br>TIM1_CH1/ I2C3_SCL/<br>OTG_FS_SOF/<br>EVENTOUT                   | -                       |

| 42     | D2      | 68      | 101     | E15      | 120     | PA9                                                  | I/O      | FT              | -     | USART1_TX/ TIM1_CH2 /<br>I2C3_SMBA / DCMI_D0/<br>EVENTOUT                             | OTG_FS_VBUS             |

| 43     | D3      | 69      | 102     | D15      | 121     | PA10                                                 | I/O      | FT              | -     | USART1_RX/ TIM1_CH3/<br>OTG_FS_ID/DCMI_D1/<br>EVENTOUT                                | -                       |

| 44     | C1      | 70      | 103     | C15      | 122     | PA11                                                 | I/O      | FT              | -     | USART1_CTS / CAN1_RX<br>/ TIM1_CH4 /<br>OTG_FS_DM/ EVENTOUT                           | -                       |

| 45     | C2      | 71      | 104     | B15      | 123     | PA12                                                 | I/O      | FT              | -     | USART1_RTS/CAN1_TX/<br>TIM1_ETR/OTG_FS_DP/<br>EVENTOUT                                | -                       |

| 46     | D4      | 72      | 105     | A15      | 124     | PA13<br>(JTMS-SWDIO)                                 | I/O      | FT              | -     | JTMS-SWDIO/ EVENTOUT                                                                  | -                       |

| 47     | B1      | 73      | 106     | F13      | 125     | V <sub>CAP_2</sub>                                   | S        | -               | -     | -                                                                                     | -                       |

| -      | E7      | 74      | 107     | F12      | 126     | V <sub>SS</sub>                                      | S        | -               | -     | -                                                                                     | -                       |

| 48     | E6      | 75      | 108     | G13      | 127     | V <sub>DD</sub>                                      | S        | -               | -     | -                                                                                     | -                       |

| -      | -       | -       | -       | E12      | 128     | PH13                                                 | I/O      | FT              | -     | TIM8_CH1N / CAN1_TX/<br>EVENTOUT                                                      | -                       |

| -      | -       | -       | -       | E13      | 129     | PH14                                                 | I/O      | FT              | -     | TIM8_CH2N / DCMI_D4/<br>EVENTOUT                                                      | -                       |

| -      | -       | -       | -       | D13      | 130     | PH15                                                 | I/O      | FT              | -     | TIM8_CH3N / DCMI_D11/<br>EVENTOUT                                                     | -                       |

| -      | C3      | -       | -       | E14      | 131     | PI0                                                  | I/O      | FT              | -     | TIM5_CH4 / SPI2_NSS /<br>I2S2_WS / DCMI_D13/<br>EVENTOUT                              | -                       |

| -      | B2      | -       | -       | D14      | 132     | PI1                                                  | I/O      | FT              | -     | SPI2_SCK / I2S2_CK /<br>DCMI_D8/ EVENTOUT                                             | -                       |

Table 7. STM32F41xxx pin and ball definitions (continued)

68/206

DocID022063 Rev 8

|        |      | AF0 | AF1    | AF2      | AF3              | AF4      | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10              | AF11 | AF12                   | AF13     |      |          |

|--------|------|-----|--------|----------|------------------|----------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|-------------------|------|------------------------|----------|------|----------|

| Port   |      | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3 | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS | ЕТН  | FSMC/SDIO<br>/OTG_FS   | DCMI     | AF14 | AF15     |

|        | PD0  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | CAN1_RX                   | -                 | -    | FSMC_D2                | -        | -    | EVENTOUT |

|        | PD1  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | CAN1_TX                   | -                 | -    | FSMC_D3                | -        | -    | EVENTOUT |

|        | PD2  | -   | -      | TIM3_ETR | -                | -        | -                              | -                    | -                      | UART5_RX           | -                         | -                 | -    | SDIO_CMD               | DCMI_D11 | -    | EVENTOUT |

|        | PD3  | -   | -      | -        | -                | -        | -                              | -                    | USART2_CTS             | -                  | -                         | -                 | -    | FSMC_CLK               | -        | -    | EVENTOUT |

|        | PD4  | -   | -      | -        | -                | -        | -                              | -                    | USART2_RTS             | -                  | -                         | -                 | -    | FSMC_NOE               | -        | -    | EVENTOUT |

|        | PD5  | -   | -      | -        | -                | -        | -                              | -                    | USART2_TX              | -                  | -                         | -                 | -    | FSMC_NWE               | -        | -    | EVENTOUT |

|        | PD6  | -   | -      | -        | -                | -        | -                              | -                    | USART2_RX              | -                  | -                         | -                 | -    | FSMC_NWAIT             | -        | -    | EVENTOUT |

| Port D | PD7  | -   | -      | -        | -                | -        | -                              | -                    | USART2_CK              | -                  | -                         | -                 | -    | FSMC_NE1/<br>FSMC_NCE2 | -        | -    | EVENTOUT |

|        | PD8  | -   | -      | -        | -                | -        | -                              | -                    | USART3_TX              | -                  | -                         | -                 | -    | FSMC_D13               | -        | -    | EVENTOUT |

|        | PD9  | -   | -      | -        | -                | -        | -                              | -                    | USART3_RX              | -                  | -                         | -                 | -    | FSMC_D14               | -        | -    | EVENTOUT |

|        | PD10 | -   | -      | -        | -                | -        | -                              | -                    | USART3_CK              | -                  | -                         | -                 | -    | FSMC_D15               | -        | -    | EVENTOUT |

|        | PD11 | -   | -      | -        | -                | -        | -                              | -                    | USART3_CTS             | -                  | -                         | -                 | -    | FSMC_A16               | -        | -    | EVENTOUT |

|        | PD12 | -   | -      | TIM4_CH1 | -                | -        | -                              | -                    | USART3_RTS             | -                  | -                         | -                 | -    | FSMC_A17               | -        | -    | EVENTOUT |

|        | PD13 | -   | -      | TIM4_CH2 | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A18               | -        | -    | EVENTOUT |

|        | PD14 | -   | -      | TIM4_CH3 | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_D0                | -        | -    | EVENTOUT |

|        | PD15 | -   | -      | TIM4_CH4 | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_D1                | -        | -    | EVENTOUT |

Table 9. Alternate function mapping (continued)

577

| Bus  | Boundary address          | Peripheral          |

|------|---------------------------|---------------------|

|      | 0x4000 7800 - 0x4000 7FFF | Reserved            |

|      | 0x4000 7400 - 0x4000 77FF | DAC                 |

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |

|      | 0x4000 6C00 - 0x4000 6FFF | Reserved            |

|      | 0x4000 6800 - 0x4000 6BFF | CAN2                |

|      | 0x4000 6400 - 0x4000 67FF | CAN1                |

|      | 0x4000 6000 - 0x4000 63FF | Reserved            |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |

|      | 0x4000 5800 - 0x4000 5BFF | 12C2                |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |

|      | 0x4000 5000 - 0x4000 53FF | UART5               |

|      | 0x4000 4C00 - 0x4000 4FFF | UART4               |

|      | 0x4000 4800 - 0x4000 4BFF | USART3              |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |

|      | 0x4000 4000 - 0x4000 43FF | I2S3ext             |

| APB1 | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |

|      | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |

|      | 0x4000 3400 - 0x4000 37FF | I2S2ext             |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |

|      | 0x4000 2400 - 0x4000 27FF | Reserved            |

|      | 0x4000 2000 - 0x4000 23FF | TIM14               |

|      | 0x4000 1C00 - 0x4000 1FFF | TIM13               |

|      | 0x4000 1800 - 0x4000 1BFF | TIM12               |

|      | 0x4000 1400 - 0x4000 17FF | TIM7                |

|      | 0x4000 1000 - 0x4000 13FF | TIM6                |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |

|      | 0x4000 0400 - 0x4000 07FF | TIM3                |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |

Table 10. STM32F41x register boundary addresses (continued)

| Operating<br>power<br>supply<br>range            | ADC<br>operation                     | Maximum<br>Flash<br>memory<br>access<br>frequency<br>with no wait<br>state<br>(f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency<br>with wait<br>states <sup>(1) (2)</sup> | I/O operation                                                                                  | Clock output<br>Frequency on<br>I/O pins                                                                                                             | Possible<br>Flash<br>memory<br>operations        |

|--------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| V <sub>DD</sub> =1.8 to<br>2.1 V <sup>(3)</sup>  | Conversion<br>time up to<br>1.2 Msps | 20 MHz <sup>(4)</sup>                                                                                  | 160 MHz with 7<br>wait states                                                         | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>No I/O<br/>compensation</li> </ul>        | up to 30 MHz                                                                                                                                         | 8-bit erase<br>and program<br>operations<br>only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                | Conversion<br>time up to<br>1.2 Msps | 22 MHz                                                                                                 | 168 MHz with 7<br>wait states                                                         | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>No I/O<br/>compensation</li> </ul>        | up to 30 MHz                                                                                                                                         | 16-bit erase<br>and program<br>operations        |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                | Conversion<br>time up to<br>2.4 Msps | 24 MHz                                                                                                 | 168 MHz with 6<br>wait states                                                         | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>I/O<br/>compensation<br/>works</li> </ul> | up to 48 MHz                                                                                                                                         | 16-bit erase<br>and program<br>operations        |

| V <sub>DD</sub> = 2.7 to<br>3.6 V <sup>(5)</sup> | Conversion<br>time up to<br>2.4 Msps | 30 MHz                                                                                                 | 168 MHz with 5<br>wait states                                                         | <ul> <li>Full-speed<br/>operation</li> <li>I/O<br/>compensation<br/>works</li> </ul>           | <ul> <li>up to<br/>60 MHz<br/>when V<sub>DD</sub> =<br/>3.0 to 3.6 V</li> <li>up to<br/>48 MHz<br/>when V<sub>DD</sub> =<br/>2.7 to 3.0 V</li> </ul> | 32-bit erase<br>and program<br>operations        |

Table 15. Limitations depending on the operating power supply range

1. It applies only when code executed from Flash memory access, when code executed from RAM, no wait state is required.

2. Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

3. V<sub>DD</sub>/VDDA minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to *Section : Internal reset OFF*).

4. Prefetch is not available. Refer to AN3430 application note for details on how to adjust performance and power.

5. The voltage range for OTG USB FS can drop down to 2.7 V. However it is degraded between 2.7 and 3 V.

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 28*. The MCU is placed under the following conditions:

- At startup, all I/O pins are configured as analog pins by firmware.

- All peripherals are disabled unless otherwise mentioned

- The code is running from Flash memory and the Flash memory access time is equal to 5 wait states at 168 MHz.

- The code is running from Flash memory and the Flash memory access time is equal to 4 wait states at 144 MHz, and the power scale mode is set to 2.

- The ART accelerator is ON.

- The given value is calculated by measuring the difference of current consumption

- with all peripherals clocked off

- with one peripheral clocked on (with only the clock applied)

- When the peripherals are enabled: HCLK is the system clock, f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2.

- The typical values are obtained for V<sub>DD</sub> = 3.3 V and T<sub>A</sub>= 25 °C, unless otherwise specified.

|                 |                                                    | I <sub>DD</sub> (T       | I <sub>DD</sub> (Typ) <sup>(1)</sup> |        |  |  |

|-----------------|----------------------------------------------------|--------------------------|--------------------------------------|--------|--|--|

| Perip           | heral                                              | Scale1<br>(up t 168 MHz) | Scale2<br>(up to 144 MHz)            | Unit   |  |  |

|                 | GPIOA                                              | 2.70                     | 2.40                                 |        |  |  |

|                 | GPIOB                                              | 2.50                     | 2.22                                 |        |  |  |

|                 | GPIOC                                              | 2.54                     | 2.28                                 |        |  |  |

|                 | GPIOD                                              | 2.55                     | 2.28                                 |        |  |  |

|                 | GPIOE                                              | 2.68                     | 2.40                                 |        |  |  |

|                 | GPIOF                                              | 2.53                     | 2.28                                 |        |  |  |

|                 | GPIOG                                              | 2.51                     | 2.22                                 |        |  |  |

|                 | GPIOH                                              | 2.51                     | 2.22                                 |        |  |  |

| AHB1            | GPIOI                                              | 2.50                     | 2.22                                 | µA/MHz |  |  |

| (up to 168 MHz) | OTG_HS+ULPI                                        | 28.33                    | 25.38                                |        |  |  |

|                 | CRC                                                | 0.41                     | 0.40                                 |        |  |  |

|                 | BKPSRAM                                            | 0.63                     | 0.58                                 |        |  |  |

|                 | DMA1                                               | 37.44                    | 33.58                                |        |  |  |

|                 | DMA2                                               | 37.69                    | 33.93                                |        |  |  |

|                 | ETH_MAC<br>ETH_MAC_TX<br>ETH_MAC_RX<br>ETH_MAC_PTP | 20.43                    | 18.39                                |        |  |  |

Table 28. Peripheral current consumption

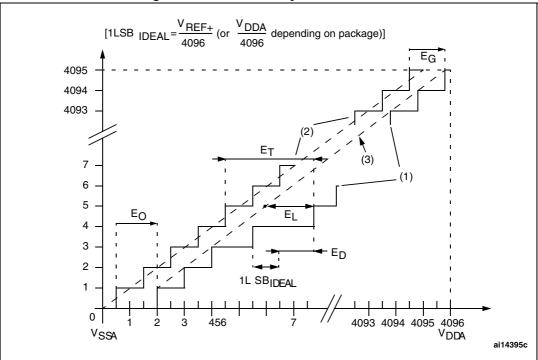

Figure 49. ADC accuracy characteristics

- See also Table 68. 1.

- 2. Example of an actual transfer curve.

- Ideal transfer curve. 3.

- 4. End point correlation line.

- $E_T$  = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. 5. EG = Offset Error: deviation between the first actual transition and the first ideal one. EG = Gain Error: deviation between the last ideal transition and the last actual one.

- ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one.

EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

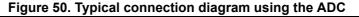

- Refer to Table 67 for the values of  $\mathsf{R}_{AIN},\,\mathsf{R}_{ADC}\,\text{and}\,\mathsf{C}_{ADC}.$ 1.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 5 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced. 2.

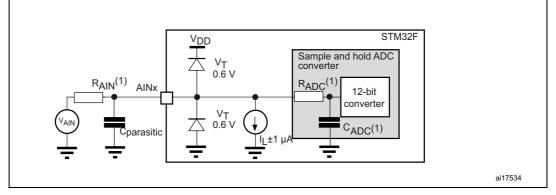

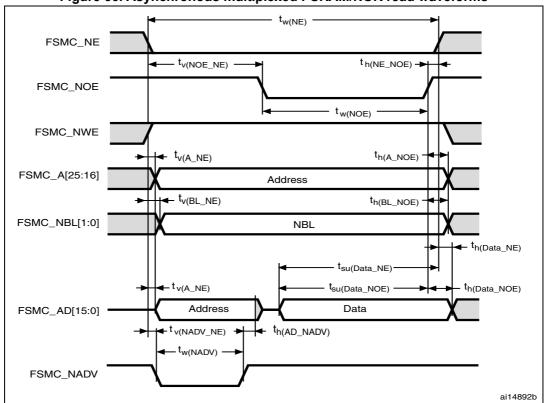

Figure 55. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

| Table 76. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings <sup>(1)(2)</sup> |

|---------------------------------------------------------------------------------------|

| Table To. Asynchronous non-multiplexed Strawn Strawnort write unings                  |

| Symbol                   | Parameter                               | Min                    | Мах                    | Unit |

|--------------------------|-----------------------------------------|------------------------|------------------------|------|

| t <sub>w(NE)</sub>       | FSMC_NE low time                        | 3T <sub>HCLK</sub>     | 3T <sub>HCLK</sub> + 4 | ns   |

| t <sub>v(NWE_NE)</sub>   | FSMC_NEx low to FSMC_NWE low            | T <sub>HCLK</sub> –0.5 | T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NWE)</sub>      | FSMC_NWE low time                       | T <sub>HCLK</sub> –1   | T <sub>HCLK</sub> +2   | ns   |

| t <sub>h(NE_NWE)</sub>   | FSMC_NWE high to FSMC_NE high hold time | T <sub>HCLK</sub> –1   | -                      | ns   |

| t <sub>v(A_NE)</sub>     | FSMC_NEx low to FSMC_A valid            | -                      | 0                      | ns   |

| t <sub>h(A_NWE)</sub>    | Address hold time after FSMC_NWE high   | T <sub>HCLK</sub> – 2  | -                      | ns   |

| t <sub>v(BL_NE)</sub>    | FSMC_NEx low to FSMC_BL valid           | -                      | 1.5                    | ns   |

| t <sub>h(BL_NWE)</sub>   | FSMC_BL hold time after FSMC_NWE high   | T <sub>HCLK</sub> – 1  | -                      | ns   |

| t <sub>v(Data_NE)</sub>  | Data to FSMC_NEx low to Data valid      | -                      | T <sub>HCLK</sub> +3   | ns   |

| t <sub>h(Data_NWE)</sub> | Data hold time after FSMC_NWE high      | T <sub>HCLK</sub> –1   | -                      | ns   |

| t <sub>v(NADV_NE)</sub>  | FSMC_NEx low to FSMC_NADV low           | -                      | 2                      | ns   |

| t <sub>w(NADV)</sub>     | FSMC_NADV low time                      | -                      | T <sub>HCLK</sub> +0.5 | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

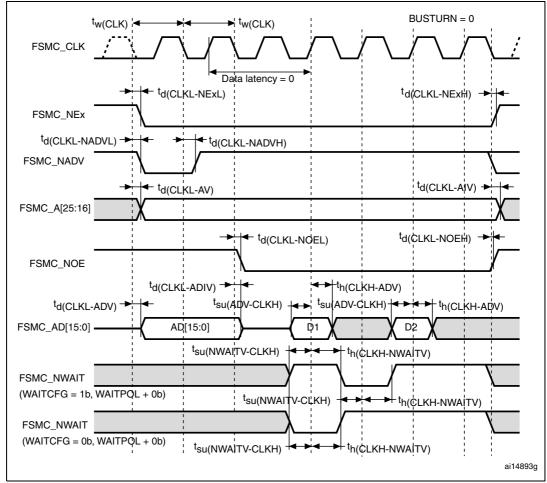

Figure 56. Asynchronous multiplexed PSRAM/NOR read waveforms

## Table 77. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                                             | Min                     | Мах                     | Unit |

|---------------------------|-------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                      | 3T <sub>HCLK</sub> –1   | 3T <sub>HCLK</sub> +1   | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low                          | 2T <sub>HCLK</sub> -0.5 | 2T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                                     | T <sub>HCLK</sub> –1    | T <sub>HCLK</sub> +1    | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time               | 0                       | -                       | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                          | -                       | 3                       | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                         | 1                       | 2                       | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                                    | T <sub>HCLK</sub> – 2   | T <sub>HCLK</sub> +1    | ns   |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD(adress) valid hold time after FSMC_NADV high) | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high                 | T <sub>HCLK</sub> –1    | -                       | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL time after FSMC_NOE high                      | 0                       | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                         | -                       | 2                       | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time                      | T <sub>HCLK</sub> +4    | -                       | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOE high setup time                      | T <sub>HCLK</sub> +4    | -                       | ns   |

| t <sub>h(Data_NE)</sub>   | Data hold time after FSMC_NEx high                    | 0                       | -                       | ns   |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FSMC_NOE high                    | 0                       | -                       | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

2. Guaranteed by characterization.

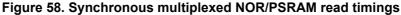

#### Synchronous waveforms and timings

*Figure 58* through *Figure 61* represent synchronous waveforms and *Table 80* through *Table 82* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- BurstAccessMode = FSMC\_BurstAccessMode\_Enable;

- MemoryType = FSMC\_MemoryType\_CRAM;

- WriteBurst = FSMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F40xxx/41xxx reference manual)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period (with maximum FSMC\_CLK = 60 MHz).

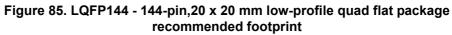

## 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

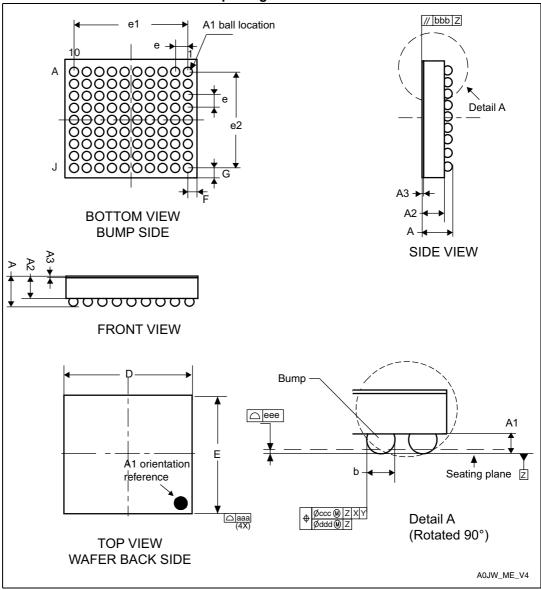

## 6.1 WLCSP90 package information

Figure 75. WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

DocID022063 Rev 8

| Cumhal |        | millimeters |        | inches |        |        |  |  |  |  |  |

|--------|--------|-------------|--------|--------|--------|--------|--|--|--|--|--|

| Symbol | Min    | Тур         | Max    | Min    | Тур    | Max    |  |  |  |  |  |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512 | 0.5591 |  |  |  |  |  |

| E3     | -      | 12.000      | -      | -      | 0.4724 | -      |  |  |  |  |  |

| е      | -      | 0.500       | -      | -      | 0.0197 | -      |  |  |  |  |  |

| L      | 0.450  | 0.600       | 0.750  | 0.0177 | 0.0236 | 0.0295 |  |  |  |  |  |

| L1     | -      | 1.000       | -      | -      | 0.0394 | -      |  |  |  |  |  |

| k      | 0°     | 3.5°        | 7°     | 0°     | 3.5°   | 7°     |  |  |  |  |  |

| CCC    | -      | -           | 0.080  | -      | -      | 0.0031 |  |  |  |  |  |

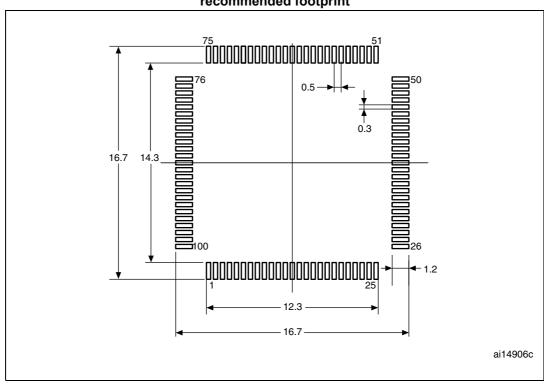

## Table 93. LQPF100 – 100-pin, 14 x 14 mm low-profile quad flat package mechanical data<sup>(1)</sup> (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

1. Dimensions are in millimeters.

| Table 95. UFBGA176+25 ball, 10 × 10 × 0.65 mm pitch, ultra thin fine pitch |  |

|----------------------------------------------------------------------------|--|

| ball grid array mechanical data (continued)                                |  |

| Symbol |     | millimeters |       |     | inches <sup>(1)</sup> |        |  |

|--------|-----|-------------|-------|-----|-----------------------|--------|--|

| Symbol | Min | Тур         | Max   | Min | Тур                   | Max    |  |

| eee    | -   | -           | 0.150 | -   | -                     | 0.0059 |  |

| fff    | -   | -           | 0.050 | -   | -                     | 0.0020 |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

## Figure 88. UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array recommended footprint

| 00000000000000000000000000000000000000  |           |

|-----------------------------------------|-----------|

|                                         |           |

|                                         |           |

| 0000 00000 0000                         |           |

| 0000 00000 0000                         |           |

| 0000 00000 0000                         |           |

| 0000 00000 0000                         |           |

| 0000 0000                               |           |

| 000000000000000000000000000000000000000 |           |

| 000000000000000000000000000000000000000 |           |

| 000000000000000000000000000000000000000 |           |

| 000000000000000                         | 0E7_FP_V1 |

|                                         |           |

#### Table 96. UFBGA176+2 recommended PCB design rules (0.65 mm pitch BGA)

| Dimension | Recommended values                                               |

|-----------|------------------------------------------------------------------|

| Pitch     | 0.65                                                             |

| Dpad      | 0.300 mm                                                         |

| Dsm       | 0.400 mm typ. (depends on the soldermask registration tolerance) |

Note:

Non solder mask defined (NSMD) pads are recommended.

4 to 6 mils solder paste screen printing process.

Stencil opening is 0.300 mm.

Stencil thickness is between 0.100 mm and 0.125 mm.

Pad trace width is 0.100 mm.

| mechanical data (continued) |        |             |        |                       |        |        |

|-----------------------------|--------|-------------|--------|-----------------------|--------|--------|

| Cumhal                      |        | millimeters |        | inches <sup>(1)</sup> |        |        |

| Symbol                      | Min    | Тур         | Мах    | Min                   | Тур    | Max    |

| ZD                          | -      | 1.250       | -      | -                     | 0.0492 | -      |

| Е                           | 23.900 | -           | 24.100 | 0.9409                | -      | 0.9488 |

| HE                          | 25.900 | -           | 26.100 | 1.0197                | -      | 1.0276 |

| ZE                          | -      | 1.250       | -      | -                     | 0.0492 | -      |

| е                           | -      | 0.500       | -      | -                     | 0.0197 | -      |

| L <sup>(2)</sup>            | 0.450  | -           | 0.750  | 0.0177                | -      | 0.0295 |

| L1                          | -      | 1.000       | -      | -                     | 0.0394 | -      |

| k                           | 0°     | -           | 7°     | 0°                    | -      | 7°     |

| CCC                         | -      | -           | 0.080  | -                     | -      | 0.0031 |

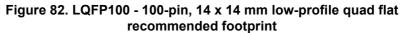

## Table 97. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat packagemechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. L dimension is measured at gauge plane at 0.25 mm above the seating plane.

## 8 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-Sep-2011 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 24-Jan-2012 | 2        | Added WLCSP90 package on cover page.<br>Renamed USART4 and USART5 into UART4 and UART5,<br>respectively.<br>Updated number of USB OTG HS and FS in Table 2: STM32F415xx<br>and STM32F417xx: features and peripheral counts.<br>Updated Figure 3: Compatible board design between<br>STM32F10xx/STM32F2/STM32F41xxx for LQFP144 package and<br>Figure 4: Compatible board design between<br>STM32F10xx/STM32F2/STM32F41xxx for LQFP144 package and<br>Figure 4: Compatible board design between STM32F2 and<br>STM32F41xxx for LQFP176 and BGA176 packages, and removed<br>note 1 and 2.<br>Updated Section 2.2.9: Flexible static memory controller (FSMC).<br>Modified I/Os used to reprogram the Flash memory for CAN2 and<br>USB OTG FS in Section 2.2.13: Boot modes.<br>Updated note in Section 2.2.14: Power supply schemes.<br>PDR_ON no more available on LQFP100 package. Updated<br>Section 2.2.16: Voltage regulator. Updated condition to obtain a<br>minimum supply voltage of 1.7 V in the whole document.<br>Renamed USART4/5 to UART4/5 and added LIN and IrDA feature for<br>UART4 and UART5 in Table 5: USART feature comparison.<br>Removed support of I2C for OTG PHY in Section 2.2.30: Universal<br>serial bus on-the-go full-speed (OTG_FS).<br>Added Table 6: Legend/abbreviations used in the pinout table.<br>Table 7: STM32F41xxx pin and ball definitions: replaced V <sub>SS</sub> _3,<br>V <sub>SS</sub> _4, and V <sub>SS</sub> _8 by V <sub>SS</sub> ; reformatted Table 7: STM32F41xxx pin and<br>ball definitions to better highlight I/O structure, and alternate functions<br>versus additional functions; signal corresponding to LQFP100 pin 99<br>changed from PDR_ON to V <sub>SS</sub> ; EVENTOUT added in the list of<br>alternate functions for all I/OS; ADC3_IN8 added as alternate functions<br>for PD11 and PD12, respectively; PH10 alternate function<br>TIM15_CH1_ETR renamed TIM5_CH1; updated PA4 and PA5 I/O<br>structure to TTa.<br>Removed OTG_HS_SCL, OTG_HS_SDA, OTG_FS_INTN in Table 7:<br>STM32F41xxx pin and ball definitions and Table 9: Alternate function<br>mapping.<br>Changed TCM data RAM to CCM data RAM in Figure 18:<br>STM32F41xxx memory map.<br>Added I <sub>VDD</sub> and I <sub>VSS</sub> maximum values |

### Table 100. Document revision history

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24-Jan-2012 | 2<br>(continued) | Updated Table 61: USB HS clock timing parameters<br>Updated Table 67: ADC characteristics.<br>Updated Table 68: ADC accuracy at fADC = 30 MHz.<br>Updated Note 1 in Table 74: DAC characteristics.<br>Section 5.3.26: FSMC characteristics: updated Table 75 to Table 86,<br>changed C <sub>L</sub> value to 30 pF, and modified FSMC configuration for<br>asynchronous timings and waveforms. Updated Figure 59:<br>Synchronous multiplexed PSRAM write timings.<br>Updated Table 98: Package thermal characteristics.<br>Appendix A.1: USB OTG full speed (FS) interface solutions: modified<br>Figure 93: USB controller configured as peripheral-only and used in<br>Full speed mode added Note 2, updated Figure 94: USB controller<br>configured as host-only and used in full speed mode and added<br>Note 2, changed Figure 95: USB controller configured in dual mode<br>and used in full speed mode and added Note 3.<br>Appendix A.2: USB OTG high speed (HS) interface solutions: removed<br>figures USB OTG HS device-only connection in FS mode and USB<br>OTG HS host-only connection in FS mode, and updated Figure 96:<br>USB controller configured as peripheral, host, or dual-mode and used<br>in high speed mode and added Note 2.<br>Added Appendix A.3: Ethernet interface solutions. |

| Table 100. | Document revision | history | (continued) |

|------------|-------------------|---------|-------------|

|            | Boounion          | motory  | (continuou) |

Table 100. Document revision history (continued)

|             | Table 100. Document revision history (continued)   |                                                                                                           |  |  |  |

|-------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|

| Date        | Revision                                           | Changes                                                                                                   |  |  |  |

|             |                                                    | Updated Figure 6: Multi-AHB matrix.                                                                       |  |  |  |

|             |                                                    | Updated Figure 7: Power supply supervisor interconnection with internal reset OFF                         |  |  |  |

|             |                                                    | Changed 1.2 V to V <sub>12</sub> in <i>Section : Regulator OFF</i>                                        |  |  |  |

|             |                                                    | Updated LQFP176 pin 48.                                                                                   |  |  |  |

|             |                                                    | Updated Section 1: Introduction.                                                                          |  |  |  |

|             |                                                    | Updated Section 2: Description.                                                                           |  |  |  |

|             |                                                    | Updated operating voltage in <i>Table 2:</i> STM32F415xx and STM32F417xx: features and peripheral counts. |  |  |  |

|             |                                                    | Updated Note 1.                                                                                           |  |  |  |

|             |                                                    | Updated Section 2.2.15: Power supply supervisor.                                                          |  |  |  |

|             |                                                    | Updated Section 2.2.16: Voltage regulator.                                                                |  |  |  |

|             |                                                    | Updated Figure 9: Regulator OFF.                                                                          |  |  |  |

|             |                                                    | Updated Table 3: Regulator ON/OFF and internal reset ON/OFF availability.                                 |  |  |  |

|             |                                                    | Updated Section 2.2.19: Low-power modes.                                                                  |  |  |  |

|             |                                                    | Updated Section 2.2.20: VBAT operation.                                                                   |  |  |  |

|             |                                                    | Updated Section 2.2.22: Inter-integrated circuit interface (I <sup>2</sup> C)                             |  |  |  |

|             |                                                    | Updated pin 48 in Figure 15: STM32F41xxx LQFP176 pinout.                                                  |  |  |  |

|             |                                                    | Updated Table 6: Legend/abbreviations used in the pinout table.                                           |  |  |  |

|             |                                                    | Updated Table 7: STM32F41xxx pin and ball definitions.                                                    |  |  |  |

|             |                                                    | Updated Table 14: General operating conditions.                                                           |  |  |  |

| 04 Jun 2012 | 4                                                  | Updated Table 15: Limitations depending on the operating power                                            |  |  |  |

| 04-Jun-2013 | (continued)                                        | supply range                                                                                              |  |  |  |

|             |                                                    | Updated Section 5.3.7: Wakeup time from low-power mode.                                                   |  |  |  |

|             |                                                    | Updated Table 34: HSI oscillator characteristics.                                                         |  |  |  |

|             |                                                    | Updated Section 5.3.15: I/O current injection characteristics.                                            |  |  |  |

|             |                                                    | Updated Table 48: I/O static characteristics.                                                             |  |  |  |

|             |                                                    | Updated Table 51: NRST pin characteristics.                                                               |  |  |  |

|             |                                                    | Updated Table 56: I <sup>2</sup> C characteristics.                                                       |  |  |  |

|             |                                                    | Updated Figure 39: I <sup>2</sup> C bus AC waveforms and measurement circuit.                             |  |  |  |

|             | Updated Section 5.3.19: Communications interfaces. |                                                                                                           |  |  |  |

|             |                                                    | Updated Table 67: ADC characteristics.                                                                    |  |  |  |

|             |                                                    | Added Table 70: Temperature sensor calibration values.                                                    |  |  |  |

|             |                                                    | Added Table 73: Internal reference voltage calibration values.                                            |  |  |  |

|             |                                                    | Updated Section 5.3.26: FSMC characteristics.                                                             |  |  |  |

|             |                                                    | Updated Section 5.3.28: SD/SDIO MMC card host interface (SDIO) characteristics.                           |  |  |  |

|             |                                                    | Updated Table 23: Typical and maximum current consumptions in Stop mode.                                  |  |  |  |

|             |                                                    | Updated Section : SPI interface characteristics included Table 55.                                        |  |  |  |

|             |                                                    | Updated Section : I2S interface characteristics included Table 56.                                        |  |  |  |

|             |                                                    | Updated Table 64: Dynamic characteristics: Eternity MAC signals for SMI.                                  |  |  |  |

|             |                                                    | Updated Table 66: Dynamic characteristics: Ethernet MAC signals for MII.                                  |  |  |  |

| Table 100. Document revision history (continued) |

|--------------------------------------------------|

|--------------------------------------------------|

| Date        | Revision                                                                                                                                                                                                                                                                                                                                                                                                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-Oct-2015 | 6                                                                                                                                                                                                                                                                                                                                                                                                               | In the whole document, updated notes related to values guaranteed by design or by characterization.<br>Updated <i>Table 34: HSI oscillator characteristics</i> .<br>Changed f <sub>VCO_OUT</sub> minimum value and VCO freq to 100 MHz in <i>Table 36: Main PLL characteristics</i> and <i>Table 37: PLLI2S (audio PLL) characteristics</i> .<br>Updated <i>Figure 39: SPI timing diagram - slave mode and CPHA = 0</i> .<br>Updated <i>Figure 53: 12-bit buffered /non-buffered DAC</i> .<br>Removed note 1 related to better performance using a restricted V <sub>DD</sub> range in <i>Table 68: ADC accuracy at fADC = 30 MHz</i> .<br>Updated <i>Figure 84: LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline</i> .<br>Updated <i>Figure 87: UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package outline</i> and <i>Table 95: UFBGA176+25 ball, 10 x 10 x 0.65 mm pitch, ultra thin fine pitch ball grid array mechanical data</i> . |

| 16-Mar-2016 | <ul> <li>7</li> <li><sup>7</sup> Updated Figure 2: Compatible board design<br/>STM32F10xx/STM32F2/STM32F41xxx for LQFP100 package.<br/>Updated  Vssx-Vss  in Table 11: Voltage characteristics to add V<sub>R</sub><br/>Added V<sub>REF-</sub>in Table 67: ADC characteristics.<br/>Updated Table 90: WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch<br/>wafer level chip scale package mechanical data.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 09-Sep-2016 | 8                                                                                                                                                                                                                                                                                                                                                                                                               | Removed note 1 below <i>Figure 5: STM32F41xxx block diagram</i> .<br>Updated definition of stresses above maximum ratings in Section 5.2:<br><i>Absolute maximum ratings</i> .<br>Updated $t_{h(NSS)}$ in <i>Figure 39: SPI timing diagram - slave mode and</i><br><i>CPHA = 0Figure</i> and <i>Figure 40: SPI timing diagram - slave mode and</i><br><i>CPHA = 1.</i><br>Added note related to optional marking and inset/upset marks in all<br>package marking sections.<br>Updated <i>Figure 87: UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch,</i><br><i>ultra fine pitch ball grid array package outline</i> and <i>Table 95:</i><br><i>UFBGA176+25 ball, 10 x 10 x 0.65 mm pitch, ultra thin fine pitch ball</i><br><i>grid array mechanical data.</i>                                                                                                                                                                                                                                    |

Table 100. Document revision history (continued)