# E. Analog Devices Inc./Maxim Integrated - 73S1210F-68M/F/PH Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 80515                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SmartCard, UART/USART                               |

| Peripherals                | LED, POR, WDT                                                         |

| Number of I/O              | 8                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6.5V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 68-VFQFN Exposed Pad                                                  |

| Supplier Device Package    | 68-QFN (8x8)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/73s1210f-68m-f-ph |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Figures

| Figure 1: IC Functional Block Diagram                                           | 7   |

|---------------------------------------------------------------------------------|-----|

| Figure 2: Memory Map                                                            | 15  |

| Figure 3: Clock Generation and Control Circuits                                 |     |

| Figure 4: Oscillator Circuit                                                    |     |

| Figure 5: Detailed Power Management Logic Block Diagram                         |     |

| Figure 6: Power Down Control                                                    |     |

| Figure 7: Detail of Power Down Interrupt Logic                                  | 28  |

| Figure 8: Power Down Sequencing                                                 | 29  |

| Figure 9: External Interrupt Configuration                                      |     |

| Figure 10: I <sup>2</sup> C Write Mode Operation                                |     |

| Figure 11: I <sup>2</sup> C Read Operation                                      |     |

| Figure 12: Simplified Keypad Block Diagram                                      |     |

| Figure 13: Keypad Interface Flow Chart                                          |     |

| Figure 14: Smart Card Interface Block Diagram                                   |     |

| Figure 15: External Smart Card Interface Block Diagram                          |     |

| Figure 16: Asynchronous Activation Sequence Timing                              |     |

| Figure 17: Deactivation Sequence                                                |     |

| Figure 18: Smart Card CLK and ETU Generation                                    | 74  |

| Figure 19: Guard, Block, Wait and ATR Time Definitions                          |     |

| Figure 20: Synchronous Activation                                               | 77  |

| Figure 21: Example of Sync Mode Operation: Generating/Reading ATR Signals       |     |

| Figure 22: Creation of Synchronous Clock Start/Stop Mode Start Bit in Sync Mode |     |

| Figure 23: Creation of Synchronous Clock Start/Stop Mode Stop Bit in Sync Mode  |     |

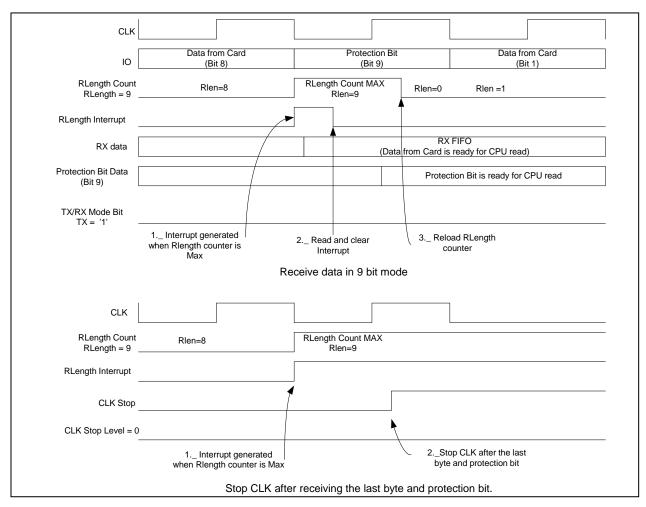

| Figure 24: Operation of 9-bit Mode in Sync Mode                                 |     |

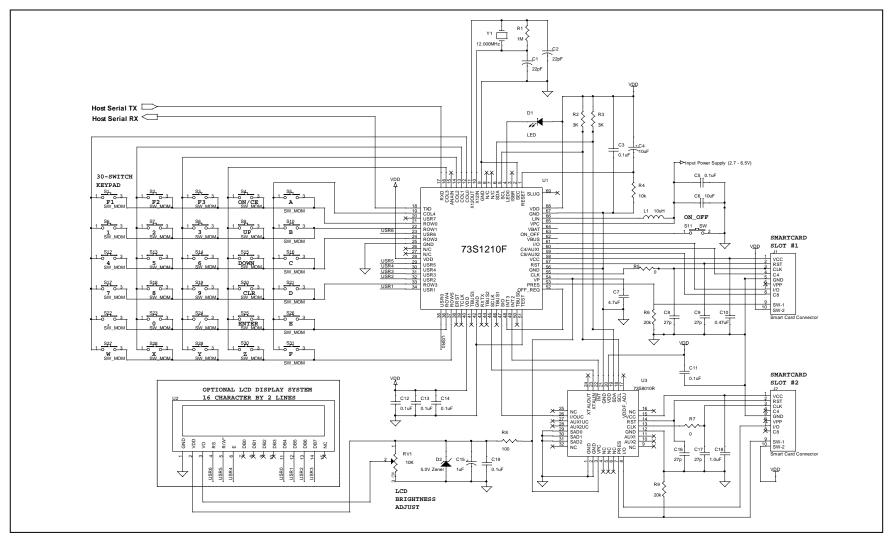

| Figure 25: 73S1210F Typical Application Schematic                               |     |

| Figure 26: 12 MHz Oscillator Circuit                                            |     |

| Figure 27: 32KHz Oscillator Circuit                                             |     |

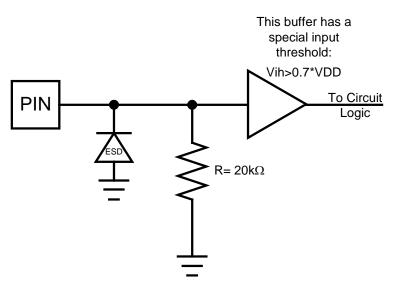

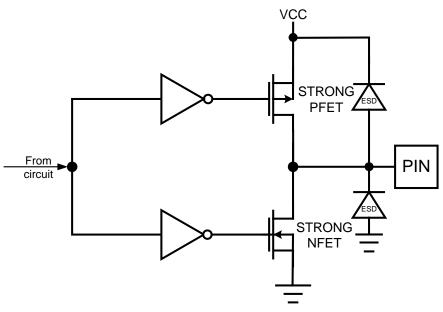

| Figure 28: Digital I/O Circuit                                                  | 113 |

| Figure 29: Digital Output Circuit                                               |     |

| Figure 30: Digital I/O with Pull Up Circuit                                     |     |

| Figure 31: Digital I/O with Pull Down Circuit                                   | 114 |

| Figure 32: Digital Input Circuit                                                |     |

| Figure 33: OFF_REQ Interface Circuit                                            | 115 |

| Figure 34: Keypad Row Circuit                                                   |     |

| Figure 35: Keypad Column Circuit                                                |     |

| Figure 36: LED Circuit                                                          |     |

| Figure 37: Test and Security Pin Circuit                                        |     |

| Figure 38: Analog Input Circuit                                                 |     |

| Figure 39: Smart Card Output Circuit                                            |     |

| Figure 40: Smart Card I/O Circuit                                               |     |

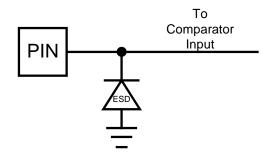

| Figure 41: PRES Input Circuit                                                   |     |

| Figure 42: PRESB Input Circuit                                                  |     |

| Figure 43: ON_OFF Input Circuit                                                 |     |

| Figure 44: 73S1210F 68 QFN Pinout                                               |     |

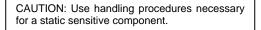

| Figure 45: 73S1210F 44 QFN Pinout                                               |     |

| Figure 46: 73S1210F 68 QFN Mechanical Drawing                                   |     |

| Figure 47: 73S1210F 44 QFN Package Drawing                                      | 123 |

## 1.2 Hardware Overview

The 73S1210F single smart card controller integrates all primary functional blocks required to implement a smart card reader. Included on chip are an 8051-compatible microprocessor (MPU) which executes up to one instruction per clock cycle (80515), a fully integrated ISO 7816 compliant smart card interface, expansion smart card interface, serial interface, I2C interface, 6 x 5 keypad interface, RAM, FLASH memory, and a variety of I/O pins.

The power management circuitry provides a 3.3V voltage output (VDD, pin #68) that must be connected to the power supply inputs of the digital core of the circuit, pins # 28 and 40 (these are not internally connected). Should external circuitry require a 3.3V digital power supply, the VDD output is capable of supplying additional current.

Figure 1 shows a functional block diagram of the 73S1210F.

## 1.3 80515 MPU Core

## 1.3.1 80515 Overview

The 73S1210F includes an 80515 MPU (8-bit, 8051-compatible) that performs most instructions in one clock cycle. The 80515 architecture eliminates redundant bus states and implements parallel execution of fetch and execution phases. Normally a machine cycle is aligned with a memory fetch, therefore, most of the 1-byte instructions are performed in a single cycle. This leads to an 8x performance (average) improvement (in terms of MIPS) over the Intel 8051 device running at the same clock frequency.

Actual processor clocking speed can be adjusted to the total processing demand of the application (cryptographic calculations, key management, memory management, and I/O management) using the XRAM special function register MPUCKCtl.

Typical smart card, serial, keyboard and I2C management functions are available for the MPU as part of the Teridian standard library. A standard ANSI "C" 80515-application programming interface library is available to help reduce design cycle. Refer to the *73S12xxF Software User's Guide*.

## 1.3.2 Memory Organization

The 80515 MPU core incorporates the Harvard architecture with separate code and data spaces. Memory organization in the 80515 is similar to that of the industry standard 8051. There are three memory areas: Program memory (Flash), external data memory (XRAM), and internal data memory (IRAM). Data bus address space is allocated to on-chip memory as shown Table 2

| Address<br>(hex) | Memory<br>Technology | Memory Type  | Typical Usage                 | Memory Size<br>(bytes) |

|------------------|----------------------|--------------|-------------------------------|------------------------|

| 0000-7FFF        | Flash Memory         | Non-volatile | Program and non-volatile data | 32KB                   |

| 0000-07FF        | Static RAM           | Volatile     | MPU data XRAM                 | 2KB                    |

| FC00-FFFF        | External SFR         | Volatile     | Peripheral control            | 1KB                    |

Table 2: MPU Data Memory Map

Note: The IRAM is part of the core and is addressed differently.

**Program Memory:** The 80515 can address up to 32KB of program memory space from 0x0000 to 0xFFFF. Program memory is read when the MPU fetches instructions or performs a MOVC operation. After reset, the MPU starts program execution from location 0x0000. The lower part of the program memory includes reset and interrupt vectors. The interrupt vectors are spaced at 8-byte intervals, starting from 0x0003. Reset is located at 0x0000.

**Flash Memory:** The program memory consists of flash memory. The flash memory is intended to primarily contain MPU program code. Flash erasure is initiated by writing a specific data pattern to

| Name    | Location | Reset Value | Description                                        |

|---------|----------|-------------|----------------------------------------------------|

| KROW    | 0XD2     | 0x3F        | Keypad Row                                         |

| KSCAN   | 0XD3     | 0x00        | Keypad Scan Time                                   |

| KSTAT   | 0XD4     | 0x00        | Keypad Control/Status                              |

| KSIZE   | 0XD5     | 0x00        | Keypad Size                                        |

| KORDERL | 0XD6     | 0x00        | Keypad Column LS Scan Order                        |

| KORDERH | 0XD7     | 0x00        | Keypad Column MS Scan Order                        |

| BRCON   | 0xD8     | 0x00        | Baud Rate Control Register (only BRCON.7 bit used) |

| А       | 0xE0     | 0x00        | Accumulator                                        |

| В       | 0xF0     | 0x00        | B Register                                         |

## 1.5.3 External Data Special Function Registers (SFRs)

A map of the XRAM Special Function Registers is shown in Table 8. The smart card registers are listed separately in Table 107.

| Name       | Location | Reset Value | Description                                      |

|------------|----------|-------------|--------------------------------------------------|

| DAR        | 0x FF80  | 0x00        | Device Address Register (I <sup>2</sup> C)       |

| WDR        | 0x FF81  | 0x00        | Write Data Register (I <sup>2</sup> C)           |

| SWDR       | 0x FF82  | 0x00        | Secondary Write Data Register (I <sup>2</sup> C) |

| RDR        | 0x FF83  | 0x00        | Read Data Register (I <sup>2</sup> C)            |

| SRDR       | 0x FF84  | 0x00        | Secondary Read Data Register (I <sup>2</sup> C)  |

| CSR        | 0x FF85  | 0x00        | Control and Status Register (I <sup>2</sup> C)   |

| USRIntCtl1 | 0x FF90  | 0x00        | External Interrupt Control 1                     |

| USRIntCtl2 | 0x FF91  | 0x00        | External Interrupt Control 2                     |

| USRIntCtl3 | 0x FF92  | 0x00        | External Interrupt Control 3                     |

| USRIntCtl4 | 0x FF93  | 0x00        | External Interrupt Control 4                     |

| INT5Ctl    | 0x FF94  | 0x00        | External Interrupt Control 5                     |

| INT6Ctl    | 0x FF95  | 0x00        | External Interrupt Control 6                     |

| MPUCKCtl   | 0x FFA1  | 0x0C        | MPU Clock Control                                |

| ACOMP      | 0x FFD0  | 0x00        | Analog Compare Register                          |

| TRIMPCtl   | 0x FFD1  | 0x00        | TRIM Pulse Control                               |

| FUSECtl    | 0x FFD2  | 0x00        | FUSE Control                                     |

| VDDFCtl    | 0x FFD4  | 0x00        | VDDFault Control                                 |

| SECReg     | 0x FFD7  | 0x00        | Security Register                                |

| MISCtI0    | 0x FFF1  | 0x00        | Miscellaneous Control Register 0                 |

| MISCtl1    | 0x FFF2  | 0x10        | Miscellaneous Control Register 1                 |

| LEDCtl     | 0x FFF3  | 0xFF        | LED Control Register                             |

**Table 8: XRAM Special Function Registers Reset Values**

Accumulator (ACC, A): ACC is the accumulator register. Most instructions use the accumulator to hold the operand. The mnemonics for accumulator-specific instructions refer to accumulator as "A", not ACC.

**B Register:** The B register is used during multiply and divide instructions. It can also be used as a scratch-pad register to hold temporary data.

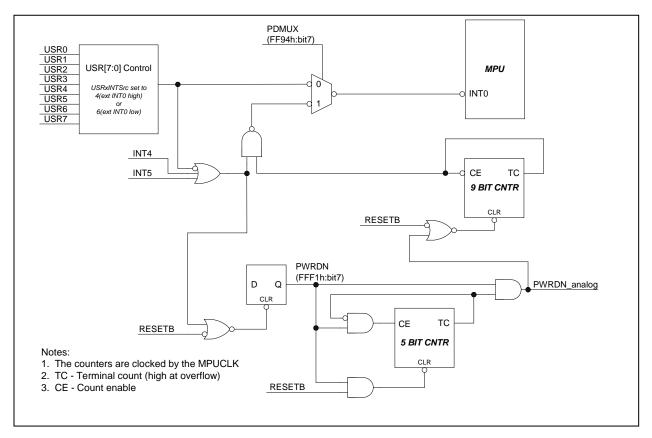

When the PWRDN bit is set, the clock subsystem will provide a delay of 32 MPUCLK cycles to allow the program to set the STOP bit in the PCON register. This delay will enable the program to properly halt the core before the analog circuits shut down (high speed oscillator, VCO/PLL, voltage reference and bias circuitry, etc.). The PDMUX bit in SFR INT5Ctl should be set prior to setting the PWRDN bit in order to configure the wake up interrupt logic. The power down mode is de-asserted by any of the interrupts connected to external interrupts 0, 4 and 5 (external USR[0:7], smart card and Keypad). These interrupt sources are OR'ed together and routed through some delay logic into INT0 to provide this functionality. The interrupt will turn on the power to all sections that were shut off and start the clock subsystem. After the clock subsystem clocks start running, the MPUCLK begins to clock a 512 count delay counter. When the counter times out, the interrupt will then be active on INT0 and the program can resume. Figure 7 shows the detailed logic for waking up the 73S1210F from a power down mode.

Figure 7: Detail of Power Down Interrupt Logic

## External Interrupt Control Register (INT5CtI): 0xFF94 ← 0x00

## Table 14: The INT5Ctl Register

| MSB   |   |   |   |   |   |       | LSB   |  |

|-------|---|---|---|---|---|-------|-------|--|

| PDMUX | - | - | - | - | - | KPIEN | KPINT |  |

| Bit       | Symbol | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT5Ctl.7 | PDMUX  | When set = 1, enables interrupts from Keypad (normally going to int5),<br>Smart Card interrupts (normally going to int4), or USR(7:0) pins (int0) to<br>cause interrupt on int0. The assertion of the interrupt to int0 is delayed by<br>512 MPU clocks to allow the analog circuits, including the clock system, to<br>stabilize. This bit must be set prior to asserting the PWRDN bit in order to<br>properly configure the interrupts that will wake up the circuit. This bit is<br>reset = 0 when this register is read. |

| INT5Ctl.6 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INT5Ctl.5 | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INT5Ctl.4 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INT5Ctl.3 | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INT5Ctl.2 | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INT5Ctl.1 | KPIEN  | Keypad interrupt enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| INT5Ctl.0 | KPINT  | Keypad interrupt flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

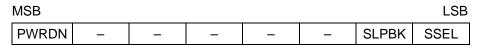

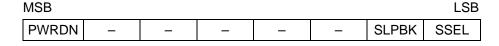

## Miscellaneous Control Register 0 (MISCtI0): 0xFFF1 ← 0x00

#### Table 15: The MISCtI0 Register

| Bit       | Symbol | Function                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MISCtI0.7 | PWRDN  | This bit sets the circuit into a low-power condition. All analog (high-speed oscillator and VCO/PLL) functions are disabled 32 MPU clock cycles after this bit is set = 1. This allows time for the next instruction to set the STOP bit in the PCON register to stop the CPU core. The MPU is not operative in this mode. When set, this bit overrides the individual control bits that otherwise control power consumption. |

| MISCtI0.6 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MISCtI0.5 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MISCtI0.4 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MISCtI0.3 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MISCtI0.2 | _      |                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MISCtI0.1 | SLPBK  | UART loop back testing mode.                                                                                                                                                                                                                                                                                                                                                                                                  |

| MISCtI0.0 | SSEL   | Serial port pins select.                                                                                                                                                                                                                                                                                                                                                                                                      |

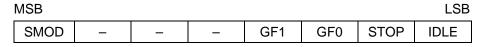

## Power Control Register 0 (PCON): 0x87 ← 0x00

The SMOD bit used for the baud rate generator is set up via this register.

## Table 18: The PCON Register

| Bit    | Symbol | Function                               |

|--------|--------|----------------------------------------|

| PCON.7 | SMOD   | If SM0D = 1, the baud rate is doubled. |

| PCON.6 | -      |                                        |

| PCON.5 | -      |                                        |

| PCON.4 | -      |                                        |

| PCON.3 | GF1    | General purpose flag 1.                |

| PCON.2 | GF0    | General purpose flag 1.                |

| PCON.1 | STOP   | Sets CPU to Stop mode.                 |

| PCON.0 | IDLE   | Sets CPU to Idle mode.                 |

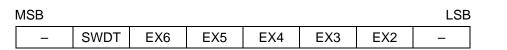

#### Interrupt Enable 1 Register (IEN1): 0xB8 ← 0x00

Table 20: The IEN1 Register

| Bit    | Symbol | Function                                |

|--------|--------|-----------------------------------------|

| IEN1.7 | _      |                                         |

| IEN1.6 | SWDT   | Not used for interrupt control.         |

| IEN1.5 | EX6    | EX6 = 0 - disable external interrupt 6. |

| IEN1.4 | EX5    | EX5 = 0 - disable external interrupt 5. |

| IEN1.3 | EX4    | EX4 = 0 - disable external interrupt 4. |

| IEN1.2 | EX3    | EX3 = 0 – disable external interrupt 3. |

| IEN1.1 | EX2    | EX2 = 0 – disable external interrupt 2. |

| IEN1.0 | -      |                                         |

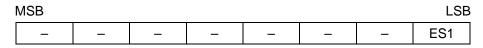

#### Interrupt Enable 2 Register (IEN2): 0x9A ← 0x00

## Table 21: The IEN2 Register

| Bit    | Symbol | Function                                    |  |

|--------|--------|---------------------------------------------|--|

| IEN2.0 | ES1    | ES1 = 0 – disable serial channel interrupt. |  |

#### Miscellaneous Control Register 0 (MISCtI0): 0xFFF1 ← 0x00

Transmit and receive (TX and RX) pin selection and loop back test configuration are setup via this register.

#### Table 37: The MISCtI0 Register

| Bit       | Symbol | Function                                                                                                                                                                                                                                                                       |  |  |

|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MISCtI0.7 | PWRDN  | This bit places the 73S1210F into a power down state.                                                                                                                                                                                                                          |  |  |

| MISCtI0.6 | -      |                                                                                                                                                                                                                                                                                |  |  |

| MISCtI0.5 | -      |                                                                                                                                                                                                                                                                                |  |  |

| MISCtI0.4 | -      |                                                                                                                                                                                                                                                                                |  |  |

| MISCtI0.3 | _      |                                                                                                                                                                                                                                                                                |  |  |

| MISCtI0.2 | -      |                                                                                                                                                                                                                                                                                |  |  |

| MISCtI0.1 | SLPBK  | 1 = UART loop back testing mode. The pins TXD and RXD are to be connected together externally (with SLPBK =1) and therefore:   SLPBK SSEL Mode   0 0 normal using Serial_0   0 1 normal using Serial_1   1 0 Serial_0 TX feeds Serial_1 RX   1 1 Serial 1 TX feeds Serial 0 RX |  |  |

| MISCtI0.0 | SSEL   | Selects either Serial_1 if set =1 or Serial_0 if set = 0 to be connected to RXD and TXD pins.                                                                                                                                                                                  |  |  |

#### 1.7.6.1 Serial Interface 0

The Serial Interface 0 can operate in 4 modes:

#### • Mode 0

Pin RX serves as input and output. TX outputs the shift clock. 8 bits are transmitted with LSB first. The baud rate is fixed at 1/12 of the crystal frequency. Reception is initialized in Mode 0 by setting the flags in SOCON as follows: RI0 = 0 and REN0 = 1. In other modes, a start bit when REN0 = 1 starts receiving serial data.

#### • Mode 1

Pin RX serves as input, and TX serves as serial output. No external shift clock is used, 10 bits are transmitted: a start bit (always 0), 8 data bits (LSB first), and a stop bit (always 1). On receive, a start bit synchronizes the transmission, 8 data bits are available by reading S0BUF, and stop bit sets the flag RB80 in the Special Function Register S0CON. In mode 1 either internal baud rate generator or timer 1 can be use to specify baud rate.

#### • Mode 2

This mode is similar to Mode 1, with two differences. The baud rate is fixed at 1/32 or 1/64 of oscillator frequency and 11 bits are transmitted or received: a start bit (0), 8 data bits (LSB first), a programmable 9th bit, and a stop bit (1). The 9th bit can be used to control the parity of the serial interface: at transmission, bit TB80 in SOCON is output as the 9th bit, and at receive, the 9th bit affects RB80 in Special Function Register SOCON.

#### 1.7.6.2 Serial Interface 1

The Serial Interface 1 can operate in 2 modes:

#### • Mode A

This mode is similar to Mode 2 and 3 of Serial interface 0, 11 bits are transmitted or received: a start bit (0), 8 data bits (LSB first), a programmable 9th bit, and a stop bit (1). The 9th bit can be used to control the parity of the serial interface: at transmission, bit TB81 in S1CON is outputted as the 9th bit, and at receive, the 9th bit affects RB81 in Special Function Register S1CON. The only difference between Mode 3 and A is that in Mode A only the internal baud rate generator can be use to specify baud rate.

• Mode B

This mode is similar to Mode 1 of Serial interface 0. Pin RX serves as input, and TX serves as serial output. No external shift clock is used, 10 bits are transmitted: a start bit (always 0), 8 data bits (LSB first), and a stop bit (always 1). On receive, a start bit synchronizes the transmission, 8 data bits are available by reading S1BUF, and stop bit sets the flag RB81 in the Special Function Register S1CON. In mode 1, the internal baud rate generator is use to specify the baud rate.

The S1BUF register is used to read/write data to/from the serial 1 interface.

#### Serial Interface Control Register (S1CON): 0x9B ← 0x00

The function of the serial port depends on the setting of the Serial Port Control Register S1CON.

| MSB |   |      |      |      |      |     | LSB |  |

|-----|---|------|------|------|------|-----|-----|--|

| SM  | - | SM21 | REN1 | TB81 | RB81 | TI1 | RI1 |  |

Table 39: The S1CON Register

| Bit     | Symbol |             | Function                                                                                                        |                    |                    |                                             |  |  |  |  |  |

|---------|--------|-------------|-----------------------------------------------------------------------------------------------------------------|--------------------|--------------------|---------------------------------------------|--|--|--|--|--|

| S1CON.7 | SM     | Sets the l  | JART opera                                                                                                      | ation mode.        |                    |                                             |  |  |  |  |  |

|         |        | SM          | Mode                                                                                                            | Description        | Baud Rate          |                                             |  |  |  |  |  |

|         |        | 0           | А                                                                                                               | 9-bit UART         | variable           |                                             |  |  |  |  |  |

|         |        | 1           | 1 B 8-bit UART variable                                                                                         |                    |                    |                                             |  |  |  |  |  |

| S1CON.6 | _      |             |                                                                                                                 |                    |                    |                                             |  |  |  |  |  |

| S1CON.5 | SM21   | Enables t   | Enables the inter-processor communication feature.                                                              |                    |                    |                                             |  |  |  |  |  |

| S1CON.4 | REN1   | If set, ena | ables serial                                                                                                    | reception. Cleare  | d by software to d | disable reception.                          |  |  |  |  |  |

| S1CON.3 | TB81   |             |                                                                                                                 |                    |                    | by the MPU, depending communication, etc.). |  |  |  |  |  |

| S1CON.2 | RB81   | In Mode E   | 3, if sm21 is                                                                                                   | 0, rb81 is the sto | p bit. Must be cle | eared by software.                          |  |  |  |  |  |

| S1CON.1 | TI1    |             | Transmit interrupt flag, set by hardware after completion of a serial transfer.<br>Must be cleared by software. |                    |                    |                                             |  |  |  |  |  |

| S1CON.0 | RI1    |             | nterrupt flac<br>leared by s                                                                                    |                    | after completion   | of a serial reception.                      |  |  |  |  |  |

**Multiprocessor operation mode:** The feature of receiving 9 bits in Modes 2 and 3 of Serial Interface 0 or in Mode A of Serial Interface 1 can be used for multiprocessor communication. In this case, the slave processors have bit SM20 in S0CON or SM21 in S1CON set to 1. When the master processor outputs slave's address, it sets the 9th bit to 1, causing a serial port receive interrupt in all the slaves. The slave processors compare the received byte with their network address. If there is a match, the addressed slave will clear SM20 or SM21 and receive the rest of the message, while other slaves will leave the SM20 or SM21 bit unaffected and ignore this message. After addressing the slave, the host will output the rest of the message with the 9th bit set to 0, so no serial port receive interrupt will be generated in unselected slaves.

#### 1.7.15.2 Answer to Reset Processing

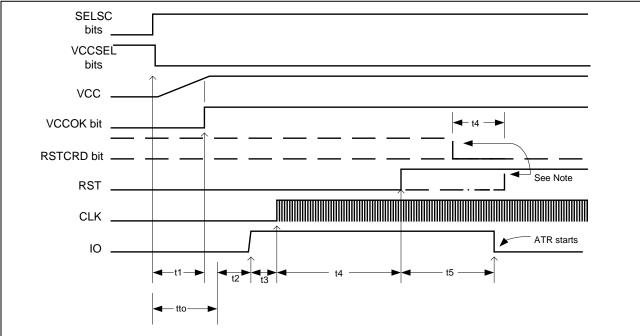

A card insertion event generates an interrupt to the firmware, which is then responsible for the configuration of the electrical interface, the UART and activation of the card. The activation sequencer goes through the power up sequence as defined in the ISO 7816-3 specification. An asynchronous activation timing diagram is shown in

Figure 16. After the card reset is de-asserted, the firmware instructs the hardware to look for a TS byte that begins the ATR response. If a response is not provided within the pre-programmed timeout period, an interrupt is generated and the firmware can then take appropriate action, including instructing the 73S1210F to begin a deactivation sequence. Once commanded, the deactivation sequencer goes through the power down sequence as defined in the ISO 7816-3 specification. If an ATR response is received, the hardware looks for a TS byte that determines direct/inverse convention. The hardware handles the indirect convention conversion such that the embedded firmware only receives direct convention. This feature can be disabled by firmware within SByteCtI register. Parity checking and break generation is performed on the TS byte unless disabled by firmware. If during the card session, a card removal, over-current or other error event is detected, the hardware will automatically perform the deactivation sequence and then generate an interrupt to the firmware. The firmware can then perform any other error handling required for proper system operation. Smart card RST, I/O and CLK, C4, C8 shall be low before the end of the deactivation sequence. Figure 17 shows the timing for a deactivation sequence.

t1: SELSC.1 bit set (selects internal ICC interface) and a non-zero value in VCCSEL bits (calling for a value of Vcc of 1.8, 3.0, or 5.0 volts) will begin the activation sequence. t1 is the time for Vcc to rise to acceptable level, declared as Vcc OK (bit VCCOK gets set). This time depends on filter capacitor value and card lcc load.

tto: The time allowed for Vcc to rise to Vcc OK status after setting of the VCCSEL bits. This time is generated by the VCCTMR counter. If Vcc OK is not set, (bit VCCOK) at this time, a deactivation will be initiated. VCCSEL bits are not automatically cleared. The firmware must clear the VCCSEL bits before starting a new activation.

t2: Time from VccTmr timeout and VCC OK to IO reception (high), typically 2-3 CLK cycles if RDYST = 0. If RDYST = 1, t2 starts when VCCOK = 1.

t3: Time from IO = high to CLK start, typically 2-3 CLK cycles.

t4: Time allowed for start of CLK to de-assertion of RST. Programmable by the RLength register. t5: Time allowed for ATR timeout, set by the STSTO register.

Note: If the RSTCRD bit is set, RST is asserted (low). Upon clearing RSTCRD bit, RST will be de-asserted after t4.

Figure 24: Operation of 9-bit Mode in Sync Mode

Synchronous card operation is broken down into three primary types. These are commonly referred to as 2-wire, 3-wire and I2C synchronous cards. Each card type requires different control and timing and therefore requires different algorithms to access. Teridian has created an application note to provide detailed algorithms for each card type. Refer to the application note titled "73S12xxF Synchronous Card Design Application Note".

#### STX Data Register (STXData): 0xFE07 ← 0x00

#### Table 79: The STXData Register

| MSB      |          |          |          |          |          |          | LSB      | , |

|----------|----------|----------|----------|----------|----------|----------|----------|---|

| STXDAT.7 | STXDAT.6 | STXDAT.5 | STXDAT.4 | STXDAT.3 | STXDAT.2 | STXDAT.1 | STXDAT.0 |   |

| Bit       | Function                                                                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STXData.7 |                                                                                                                                                                          |

| STXData.6 |                                                                                                                                                                          |

| STXData.5 | Data to be transmitted to smart card. Gets stored in the TX FIFO and then extracted by                                                                                   |

| STXData.4 | the hardware and sent to the selected smart card. When the MPU reads this register, the byte pointer is changed to effectively "read out" the data. Thus, two reads will |

| STXData.3 | always result in an "empty" FIFO condition. The contents of the FIFO registers are not                                                                                   |

| STXData.2 | cleared, but will be overwritten by writes.                                                                                                                              |

| STXData.1 |                                                                                                                                                                          |

| STXData.0 |                                                                                                                                                                          |

## SRX Control/Status Register (SRXCtl): 0xFE08 ← 0x00

This register is used to monitor reception of data from the smart card.

#### Table 80: The SRXCtl Register

| MSB     |   |        |        |        |        |        | LSB     |

|---------|---|--------|--------|--------|--------|--------|---------|

| BIT9DAT | Ι | LASTRX | CRCERR | RXFULL | RXEMTY | RXOVRR | PARITYE |

| Bit             | Symbol  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRXCtl.7        | BIT9DAT | Bit 9 Data - When in sync mode and with MODE9/8B set, this bit will contain the data on IO (or SIO) pin that was sampled on the ninth CLK (or SCLK) rising edge. This is used to read data in synchronous 9-bit formats.                                                                                                                                                                                                                         |

| SRXCtl.6        | -       |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SRXCtl.5        | LASTRX  | Last RX Byte - User sets this bit during the reception of the last byte. When byte is received and this bit is set, logic checks CRC to match 0x1D0F (T=1 mode) or LRC to match 00h (T=1 mode), otherwise a CRC or LRC error is asserted.                                                                                                                                                                                                        |

| SRXCtl.4        | CRCERR  | (Read only) 1 = CRC (or LRC) error has been detected.                                                                                                                                                                                                                                                                                                                                                                                            |

| SRXCtl.3        | RXFULL  | (Read only) RX FIFO is full. Status bit to indicate RX FIFO is full.                                                                                                                                                                                                                                                                                                                                                                             |

| SRXCtl.2        | RXEMTY  | (Read only) RX FIFO is empty. This is only a status bit and does not generate an RX interrupt.                                                                                                                                                                                                                                                                                                                                                   |

| SRXCtl.1 RXOVRR |         | RX Overrun - (Read Only) Asserted when a receive-over-run condition has<br>occurred. An over-run is defined as a byte was received from the smart card<br>when the RX FIFO was full. Invalid data may be in the receive FIFO.<br>Firmware should take appropriate action. Cleared when read. Additional<br>writes to the RX FIFO are discarded when a RXOVRR occurs until the overrun<br>condition is cleared. Will generate an RXERR interrupt. |

| SRXCtl.0        | PARITYE | Parity Error - (Read only) 1 = The logic detected a parity error on incoming data from the smart card. Cleared when read. Will generate an RXERR interrupt.                                                                                                                                                                                                                                                                                      |

#### Byte Control Register (SByteCtl): 0xFE12 ← 0x2C

This register controls the processing of characters and the detection of the TS byte. When receiving, a Break is asserted at 10.5 ETU after the beginning of the start bit. Break from the card is sampled at 11 ETU.

## Table 89: The SByteCtl Register

| Ν | /ISB |       |       |          |          |   |   | LSB |  |

|---|------|-------|-------|----------|----------|---|---|-----|--|

|   | -    | DETTS | DIRTS | BRKDUR.1 | BRKDUR.0 | - | - | -   |  |

|   |      |       |       |          |          |   |   |     |  |

| Bit              | Symbol   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SByteCtl.7       | _        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SByteCtl.6       | DETTS    | Detect TS Byte – 1 = Next Byte is TS, 0 = Next byte is not TS. When set, the hardware will treat the next character received as the TS and determine if direct or indirect convention is being used. Direct convention is the default used if firmware does not set this bit prior to transmission of TS by the smart card to the firmware. The hardware will check parity and generate a break as defined by the DISPAR and BRKGEN bits in the parity control register. This bit is cleared by hardware after TS is received. TS is decoded prior to the FIFO and is stored in the receive FIFO. |

| SByteCtl.5 DIRTS |          | Direct Mode TS Select $-1$ = direct mode, 0 = indirect mode. Set/cleared by hardware when TS is processed indicating either direct/indirect mode of operation. When switching between smart cards, the firmware should write the bit appropriately since this register is not unique to an individual smart card (firmware should keep track of this bit).                                                                                                                                                                                                                                        |

| SByteCtl.4       | BRKDUR.1 | Break Duration Select $-00 = 1$ ETU, $01 = 1.5$ ETU, $10 = 2$ ETU,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SByteCtl.3       | BRKDUR.0 | 11 = reserved. Determines the length of a Break signal which is generated when detecting a parity error on a character reception in T=0 mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SByteCtl.2       | _        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SByteCtl.1       | -        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SByteCtl.0       | _        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### Block Guard Time Register (BGT): 0xFE16 ← 0x10

This register contains the Extra Guard Time Value (EGT) most-significant bit. The Extra Guard Time indicates the minimum time between the leading edges of the start bit of consecutive characters. The delay is depends on the T=0/T=1 mode. Used in transmit mode. This register also contains the Block Guard Time (BGT) value. Block Guard Time is the minimum time between the leading edge of the start bit of the last character received and the leading edge of the start bit of the first character transmitted. This should not be set less than the character length. The transmission of the first character will be held off until BGT has elapsed regardless of the TX data and TX/RX control bit timing.

#### Table 95: The BGT Register

| EGT.8 – – BGT.4 BGT.3 BGT.1 BGT.2 BGT    |    |

|------------------------------------------|----|

| EG1.8BG1.4   BG1.3   BG1.1   BG1.2   BG1 | .0 |

| Bit   | Symbol | Function                                                                |

|-------|--------|-------------------------------------------------------------------------|

| BGT.7 | EGT.8  | Most-significant bit for 9-bit EGT timer. See the EGT register.         |

| BGT.6 | -      |                                                                         |

| BGT.5 | _      |                                                                         |

| BGT.4 | BGT.4  |                                                                         |

| BGT.3 | BGT.3  | Time in ETUs between the start bit of the last received character to    |

| BGT.2 | BGT.2  | start bit of the first character transmitted to the smart card. Default |

| BGT.1 | BGT.1  | value is 22.                                                            |

| BGT.0 | BGT.0  |                                                                         |

#### Extra Guard Time Register (EGT): 0xFE17 ← 0x0C

This register contains the Extra Guard Time Value (EGT) least-significant byte. The Extra Guard Time indicates the minimum time between the leading edges of the start bit of consecutive characters. The delay depends on the T=0/T=1 mode. Used in transmit mode.

#### Table 96: The EGT Register

| MS | 3                                                           |     |                                                                                                                                                                                                               |             |               |               |              |             | LSB    |  |

|----|-------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|---------------|--------------|-------------|--------|--|

| E  | EGT.7 EG                                                    |     | T.6                                                                                                                                                                                                           | EGT.5       | EGT.4         | EGT.3         | EGT.1        | EGT.2       | EGT.0  |  |

|    |                                                             |     |                                                                                                                                                                                                               |             |               |               |              |             |        |  |

|    | Bi                                                          | t   | Function                                                                                                                                                                                                      |             |               |               |              |             |        |  |

|    | EGT.7<br>EGT.6<br>EGT.5<br>EGT.4<br>EGT.3<br>EGT.2<br>EGT.1 |     |                                                                                                                                                                                                               |             |               |               |              |             |        |  |

|    |                                                             |     |                                                                                                                                                                                                               |             |               |               |              |             |        |  |

|    |                                                             |     | Time                                                                                                                                                                                                          | in ETUs be  | etween star   | t bits of con | secutive ch  | aracters. I | n T=0  |  |

|    |                                                             |     | mode, the minimum is 1. In T=0, the leading edge of the next start bit may be delayed if there is a break detected from the smart card. Default value is 12. In T=0 mode, regardless of the value loaded, the |             |               |               |              |             |        |  |

|    |                                                             |     |                                                                                                                                                                                                               |             |               |               |              |             |        |  |

|    |                                                             |     | minir                                                                                                                                                                                                         | num value i | is 12, and fo | or T=1 mod    | e, the minin | num value i | is 11. |  |

|    |                                                             |     |                                                                                                                                                                                                               |             |               |               |              |             |        |  |

|    | EG                                                          | Г.О |                                                                                                                                                                                                               |             |               |               |              |             |        |  |

#### ATR Timeout Registers (ATRLsB): 0xFE20 ← 0x00, (ATRMsB): 0xFE1F ← 0x00

These registers form the ATR timeout (ATRTO [15:0]) parameter. Time in ETU between the leading edge of the first character and leading edge of the last character of the ATR response. Timer is enabled when the RCVATR is set and starts when leading edge of the first start bit is received and disabled when the RCVATR is cleared. An ATR timeout is generated if this time is exceeded.

#### Table 103: The ATRLsB Register

| MSB     |         |         |         |         |         |         | LSB     |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ATRTO.7 | ATRTO.6 | ATRTO.5 | ATRTO.4 | ATRTO.3 | ATRTO.1 | ATRTO.2 | ATRTO.0 |

#### Table 104: The ATRMsB Register

| MSB      |          |          |          |          |          |         | LSB     |

|----------|----------|----------|----------|----------|----------|---------|---------|

| ATRTO.15 | ATRTO.14 | ATRTO.13 | ATRTO.12 | ATRTO.11 | ATRTO.10 | ATRTO.9 | ATRTO.8 |

#### TS Timeout Register (STSTO): 0xFE21 ← 0x00

The TS timeout is the time in ETU between the de-assertion of smart card reset and the leading edge of the TS character in the ATR (when DETTS is set). The timer is started when smart card reset is de-asserted. An ATR timeout is generated if this time is exceeded (MUTE card).

#### Table 105: The STSTO Register

| MSB    |        |        |        |        |        |        | LSB    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TST0.7 | TST0.6 | TST0.5 | TST0.4 | TST0.3 | TST0.1 | TST0.2 | TST0.0 |

#### Reset Time Register (RLength): 0xFE22 ← 0x70

Time in ETUs that the hardware delays the de-assertion of RST. If set to 0 and RSTCRD = 0, the hardware adds no extra delay and the hardware will release RST after VCCOK is asserted during power-up. If set to 1, it will delay the release of RST by the time in this register. When the firmware sets the RSTCRD bit, the hardware will assert reset (RST = 0 on pin). When firmware clears the bit, the hardware will release RST after the delay specified in Rlen. If firmware sets the RSTCRD bit prior to instructing the power to be applied to the smart card, the hardware will not release RST after power-up until RLen after the firmware clears the RSTCRD bit. This provides a means to power up the smart card and hold it in reset until the firmware wants to release the RST to the selected smart card. Works with the selected smart card interface.

#### Table 106: The RLength Register

| MSB    |        |        |        |        |        |        | LSB    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RLen.7 | RLen.6 | RLen.5 | RLen.4 | RLen.3 | RLen.1 | RLen.2 | RLen.0 |

## **2** Typical Application Schematic

Figure 25: 73S1210F Typical Application Schematic

| Symbol                              | Parameter                       | Condition                                                                                                      | Min                   | Тур. | Мах                   | Unit |

|-------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|------|

| Interface                           | Requirements – Data Signals: I/ | O, AUX1 and AUX2                                                                                               |                       |      |                       | •    |

|                                     |                                 | I <sub>OH</sub> = 0                                                                                            | 0.9 * V <sub>CC</sub> |      | V <sub>cc</sub> +0.1  | V    |

| V <sub>OH</sub>                     | Output level, high              | I <sub>OH</sub> = -40μA                                                                                        | 0.75 V <sub>CC</sub>  |      | V <sub>cc</sub> +0.1  | V    |

| V <sub>OL</sub>                     | Output level, low               | I <sub>OL</sub> = 1mA                                                                                          |                       |      | 0.15 *V <sub>CC</sub> | V    |

| V <sub>IH</sub>                     | Input level, high               |                                                                                                                | 0.6 * V <sub>CC</sub> |      | V <sub>CC</sub> +0.30 | V    |

| V <sub>IL</sub>                     | Input level, low                |                                                                                                                | -0.15                 |      | 0.2 * V <sub>CC</sub> | V    |

| V                                   | Output voltage when outside     | $I_{OL} = 0$                                                                                                   |                       |      | 0.1                   | V    |

| VINACT                              | of session                      | $I_{OL} = 1mA$                                                                                                 |                       |      | 0.3                   | V    |

| <b>I</b> <sub>LEAK</sub>            | Input leakage                   | $V_{IH} = V_{CC}$                                                                                              |                       |      | 10                    | μA   |

| IIL                                 | Input current, low              | $V_{IL} = 0$                                                                                                   |                       |      | 0.65                  | mA   |

| IIL                                 | Input current, low              | $V_{IL} = 0$                                                                                                   |                       |      | 0.7                   | mA   |

| I <sub>SHORTL</sub>                 | Short circuit output current    | For output low, shorted to $V_{CC}$ through $33\Omega$                                                         |                       |      | 15                    | mA   |

| I <sub>SHORTH</sub>                 | Short circuit output current    | For output high,<br>shorted to ground<br>through 33Ω                                                           |                       |      | 15                    | mA   |

| t <sub>R</sub> , t <sub>F</sub>     | Output rise time, fall times    | For I/O, AUX1, AUX2,<br>$C_L = 80 pF$ , 10% to<br>90%. For I/OUC,<br>AUX1UC, AUX2UC, CL<br>= 50Pf, 10% to 90%. |                       |      | 100                   | ns   |

| t <sub>IR</sub> , t <sub>IF</sub>   | Input rise, fall times          |                                                                                                                |                       |      | 1                     | μS   |

| R <sub>PU</sub>                     | Internal pull-up resistor       | Output stable for<br>>200ns                                                                                    | 8                     | 11   | 14                    | kΩ   |

| FD <sub>MAX</sub> Maximum data rate |                                 |                                                                                                                |                       |      | 1                     | MHz  |

| Reset and                           | Clock for card interface, RST,  | CLK                                                                                                            |                       |      |                       |      |

| V <sub>OH</sub>                     | Output level, high              | I <sub>OH</sub> = -200μA                                                                                       | 0.9 * V <sub>CC</sub> |      | V <sub>cc</sub>       | V    |

| V <sub>OL</sub>                     | Output level, low               | I <sub>OL</sub> = 200μA                                                                                        | 0                     |      | 0.15 *V <sub>CC</sub> | V    |

| <i>\</i> /                          | Output voltage when outside     | $I_{OL} = 0$                                                                                                   |                       |      | 0.1                   | V    |

| VINACT                              | of session                      | I <sub>OL</sub> = 1mA                                                                                          |                       |      | 0.3                   | V    |

| I <sub>RST_LIM</sub>                | Output current limit, RST       |                                                                                                                |                       |      | 30                    |      |

| I <sub>CLK_LIM</sub>                | Output current limit, CLK       |                                                                                                                |                       |      | 70                    | mA   |

|                                     |                                 | $C_{L} = 35 pF$ for CLK,<br>10% to 90%                                                                         |                       |      | 8                     | ns   |

| t <sub>R</sub> , t <sub>F</sub>     | Output rise time, fall time     | C <sub>L</sub> = 200pF for RST,<br>10% to 90%                                                                  |                       |      | 100                   | ns   |

| δ                                   | Duty cycle for CLK              | $C_L$ = 35pF, $F_{CLK}$<br>≤ 20MHz, CLKIN duty<br>cycle is 48% to 52%.                                         | 45                    |      | 55                    | %    |

Figure 37: Test and Security Pin Circuit

Figure 38: Analog Input Circuit

Figure 39: Smart Card Output Circuit

## 5.2 44-pin QFN Pinout

Figure 45: 73S1210F 44 QFN Pinout

# **Revision History**

| Revision | Date       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.0      | 5/10/2007  | First publication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 1.1      | 11/6/2007  | In Table 1, added Equivalent Circuit references.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|          |            | In Section 1.4, updated program security description to remove pre-boot and 32-cycle references.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|          |            | In Section 1.7.1, changed "Mcount is configured in the MCLKCtl register must be bound between a value of 1 to 7. The possible crystal or external clock are shown in Table 12." to "Mcount is configured in the MCLKCtl register must be bound between a value of 1 to 7. The possible crystal or external clock frequencies for getting MCLK = 96MHz are shown in Table 11."                                                                                                                                                                                                                                   |  |

|          |            | In the BRCON description, changed "If BSEL = 1, the baud rate is derived using timer 1." to "If BSEL = 0, the baud rate is derived using timer 1."                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|          |            | In Section 1.7.14, removed the following from the emulator port description: "The signals of the emulator port have weak pull-ups. Adding resistor footprints for signals E_RST, E_TCLK and E_RXTX on the PCB is recommended. If necessary, adding 10K $\Omega$ pull-up resistors on E_TCLK and E_RXTX and a 3K $\Omega$ on E_RST will help the emulator operate normally if a problem arises."                                                                                                                                                                                                                 |  |