# E · ) ( Faralog Devices Inc./Maxim Integrated - 73S1210F-68MR/F/PG Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 80515                                                                  |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 24MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SmartCard, UART/USART                                |

| Peripherals                | LED, POR, WDT                                                          |

| Number of I/O              | 8                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | •                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6.5V                                                            |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 68-VFQFN Exposed Pad                                                   |

| Supplier Device Package    | 68-QFN (8x8)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/73s1210f-68mr-f-pg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1    | •          |                                                                                              |    |  |  |  |  |

|------|------------|----------------------------------------------------------------------------------------------|----|--|--|--|--|

|      | 1.1        | Pin Description                                                                              | 8  |  |  |  |  |

|      | 1.2        | Hardware Overview                                                                            |    |  |  |  |  |

|      | 1.3        | 80515 MPU Core                                                                               | 11 |  |  |  |  |

|      |            | 1.3.1 80515 Overview                                                                         | 11 |  |  |  |  |

|      |            | 1.3.2 Memory Organization                                                                    |    |  |  |  |  |

|      | 1.4        | Program Security                                                                             |    |  |  |  |  |

|      | 1.5        | Special Function Registers (SFRs)                                                            |    |  |  |  |  |

|      |            | 1.5.1 Internal Data Special Function Registers (SFRs)                                        |    |  |  |  |  |

|      |            | 1.5.2 IRAM Special Function Registers (Generic 80515 SFRs)                                   |    |  |  |  |  |

|      |            | 1.5.3 External Data Special Function Registers (SFRs)                                        |    |  |  |  |  |

|      | 1.6        | Instruction Set                                                                              |    |  |  |  |  |

|      | 1.7        | Peripheral Descriptions                                                                      |    |  |  |  |  |

|      |            | 1.7.1 Oscillator and Clock Generation                                                        |    |  |  |  |  |

|      |            | 1.7.2 Power Supply Management                                                                |    |  |  |  |  |

|      |            | 1.7.3 Power ON/OFF                                                                           |    |  |  |  |  |

|      |            | 1.7.4 Power Control Modes                                                                    |    |  |  |  |  |

|      |            | 1.7.5 Interrupts                                                                             |    |  |  |  |  |

|      |            | 1.7.6 UART                                                                                   |    |  |  |  |  |

|      |            | <ul><li>1.7.7 Timers and Counters</li><li>1.7.8 WD Timer (Software Watchdog Timer)</li></ul> |    |  |  |  |  |

|      |            | 1.7.9 User (USR) Ports                                                                       |    |  |  |  |  |

|      |            | 1.7.9 Oser (OSIC) Fors                                                                       |    |  |  |  |  |

|      |            | 1.7.10 Analog Voltage Comparator                                                             |    |  |  |  |  |

|      |            | 1.7.12 I <sup>2</sup> C Master Interface                                                     |    |  |  |  |  |

|      |            | 1.7.13 Keypad Interface                                                                      |    |  |  |  |  |

|      |            | 1.7.14 Emulator Port                                                                         |    |  |  |  |  |

|      |            | 1.7.15 Smart Card Interface Function                                                         |    |  |  |  |  |

|      |            | 1.7.16 VDD Fault Detect Function                                                             |    |  |  |  |  |

| 2    | Typic      | cal Application Schematic1                                                                   | 04 |  |  |  |  |

|      |            |                                                                                              |    |  |  |  |  |

| 3    |            | rical Specification1                                                                         |    |  |  |  |  |

|      | 3.1        | Absolute Maximum Ratings1                                                                    |    |  |  |  |  |

|      | 3.2        | Recommended Operating Conditions                                                             |    |  |  |  |  |

|      | 3.3        | Digital IO Characteristics                                                                   |    |  |  |  |  |

|      | 3.4        | Oscillator Interface Requirements                                                            |    |  |  |  |  |

|      | 3.5        | DC Characteristics: Analog Input                                                             |    |  |  |  |  |

|      | 3.6        | Smart Card Interface Requirements                                                            |    |  |  |  |  |

|      | 3.7        | DC Characteristics                                                                           |    |  |  |  |  |

|      | 3.8        | Current Fault Detection Circuits1                                                            |    |  |  |  |  |

| 4    | Equi       | valent Circuits1                                                                             | 12 |  |  |  |  |

| 5    | Pack       | age Pin Designation1                                                                         | 20 |  |  |  |  |

|      | 5.1        | 68-pin QFN Pinout                                                                            |    |  |  |  |  |

|      | 5.2        | 44-pin QFN Pinout                                                                            |    |  |  |  |  |

| 6    |            | aging Information1                                                                           |    |  |  |  |  |

| 0    |            |                                                                                              |    |  |  |  |  |

|      | 6.1<br>6.2 | 68-Pin QFN Package Outline                                                                   |    |  |  |  |  |

|      | -          | 44-Pin QFN Package Outline1                                                                  |    |  |  |  |  |

| 7    | Orde       | ring Information1                                                                            | 24 |  |  |  |  |

| 8    | Relat      | ed Documentation1                                                                            | 24 |  |  |  |  |

| 9    | Cont       | act Information1                                                                             | 24 |  |  |  |  |

| Revi | ision      | History1                                                                                     | 25 |  |  |  |  |

## MPU Clock Control Register (MPUCKCtl): 0xFFA1 ← 0x0C

#### Table 13: The TCON Register

| MSB |   |        |        |        |        |        | LSB    |

|-----|---|--------|--------|--------|--------|--------|--------|

| _   | - | MDIV.5 | MDIV.4 | MDIV.3 | MDIV.2 | MDIV.1 | MDIV.0 |

| Bit        | Symbol | Function                                                                                                |

|------------|--------|---------------------------------------------------------------------------------------------------------|

| MPUCKCtl.7 | _      |                                                                                                         |

| MPUCKCtl.6 | -      |                                                                                                         |

| MPUCKCtl.5 | MDIV.5 |                                                                                                         |

| MPUCKCtl.4 | MDIV.4 | This value determines the ratio of the MPU master clock frequency to the VCO frequency (MCLK) such that |

| MPUCKCtl.3 | MDIV.3 | MPUClk = MCLK/(2 * (MPUCKDiv(5:0) + 1)).                                                                |

| MPUCKCtl.2 | MDIV.2 | Do not use values of 0 or 1 for MPUCKDiv(n).                                                            |

| MPUCKCtl.1 | MDIV.1 | Default is 0Ch to set CPCLK = $3.6923$ MHz.                                                             |

| MPUCKCtl.0 | MDIV.0 |                                                                                                         |

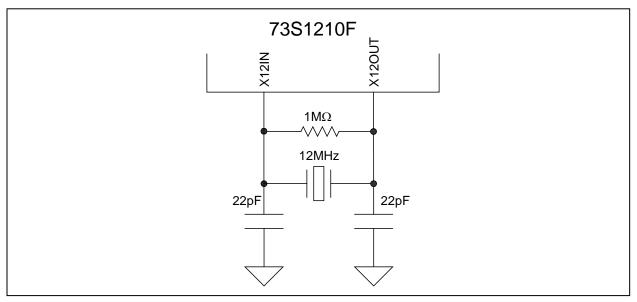

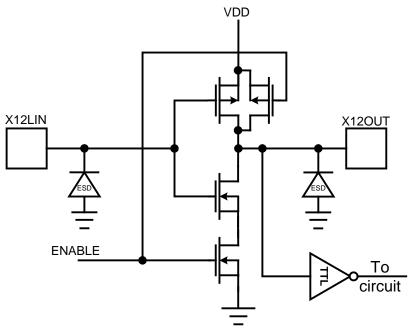

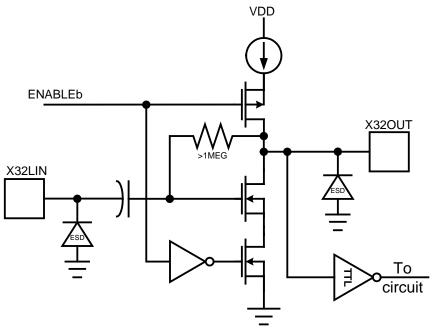

The oscillator circuits are designed to connect directly to standard parallel resonant crystal in a Pierce oscillator configuration. Each side of the crystal should include a 22pF capacitor to ground for both oscillator circuits and a  $1M\Omega$  resistor is required across the 12MHz crystal.

Note: The crystal should be placed as close as possible to the IC, and vias should be avoided.

#### Figure 4: Oscillator Circuit

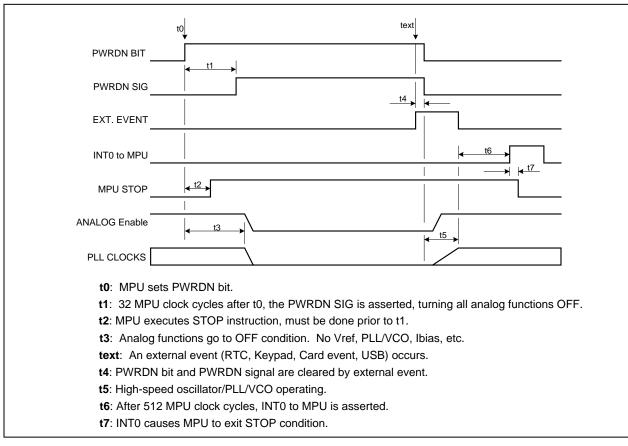

Figure 8: Power Down Sequencing

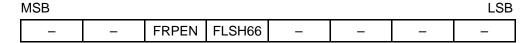

#### Miscellaneous Control Register 1 (MISCtI1): 0xFFF2 ← 0x10

Table 16: The MISCtl1 Register

| Bit       | Symbol | Function                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MISCtl1.7 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MISCtl1.6 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MISCtl1.5 | FRPEN  | Flash Read Pulse enable (low). If FRPEN = 1, the Flash Read signal is passed through with no change. When FRPEN = 0 a one-shot circuit that shortens the Flash Read signal is enabled to save power. The Flash Read pulse will shorten to 40 or 66ns (approximate based on the setting of the FLSH66 bit) in duration, regardless of the MPU clock rate. For MPU clock frequencies greater than 10MHz, this bit should be set high. |

| MISCtl1.4 | FLSH66 | When high, creates a 66ns Flash read pulse, otherwise creates a 40ns read pulse when FRPEN is set.                                                                                                                                                                                                                                                                                                                                  |

| MISCtl1.3 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MISCtl1.2 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MISCtl1.1 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MISCtl1.0 | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### Master Clock Control Register (MCLKCtl): 0x8F ← 0x0A

#### Table 17: The MCLKCtl Register

| MSB   |      |      |   |   |       |       | LSB   |

|-------|------|------|---|---|-------|-------|-------|

| HSOEN | KBEN | SCEN | _ | - | MCT.2 | MCT.1 | MCT.0 |

| Bit       | Symbol | Function                                                                                                                                                                                                     |  |  |

|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MCLKCtl.7 | HSOEN* | High-speed oscillator enable. When set = 1, disables the high-speed crystal oscillator and VCO/PLL system. This bit is not changed when the PWRDN bit is set but the oscillator/VCO/PLL is disabled.         |  |  |

| MCLKCtl.6 | KBEN   | 1 = Disable the keypad logic clock. This bit is not changed in PWRDN mode but the function is disabled.                                                                                                      |  |  |

| MCLKCtl.5 | SCEN   | 1 = Disable the smart card logic clock. This bit is not changed in PWRDN mode but the function is disabled. Interrupt logic for card insertion/removal remains operable even with smart card clock disabled. |  |  |

| MCLKCtl.4 | _      |                                                                                                                                                                                                              |  |  |

| MCLKCtl.3 | _      |                                                                                                                                                                                                              |  |  |

| MCLKCtl.2 | MCT.2  | This value determines the ratio of the VCO frequency (MCLK) to the                                                                                                                                           |  |  |

| MCLKCtl.1 | MCT.1  | high-speed crystal oscillator frequency such that:                                                                                                                                                           |  |  |

| MCLKCtl.0 | MCT.0  | MCLK = $(MCount^2 + 4)^*Fxtal$ . The default value is MCount = 2h such that MCLK = $(2^2 + 4)^*12.00MHz = 96MHz$ .                                                                                           |  |  |

\*Note: The HSOEN bit should never be set under normal circumstances. Power down control should only be initiated via use of the PWRDN bit in MISCtl0.

# Timer/Counter Control Register (TCON): 0x88 ← 0x00

Table 22: The TCON Register

| MSB |     |     |     |     |     |     | LSB | , |

|-----|-----|-----|-----|-----|-----|-----|-----|---|

| TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |   |

| Bit    | Symbol | Function                                                                                                                                       |  |  |  |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TCON.7 | TF1    | Timer 1 overflow flag.                                                                                                                         |  |  |  |

| TCON.6 | TR1    | Not used for interrupt control.                                                                                                                |  |  |  |

| TCON.5 | TF0    | mer 0 overflow flag.                                                                                                                           |  |  |  |

| TCON.4 | TR0    | lot used for interrupt control.                                                                                                                |  |  |  |

| TCON.3 | IE1    | nterrupt 1 edge flag is set by hardware when the falling edge on external nterrupt int1 is observed. Cleared when an interrupt is processed.   |  |  |  |

| TCON.2 | IT1    | Interrupt 1 type control bit. 1 selects falling edge and 0 selects low level for input pin to cause an interrupt.                              |  |  |  |

| TCON.1 | IE0    | Interrupt 0 edge flag is set by hardware when the falling edge on external interrupt int0 is observed. Cleared when an interrupt is processed. |  |  |  |

| TCON.0 | IT0    | Interrupt 0 type control bit. 1 selects falling edge and 0 sets low level for input pin to cause interrupt.                                    |  |  |  |

# Timer/Interrupt 2 Control Register (T2CON): 0xC8 ← 0x00

# Table 23: The T2CON Register

| Bit     | Symbol | Function                                                                                                               |

|---------|--------|------------------------------------------------------------------------------------------------------------------------|

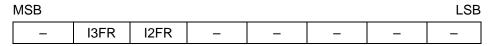

| T2CON.7 | -      |                                                                                                                        |

|         |        | External interrupt 3 failing/rising edge flag.                                                                         |

| T2CON.6 | I3FR   | I3FR = 0 external interrupt 3 negative transition active.<br>I3FR = 1 external interrupt 3 positive transition active. |

|         |        | External interrupt 3 failing/rising edge flag.                                                                         |

| T2CON.5 | I2FR   | I2FR = 0 external interrupt 3 negative transition active.<br>I2FR = 1 external interrupt 3 positive transition active. |

| T2CON.4 | -      |                                                                                                                        |

| T2CON.3 | -      |                                                                                                                        |

| T2CON.2 | _      |                                                                                                                        |

| T2CON.1 | _      |                                                                                                                        |

| T2CON.0 | _      |                                                                                                                        |

# 1.7.6 UART

The 80515 core of the 73S1210F includes two separate UARTs that can be programmed to communicate with a host. The 73S1210F can only connect one UART at a time since there is only one set of TX and Rx pins. The MISCtI0 register is used to select which UART is connected to the TX and RX pins. Each UART has a different set of operating modes that the user can select according to their needs. The UART is a dedicated 2-wire serial interface, which can communicate with an external host processor at up to 115,200 bits/s. The TX and RX pins operate at the V<sub>DD</sub> supply voltage levels and should never exceed 3.6V. The operation of each pin is as follows:

**RX**: Serial input data is applied at this pin. Conforming to RS-232 standard, the bytes are input LSB first. The voltage applied at RX must not exceed 3.6V.

**TX**: This pin is used to output the serial data. The bytes are output LSB first.

The 73S1210F has several UART-related read/write registers. All UART transfers are programmable for parity enable, parity select, 2 stop bits/1 stop bit and XON/XOFF options for variable communication baud rates from 300 to 115200 bps. Table 33 shows the selectable UART operation modes and Table 34 shows how the baud rates are calculated.

|        | UART 0                                                                                                        | UART 1                                                                                       |

|--------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Mode 0 | N/A                                                                                                           | Start bit, 8 data bits, parity, stop bit, variable baud rate (internal baud rate generator). |

| Mode 1 | Start bit, 8 data bits, stop bit, variable<br>baud rate (internal baud rate generator<br>or timer 1).         | Start bit, 8 data bits, stop bit, variable baud rate (internal baud rate generator).         |

| Mode 2 | Start bit, 8 data bits, parity, stop bit, fixed baud rate 1/32 or 1/64 of f <sub>CKMPU</sub> .                | N/A                                                                                          |

| Mode 3 | Start bit, 8 data bits, parity, stop bit,<br>variable baud rate (internal baud rate<br>generator or timer 1). | N/A                                                                                          |

#### Table 33: UART Modes

Note: Parity of serial data is available through the P flag of the accumulator. Seven-bit serial modes with parity, such as those used by the FLAG protocol, can be simulated by setting and reading bit 7 of 8-bit output data. Seven-bit serial modes without parity can be simulated by setting bit 7 to a constant 1. 8-bit serial modes with parity can be simulated by setting the 9th bit, using the control bits S0CON3 and S1CON3 in the S0COn and S1CON SFRs.

#### Table 34: Baud Rate Generation

|                    | Using Timer 1                                              | Using Internal Baud Rate Generator                                      |

|--------------------|------------------------------------------------------------|-------------------------------------------------------------------------|

| Serial Interface 0 | 2 <sup>smod</sup> * f <sub>CKMPU</sub> / (384 * (256-TH1)) | 2 <sup>smod</sup> * f <sub>CKMPU</sub> /(64 * (2 <sup>10</sup> -S0REL)) |

| Serial Interface 1 | N/A                                                        | f <sub>CKMPU</sub> /(32 * (2 <sup>10</sup> -S1REL))                     |

Note: S0REL (9:0) and S1REL (9:0) are 10-bit values derived by combining bits from the respective timer reload registers SxRELH (bits 1:0) and SxRELL (bits 7:0). TH1 is the high byte of timer 1. The SMOD bit is located in the PCON SFR.

#### • Mode 3

The only difference between Mode 2 and Mode 3 is that in Mode 3 either internal baud rate generator or timer 1 can be use to specify baud rate.

The SOBUF register is used to read/write data to/from the serial 0 interface.

#### Serial Interface 0 Control Register (S0CON): 0x9B ← 0x00

Transmit and receive data are transferred via this register.

#### Table 38: The S0CON Register

| MSB |     |      |      |      |      |     | LSB |  |

|-----|-----|------|------|------|------|-----|-----|--|

| SM0 | SM1 | SM20 | REN0 | TB80 | RB80 | TI0 | RI0 |  |

| Bit     | Symbol           | Function                                                                                                                                                      |                                                                             |         |               |                                    |  |  |

|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------|---------------|------------------------------------|--|--|

| S0CON.7 | SM0              | These two bi                                                                                                                                                  | its set the UART                                                            | ) mode: |               |                                    |  |  |

|         |                  | Mode Description SM0 SM1                                                                                                                                      |                                                                             |         |               |                                    |  |  |

|         |                  | 0                                                                                                                                                             | N/A                                                                         | 0       | 0             |                                    |  |  |

| S0CON.6 | SM1              | 1 1 8-bit UART 0                                                                                                                                              |                                                                             |         |               |                                    |  |  |

|         |                  | 2                                                                                                                                                             | 9-bit UART                                                                  | 1       | 0             |                                    |  |  |

|         | 3 9-bit UART 1 1 |                                                                                                                                                               |                                                                             |         |               |                                    |  |  |

| S0CON.5 | SM20             | Enables the                                                                                                                                                   | Enables the inter-processor communication feature.                          |         |               |                                    |  |  |

| S0CON.4 | REN0             | If set, enable                                                                                                                                                | If set, enables serial reception. Cleared by software to disable reception. |         |               |                                    |  |  |

| S0CON.3 | TB80             |                                                                                                                                                               | n the function it p                                                         |         |               | leared by the MPU,<br>ltiprocessor |  |  |

| S0CON.2 | RB80             | In Modes 2 and 3 it is the 9th data bit received. In Mode 1, if SM20 is 0, RB80 is the stop bit. In Mode 0 this bit is not used. Must be cleared by software. |                                                                             |         |               |                                    |  |  |

| S0CON.1 | TI0              | Transmit interrupt flag, set by hardware after completion of a serial transfer.<br>Must be cleared by software.                                               |                                                                             |         |               |                                    |  |  |

| S0CON.0 | RI0              |                                                                                                                                                               | rrupt flag, set by<br>lust be cleared by                                    |         | er completion | of a serial                        |  |  |

#### 1.7.6.2 Serial Interface 1

The Serial Interface 1 can operate in 2 modes:

#### • Mode A

This mode is similar to Mode 2 and 3 of Serial interface 0, 11 bits are transmitted or received: a start bit (0), 8 data bits (LSB first), a programmable 9th bit, and a stop bit (1). The 9th bit can be used to control the parity of the serial interface: at transmission, bit TB81 in S1CON is outputted as the 9th bit, and at receive, the 9th bit affects RB81 in Special Function Register S1CON. The only difference between Mode 3 and A is that in Mode A only the internal baud rate generator can be use to specify baud rate.

• Mode B

This mode is similar to Mode 1 of Serial interface 0. Pin RX serves as input, and TX serves as serial output. No external shift clock is used, 10 bits are transmitted: a start bit (always 0), 8 data bits (LSB first), and a stop bit (always 1). On receive, a start bit synchronizes the transmission, 8 data bits are available by reading S1BUF, and stop bit sets the flag RB81 in the Special Function Register S1CON. In mode 1, the internal baud rate generator is use to specify the baud rate.

The S1BUF register is used to read/write data to/from the serial 1 interface.

#### Serial Interface Control Register (S1CON): 0x9B ← 0x00

The function of the serial port depends on the setting of the Serial Port Control Register S1CON.

| MSB |   |      |      |      |      |     | LSB |  |

|-----|---|------|------|------|------|-----|-----|--|

| SM  | - | SM21 | REN1 | TB81 | RB81 | TI1 | RI1 |  |

Table 39: The S1CON Register

| Bit     | Symbol |             | Function                                                                                                        |                    |                    |                                             |  |  |  |  |

|---------|--------|-------------|-----------------------------------------------------------------------------------------------------------------|--------------------|--------------------|---------------------------------------------|--|--|--|--|

| S1CON.7 | SM     | Sets the l  | Sets the UART operation mode.                                                                                   |                    |                    |                                             |  |  |  |  |

|         |        | SM          | Mode                                                                                                            |                    |                    |                                             |  |  |  |  |

|         |        | 0           | А                                                                                                               | 9-bit UART         | variable           |                                             |  |  |  |  |

|         |        | 1           | В                                                                                                               | 8-bit UART         | variable           |                                             |  |  |  |  |

| S1CON.6 | _      |             |                                                                                                                 |                    |                    |                                             |  |  |  |  |

| S1CON.5 | SM21   | Enables t   | he inter-pro                                                                                                    | cessor communic    | ation feature.     |                                             |  |  |  |  |

| S1CON.4 | REN1   | If set, ena | ables serial                                                                                                    | reception. Cleare  | d by software to d | disable reception.                          |  |  |  |  |

| S1CON.3 | TB81   |             |                                                                                                                 |                    |                    | by the MPU, depending communication, etc.). |  |  |  |  |

| S1CON.2 | RB81   | In Mode E   | 3, if sm21 is                                                                                                   | 0, rb81 is the sto | p bit. Must be cle | eared by software.                          |  |  |  |  |

| S1CON.1 | TI1    |             | Transmit interrupt flag, set by hardware after completion of a serial transfer.<br>Must be cleared by software. |                    |                    |                                             |  |  |  |  |

| S1CON.0 | RI1    |             | nterrupt flac<br>leared by s                                                                                    |                    | after completion   | of a serial reception.                      |  |  |  |  |

**Multiprocessor operation mode:** The feature of receiving 9 bits in Modes 2 and 3 of Serial Interface 0 or in Mode A of Serial Interface 1 can be used for multiprocessor communication. In this case, the slave processors have bit SM20 in S0CON or SM21 in S1CON set to 1. When the master processor outputs slave's address, it sets the 9th bit to 1, causing a serial port receive interrupt in all the slaves. The slave processors compare the received byte with their network address. If there is a match, the addressed slave will clear SM20 or SM21 and receive the rest of the message, while other slaves will leave the SM20 or SM21 bit unaffected and ignore this message. After addressing the slave, the host will output the rest of the message with the 9th bit set to 0, so no serial port receive interrupt will be generated in unselected slaves.

#### Mode 0

Putting either timer/counter into mode 0 configures it as an 8-bit timer/counter with a divide-by-32 prescaler. In this mode, the timer register is configured as a 13-bit register. As the count rolls over from all 1's to all 0's, it sets the timer overflow flag TF0. The overflow flag TF0 then can be used to request an interrupt. The counted input is enabled to the timer when TRx = 1 and either GATE = 0 or TX = 1 (setting GATE = 1 allows the timer to be controlled by external input TX, to facilitate pulse width measurements). TRx are control bits in the special function register TCON; GATE is in TMOD. The 13-bit register consists of all 8 bits of TH1 and the lower 5 bits of TL0. The upper 3 bits of TL0 are indeterminate and should be ignored. Setting the run flag (TRx) does not clear the registers. Mode 0 operation is the same for timer 0 as for timer 1.

#### Mode 1

Mode 1 is the same as mode 0, except that the timer register is run with all 16 bits.

#### Mode 2

Mode 2 configures the timer register as an 8-bit counter (TLx) with automatic reload. The overflow from TLx not only sets TFx, but also reloads TLx with the contents of THx, which is preset by software. The reload leaves THx unchanged.

#### Mode 3

Mode 3 has different effects on timer 0 and timer 1. Timer 1 in mode 3 simply holds its count. The effect is the same as setting TR1 = 0. Timer 0 in mode 3 establishes TL0 and TH0 as two separate counters. TL0 uses the timer 0 control bits: C/T, GATE, TR0, INT0, and TF0. TH0 is locked into a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from timer 1. Thus, TH0 now controls the "timer 1" interrupt. Mode 3 is provided for applications requiring an extra 8-bit timer or counter. When timer 0 is in mode 3, timer 1 can be turned on and off by switching it out of and into its own mode 3, or can still be used by the serial channel as a baud rate generator, or in fact, in any application not requiring an interrupt from timer 1 itself.

## Timer/Counter Control Register (TCON): 0x88 ← 0x00

| MSB |     |     |     |     |     |     | LSB |  |

|-----|-----|-----|-----|-----|-----|-----|-----|--|

| TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |  |

Table 42: The TCON Register

| Bit    | Symbol | Function                                                                                                                                       |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| TCON.7 | TF1    | Timer 1 overflow flag.                                                                                                                         |

| TCON.6 | TR1    | Not used for interrupt control.                                                                                                                |

| TCON.5 | TF0    | Timer 0 overflow flag.                                                                                                                         |

| TCON.4 | TR0    | Not used for interrupt control.                                                                                                                |

| TCON.3 | IE1    | Interrupt 1 edge flag is set by hardware when the falling edge on external interrupt int1 is observed. Cleared when an interrupt is processed. |

| TCON.2 | IT1    | Interrupt 1 type control bit. 1 selects falling edge and 0 selects low level for input pin to cause an interrupt.                              |

| TCON.1 | IE0    | Interrupt 0 edge flag is set by hardware when the falling edge on external interrupt int0 is observed. Cleared when an interrupt is processed. |

| TCON.0 | IT0    | Interrupt 0 type control bit. 1 selects falling edge and 0 sets low level for input pin to cause interrupt.                                    |

# External Interrupt Control Register (INT6CtI): 0xFF95 ← 0x00

# Table 63: The INT6Ctl Register

| MSB |   |        |        |        |        |       | LSB   |  |

|-----|---|--------|--------|--------|--------|-------|-------|--|

| -   | - | VFTIEN | VFTINT | I2CIEN | I2CINT | ANIEN | ANINT |  |

| Bit       | Symbol                                   | Function                                                                                                       |  |  |  |  |  |

|-----------|------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| INT6Ctl.7 | _                                        |                                                                                                                |  |  |  |  |  |

| INT6Ctl.6 | -                                        |                                                                                                                |  |  |  |  |  |

| INT6Ctl.5 | Ctl.5 VFTIEN VDD fault interrupt enable. |                                                                                                                |  |  |  |  |  |

| INT6Ctl.4 | VFTINT                                   | VDD fault interrupt flag.                                                                                      |  |  |  |  |  |

| INT6Ctl.3 | I2CIEN                                   | When set = 1, the $I^2C$ interrupt is enabled.                                                                 |  |  |  |  |  |

| INT6Ctl.2 | I2CINT                                   | When set = 1, the $I^2C$ transaction has completed. Cleared upon the start of a subsequent $I^2C$ transaction. |  |  |  |  |  |

| INT6Ctl.1 | ANIEN                                    | Analog compare interrupt enable.                                                                               |  |  |  |  |  |

| INT6Ctl.0 | ANINT                                    | Analog compare interrupt flag.                                                                                 |  |  |  |  |  |

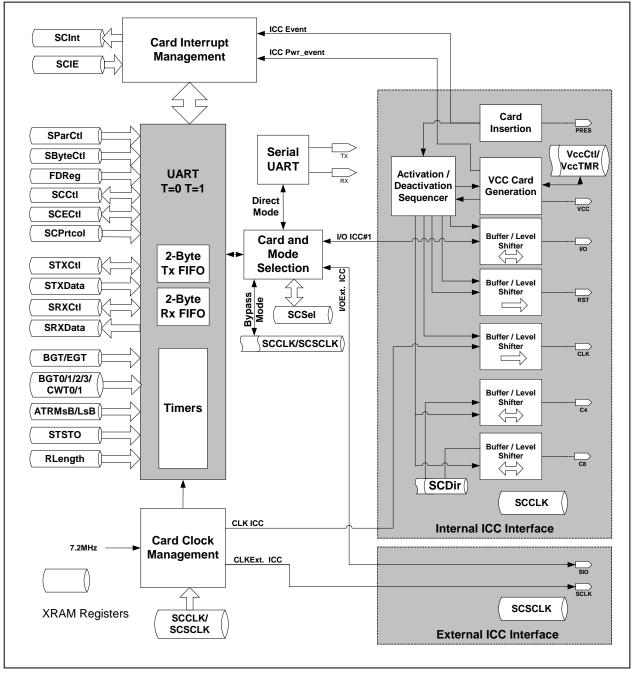

# 1.7.15 Smart Card Interface Function

The 73S1210F integrates one ISO-7816 (T=0, T=1) UART, one complete ICC electrical interface as well as an external smart card interface to allow multiple smart cards to be connected using the Teridian 8010 family of interface devices. Figure 14 shows the simplified block diagram of the card circuitry (UART + interfaces), with detail of dedicated XRAM registers.

Figure 14: Smart Card Interface Block Diagram

Card interrupts are managed through two dedicated registers: SCIE (Interrupt Enable to define which interrupt is enabled) and SCInt (Interrupt status). They allow the firmware to determine the source of an interrupt, that can be a card insertion / removal, card power fault, or a transmission (TX) or reception (RX) event / fault. It should be noted that even when card clock is disabled, an ICC interrupt can be generated

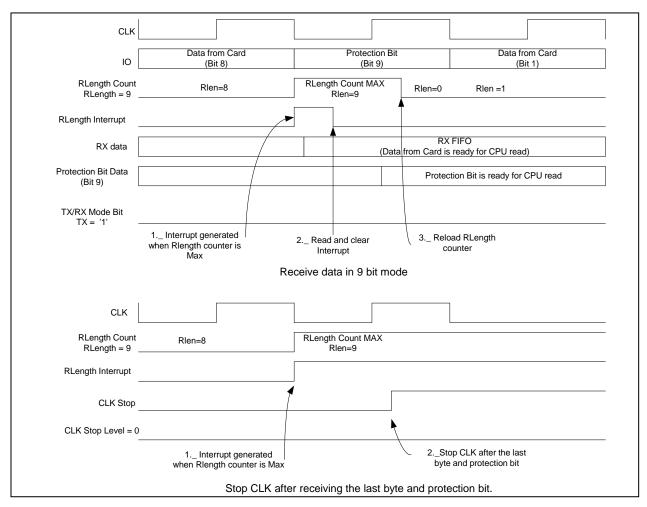

Figure 24: Operation of 9-bit Mode in Sync Mode

Synchronous card operation is broken down into three primary types. These are commonly referred to as 2-wire, 3-wire and I2C synchronous cards. Each card type requires different control and timing and therefore requires different algorithms to access. Teridian has created an application note to provide detailed algorithms for each card type. Refer to the application note titled "73S12xxF Synchronous Card Design Application Note".

#### STX Data Register (STXData): 0xFE07 ← 0x00

#### Table 79: The STXData Register

| MSB      |          |          |          |          |          |          | LSB      | , |

|----------|----------|----------|----------|----------|----------|----------|----------|---|

| STXDAT.7 | STXDAT.6 | STXDAT.5 | STXDAT.4 | STXDAT.3 | STXDAT.2 | STXDAT.1 | STXDAT.0 |   |

| Bit       | Function                                                                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STXData.7 |                                                                                                                                                                          |

| STXData.6 |                                                                                                                                                                          |

| STXData.5 |                                                                                                                                                                          |

| STXData.4 | the hardware and sent to the selected smart card. When the MPU reads this register, the byte pointer is changed to effectively "read out" the data. Thus, two reads will |

| STXData.3 | always result in an "empty" FIFO condition. The contents of the FIFO registers are not                                                                                   |

| STXData.2 | cleared, but will be overwritten by writes.                                                                                                                              |

| STXData.1 |                                                                                                                                                                          |

| STXData.0 |                                                                                                                                                                          |

# SRX Control/Status Register (SRXCtl): 0xFE08 ← 0x00

This register is used to monitor reception of data from the smart card.

#### Table 80: The SRXCtl Register

| MSB     |   |        |        |        |        |        | LSB     |

|---------|---|--------|--------|--------|--------|--------|---------|

| BIT9DAT | Ι | LASTRX | CRCERR | RXFULL | RXEMTY | RXOVRR | PARITYE |

| Bit      | Symbol  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRXCtl.7 | BIT9DAT | Bit 9 Data - When in sync mode and with MODE9/8B set, this bit will contain the data on IO (or SIO) pin that was sampled on the ninth CLK (or SCLK) rising edge. This is used to read data in synchronous 9-bit formats.                                                                                                                                                                                                                         |

| SRXCtl.6 | -       |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SRXCtl.5 | LASTRX  | Last RX Byte - User sets this bit during the reception of the last byte. When byte is received and this bit is set, logic checks CRC to match 0x1D0F (T=1 mode) or LRC to match 00h (T=1 mode), otherwise a CRC or LRC error is asserted.                                                                                                                                                                                                        |

| SRXCtl.4 | CRCERR  | (Read only) 1 = CRC (or LRC) error has been detected.                                                                                                                                                                                                                                                                                                                                                                                            |

| SRXCtl.3 | RXFULL  | (Read only) RX FIFO is full. Status bit to indicate RX FIFO is full.                                                                                                                                                                                                                                                                                                                                                                             |

| SRXCtl.2 | RXEMTY  | (Read only) RX FIFO is empty. This is only a status bit and does not generate an RX interrupt.                                                                                                                                                                                                                                                                                                                                                   |

| SRXCtl.1 | RXOVRR  | RX Overrun - (Read Only) Asserted when a receive-over-run condition has<br>occurred. An over-run is defined as a byte was received from the smart card<br>when the RX FIFO was full. Invalid data may be in the receive FIFO.<br>Firmware should take appropriate action. Cleared when read. Additional<br>writes to the RX FIFO are discarded when a RXOVRR occurs until the overrun<br>condition is cleared. Will generate an RXERR interrupt. |

| SRXCtl.0 | PARITYE | Parity Error - (Read only) 1 = The logic detected a parity error on incoming data from the smart card. Cleared when read. Will generate an RXERR interrupt.                                                                                                                                                                                                                                                                                      |

# Parity Control Register (SParCtl): 0xFE11 ← 0x00

This register provides the ability to configure the parity circuitry on the smart card interface. The settings apply to both integrated smart card interfaces.

#### Table 88: The SParCtl Register

| MSB |        |        |        |        |        |       | LSB    |   |

|-----|--------|--------|--------|--------|--------|-------|--------|---|

| _   | DISPAR | BRKGEN | BRKDET | RETRAN | DISCRX | INSPE | FORCPE | 1 |

| Bit       | Symbol | Function                                                                                                                                                                                                                                                                                   |

|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SParCtl.7 | -      |                                                                                                                                                                                                                                                                                            |

| SParCtl.6 | DISPAR | Disable Parity Check $-1$ = disabled, 0 = enabled. If enabled, the UART will check for even parity (the number of 1's including the parity bit is even) on every character. This also applies to the TS during ATR.                                                                        |

| SParCtl.5 | BRKGEN | Break Generation Disable $-1$ = disabled, 0 = enabled. If enabled, and T=0 protocol, the UART will generate a Break to the smart card if a parity error is detected on a receive character. No Break will be generated if parity checking is disabled. This also applies to TS during ATR. |

| SParCtl.4 | BRKDET | Break Detection Disable $-1$ = disabled, 0 = enabled. If enabled, and T=0 protocol, the UART will detect the generation of a Break by the smart card.                                                                                                                                      |

| SParCtl.3 | RETRAN | Retransmit Byte $-1$ = enabled, 0 = disabled. If enabled and a Break is detected from the smart card (Break Detection must be enabled), the last character will be transmitted again. This bit applies to T=0 protocol.                                                                    |

| SParCtl.2 | DISCRX | Discard Received Byte $-1$ = enabled, 0 = disabled. If enabled and a parity error is detected (Parity checking must be enabled), the last character received will be discarded. This bit applies to T=0 protocol.                                                                          |

| SParCtl.1 | INSPE  | Insert Parity Error $-1$ = enabled, 0 = disabled. Used for test purposes. If enabled, the UART will insert a parity error in every character transmitted by generating odd parity instead of even parity for the character.                                                                |

| SParCtl.0 | FORCPE | Force Parity Error $-1$ = enabled, 0 = disabled. Used for test purposes. If enabled, the UART will generate a parity error on a character received from the smart card.                                                                                                                    |

#### Byte Control Register (SByteCtl): 0xFE12 ← 0x2C

This register controls the processing of characters and the detection of the TS byte. When receiving, a Break is asserted at 10.5 ETU after the beginning of the start bit. Break from the card is sampled at 11 ETU.

# Table 89: The SByteCtl Register

| Ν | /ISB |       |       |          |          |   |   | LSB |  |

|---|------|-------|-------|----------|----------|---|---|-----|--|

|   | -    | DETTS | DIRTS | BRKDUR.1 | BRKDUR.0 | - | - | -   |  |

|   |      |       |       |          |          |   |   |     |  |

| Bit        | Symbol   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SByteCtl.7 | Ι        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SByteCtl.6 | DETTS    | Detect TS Byte – 1 = Next Byte is TS, 0 = Next byte is not TS. When set, the hardware will treat the next character received as the TS and determine if direct or indirect convention is being used. Direct convention is the default used if firmware does not set this bit prior to transmission of TS by the smart card to the firmware. The hardware will check parity and generate a break as defined by the DISPAR and BRKGEN bits in the parity control register. This bit is cleared by hardware after TS is received. TS is decoded prior to the FIFO and is stored in the receive FIFO. |

| SByteCtl.5 | DIRTS    | Direct Mode TS Select $-1$ = direct mode, 0 = indirect mode. Set/cleared by hardware when TS is processed indicating either direct/indirect mode of operation. When switching between smart cards, the firmware should write the bit appropriately since this register is not unique to an individual smart card (firmware should keep track of this bit).                                                                                                                                                                                                                                        |

| SByteCtl.4 | BRKDUR.1 | Break Duration Select $-00 = 1$ ETU, $01 = 1.5$ ETU, $10 = 2$ ETU,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SByteCtl.3 | BRKDUR.0 | 11 = reserved. Determines the length of a Break signal which is generated when detecting a parity error on a character reception in T=0 mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SByteCtl.2 | _        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SByteCtl.1 | _        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SByteCtl.0 | -        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## FD Control Register (FDReg): 0xFE13 ← 0x11

This register uses the transmission factors F and D to set the ETU (baud) rate. The values in this register are mapped to the ISO 7816 conversion factors as described below. The CLK signal for each interface is created by dividing a high-frequency, intermediate signal (MSCLK) by 2. The ETU baud rate is created by dividing MSCLK by 2 times the Fi/Di ratio specified by the codes below. For example, if FI = 0001 and DI = 0001, the ratio of Fi/Di is 372/1. Thus the ETU divider is configured to divide by 2 \* 372 = 744. The maximum supported F/D ratio is 4096.

#### Table 90: The FDReg Register

| MSB    |        |        |        |        |        |        | LSB    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FVAL.3 | FVAL.2 | FVAL.1 | FVAL.0 | DVAL.3 | DVAL.2 | DVAL.1 | DVAL.0 |

#### Table 91: The FDReg Bit Functions

| Bit     | Symbol | Function                                                                             |

|---------|--------|--------------------------------------------------------------------------------------|

| FDReg.7 | FVAL.3 | Refer to the Table 93 above. This value is converted per the table to                |

| FDReg.6 | FVAL.2 | set the divide ratio used to generate the baud rate (ETU). Default,                  |

| FDReg.5 | FVAL.1 | also used for ATR, is 0001 (Fi = 372). This value is used by the                     |

| FDReg.4 | FVAL.0 | selected interface.                                                                  |

| FDReg.3 | DVAL.3 |                                                                                      |

| FDReg.2 | DVAL.2 | Refer to Table 93 above. This value is used to set the divide ratio                  |

| FDReg.1 | DVAL.1 | used to generate the smart card CLK. Default, also used for ATR, is $0001$ (Di = 1). |

| FDReg.0 | DVAL.0 |                                                                                      |

#### Table 92: Divider Ratios Provided by the ETU Counter

|            |      |      | -    | r    |      | r    |       |       |

|------------|------|------|------|------|------|------|-------|-------|

| FI (code)  | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110  | 0111  |

| Fi (ratio) | 372  | 372  | 558  | 744  | 1116 | 1488 | 1860  | 1860⊕ |

| FCLK max   | 4    | 5    | 6    | 8    | 12   | 16   | 20    | 20⊕   |

|            |      |      |      | •    | •    | •    | •     |       |

| FI(code)   | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110  | 1111  |

| Fi(ratio)  | 512⊕ | 512  | 768  | 1024 | 1536 | 2048 | 2048⊕ | 2048⊕ |

| FCLK max   | 5⊕   | 5    | 7.5  | 10   | 15   | 20   | 20⊕   | 20⊕   |

|            |      |      |      |      |      |      |       |       |

| DI(code)   | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110  | 0111  |

| Di(ratio)  | 1⊕   | 1    | 2    | 4    | 8    | 16   | 32    | 32⊕   |

|            |      |      |      |      |      |      |       |       |

| DI(code)   | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110  | 1111  |

| Di(ratio)  | 12   | 20   | 16⊕  | 16⊕  | 16⊕  | 16⊕  | 16⊕   | 16⊕   |

|            |      |      | •    | •    | •    | •    | •     |       |

Note: values marked with  $\oplus$  are not included in the ISO definition and arbitrary values have been assigned.

The values given below are used by the ETU divider to create the ETU clock. The entries that are not shaded will result in precise CLK/ETU per ISO requirements. Shaded areas are not precise but are within 1% of the target value.

|      | Fi code | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 |

|------|---------|------|------|------|------|------|------|

| Di   | F→      | 372  | 372  | 558  | 744  | 1116 | 1488 |

| code | D↓      |      |      |      |      |      |      |

| 0001 | 1       | 744  | 744  | 1116 | 1488 | 2232 | 2976 |

| 0010 | 2       | 372  | 372  | 558  | 744  | 1116 | 1488 |

| 0011 | 4       | 186  | 186  | 279  | 372  | 558  | 744  |

| 0100 | 8       | 93   | 93   | 138  | 186  | 279  | 372  |

| 1000 | 12      | 62   | 62   | 93   | 124  | 186  | 248  |

| 0101 | 16      | 47   | 47   | 70   | 93   | 140  | 186  |

| 1001 | 20      | 37   | 37   | 56   | 74   | 112  | 149  |

| 0110 | 32      | 23   | 23   | 35   | 47   | 70   | 93   |

# Table 93: Divider Values for the ETU Clock

|      | Fi code         | 0110 | 1001 | 1010 | 1011 | 1100 | 1101 |

|------|-----------------|------|------|------|------|------|------|

| Di   | $F \rightarrow$ | 1860 | 512  | 768  | 1024 | 1536 | 2048 |

| code | D↓              |      |      |      |      |      |      |

| 0001 | 1               | 3720 | 1024 | 1536 | 2048 | 3072 | 4096 |

| 0010 | 2               | 1860 | 512  | 768  | 1024 | 1536 | 2048 |

| 0011 | 4               | 930  | 256  | 384  | 512  | 768  | 1024 |

| 0100 | 8               | 465  | 128  | 192  | 256  | 384  | 512  |

| 1000 | 12              | 310  | 85   | 128  | 171  | 256  | 341  |

| 0101 | 16              | 233  | 64   | 96   | 128  | 192  | 256  |

| 1001 | 20              | 186  | 51   | 77   | 102  | 154  | 205  |

| 0110 | 32              | 116  | 32   | 48   | 64   | 96   | 128  |

Shaded locations indicate functions that are not provided in the synchronous mode.

| Name     | Address | b7               | b6       | b5      | b4     | b3       | b2                  | b1      | b0      |

|----------|---------|------------------|----------|---------|--------|----------|---------------------|---------|---------|

| SCSel    | FE00    |                  |          |         |        | SelS     | C(1:0)              | BYPASS  |         |

| SCInt    | FE01    | WAITTO/<br>RLIEN | CRDEVT   | VCCTMR  | RXDAVI | TXEVNT   | TXSENT              | TXERR   | RXERR   |

| SCIE     | FE02    | WTOI/<br>RLIEN   | CDEVNT   | VTMREN  | RXDAEN | TXEVEN   | TXSNTEN             | TXERR   | RXERR   |

| VccCtl   | FE03    | VCCSEL.1         | VCCSEL.0 | VDDFLT  | RDYST  | VCCOK    |                     |         | SCPWRDN |

| VCCTmr   | FE04    |                  | OFFT     | MR(3:0) |        |          | VCCTI               | MR(3:0) |         |

| CRDCtl   | FE05    | DEBOUN           | CDETEN   |         |        | DETPOL   | PUENB               | PDEN    | CARDIN  |

| STXCtl   | FE06    | I2CMODE          |          | TXFULL  | TXEMTY | TXUNDR   | LASTTX              | TX/RXB  | BREAKD  |

| STXData  | FE07    |                  |          |         | TXDA   | TA(7:0)  |                     |         |         |

| SRXCtl   | FE08    | BIT9DAT          |          | LASTRX  | CRCERR | RXFULL   | RXEMTY              | RXOVRR  | PARITYE |

| SRXData  | FE09    |                  |          |         | RXDA   | TA(7:0)  |                     |         |         |

| SCCtl    | FE0A    | RSTCRD           |          | IO      | IOD    | C8       | C4                  | CLKLVL  | CLKOFF  |

| SCECtl   | FE0B    |                  |          | SIO     | SIOD   |          |                     | SCLKLVL | SCLKOFF |

| SCDIR    | FE0C    |                  |          |         |        | C8D      | C4D                 |         |         |

| SPrtcol  | FE0D    | SCISYN           | MOD9/8B  | SCESYN  | 0      | TMODE    | CRCEN               | CRCMS   | RCVATR  |

| SCCLK    | FE0F    |                  |          |         |        | ICLKF    | <sup>-</sup> S(5:0) |         |         |

| SCECLK   | FE10    |                  |          |         |        | ECLK     | FS(5:0)             |         |         |

| SParCtl  | FE11    |                  | DISPAR   | BRKGEN  | BRKDET | RTRAN    | DISCRX              | INSPE   | FORCPE  |

| SByteCtl | FE12    |                  | DETTS    | DIRTS   | BRKDL  | JR (1:0) |                     |         |         |

| FDReg    | FE13    |                  | FVA      | L(3:0)  |        |          | DVA                 | L (3:0) |         |

| CRCMsB   | FE14    |                  |          |         | CRC    | (15:8)   |                     |         |         |

| CRCLsB   | FE15    |                  |          |         | CRC    | C(7:0)   |                     |         |         |

| BGT      | FE16    | EGT8             |          |         |        |          | BG1                 | 「(4:0)  |         |

| EGT      | FE17    |                  |          |         | EGT    | (7:0)    |                     |         |         |

| BWTB3    | FE18    |                  |          |         |        |          | BWT                 | (27:24) |         |

| BWTB2    | FE19    |                  |          |         | ,      | 23:16)   |                     |         |         |

| BWTB1    | FE1A    |                  |          |         | BWT    | (15:8)   |                     |         |         |

| BWTB0    | FE1B    |                  |          |         | BWT    | (7:0)    |                     |         |         |

| CWTB1    | FE1C    |                  |          |         | CWT    | (15:8)   |                     |         |         |

| CWTB0    | FE1D    |                  |          |         | CWT    | (7:0)    |                     |         |         |

| ATRMsB   | FE1F    |                  |          |         | ATRT   | D(15:8)  |                     |         |         |

| ATRLsB   | FE20    |                  |          |         | ATRT   | O(7:0)   |                     |         |         |

| STSTO    | FE21    |                  |          |         | TSTO   | D(7:0)   |                     |         |         |

| RLength  | FE22    |                  |          |         | RLer   | n(7:0)   |                     |         |         |

# Table 107: Smart Card SFR Table

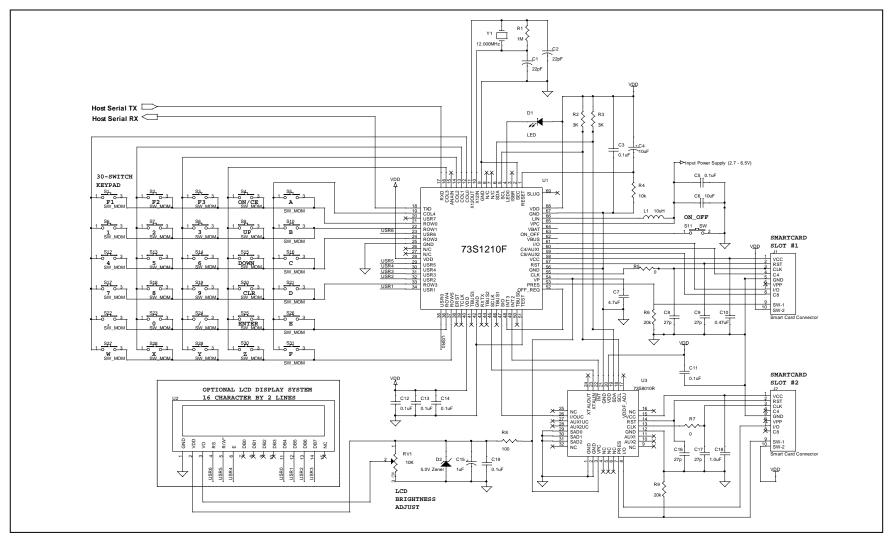

# 2 Typical Application Schematic

Figure 25: 73S1210F Typical Application Schematic

# 4 Equivalent Circuits

Figure 26: 12 MHz Oscillator Circuit

Figure 27: 32KHz Oscillator Circuit