# E · / Analog Devices Inc./Maxim Integrated - 73S1210F-68MR/F/PJ Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 80515                                                                  |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 24MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SmartCard, UART/USART                                |

| Peripherals                | LED, POR, WDT                                                          |

| Number of I/O              | 8                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6.5V                                                            |

| Data Converters            | ·                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 68-VFQFN Exposed Pad                                                   |

| Supplier Device Package    | 68-QFN (8x8)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/73s1210f-68mr-f-pj |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1    | Hard       | ware Description                                                                             | 8  |

|------|------------|----------------------------------------------------------------------------------------------|----|

|      | 1.1        | Pin Description                                                                              | 8  |

|      | 1.2        | Hardware Overview                                                                            |    |

|      | 1.3        | 80515 MPU Core                                                                               | 11 |

|      |            | 1.3.1 80515 Overview                                                                         | 11 |

|      |            | 1.3.2 Memory Organization                                                                    |    |

|      | 1.4        | Program Security                                                                             |    |

|      | 1.5        | Special Function Registers (SFRs)                                                            |    |

|      |            | 1.5.1 Internal Data Special Function Registers (SFRs)                                        |    |

|      |            | 1.5.2 IRAM Special Function Registers (Generic 80515 SFRs)                                   |    |

|      |            | 1.5.3 External Data Special Function Registers (SFRs)                                        |    |

|      | 1.6        | Instruction Set                                                                              |    |

|      | 1.7        | Peripheral Descriptions                                                                      |    |

|      |            | 1.7.1 Oscillator and Clock Generation                                                        |    |

|      |            | 1.7.2 Power Supply Management                                                                |    |

|      |            | 1.7.3 Power ON/OFF                                                                           |    |

|      |            | 1.7.4 Power Control Modes                                                                    |    |

|      |            | 1.7.5 Interrupts                                                                             |    |

|      |            | 1.7.6 UART                                                                                   |    |

|      |            | <ul><li>1.7.7 Timers and Counters</li><li>1.7.8 WD Timer (Software Watchdog Timer)</li></ul> |    |

|      |            | 1.7.9 User (USR) Ports                                                                       |    |

|      |            | 1.7.9 Oser (OSIC) Fors                                                                       |    |

|      |            | 1.7.10 Analog Voltage Comparator                                                             |    |

|      |            | 1.7.12 I <sup>2</sup> C Master Interface                                                     |    |

|      |            | 1.7.13 Keypad Interface                                                                      |    |

|      |            | 1.7.14 Emulator Port                                                                         |    |

|      |            | 1.7.15 Smart Card Interface Function                                                         |    |

|      |            | 1.7.16 VDD Fault Detect Function                                                             |    |

| 2    | Typic      | cal Application Schematic1                                                                   | 04 |

|      |            |                                                                                              |    |

| 3    |            | rical Specification1                                                                         |    |

|      | 3.1        | Absolute Maximum Ratings1                                                                    |    |

|      | 3.2        | Recommended Operating Conditions                                                             |    |

|      | 3.3        | Digital IO Characteristics                                                                   |    |

|      | 3.4        | Oscillator Interface Requirements                                                            |    |

|      | 3.5        | DC Characteristics: Analog Input                                                             |    |

|      | 3.6        | Smart Card Interface Requirements                                                            |    |

|      | 3.7        | DC Characteristics                                                                           |    |

|      | 3.8        | Current Fault Detection Circuits1                                                            |    |

| 4    | Equi       | valent Circuits1                                                                             | 12 |

| 5    | Pack       | age Pin Designation1                                                                         | 20 |

|      | 5.1        | 68-pin QFN Pinout                                                                            |    |

|      | 5.2        | 44-pin QFN Pinout                                                                            |    |

| 6    |            | aging Information1                                                                           |    |

| 0    |            |                                                                                              |    |

|      | 6.1<br>6.2 | 68-Pin QFN Package Outline                                                                   |    |

|      | -          | 44-Pin QFN Package Outline1                                                                  |    |

| 7    | Orde       | ring Information1                                                                            | 24 |

| 8    | Relat      | ed Documentation1                                                                            | 24 |

| 9    | Cont       | act Information1                                                                             | 24 |

| Revi | ision      | History1                                                                                     | 25 |

| Register | SFR<br>Address | R/W | Description                                                                                                                                                                                                                                              |  |  |  |  |  |

|----------|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ERASE    | 0x94           | W   | This register is used to initiate either the Flash Mass Erase cycle or the Flash Page Erase cycle. Specific patterns are expected for ERASE in order to initiate the appropriate Erase cycle (default = 0x00).                                           |  |  |  |  |  |

|          |                |     | <ul> <li>0x55 – Initiate Flash Page Erase cycle. Must be proceeded by a write to PGADDR @ SFR 0xB7.</li> <li>0xAA – Initiate Flash Mass Erase cycle. Must be proceeded by a write to FLSH_MEEN @ SFR 0xB2 and the debug port must be enabled.</li> </ul> |  |  |  |  |  |

|          |                |     | Any other pattern written to ERASE will have no effect.                                                                                                                                                                                                  |  |  |  |  |  |

| PGADDR   | 0xB7           | R/W | Flash Page Erase Address register containing the flash memory page address (page 0 through 127) that will be erased during the Page Erase cycle (default = $0x00$ ). Note: the page address is shifted left by one bit (see detailed description above). |  |  |  |  |  |

|          |                |     | Must be re-written for each new Page Erase cycle.                                                                                                                                                                                                        |  |  |  |  |  |

| FLSHCTL  | 0xB2           | R/W | Bit 0 (FLSH_PWE): Program Write Enable:                                                                                                                                                                                                                  |  |  |  |  |  |

|          |                |     | 0 – MOVX commands refer to XRAM Space, normal operation (default).<br>1 – MOVX @DPTR,A moves A to Program Space (Flash) @ DPTR.                                                                                                                          |  |  |  |  |  |

|          |                |     | This bit is automatically reset after each byte written to flash. Writes to this bit are inhibited when interrupts are enabled.                                                                                                                          |  |  |  |  |  |

|          |                | W   | Bit 1 (FLSH_MEEN): Mass Erase Enable:                                                                                                                                                                                                                    |  |  |  |  |  |

|          |                |     | 0 – Mass Erase disabled (default).<br>1 – Mass Erase enabled.                                                                                                                                                                                            |  |  |  |  |  |

|          |                |     | Must be re-written for each new Mass Erase cycle.                                                                                                                                                                                                        |  |  |  |  |  |

|          |                | R/W | Bit 6 (SECURE):<br>Enables security provisions that prevent external reading of flash<br>memory and CE program RAM. This bit is reset on chip reset and may<br>only be set. Attempts to write zero are ignored.                                          |  |  |  |  |  |

| Table 3: Flas | n Special Function | n Registers |

|---------------|--------------------|-------------|

|---------------|--------------------|-------------|

**Internal Data Memory:** The Internal data memory provides 256 bytes (0x00 to 0xFF) of data memory. The internal data memory address is always one byte wide and can be accessed by either direct or indirect addressing. The Special Function Registers occupy the upper 128 bytes. This SFR area is available only by direct addressing. Indirect addressing accesses the upper 128 bytes of Internal RAM.

The lower 128 bytes contain working registers and bit-addressable memory. The lower 32 bytes form four banks of eight registers (R0-R7). Two bits on the program memory status word (PSW) select which bank is in use. The next 16 bytes form a block of bit-addressable memory space at bit addresses 0x00-0x7F. All of the bytes in the lower 128 bytes are accessible through direct or indirect addressing. Table 4 shows the internal data memory map.

| Address | Direct Addressing Indirect Addressing |     |  |  |  |

|---------|---------------------------------------|-----|--|--|--|

| 0xFF    | Special Function                      | RAM |  |  |  |

| 0x80    | Registers (SFRs)                      | RAM |  |  |  |

| 0x7F    |                                       |     |  |  |  |

| 0x30    | Byte-addressable area                 |     |  |  |  |

| 0x2F    | Dute er hit eddressehle e             |     |  |  |  |

| 0x20    | Byte or bit-addressable area          |     |  |  |  |

| 0x1F    | Register banks R0…R7 (x4)             |     |  |  |  |

| 0x00    |                                       |     |  |  |  |

## Table 4: Internal Data Memory Map

**External Data Memory:** While the 80515 can address up to 64KB of external data memory in the space from 0x0000 to 0xFFFF, only the memory ranges shown in Figure 2 contain physical memory. The 80515 writes into external data memory when the MPU executes a MOVX @Ri,A or MOVX @DPTR,A instruction. The MPU reads external data memory by executing a MOVX A,@Ri or MOVX A,@DPTR instruction.

There are two types of instructions, differing in whether they provide an eight-bit or sixteen-bit indirect address to the external data RAM.

In the first type (MOVX A,@Ri), the contents of R0 or R1, in the current register bank, provide the eight lower-ordered bits of address. This method allows the user access to the first 256 bytes of the 2KB of external data RAM. In the second type of MOVX instruction (MOVX A,@DPTR), the data pointer generates a sixteen-bit address.

## • Mode 3

The only difference between Mode 2 and Mode 3 is that in Mode 3 either internal baud rate generator or timer 1 can be use to specify baud rate.

The SOBUF register is used to read/write data to/from the serial 0 interface.

### Serial Interface 0 Control Register (S0CON): 0x9B ← 0x00

Transmit and receive data are transferred via this register.

#### Table 38: The S0CON Register

| MSB |     |      |      |      |      |     |     |  |

|-----|-----|------|------|------|------|-----|-----|--|

| SM0 | SM1 | SM20 | REN0 | TB80 | RB80 | TI0 | RI0 |  |

| Bit     | Symbol | Function                                                                                                                                                      |                                          |               |               |                                    |  |  |  |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------|---------------|------------------------------------|--|--|--|

| S0CON.7 | SM0    | These two bi                                                                                                                                                  | These two bits set the UART0 mode:       |               |               |                                    |  |  |  |

|         |        | Mode                                                                                                                                                          | Description                              | SM0           | SM1           |                                    |  |  |  |

|         |        | 0                                                                                                                                                             | N/A                                      | 0             | 0             |                                    |  |  |  |

| S0CON.6 | SM1    | 1                                                                                                                                                             | 8-bit UART                               | 0             | 1             |                                    |  |  |  |

|         |        | 2                                                                                                                                                             | 9-bit UART                               | 1             | 0             |                                    |  |  |  |

|         |        | 3                                                                                                                                                             | 9-bit UART                               | 1             | 1             |                                    |  |  |  |

| S0CON.5 | SM20   | Enables the                                                                                                                                                   | inter-processor c                        | ommunicatio   | n feature.    |                                    |  |  |  |

| S0CON.4 | REN0   | If set, enable                                                                                                                                                | es serial receptior                      | n. Cleared by | / software to | disable reception.                 |  |  |  |

| S0CON.3 | TB80   |                                                                                                                                                               | n the function it p                      |               |               | leared by the MPU,<br>ltiprocessor |  |  |  |

| S0CON.2 | RB80   | In Modes 2 and 3 it is the 9th data bit received. In Mode 1, if SM20 is 0, RB80 is the stop bit. In Mode 0 this bit is not used. Must be cleared by software. |                                          |               |               |                                    |  |  |  |

| S0CON.1 | TI0    | Transmit interrupt flag, set by hardware after completion of a serial transfer.<br>Must be cleared by software.                                               |                                          |               |               |                                    |  |  |  |

| S0CON.0 | RI0    |                                                                                                                                                               | rrupt flag, set by<br>lust be cleared by |               | er completion | of a serial                        |  |  |  |

## Mode 0

Putting either timer/counter into mode 0 configures it as an 8-bit timer/counter with a divide-by-32 prescaler. In this mode, the timer register is configured as a 13-bit register. As the count rolls over from all 1's to all 0's, it sets the timer overflow flag TF0. The overflow flag TF0 then can be used to request an interrupt. The counted input is enabled to the timer when TRx = 1 and either GATE = 0 or TX = 1 (setting GATE = 1 allows the timer to be controlled by external input TX, to facilitate pulse width measurements). TRx are control bits in the special function register TCON; GATE is in TMOD. The 13-bit register consists of all 8 bits of TH1 and the lower 5 bits of TL0. The upper 3 bits of TL0 are indeterminate and should be ignored. Setting the run flag (TRx) does not clear the registers. Mode 0 operation is the same for timer 0 as for timer 1.

## Mode 1

Mode 1 is the same as mode 0, except that the timer register is run with all 16 bits.

### Mode 2

Mode 2 configures the timer register as an 8-bit counter (TLx) with automatic reload. The overflow from TLx not only sets TFx, but also reloads TLx with the contents of THx, which is preset by software. The reload leaves THx unchanged.

### Mode 3

Mode 3 has different effects on timer 0 and timer 1. Timer 1 in mode 3 simply holds its count. The effect is the same as setting TR1 = 0. Timer 0 in mode 3 establishes TL0 and TH0 as two separate counters. TL0 uses the timer 0 control bits: C/T, GATE, TR0, INT0, and TF0. TH0 is locked into a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from timer 1. Thus, TH0 now controls the "timer 1" interrupt. Mode 3 is provided for applications requiring an extra 8-bit timer or counter. When timer 0 is in mode 3, timer 1 can be turned on and off by switching it out of and into its own mode 3, or can still be used by the serial channel as a baud rate generator, or in fact, in any application not requiring an interrupt from timer 1 itself.

## Timer/Counter Control Register (TCON): 0x88 ← 0x00

| MSB |     |     |     |     |     |     | LSB |  |

|-----|-----|-----|-----|-----|-----|-----|-----|--|

| TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |  |

Table 42: The TCON Register

| Bit    | Symbol | Function                                                                                                                                       |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| TCON.7 | TF1    | Timer 1 overflow flag.                                                                                                                         |

| TCON.6 | TR1    | Not used for interrupt control.                                                                                                                |

| TCON.5 | TF0    | Timer 0 overflow flag.                                                                                                                         |

| TCON.4 | TR0    | Not used for interrupt control.                                                                                                                |

| TCON.3 | IE1    | Interrupt 1 edge flag is set by hardware when the falling edge on external interrupt int1 is observed. Cleared when an interrupt is processed. |

| TCON.2 | IT1    | Interrupt 1 type control bit. 1 selects falling edge and 0 selects low level for input pin to cause an interrupt.                              |

| TCON.1 | IE0    | Interrupt 0 edge flag is set by hardware when the falling edge on external interrupt int0 is observed. Cleared when an interrupt is processed. |

| TCON.0 | IT0    | Interrupt 0 type control bit. 1 selects falling edge and 0 sets low level for input pin to cause interrupt.                                    |

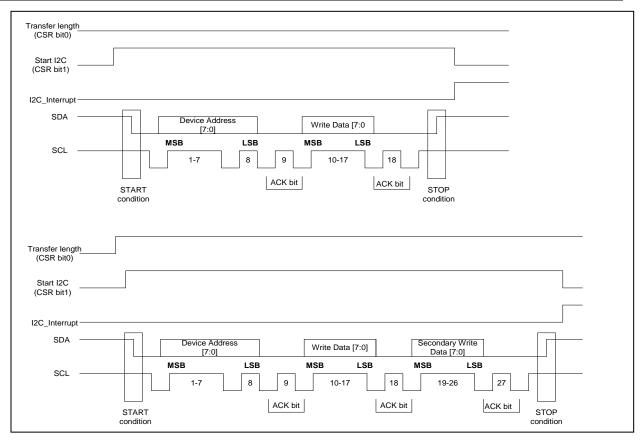

Figure 10: I<sup>2</sup>C Write Mode Operation

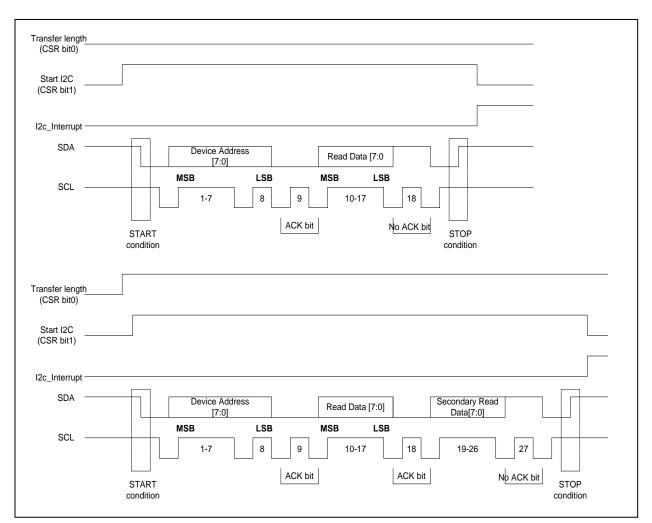

### 1.7.12.2 I<sup>2</sup>C Read Sequence

To read data on the I<sup>2</sup>C Master Bus from a slave device, the 80515 has to program the following registers in this sequence:

- 1. Write slave device address to Device Address register (DAR). The data contains 7 bits device address and 1 bit of op-code. The op-code bit should be written with a 1.

- Write control data to Control and Status register. Write a 1 to bit 1 to start I<sup>2</sup>C Master Bus. Also write a 1 to bit 0 if the Secondary Read Data register (SRDR) is to be captured from the I<sup>2</sup>C Slave device.

- 3. Wait for I<sup>2</sup>C interrupt to be asserted. It indicates that the read operation on the I<sup>2</sup>C bus is done. Refer to information about the INT6Ctl, IEN1 and IRCON registers for masking and flag operation.

- 4. Read data from the Read Data register (RDR).

- 5. Read data from Secondary Read Data register (SRDR) if bit 0 of Control and Status register (CSR) is written with a 1.

Figure 11 shows the timing of the  $I^2C$  read mode:

Figure 11: I<sup>2</sup>C Read Operation

written into the KCOL and KROW registers. The keypad interface uses a 1kHz clock derived from the 12MHz crystal. The clock is enabled by setting bit 6 – KBEN – in the MCLKCtl register (see the Oscillator and Clock Generation section) to carry out scanning and debouncing. The keypad size can be adjusted within the KSIZE register.

Normal scanning is performed by hardware when the SCNEN bit is set at 1 in the KSTAT register. Figure 13 shows the flowchart of how the hardware scanning operates. In order to minimize power, scanning does not occur until a key-press is detected. Once hardware key scanning is enabled, the hardware drives all column outputs low and waits for a low to be detected on one of the inputs. When a low is detected on any row, and before key scanning starts, the hardware checks that the low level is still detected after a debounce time. The debounce time is defined by firmware in the KSCAN register (bits 7:0, DBTIME). Debounce times from 4ms to 256ms in 4ms increments are supported. If a key is not pressed after the debounce time, the hardware will go back to looking for any input to be low. If a key is confirmed to be pressed, key scanning begins.

Key scanning asserts one of the 5 drive lines (COL 4:0) low and looks for a low on a sense line indicating that a key is pressed at the intersection of the drive/sense line in the keypad. After all sense lines have been checked without a key-press being detected, the next column line is asserted. The time between checking each sense line is the scan time and is defined by firmware in the KSCAN register (bits 0:1 – SCTIME). Scan times from 1ms to 4ms are supported. Scanning order does not affect the scan time. This scanning continues until the entire keypad is scanned. If only one key is pressed, a valid key is detected. Simultaneous key presses are not considered as valid (If two keys are pressed, no key is reported to firmware).

Possible scrambling of the column scan order is provided by means of the KORDERL and KORDERH registers that define the order of column scanning. Values in these registers must be updated every time a new keyboard scan order is desired. It is not possible to change the order of scanning the sense lines. The column and row intersection for the detected valid key are stored in the KCOL and KROW registers. When a valid key is detected, an interrupt is generated. Firmware can then read those registers to determine which key had been pressed. After reading the KCOL and KROW registers, the firmware can update the KORDERL / KORDERH registers if a new scan order is needed. When the SCNEN bit is enabled in the KSTAT register, the KCOL and KROW registers are only updated after a valid key has been identified. The hardware does not wait for the firmware to service the interrupt in order to proceed with the key scanning process. Once the valid key (or invalid key – e.g. two keys pressed) is detected, the hardware waits for the key to be released. Once the key is released, the debounce timer is started. If the key is not still released after the debounce time, the debounce counter starts again. After a key release, all columns will be driven low as before and the process will repeat waiting for any key to be pressed. When the SCNEN bit is disabled, all drive outputs are set to the value in the KCOL register. If firmware clears the SCNEN bit in the middle of a key scan, the KCOL register contains the last value stored in there which will then be reflected on the output pins. A bypass mode is provided so that the firmware can do the key scanning manually (SCNEN bit must be cleared). In bypass mode, the firmware writes/reads the Column and Row registers to perform the key scanning.

on a card insertion / removal to allow power saving modes. Card insertion / removal is generated from the respective card switch detection inputs (whose polarity is programmable).

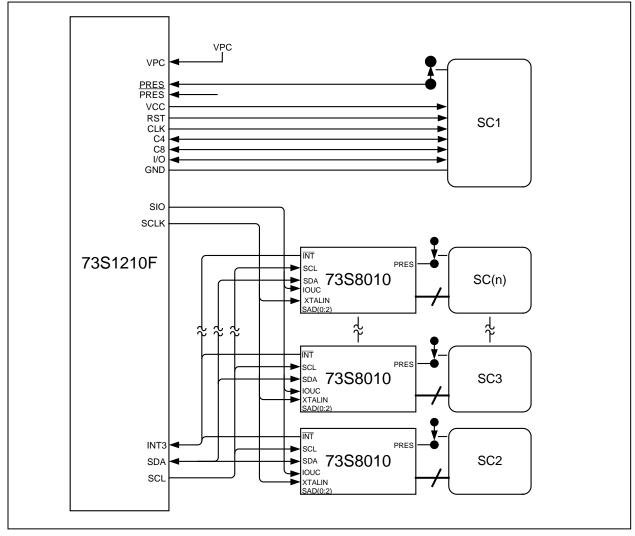

The built-in ICC Interface has a linear regulator ( $V_{CC}$  generator) capable of driving 1.8, 3.0 and 5.0V smart cards in accordance with the ISO 7816-3 and EMV4.1 standards. This converter uses the  $V_P$  (5.5V nominal) input supply source. See the power supply management section above for more detail. Auxiliary I/O lines C4 and C8 are only provided for the built-in interface. If support for the auxiliary lines is necessary for the external smart card interface, they need to be handled manually through the USR GPIO pins. The external 73S8010x devices directly connect the I/O (SIO) and clock (SCLK) signals and control is handled via the I<sup>2</sup>C interface.

Figure 15 shows how multiple 8010 devices can be connected to the 73S1210F.

Figure 15: External Smart Card Interface Block Diagram

## Special Notes Regarding Synchronous Mode Operation

When the SCISYN or SCESNC bits (SPrtcol, bit 7, bit 5, respectively) are set, the selected smart card interface operates in synchronous mode and there are changes in the definition and behavior of pertinent register bits and associated circuitry. The following requirements are to be noted:

- 1. The source for the smart card clock (CLK or SCLK) is the ETU counter. Only the actively selected interface can have a running synchronous clock. In contrast, an unselected interface may have a running clock in the asynchronous mode of operation.

- 2. The control bits CLKLVL, SCLKLVL, CLKOFF, and SCLKOFF are functional in synchronous mode. When the CLKOFF bit is set, it will not truncate either the logic low or logic high period when the (stop at) level is of opposite polarity. The CLK/SCLK signal will complete a correct logic low or logic high duty cycle before stopping at the selected level. The CLK "start" is a result of the falling edge of the CLKOFF bit. Setting clock to run when it is stopped low will result in a half period of low before going high. Setting clock to run when it is stopped high will result in the clock going low immediately and then running at the selected rate with 50% duty cycle (within the limitations of the ETU divisor value).

- 3. The Rlen(7:0) is configured to count the falling edges of the ETU clock (CLK or SCLK) after it has been loaded with a value from 1 to 255. A value of 0 disables the counting function and RLen functions such as I/O source selection (I/O signal bypasses the FIFOs and is controlled by the SCCLK/SCECLK SFRs). When the RLen counter reaches the "max" (loaded) value, it sets the WAITTO interrupt (SCInt, bit 7), which is maskable via WTOIEN (SCIE, bit 7). It must be reloaded in order to start the counting/clocking process again. This allows the processor to select the number of CLK cycles and hence, the number of bits to be read or written to/from the card.

- 4. The FIFO is not clocked by the first CLK (falling) edge resulting from a CLKOFF de-assertion (a clock start event) when the CLK was stopped in the high state and RLen has been loaded but not yet clocked.

- 5. The state of the pin IO or SIO is sampled on the rising edge of CLK/SCLK and stored in bit 5 of the SCCtl/SCECtl register.

- When Rlen = max or 0 and I2CMODE= 1 (STXCtl, b7), the IO or SIO signal is directly controlled by the data and direction bits in the respective SCCtl and SCECtl register. The state of the data in the TX FIFO is bypassed.

- In the SPrtcol register, bit 6 (MODE9/8B) becomes active. When set, the RXData FIFO will read nine-bit words with the state of the ninth bit being readable in SRXCtl, bit 7 (B9DAT). The RXDAV interrupt will occur when the ninth bit has been clocked in (rising edge of CLK or SCLK).

- 8. Care must be taken to clear the RX and TX FIFOs at the start of any transaction. The user shall read the RX FIFO until it indicates empty status. Reading the TX FIFO twice will reset the input byte pointer and the next write to the TX FIFO will load the byte to the "first out" position. Note that the bit pointer (serializer/deserializer) is reset to bit 0 on any change of the TX/RXD bit.

Special bits that are only active for sync mode include: SRXCtl, b7 "BIT9DAT", SPrtcol, b6 "MODE9/8B", STXCtl, b7 "I2CMODE", and the definition of SCInt, b7, which was "WAITTO", becomes RLenINT interrupt, and SCIE, b7, which was "WTOIEN", becomes RLenIEN.

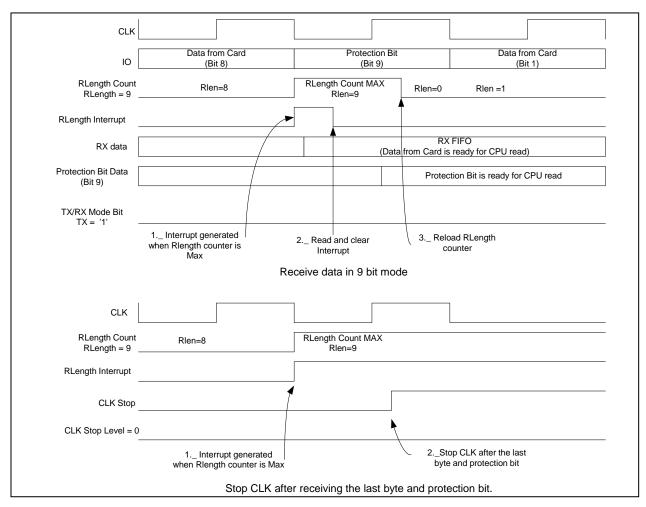

Figure 24: Operation of 9-bit Mode in Sync Mode

Synchronous card operation is broken down into three primary types. These are commonly referred to as 2-wire, 3-wire and I2C synchronous cards. Each card type requires different control and timing and therefore requires different algorithms to access. Teridian has created an application note to provide detailed algorithms for each card type. Refer to the application note titled "73S12xxF Synchronous Card Design Application Note".

1400

## Smart Card V<sub>cc</sub> Control/Status Register (VccCtl): 0xFE03 ← 0x00

This register is used to control the power up and power down of the integrated smart card interface. It is used to determine whether to apply 5V, 3V, or 1.8 to the smart card. Perform the voltage selection with one write operation, setting both VCCSEL.1 and VCCSEL.0 bits simultaneously. The VDDFLT bit (if enabled) will provide an emergency deactivation of the internal smart card slot. See the VDD Fault Detect Function section for more detail.

## Table 75: The VccCtl Register

| VCCSEL.1 | VCCSEL.0 | VDDFLT | RDYST | VCCOK | - | - | SCPWRDN |

|----------|----------|--------|-------|-------|---|---|---------|

| Bit      | Symbol   | Function                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|          |          | Setting non-zero value for bits 7,6 will begin activation sequence with target Vcc as given below:                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| VccCtl.7 | VCCSEL.1 | State         VCCSEL.1         VCCSEL.0         VCC           1         0         0         0V           2         0         1         1.8V                                                                                                                                                                                                                                                 |  |  |  |  |  |

|          |          | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| VccCtl.6 | VCCSEL.0 | A card event or VCCOK going low will initiate a deactivation sequence.<br>When the deactivation sequence for RST, CLK and I/O is complete, $V_{CC}$ will<br>be turned off. When this type of deactivation occurs, the bits must be reset<br>before initiating another activation.                                                                                                           |  |  |  |  |  |

| VccCtl.5 | VDDFLT   | When there is a VDD Fault event, this bit will be set = 0. This causes VCCSEL.1 and VCCSEL.0 bits to be immediately set = 0 to begin deactivation.                                                                                                                                                                                                                                          |  |  |  |  |  |

| VccCtl.4 | RDYST    | If this bit is set = 1, the activation sequence will start when bit VCCOK is set = 1. If not set, the deactivation sequence shall start when the VCCTMR times out.                                                                                                                                                                                                                          |  |  |  |  |  |

| VccCtl.3 | VCCOK    | (Read only). Indicates that $V_{CC}$ output voltage is stable.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| VccCtl.2 | _        |                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| VccCtl.1 | _        |                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| VccCtl.0 | SCPWRDN  | This bit controls the power-off mode of the 73S1210F circuit.<br>1 = power off, 0 = normal operation. When in power down mode,<br>$V_{DD} = 0V$ . $V_{DD}$ can only be turned on by pressing the ON/OFF switch or by<br>application of 5V to $V_{BUS}$ . If $V_{BUS}$ power is available and SCPWRDN bit is set,<br>it has no effect until $V_{BUS}$ is removed and $V_{DD}$ will shut off. |  |  |  |  |  |

## TX Control/Status Register (STXCtl): 0xFE06 ← 0x00

This register is used to control transmission of data to the smart card. Some control and some status bits are in this register.

## Table 78: The STXCtl Register

| MSB     |   |        |        |        |        |        | LSB    |

|---------|---|--------|--------|--------|--------|--------|--------|

| I2CMODE | - | TXFULL | TXEMTY | TXUNDR | LASTTX | TX/RXB | BREAKD |

| Bit      | Symbol  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STXCtl.7 | I2CMODE | I2C Mode - When in sync mode and this bit is set, and when the RLen count value = max or 0, the source of the smart card data for IO pin (or SIO pin) will be connected to the IO bit in SCCtl (or SCECtl) register rather than the TX FIFO. See the description for the Protocol Mode Register for more detail.                                                                                                                                                                             |

| STXCtl.6 | -       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| STXCtl.5 | TXFULL  | TX FIFO is full. Additional writes may corrupt the contents of the FIFO. This bit it will remain set as long as the TX FIFO is full. Generates a TX_Event interrupt upon going full.                                                                                                                                                                                                                                                                                                         |

| STXCtl.4 | TXEMTY  | 1 = TX FIFO is empty, 0 = TX FIFO is not empty. If there is data in the TX FIFO, the circuit will transmit it to the smart card if in transmit mode. In T=1 mode, if the LASTTX bit is set and the hardware is configured to transmit the CRC/LRC, the TXEMTY will not be set until the CRC/LRC is transmitted. In T=0, if the LASTTX bit is set, TXEMTY will be set after the last word has been successfully transmitted to the smart card. Generates a TXEVNT interrupt upon going empty. |

| STXCtl.3 | TXUNDR  | TX Underrrun - (Read only) Asserted when a transmit under-run condition<br>has occurred. An under-run condition is defined as an empty TX FIFO when<br>the last data word has been successfully transmitted to the smart card and<br>the LASTTX bit was not set. No special processing is performed by the<br>hardware if this condition occurs. Cleared when read by firmware. This bit<br>generates a TXERR interrupt.                                                                     |

| STXCtl.2 | LASTTX  | Last TX Byte - Set by firmware (in both T=0 and T=1) when the last byte in the current message has been written into the transmit FIFO. In T=1 mode, the CRC/LRC will be appended to the message. Should be set after the last byte has been written into the transmit FIFO. Should be cleared by firmware before writing first byte of next message into the transmit FIFO. Used in T=0 to determine when to set TXEMTY.                                                                    |

| STXCtl.1 | TX/RXB  | 1 = Transmit mode, 0 = Receive mode. Configures the hardware to be receiving from or transmitting to the smart card. Determines which counters should be enabled. This bit should be set to receive mode prior to switching to another interface. Setting and resetting this bit shall initialize the CRC logic. If LASTTX is set, this bit can be reset to RX mode and UART logic will automatically change mode to RX when TX operation is completed (TX_Empty = 1).                       |

| STXCtl.0 | BREAKD  | Break Detected - (Read only) 1 = A break has been detected on the I/O line indicating that the smart card detected a parity error. Cleared when read. This bit generates a TXERR interrupt.                                                                                                                                                                                                                                                                                                  |

## STX Data Register (STXData): 0xFE07 ← 0x00

#### Table 79: The STXData Register

| MSB      |          |          |          |          |          |          | LSB      | , |

|----------|----------|----------|----------|----------|----------|----------|----------|---|

| STXDAT.7 | STXDAT.6 | STXDAT.5 | STXDAT.4 | STXDAT.3 | STXDAT.2 | STXDAT.1 | STXDAT.0 |   |

| Bit       | Function                                                                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STXData.7 |                                                                                                                                                                          |

| STXData.6 |                                                                                                                                                                          |

| STXData.5 | Data to be transmitted to smart card. Gets stored in the TX FIFO and then extracted by                                                                                   |

| STXData.4 | the hardware and sent to the selected smart card. When the MPU reads this register, the byte pointer is changed to effectively "read out" the data. Thus, two reads will |

| STXData.3 | always result in an "empty" FIFO condition. The contents of the FIFO registers are not                                                                                   |

| STXData.2 | cleared, but will be overwritten by writes.                                                                                                                              |

| STXData.1 |                                                                                                                                                                          |

| STXData.0 |                                                                                                                                                                          |

## SRX Control/Status Register (SRXCtl): 0xFE08 ← 0x00

This register is used to monitor reception of data from the smart card.

## Table 80: The SRXCtl Register

| MSB     |   |        |        |        |        |        | LSB     |

|---------|---|--------|--------|--------|--------|--------|---------|

| BIT9DAT | Ι | LASTRX | CRCERR | RXFULL | RXEMTY | RXOVRR | PARITYE |

| Bit      | Symbol  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRXCtl.7 | BIT9DAT | Bit 9 Data - When in sync mode and with MODE9/8B set, this bit will contain the data on IO (or SIO) pin that was sampled on the ninth CLK (or SCLK) rising edge. This is used to read data in synchronous 9-bit formats.                                                                                                                                                                                                                         |

| SRXCtl.6 | -       |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SRXCtl.5 | LASTRX  | Last RX Byte - User sets this bit during the reception of the last byte. When byte is received and this bit is set, logic checks CRC to match 0x1D0F (T=1 mode) or LRC to match 00h (T=1 mode), otherwise a CRC or LRC error is asserted.                                                                                                                                                                                                        |

| SRXCtl.4 | CRCERR  | (Read only) 1 = CRC (or LRC) error has been detected.                                                                                                                                                                                                                                                                                                                                                                                            |

| SRXCtl.3 | RXFULL  | (Read only) RX FIFO is full. Status bit to indicate RX FIFO is full.                                                                                                                                                                                                                                                                                                                                                                             |

| SRXCtl.2 | RXEMTY  | (Read only) RX FIFO is empty. This is only a status bit and does not generate an RX interrupt.                                                                                                                                                                                                                                                                                                                                                   |

| SRXCtl.1 | RXOVRR  | RX Overrun - (Read Only) Asserted when a receive-over-run condition has<br>occurred. An over-run is defined as a byte was received from the smart card<br>when the RX FIFO was full. Invalid data may be in the receive FIFO.<br>Firmware should take appropriate action. Cleared when read. Additional<br>writes to the RX FIFO are discarded when a RXOVRR occurs until the overrun<br>condition is cleared. Will generate an RXERR interrupt. |

| SRXCtl.0 | PARITYE | Parity Error - (Read only) 1 = The logic detected a parity error on incoming data from the smart card. Cleared when read. Will generate an RXERR interrupt.                                                                                                                                                                                                                                                                                      |

LSB

## SRX Data Register (SRXData): 0xFE09 ← 0x00

## Table 81: The SRXData Register

## MSB

SRXDAT.7 SRXDAT.6 SRXDAT.5 SRXDAT.4 SRXDAT.3 SRXDAT.2 SRXDAT.1 SRXDAT.0

| Bit       | Function                                                                    |

|-----------|-----------------------------------------------------------------------------|

| SRXData.7 |                                                                             |

| SRXData.6 |                                                                             |

| SRXData.5 |                                                                             |

| SRXData.4 | (Read only) Data received from the smart card. Data received from the smart |

| SRXData.3 | card gets stored in a FIFO that is read by the firmware.                    |

| SRXData.2 |                                                                             |

| SRXData.1 |                                                                             |

| SRXData.0 |                                                                             |

## Smart Card Control Register (SCCtI): 0xFE0A ← 0x21

This register is used to monitor reception of data from the smart card.

## Table 82: The SCCtl Register

| MSB LSB |        |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |    |        |        |  |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|--------|--------|--|

| RST     | CRD –  | IO                                                                                                                                                                                                                                                                                                                                                                                                                        | IOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C8 | C4 | CLKLVL | CLKOFF |  |

| Bit     | Symbol | Function                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |    |        |        |  |

| SCCtl.7 | RSTCRD | the RST (see<br>RST to the so<br>operational i<br>perform a "V<br>be set = 0 to<br>parameters.<br>In sync mod                                                                                                                                                                                                                                                                                                             | 1 = Asserts the RST (set RST = 0) to the smart card interface, 0 = De-assert<br>the RST (set RST = 1) to the smart card interface. Can be used to extend<br>RST to the smart card. Refer to RLength register description. This bit is<br>operational in all modes and can be used to extend RST during activation or<br>perform a "Warm Reset" as required. In auto-sequence mode, this bit should<br>be set = 0 to allow the sequencer to de-assert RST per the RLength<br>parameters.<br>In sync mode (see the SPrtcol register) the sense of this bit is non-inverted, if<br>set = 1, RST = 1, if set = 0, RST = 0. Rlen has no effect on Reset in sync |    |    |        |        |  |

| SCCtl.6 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |    |        |        |  |

| SCCtl.5 | Ю      | synchronize<br>signal on I/C                                                                                                                                                                                                                                                                                                                                                                                              | Smart Card I/O. Read is state of I/O signal (Caution, this signal is not synchronized to the MPU clock). In Bypass mode, write value is state of signal on I/O. In sync mode, this bit will contain the value of I/O pin on the latest rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                 |    |    |        |        |  |

| SCCtl.4 | IOD    |                                                                                                                                                                                                                                                                                                                                                                                                                           | Smart Card I/O Direction control Bypass mode or sync mode. 1 = input (default), 0 = output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |    |        |        |  |

| SCCtl.3 | C8     | on the C8 lin<br>the register.<br>(Caution, thi                                                                                                                                                                                                                                                                                                                                                                           | Smart Card C8. When C8 is an output, the value written to this bit will appear<br>on the C8 line. The value read when C8 is an output is the value stored in<br>the register. When C8 is an input, the value read is the value on the C8 pin<br>(Caution, this signal is not synchronized to the MPU clock). When C8 is an<br>input, the value written will be stored in the register but not presented to the<br>C8 pin.                                                                                                                                                                                                                                  |    |    |        |        |  |

| SCCtl.2 | C4     | Smart Card C4. When C4 is an output, the value written to this bit will appear<br>on the C4 line. The value read when C4 is an output is the value stored in<br>the register. When C4 is an input, the value read is the value on the C4 pin<br>(Caution, this signal is not synchronized to the MPU clock). When C4 is an<br>input, the value written will be stored in the register but not presented to the<br>C4 pin. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |    |        |        |  |

| SCCtl.1 | CLKLVL | logic level in                                                                                                                                                                                                                                                                                                                                                                                                            | 1 = High, 0 = Low. If CLKOFF is set = 1, the CLK to smart card will be at the logic level indicated by this bit. If in bypass mode, this bit directly controls the state of CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |    |        |        |  |

| SCCtl.0 | CLKOFF | 0 = CLK is enabled. 1 = CLK is not enabled. When asserted, the CLK will stop at the level selected by CLKLVL. This bit has no effect if in bypass mode.                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |    |        |        |  |

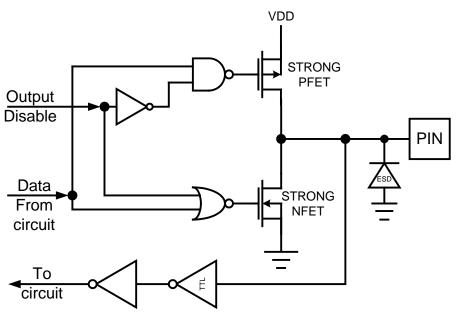

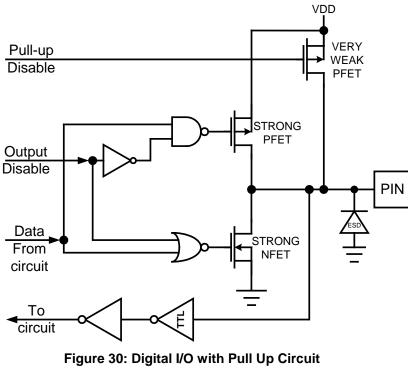

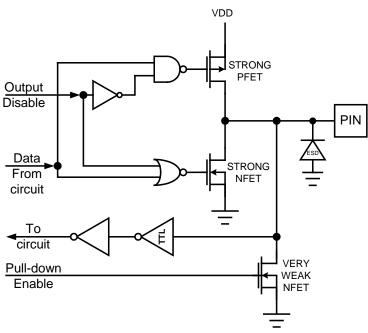

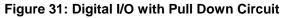

Figure 28: Digital I/O Circuit

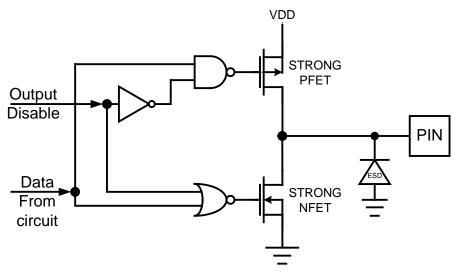

Figure 29: Digital Output Circuit

# 7 Ordering Information

Table 109 lists the order numbers and packaging marks used to identify 73S1210F products.

## Table 109: Order Numbers and Packaging Marks

| Part Description                                               | Order Number       | Packaging Mark |

|----------------------------------------------------------------|--------------------|----------------|

| 73S1210F 68-Pin QFN, Lead Free                                 | 73S1210F-68IM/F    | 73S1210F68IM   |

| 73S1210F 68-Pin QFN, Lead Free with Programming                | 73S1210F-68IM/F/P  | 73S1210F68IM   |

| 73S1210F 68-Pin QFN, Lead Free, Tape and Reel                  | 73S1210F-68IMR/F   | 73S1210F68IM   |

| 73S1210F 68-Pin QFN, Lead Free, Tape and Reel with Programming | 73S1210F-68IMR/F/P | 73S1210F68IM   |

| 73S1210F 44-Pin QFN, Lead Free                                 | 73S1210F-44IM/F    | 73S1210F44IM   |

| 73S1210F 44-Pin QFN, Lead Free with Programming                | 73S1210F-44IM/F/P  | 73S1210F44IM   |

| 73S1210F 44-Pin QFN, Lead Free, Tape and Reel                  | 73S1210F-44IMR/F   | 73S1210F44IM   |

| 73S1210F 44-Pin QFN, Lead Free, Tape and Reel with Programming | 73S1210F-44IMR/F/P | 73S1210F44IM   |

## 8 Related Documentation

The following 73S1210F documents are available from Teridian Semiconductor Corporation:

73S1210F Data Sheet (this document) 73S1210F Development Board Quick Start Guide 73S1210F Software Development Kit Quick Start Guide 73S1210F Evaluation Board User's Guide 73S12xxF Software User's Guide 73S12xxF Synchronous Card Design Application Note

# 9 Contact Information

For more information about Teridian Semiconductor products or to check the availability of the 73S1210F, contact us at:

6440 Oak Canyon Road Suite 100 Irvine, CA 92618-5201

Telephone: (714) 508-8800 FAX: (714) 508-8878 Email: scr.support@teridian.com

For a complete list of worldwide sales offices, go to http://www.teridian.com.

|     |           | In Section 1.7.15.5, deleted "The ETU clock is held in reset condition until the activation sequence begins (either by VCCOK=1 or VCCTMR timeout) and will go high $\frac{1}{2}$ the ETU period thereafter."                                                                                                                                                                                                                                                                                                  |

|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |           | In Section 1.7.15.5, added "Synchronous card operation is broken down<br>into three primary types. These are commonly referred to as 2-wire,<br>3-wire and I2C synchronous cards. Each card type requires different<br>control and timing and therefore requires different algorithms to access.<br>Teridian has created an application note to provide detailed algorithms for<br>each card type. Refer to the application note titled <i>73S12xxF</i><br><i>Synchronous Card Design Application Note.</i> " |

|     |           | In Table 78 and Table 107, changed the SYCKST bit to I2CMODE.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |           | In Figure 25, replaced the schematic with a new schematic.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |           | In Section 3.4, changed the Fxtal Min from 4 to 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |           | Added 44-pin QFN package.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |           | Added Section 8, Related Documentation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |           | Added Section 9, Contact Information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |           | Formatted the document per new standard. Added section numbering.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.3 | 1/22/2009 | Changed the value for the $I_{DD_{-}IN}$ Power Down (25°C) parameter from 13 $\mu$ A to 15 $\mu$ A.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.4 | 5/12/2009 | In Table 1, corrected the 44 QFN GND pin from 37 to 26.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |           | Added the "with Programming" ordering numbers to Table 109.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

© 2009 Teridian Semiconductor Corporation. All rights reserved.

Teridian Semiconductor Corporation is a registered trademark of Teridian Semiconductor Corporation. Windows is a registered trademark of Microsoft Corporation.

Signum Systems is a trademark of Signum Systems Corporation.

All other trademarks are the property of their respective owners.

Teridian Semiconductor Corporation makes no warranty for the use of its products, other than expressly contained in the Company's warranty detailed in the Teridian Semiconductor Corporation standard Terms and Conditions. The company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice and does not make any commitment to update the information contained herein. Accordingly, the reader is cautioned to verify that this document is current by comparing it to the latest version on http://www.teridian.com or by checking with your sales representative.

Teridian Semiconductor Corp., 6440 Oak Canyon, Suite 100, Irvine, CA 92618 TEL (714) 508-8800, FAX (714) 508-8877, http://www.teridian.com