Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                           |

| Core Size                  | 32-Bit Single-Core                                        |

| Speed                      | 50MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                 |

| Number of I/O              | 33                                                        |

| Program Memory Size        | 64KB (64K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 2K x 8                                                    |

| RAM Size                   | 16K × 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                              |

| Data Converters            | A/D 16x16b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 48-VFQFN Exposed Pad                                      |

| Supplier Device Package    | 48-QFN-EP (7x7)                                           |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mk10dx64vft5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.2.3 Voltage and current operating behaviors Table 4. Voltage and current operating behaviors

| Symbol           | Description                                                                                            | Min.                  | Max. | Unit                                                                                                     | Notes |

|------------------|--------------------------------------------------------------------------------------------------------|-----------------------|------|----------------------------------------------------------------------------------------------------------|-------|

| V <sub>OH</sub>  | Output high voltage — high drive strength                                                              |                       |      |                                                                                                          |       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = - 9 mA                                  | V <sub>DD</sub> – 0.5 | —    | V                                                                                                        |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OH}} = -3 \text{ mA}$   | V <sub>DD</sub> – 0.5 | —    | V                                                                                                        |       |

|                  | Output high voltage — low drive strength                                                               |                       |      |                                                                                                          |       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -2 mA                                   | V <sub>DD</sub> – 0.5 | _    | V                                                                                                        |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OH}} = -0.6 \text{ mA}$ | $V_{DD} - 0.5$        | _    | V                                                                                                        |       |

| I <sub>OHT</sub> | Output high current total for all ports                                                                | —                     | 100  | mA                                                                                                       |       |

| V <sub>OL</sub>  | Output low voltage — high drive strength                                                               |                       |      | V<br>V<br>V<br>(V<br>ν<br>(V)<br>V<br>V<br>V<br>V<br>V<br>(V)<br>V<br>(V)<br>V<br>(V)<br>(V)<br>(V)<br>( |       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 9 mA                                    | _                     | 0.5  |                                                                                                          |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OL}} = 3 \text{ mA}$    | _                     | 0.5  | V                                                                                                        |       |

|                  | Output low voltage — low drive strength                                                                |                       |      |                                                                                                          |       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 2 mA                                    | _                     | 0.5  | V                                                                                                        |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OL}} = 0.6 \text{ mA}$  | _                     | 0.5  | V                                                                                                        |       |

| I <sub>OLT</sub> | Output low current total for all ports                                                                 | —                     | 100  | mA                                                                                                       |       |

| I <sub>IN</sub>  | Input leakage current (per pin)                                                                        |                       |      |                                                                                                          |       |

|                  | @ full temperature range                                                                               | _                     | 1.0  | μA                                                                                                       | 1     |

|                  | • @ 25 °C                                                                                              | —                     | 0.1  | μA                                                                                                       |       |

| I <sub>OZ</sub>  | Hi-Z (off-state) leakage current (per pin)                                                             | —                     | 1    | μA                                                                                                       |       |

| I <sub>OZ</sub>  | Total Hi-Z (off-state) leakage current (all input pins)                                                | —                     | 4    | μΑ                                                                                                       |       |

| R <sub>PU</sub>  | Internal pullup resistors                                                                              | 22                    | 50   | kΩ                                                                                                       | 2     |

| R <sub>PD</sub>  | Internal pulldown resistors                                                                            | 22                    | 50   | kΩ                                                                                                       | 3     |

1. Tested by ganged leakage method

2. Measured at Vinput =  $V_{SS}$

3. Measured at Vinput =  $V_{DD}$

# 5.2.4 Power mode transition operating behaviors

All specifications except  $t_{POR}$ , and VLLSx $\rightarrow$ RUN recovery times in the following table assume this clock configuration:

- CPU and system clocks = 50 MHz

- Bus clock = 50 MHz

- Flash clock = 25 MHz

| Symbol                | Description                                                                    | Min. | Тур.  | Max.  | Unit | Notes |

|-----------------------|--------------------------------------------------------------------------------|------|-------|-------|------|-------|

| I <sub>DD_VLLS0</sub> | Very low-leakage stop mode 0 current at 3.0 V with POR detect circuit disabled |      |       |       |      |       |

|                       | ● @40 to 25°C                                                                  | —    | 0.176 | 0.859 | μA   |       |

|                       | • @ 70°C                                                                       | —    | 2.2   | 13.1  | μA   |       |

|                       | • @ 105°C                                                                      | _    | 13    | 23.9  | μA   |       |

| I <sub>DD_VBAT</sub>  | Average current with RTC and 32kHz disabled at 3.0 V                           |      |       |       |      |       |

|                       | <ul> <li>@ -40 to 25°C</li> </ul>                                              |      | 0.19  | 0.22  | μA   |       |

|                       | • @ 70°C                                                                       |      | 0.49  | 0.64  | μA   |       |

|                       | • @ 105°C                                                                      | _    | 2.2   | 3.2   | μA   |       |

| I <sub>DD_VBAT</sub>  | Average current when CPU is not accessing<br>RTC registers                     |      |       |       |      | 9     |

|                       | • @ 1.8V                                                                       |      |       |       |      |       |

|                       | • @ -40 to 25°C                                                                |      | 0.57  | 0.67  | μA   |       |

|                       | • @ 70°C                                                                       | _    | 0.90  | 1.2   | μA   |       |

|                       | • @ 105°C                                                                      |      | 2.4   | 3.5   | μA   |       |

|                       | • @ 3.0V                                                                       |      |       | 0.0   | P/ 1 |       |

|                       | <ul> <li>@ -40 to 25°C</li> </ul>                                              | _    | 0.67  | 0.94  | μA   |       |

|                       | • @ 70°C                                                                       | _    | 1.0   | 1.4   | μA   |       |

|                       | • @ 105°C                                                                      | _    | 2.7   | 3.9   | μA   |       |

#### Table 6. Power consumption operating behaviors (continued)

- 1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

- 2. 50MHz core and system clock, 25MHz bus clock, and 25MHz flash clock . MCG configured for FEI mode. All peripheral clocks disabled.

- 3. 50MHz core and system clock, 25MHz bus clock, and 25MHz flash clock. MCG configured for FEI mode. All peripheral clocks enabled, and peripherals are in active operation.

- 4. Max values are measured with CPU executing DSP instructions

- 5. 25MHz core and system clock, 25MHz bus clock, and 12.5MHz flash clock. MCG configured for FEI mode.

- 6. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled. Code executing from flash.

- 7. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks enabled but peripherals are not in active operation. Code executing from flash.

- 8. 4 MHz core, system, and bus clock and 1MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled.

- 9. Includes 32kHz oscillator current and RTC operation.

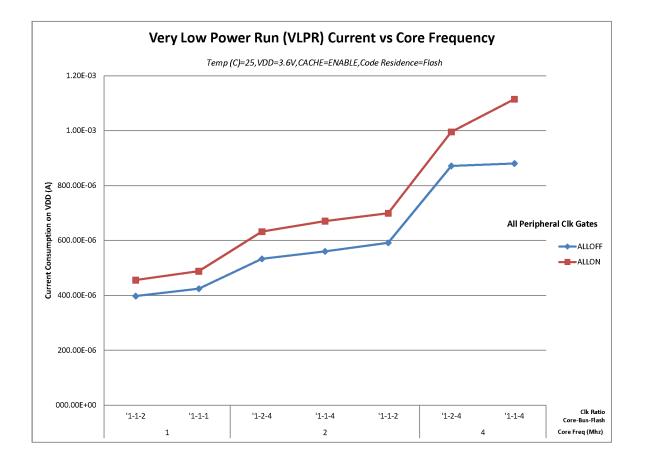

## 5.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG in FBE mode

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFL

Figure 3. VLPR mode supply current vs. core frequency

## 5.2.6 EMC radiated emissions operating behaviors Table 7. EMC radiated emissions operating behaviors for 64LQFP

| Symbol              | Description                        | Frequency<br>band (MHz) | Тур. | Unit | Notes |

|---------------------|------------------------------------|-------------------------|------|------|-------|

| V <sub>RE1</sub>    | Radiated emissions voltage, band 1 | 0.15–50                 | 19   | dBµV | 1,2   |

| V <sub>RE2</sub>    | Radiated emissions voltage, band 2 | 50–150                  | 21   | dBµV |       |

| V <sub>RE3</sub>    | Radiated emissions voltage, band 3 | 150–500                 | 19   | dBµV |       |

| V <sub>RE4</sub>    | Radiated emissions voltage, band 4 | 500–1000                | 11   | dBµV |       |

| V <sub>RE_IEC</sub> | IEC level                          | 0.15–1000               | L    | _    | 2, 3  |

Determined according to IEC Standard 61967-1, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 1: General Conditions and Definitions and IEC Standard 61967-2, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 2: Measurement of Radiated Emissions—TEM Cell and Wideband TEM Cell Method. Measurements were made while the microcontroller was running basic application code. The reported

| Symbol                   | Description                    | Min. | Max. | Unit | Notes |

|--------------------------|--------------------------------|------|------|------|-------|

| f <sub>LPTMR_pin</sub>   | LPTMR clock                    | _    | 25   | MHz  |       |

| f <sub>LPTMR_ERCLK</sub> | LPTMR external reference clock | _    | 16   | MHz  |       |

| f <sub>I2S_MCLK</sub>    | I2S master clock               | _    | 12.5 | MHz  |       |

| f <sub>I2S_BCLK</sub>    | I2S bit clock                  | _    | 4    | MHz  |       |

Table 9. Device clock specifications (continued)

1. The frequency limitations in VLPR mode here override any frequency specification listed in the timing specification for any other module.

# 5.3.2 General switching specifications

These general purpose specifications apply to all signals configured for GPIO, UART, CMT, and I<sup>2</sup>C signals.

| Symbol                                                                                                      | Description                                                                                                | Min. | Max.     | Unit                | Notes |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|----------|---------------------|-------|

|                                                                                                             | GPIO pin interrupt pulse width (digital glitch filter disabled) — Synchronous path                         | 1.5  | —        | Bus clock<br>cycles | 1, 2  |

|                                                                                                             | GPIO pin interrupt pulse width (digital glitch filter disabled, analog filter enabled) — Asynchronous path | 100  | _        | ns                  | 3     |

| GPIO pin interrupt pulse width (digital glitch filter disabled, analog filter disabled) — Asynchronous path |                                                                                                            | 50   | _        | ns                  | 3     |

|                                                                                                             | External reset pulse width (digital glitch filter disabled)                                                | 100  | _        | ns                  | 3     |

|                                                                                                             | Mode select (EZP_CS) hold time after reset deassertion                                                     | 2    | _        | Bus clock<br>cycles |       |

|                                                                                                             | Port rise and fall time (high drive strength)                                                              |      |          |                     | 4     |

|                                                                                                             | Slew disabled                                                                                              |      |          |                     |       |

|                                                                                                             | • $1.71 \le V_{DD} \le 2.7V$                                                                               | —    | 13       | ns                  |       |

|                                                                                                             | • $2.7 \le V_{DD} \le 3.6V$                                                                                | —    |          | ns                  |       |

|                                                                                                             | Slew enabled                                                                                               |      | 7        |                     |       |

|                                                                                                             | • 1.71 ≤ V <sub>DD</sub> ≤ 2.7V                                                                            | —    |          | ns                  |       |

|                                                                                                             | • $2.7 \le V_{DD} \le 3.6V$                                                                                | _    | 36<br>24 | ns                  |       |

Table 10. General switching specifications

| Symbol | Description                                  | Min. | Max. | Unit | Notes |

|--------|----------------------------------------------|------|------|------|-------|

|        | Port rise and fall time (low drive strength) |      |      |      | 5     |

|        | Slew disabled                                |      |      |      |       |

|        | • $1.71 \le V_{DD} \le 2.7V$                 | _    | 12   | ns   |       |

|        | • $2.7 \le V_{DD} \le 3.6V$                  | _    | 6    | ns   |       |

|        | Slew enabled                                 |      |      |      |       |

|        | • $1.71 \le V_{DD} \le 2.7V$                 | _    | 36   | ns   |       |

|        | • 2.7 ≤ V <sub>DD</sub> ≤ 3.6V               | —    | 24   | ns   |       |

|        |                                              |      |      |      |       |

### Table 10. General switching specifications (continued)

- 1. This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In Stop, VLPS, LLS, and VLLSx modes, the synchronizer is bypassed so shorter pulses can be recognized in that case.

- 2. The greater synchronous and asynchronous timing must be met.

- 3. This is the minimum pulse width that is guaranteed to be recognized as a pin interrupt request in Stop, VLPS, LLS, and VLLSx modes.

- 4. 75pF load

- 5. 15pF load

# 5.4 Thermal specifications

## 5.4.1 Thermal operating requirements

#### Table 11. Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit |

|----------------|--------------------------|------|------|------|

| TJ             | Die junction temperature | -40  | 125  | °C   |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   |

## 5.4.2 Thermal attributes

| Board type           | Symbol           | Description                                                              | 48 LQFP | 48 QFN | Unit | Notes |

|----------------------|------------------|--------------------------------------------------------------------------|---------|--------|------|-------|

| Single-layer<br>(1s) | R <sub>eJA</sub> | Thermal<br>resistance,<br>junction to<br>ambient (natural<br>convection) | 70      | 81     | °C/W | 1, 2  |

| Four-layer<br>(2s2p) | R <sub>eJA</sub> | Thermal<br>resistance,<br>junction to<br>ambient (natural<br>convection) | 47      | 28     | °C/W | 1, 3  |

| Board type           | Symbol            | Description                                                                                                          | 48 LQFP | 48 QFN | Unit | Notes |

|----------------------|-------------------|----------------------------------------------------------------------------------------------------------------------|---------|--------|------|-------|

| Single-layer<br>(1s) | R <sub>0JMA</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200 ft./<br>min. air speed)                                        | 58      | 66     | °C/W | 1,3   |

| Four-layer<br>(2s2p) | R <sub>eJMA</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200 ft./<br>min. air speed)                                        | 40      | 23     | °C/W | 3     |

| _                    | R <sub>0JB</sub>  | Thermal<br>resistance,<br>junction to<br>board                                                                       | 24      | 11     | °C/W | 5     |

| _                    | R <sub>θJC</sub>  | Thermal<br>resistance,<br>junction to case                                                                           | 18      | 1.4    | °C/W | 6     |

|                      | Ψ <sub>JT</sub>   | Thermal<br>characterization<br>parameter,<br>junction to<br>package top<br>outside center<br>(natural<br>convection) | 3       | 4      | °C/W | 7     |

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

2. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air) with the single layer board horizontal. For the LQFP, the board meets the JESD51-3 specification. For the MAPBGA, the board meets the JESD51-9 specification.

3. Determined according to JEDEC Standard JESD51-6, *Integrated Circuits Thermal Test Method Environmental Conditions – Forced Convection (Moving Air)* with the board horizontal.

5. Determined according to JEDEC Standard JESD51-8, *Integrated Circuit Thermal Test Method Environmental Conditions—Junction-to-Board*. Board temperature is measured on the top surface of the board near the package.

- 6. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard, Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

- 7. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air).

# 6 Peripheral operating requirements and behaviors

# 6.1 Core modules

# 6.1.1 JTAG electricals

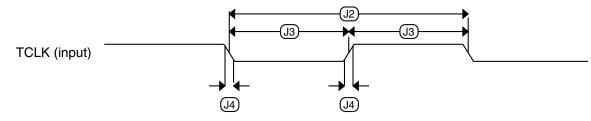

| Symbol | Description                                                     | Min. | Max. | Unit |

|--------|-----------------------------------------------------------------|------|------|------|

|        | Operating voltage                                               | 2.7  | 5.5  | V    |

| J1     | TCLK frequency of operation                                     |      |      | MHz  |

|        | • JTAG                                                          |      | 10   |      |

|        | • CJTAG                                                         | —    | 5    |      |

| J2     | TCLK cycle period                                               | 1/J1 | _    | ns   |

| J3     | TCLK clock pulse width                                          |      |      |      |

|        | • JTAG                                                          | 100  | _    | ns   |

|        | • CJTAG                                                         | 200  | —    | ns   |

|        |                                                                 |      |      | ns   |

| J4     | TCLK rise and fall times                                        | —    | 1    | ns   |

| J5     | TMS input data setup time to TCLK rise <ul> <li>JTAG</li> </ul> | 53   | _    | ns   |

|        | • CJTAG                                                         | 112  | —    |      |

| J6     | TDI input data setup time to TCLK rise                          | 8    | —    | ns   |

| J7     | TMS input data hold time after TCLK rise<br>• JTAG              | 3.4  | _    | ns   |

|        | • CJTAG                                                         | 3.4  | —    |      |

| J8     | TDI input data hold time after TCLK rise                        | 3.4  | _    | ns   |

| J9     | TCLK low to TMS data valid<br>• JTAG                            | _    | 48   | ns   |

|        | • CJTAG                                                         | —    | 85   |      |

| J10    | TCLK low to TDO data valid                                      | —    | 48   | ns   |

| J11    | Output data hold/invalid time after clock edge <sup>1</sup>     |      | 3    | ns   |

Table 12. JTAG voltage range electricals

1. They are common for JTAG and CJTAG. Input transition = 1 ns and Output load = 50pf

Figure 4. Test clock input timing

| Symbol                       | Description                                                                                                                                       |                                                                                          | Min.  | Тур.  | Max.    | Unit | Notes |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------|-------|---------|------|-------|

| f <sub>fll_ref</sub>         | FLL reference free                                                                                                                                | luency range                                                                             | 31.25 | _     | 39.0625 | kHz  |       |

| f <sub>dco</sub>             | DCO output<br>frequency range                                                                                                                     | Low range (DRS=00)<br>640 × f <sub>fll_ref</sub>                                         | 20    | 20.97 | 25      | MHz  | 2, 3  |

|                              |                                                                                                                                                   | Mid range (DRS=01)<br>1280 × f <sub>fll_ref</sub>                                        | 40    | 41.94 | 50      | MHz  |       |

|                              |                                                                                                                                                   | Mid-high range (DRS=10)<br>1920 × f <sub>fll_ref</sub>                                   | 60    | 62.91 | 75      | MHz  | -     |

|                              |                                                                                                                                                   | High range (DRS=11)<br>2560 × f <sub>fll_ref</sub>                                       | 80    | 83.89 | 100     | MHz  | -     |

| f <sub>dco_t_DMX3</sub><br>2 | DCO output<br>frequency                                                                                                                           | Low range (DRS=00) $732 \times f_{fll\_ref}$                                             |       | 23.99 | -       | MHz  | 4, 5  |

|                              |                                                                                                                                                   | Mid range (DRS=01)<br>1464 × f <sub>fll_ref</sub>                                        | _     | 47.97 | -       | MHz  |       |

|                              |                                                                                                                                                   | Mid-high range (DRS=10)<br>2197 × f <sub>fll_ref</sub>                                   |       | 71.99 | -       | MHz  |       |

|                              |                                                                                                                                                   | High range (DRS=11)<br>2929 × f <sub>fll_ref</sub>                                       |       | 95.98 | -       | MHz  | -     |

| J <sub>cyc_fll</sub>         | FLL period jitter                                                                                                                                 |                                                                                          |       | 180   |         | ps   |       |

|                              | <ul> <li>f<sub>VCO</sub> = 48 M</li> <li>f<sub>VCO</sub> = 98 M</li> </ul>                                                                        |                                                                                          | _     | 150   | _       |      |       |

| t <sub>fll_acquire</sub>     | FLL target frequer                                                                                                                                | ncy acquisition time                                                                     |       | —     | 1       | ms   | 6     |

|                              |                                                                                                                                                   | PI                                                                                       | L     |       |         |      |       |

| f <sub>vco</sub>             | VCO operating fre                                                                                                                                 | quency                                                                                   | 48.0  | _     | 100     | MHz  |       |

| I <sub>pli</sub>             |                                                                                                                                                   | rent<br>IHz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub> =<br>/ multiplier = 48) | _     | 1060  | _       | μΑ   | 7     |

| I <sub>pll</sub>             | <ul> <li>PLL operating current</li> <li>PLL @ 48 MHz (f<sub>osc_hi_1</sub> = 8 MHz, f<sub>pll_ref</sub> = 2 MHz, VDIV multiplier = 24)</li> </ul> |                                                                                          | _     | 600   | -       | μΑ   | 7     |

| f <sub>pll_ref</sub>         | PLL reference free                                                                                                                                | quency range                                                                             | 2.0   | _     | 4.0     | MHz  |       |

| J <sub>cyc_pll</sub>         | PLL period jitter (F                                                                                                                              | RMS)                                                                                     |       |       |         |      | 8     |

|                              | • f <sub>vco</sub> = 48 MH                                                                                                                        | lz                                                                                       | —     | 120   | —       | ps   |       |

|                              | • f <sub>vco</sub> = 100 M                                                                                                                        | Hz                                                                                       | —     | 50    | —       | ps   |       |

## Table 13. MCG specifications (continued)

| Symbol                | Description                           | Min.   | Тур. | Max.                                                          | Unit | Notes |

|-----------------------|---------------------------------------|--------|------|---------------------------------------------------------------|------|-------|

| J <sub>acc_pll</sub>  | PLL accumulated jitter over 1µs (RMS) |        |      |                                                               |      | 8     |

|                       | • f <sub>vco</sub> = 48 MHz           | —      | 1350 | —                                                             | ps   |       |

|                       | • f <sub>vco</sub> = 100 MHz          | _      | 600  | _                                                             | ps   |       |

| D <sub>lock</sub>     | Lock entry frequency tolerance        | ± 1.49 |      | ± 2.98                                                        | %    |       |

| D <sub>unl</sub>      | Lock exit frequency tolerance         | ± 4.47 |      | ± 5.97                                                        | %    |       |

| t <sub>pll_lock</sub> | Lock detector detection time          |        |      | 150 × 10 <sup>-6</sup><br>+ 1075(1/<br>f <sub>pll_ref</sub> ) | S    | 9     |

Table 13. MCG specifications (continued)

1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

2. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

The resulting system clock frequencies should not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco\_t</sub>) over voltage and temperature should be considered.

4. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

5. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

6. This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

7. Excludes any oscillator currents that are also consuming power while PLL is in operation.

8. This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary.

This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

## 6.3.2 Oscillator electrical specifications

This section provides the electrical characteristics of the module.

### 6.3.2.1 Oscillator DC electrical specifications Table 14. Oscillator DC electrical specifications

| Symbol   | Description                             | Min. | Тур. | Max. | Unit | Notes |

|----------|-----------------------------------------|------|------|------|------|-------|

| $V_{DD}$ | Supply voltage                          | 1.71 | —    | 3.6  | V    |       |

| IDDOSC   | Supply current — low-power mode (HGO=0) |      |      |      |      | 1     |

|          | • 32 kHz                                | _    | 500  | —    | nA   |       |

|          | • 4 MHz                                 | _    | 200  | _    | μA   |       |

|          | • 8 MHz (RANGE=01)                      | _    | 300  | —    | μA   |       |

|          | • 16 MHz                                | _    | 950  | _    | μA   |       |

|          | • 24 MHz                                | _    | 1.2  | _    | mA   |       |

|          | • 32 MHz                                | _    | 1.5  | _    | mA   |       |

## 6.4.1.2 Flash timing specifications — commands Table 19. Flash command timing specifications

| Symbol                  | Description                                          | Min.       | Тур.        | Max. | Unit | Notes |

|-------------------------|------------------------------------------------------|------------|-------------|------|------|-------|

|                         | Read 1s Block execution time                         |            |             |      |      |       |

| t <sub>rd1blk32k</sub>  | • 32 KB data flash                                   | —          | —           | 0.5  | ms   |       |

| t <sub>rd1blk128k</sub> | 128 KB program flash                                 | —          |             | 1.7  | ms   |       |

| t <sub>rd1sec1k</sub>   | Read 1s Section execution time (flash sector)        | —          |             | 60   | μs   | 1     |

| t <sub>pgmchk</sub>     | Program Check execution time                         | _          | _           | 45   | μs   | 1     |

| t <sub>rdrsrc</sub>     | Read Resource execution time                         | _          | _           | 30   | μs   | 1     |

| t <sub>pgm4</sub>       | Program Longword execution time                      | _          | 65          | 145  | μs   |       |

|                         | Erase Flash Block execution time                     |            |             |      |      | 2     |

| t <sub>ersblk32k</sub>  | • 32 KB data flash                                   | _          | 55          | 465  | ms   |       |

| t <sub>ersblk128k</sub> | <ul> <li>128 KB program flash</li> </ul>             | _          | 61          | 495  | ms   |       |

| t <sub>ersscr</sub>     | Erase Flash Sector execution time                    |            | 14          | 114  | ms   | 2     |

|                         | Program Section execution time                       |            |             |      |      |       |

| t <sub>pgmsec512</sub>  | • 512 B flash                                        | —          | 4.7         | _    | ms   |       |

| t <sub>pgmsec1k</sub>   | • 1 KB flash                                         | —          | 9.3         | _    | ms   |       |

| t <sub>rd1all</sub>     | Read 1s All Blocks execution time                    | _          |             | 1.8  | ms   |       |

| t <sub>rdonce</sub>     | Read Once execution time                             |            |             | 25   | μs   | 1     |

| t <sub>pgmonce</sub>    | Program Once execution time                          | _          | 65          |      | μs   |       |

| t <sub>ersall</sub>     | Erase All Blocks execution time                      | —          | 115         | 1000 | ms   | 2     |

| t <sub>vfykey</sub>     | Verify Backdoor Access Key execution time            | _          | —           | 30   | μs   | 1     |

|                         | Program Partition for EEPROM execution time          |            |             |      |      |       |

| t <sub>pgmpart32k</sub> | • 32 KB FlexNVM                                      | —          | 70          |      | ms   |       |

|                         | Set FlexRAM Function execution time:                 |            |             |      |      |       |

| t <sub>setramff</sub>   | Control Code 0xFF                                    | _          | 50          | _    | μs   |       |

| t <sub>setram8k</sub>   | 8 KB EEPROM backup                                   | _          | 0.3         | 0.5  | ms   |       |

| t <sub>setram32k</sub>  | 32 KB EEPROM backup                                  | _          | 0.7         | 1.0  | ms   |       |

|                         | Byte-write to FlexRAM                                | for EEPROM | l operation |      |      |       |

| t <sub>eewr8bers</sub>  | Byte-write to erased FlexRAM location execution time |            | 175         | 260  | μs   | 3     |

|                         | Byte-write to FlexRAM execution time:                |            |             |      |      |       |

| t <sub>eewr8b8k</sub>   | 8 KB EEPROM backup                                   | _          | 340         | 1700 | μs   |       |

| t <sub>eewr8b16k</sub>  | 16 KB EEPROM backup                                  | _          | 385         | 1800 | μs   |       |

| t <sub>eewr8b32k</sub>  | 32 KB EEPROM backup                                  | _          | 475         | 2000 | μs   |       |

| Symbol                   | Description                                              | Min.     | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|--------------------------|----------------------------------------------------------|----------|-------------------|------|--------|-------|

| t <sub>nvmretd1k</sub>   | Data retention after up to 1 K cycles                    | 20       | 100               | _    | years  |       |

| n <sub>nvmcycd</sub>     | Cycling endurance                                        | 10 K     | 50 K              | _    | cycles | 2     |

|                          | FlexRAM as                                               | s EEPROM |                   |      |        |       |

| t <sub>nvmretee100</sub> | Data retention up to 100% of write endurance             | 5        | 50                | _    | years  |       |

| t <sub>nvmretee10</sub>  | Data retention up to 10% of write endurance              | 20       | 100               | _    | years  |       |

|                          | Write endurance                                          |          |                   |      |        | 3     |

| n <sub>nvmwree16</sub>   | EEPROM backup to FlexRAM ratio = 16                      | 35 K     | 175 K             | —    | writes |       |

| n <sub>nvmwree128</sub>  | <ul> <li>EEPROM backup to FlexRAM ratio = 128</li> </ul> | 315 K    | 1.6 M             | —    | writes |       |

| n <sub>nvmwree512</sub>  | <ul> <li>EEPROM backup to FlexRAM ratio = 512</li> </ul> | 1.27 M   | 6.4 M             | —    | writes |       |

| n <sub>nvmwree4k</sub>   | EEPROM backup to FlexRAM ratio = 4096                    | 10 M     | 50 M              | —    | writes |       |

| n <sub>nvmwree8k</sub>   | EEPROM backup to FlexRAM ratio = 8192                    | 20 M     | 100 M             | —    | writes |       |

Table 21. NVM reliability specifications (continued)

Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25°C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

2. Cycling endurance represents number of program/erase cycles at -40°C  $\leq$  T<sub>j</sub>  $\leq$  125°C.

3. Write endurance represents the number of writes to each FlexRAM location at -40°C ≤Tj ≤ 125°C influenced by the cycling endurance of the FlexNVM (same value as data flash) and the allocated EEPROM backup. Minimum and typical values assume all byte-writes to FlexRAM.

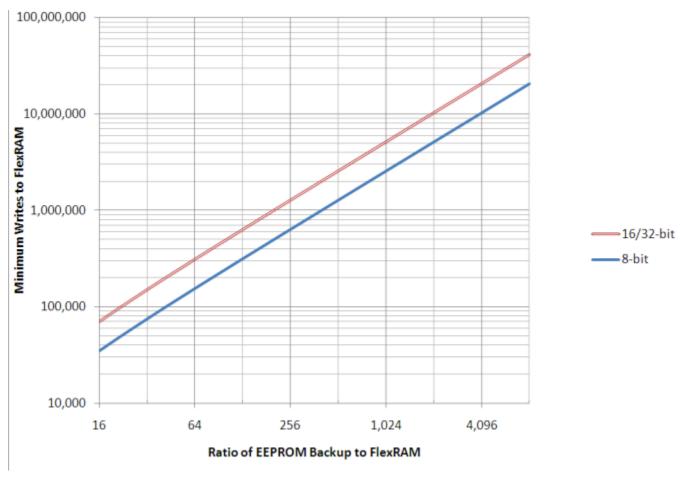

## 6.4.1.5 Write endurance to FlexRAM for EEPROM

When the FlexNVM partition code is not set to full data flash, the EEPROM data set size can be set to any of several non-zero values.

The bytes not assigned to data flash via the FlexNVM partition code are used by the flash memory module to obtain an effective endurance increase for the EEPROM data. The built-in EEPROM record management system raises the number of program/erase cycles that can be attained prior to device wear-out by cycling the EEPROM data through a larger EEPROM NVM storage space.

While different partitions of the FlexNVM are available, the intention is that a single choice for the FlexNVM partition code and EEPROM data set size is used throughout the entire lifetime of a given application. The EEPROM endurance equation and graph shown below assume that only one configuration is ever used.

Writes\_FlexRAM =

$$\frac{\text{EEPROM} - 2 \times \text{EEESIZE}}{\text{EEESIZE}} \times \text{Write}_\text{efficiency} \times n_{\text{nvmcycd}}$$

where

• Writes\_FlexRAM — minimum number of writes to each FlexRAM location

- EEPROM allocated FlexNVM based on DEPART; entered with the Program Partition command

- EEESIZE allocated FlexRAM based on DEPART; entered with the Program Partition command

- Write\_efficiency

- 0.25 for 8-bit writes to FlexRAM

- 0.50 for 16-bit or 32-bit writes to FlexRAM

- n<sub>nvmcycd</sub> data flash cycling endurance (the following graph assumes 10,000 cycles)

Figure 8. EEPROM backup writes to FlexRAM

# 6.4.2 EzPort Switching Specifications

Table 22. EzPort switching specifications

| Num | Description       | Min. | Max. | Unit |

|-----|-------------------|------|------|------|

|     | Operating voltage | 1.71 | 3.6  | V    |

Table continues on the next page ...

# 6.6.1 ADC electrical specifications

The 16-bit accuracy specifications listed in Table 23 and Table 24 are achievable on the differential pins ADCx\_DP0, ADCx\_DM0.

All other ADC channels meet the 13-bit differential/12-bit single-ended accuracy specifications.

| Symbol            | Description                       | Conditions                                                          | Min.              | Typ. <sup>1</sup> | Max.              | Unit | Notes |

|-------------------|-----------------------------------|---------------------------------------------------------------------|-------------------|-------------------|-------------------|------|-------|

| V <sub>DDA</sub>  | Supply voltage                    | Absolute                                                            | 1.71              |                   | 3.6               | V    |       |

| $\Delta V_{DDA}$  | Supply voltage                    | Delta to V <sub>DD</sub> (V <sub>DD</sub> -<br>V <sub>DDA</sub> )   | -100              | 0                 | +100              | mV   | 2     |

| $\Delta V_{SSA}$  | Ground voltage                    | Delta to V <sub>SS</sub> (V <sub>SS</sub> -<br>V <sub>SSA</sub> )   | -100              | 0                 | +100              | mV   | 2     |

| V <sub>REFH</sub> | ADC reference voltage high        |                                                                     | 1.13              | V <sub>DDA</sub>  | V <sub>DDA</sub>  | V    |       |

| V <sub>REFL</sub> | Reference<br>voltage low          |                                                                     | V <sub>SSA</sub>  | V <sub>SSA</sub>  | V <sub>SSA</sub>  | V    |       |

| V <sub>ADIN</sub> | Input voltage                     |                                                                     | V <sub>REFL</sub> | _                 | V <sub>REFH</sub> | V    |       |

| C <sub>ADIN</sub> | Input                             | 16 bit modes                                                        | _                 | 8                 | 10                | pF   |       |

|                   | capacitance                       | <ul> <li>8/10/12 bit<br/>modes</li> </ul>                           | _                 | 4                 | 5                 |      |       |

| R <sub>ADIN</sub> | Input resistance                  |                                                                     |                   | 2                 | 5                 | kΩ   |       |

| R <sub>AS</sub>   | Analog source<br>resistance       | 13/12 bit modes<br>f <sub>ADCK</sub> < 4MHz                         |                   | _                 | 5                 | kΩ   | 3     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency | ≤ 13 bit modes                                                      | 1.0               |                   | 18.0              | MHz  | 4     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency | 16 bit modes                                                        | 2.0               |                   | 12.0              | MHz  | 4     |

| C <sub>rate</sub> | ADC conversion                    | ≤ 13 bit modes                                                      |                   |                   |                   |      | 5     |

|                   | rate                              | No ADC hardware averaging                                           | 20.000            | —                 | 818.330           | Ksps |       |

|                   |                                   | Continuous<br>conversions enabled,<br>subsequent conversion<br>time |                   |                   |                   |      |       |

## 6.6.1.1 16-bit ADC operating conditions Table 23. 16-bit ADC operating conditions

| Symbol            | Description    | Conditions                                                          | Min.   | Typ. <sup>1</sup> | Max.    | Unit | Notes |

|-------------------|----------------|---------------------------------------------------------------------|--------|-------------------|---------|------|-------|

| C <sub>rate</sub> | ADC conversion | 16 bit modes                                                        |        |                   |         |      | 5     |

|                   | rate           | No ADC hardware averaging                                           | 37.037 | —                 | 461.467 | Ksps |       |

|                   |                | Continuous<br>conversions enabled,<br>subsequent conversion<br>time |        |                   |         |      |       |

Table 23. 16-bit ADC operating conditions (continued)

- Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- 2. DC potential difference.

- 3. This resistance is external to MCU. The analog source resistance should be kept as low as possible in order to achieve the best results. The results in this datasheet were derived from a system which has <8  $\Omega$  analog source resistance. The R<sub>AS</sub>/ C<sub>AS</sub> time constant should be kept to <1ns.

- 4. To use the maximum ADC conversion clock frequency, the ADHSC bit should be set and the ADLPC bit should be clear.

- 5. For guidelines and examples of conversion rate calculation, download the ADC calculator tool: http://cache.freescale.com/ files/soft\_dev\_tools/software/app\_software/converters/ADC\_CALCULATOR\_CNV.zip?fpsp=1

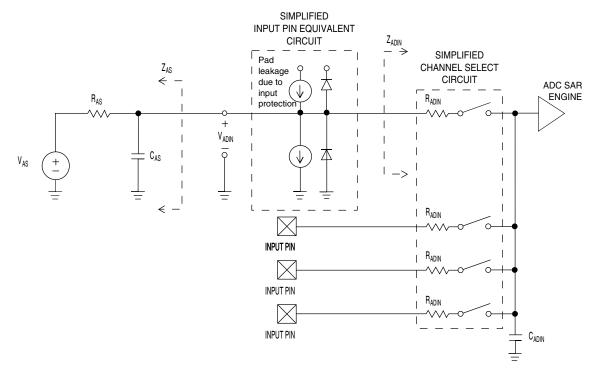

Figure 10. ADC input impedance equivalency diagram

## 6.6.1.2 16-bit ADC electrical characteristics Table 24. 16-bit ADC characteristics (V<sub>REFH</sub> = V<sub>DDA</sub>, V<sub>REFL</sub> = V<sub>SSA</sub>)

| Symbol               | Description    | Conditions <sup>1</sup> | Min.  | Typ. <sup>2</sup> | Max. | Unit | Notes |

|----------------------|----------------|-------------------------|-------|-------------------|------|------|-------|

| I <sub>DDA_ADC</sub> | Supply current |                         | 0.215 | —                 | 1.7  | mA   | 3     |

Table continues on the next page ...

| Symbol             | Description                        | Conditions <sup>1</sup>              | Min.         | Typ. <sup>2</sup> | Max.            | Unit             | Notes                   |

|--------------------|------------------------------------|--------------------------------------|--------------|-------------------|-----------------|------------------|-------------------------|

|                    | ADC                                | ADLPC=1, ADHSC=0                     | 1.2          | 2.4               | 3.9             | MHz              | t <sub>ADACK</sub> = 1/ |

|                    | asynchronous<br>clock source       | ADLPC=1, ADHSC=1                     | 3.0          | 4.0               | 7.3             | MHz              | f <sub>ADACK</sub>      |

| f <sub>ADACK</sub> |                                    | ADLPC=0, ADHSC=0                     | 2.4          | 5.2               | 6.1             | MHz              |                         |

|                    |                                    | ADLPC=0, ADHSC=1                     | 4.4          | 6.2               | 9.5             | MHz              |                         |

|                    | Sample Time                        | See Reference Manual chapte          | r for sample | times             | 1               |                  |                         |

| TUE                | Total unadjusted                   | 12 bit modes                         | _            | ±4                | ±6.8            | LSB <sup>4</sup> | 5                       |

|                    | error                              | • <12 bit modes                      | _            | ±1.4              | ±2.1            |                  |                         |

| DNL                | Differential non-<br>linearity     | 12 bit modes                         | _            | ±0.7              | -1.1 to<br>+1.9 | LSB <sup>4</sup> | 5                       |

|                    |                                    | • <12 bit modes                      | _            | ±0.2              | -0.3 to 0.5     |                  |                         |

| INL                | Integral non-<br>linearity         | 12 bit modes                         | _            | ±1.0              | -2.7 to<br>+1.9 | LSB <sup>4</sup> | 5                       |

|                    |                                    | <ul> <li>&lt;12 bit modes</li> </ul> | _            | ±0.5              | -0.7 to<br>+0.5 |                  |                         |

| E <sub>FS</sub>    | Full-scale error                   | 12 bit modes                         | —            | -4                | -5.4            | LSB <sup>4</sup> | V <sub>ADIN</sub> =     |

|                    |                                    | • <12 bit modes                      | -            | -1.4              | -1.8            |                  | V <sub>DDA</sub>        |

|                    |                                    |                                      |              |                   |                 |                  | 5                       |

| EQ                 | Quantization<br>error              | 16 bit modes                         | -            | -1 to 0           |                 | LSB <sup>4</sup> |                         |

|                    | enor                               | <ul> <li>≤13 bit modes</li> </ul>    | _            | _                 | ±0.5            |                  |                         |

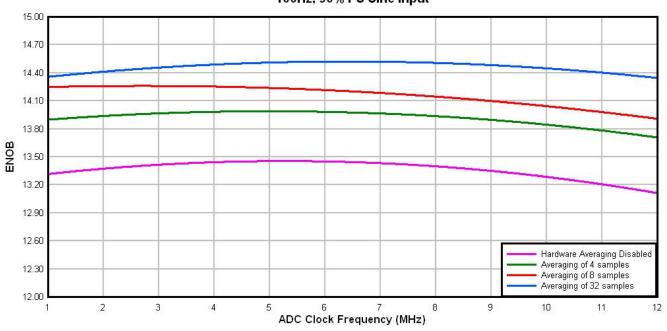

| ENOB               | Effective number                   | 16 bit differential mode             |              |                   |                 |                  | 6                       |

|                    | of bits                            | • Avg=32                             | 12.8         | 14.5              |                 | bits             |                         |

|                    |                                    | • Avg=4                              | 11.9         | 13.8              | _               | bits             |                         |

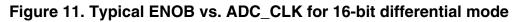

|                    |                                    | 16 bit single-ended mode             |              |                   |                 |                  |                         |

|                    |                                    | • Avg=32                             | 12.2         | 13.9              |                 | bits             |                         |

|                    |                                    | • Avg=4                              | 11.4         | 13.1              | _               | bits             |                         |

| SINAD              | Signal-to-noise<br>plus distortion | See ENOB                             | 6.02         | 2 × ENOB +        | 1.76            | dB               |                         |

| THD                | Total harmonic                     | 16 bit differential mode             |              |                   |                 |                  | 7                       |

|                    | distortion                         | • Avg=32                             | _            | -94               | -               | dB               |                         |

|                    |                                    | 16 bit single-ended mode<br>• Avg=32 | _            | -85               | _               | dB               |                         |

# Table 24. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

Table continues on the next page...

Peripheral operating requirements and behaviors

Typical ADC 16-bit Differential ENOB vs ADC Clock 100Hz, 90% FS Sine Input

Typical ADC 16-bit Single-Ended ENOB vs ADC Clock 100Hz, 90% FS Sine Input

Figure 12. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

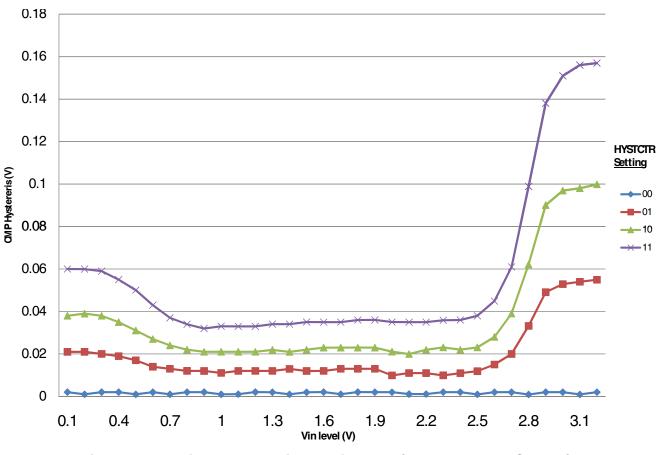

Figure 14. Typical hysteresis vs. Vin level (VDD=3.3V, PMODE=1)

## 6.6.3 Voltage reference electrical specifications

| Symbol           | Description             | Min. | Max. | Unit | Notes |

|------------------|-------------------------|------|------|------|-------|

| V <sub>DDA</sub> | Supply voltage          | 1.71 | 3.6  | V    |       |

| T <sub>A</sub>   | Temperature             | -40  | 105  | °C   |       |

| CL               | Output load capacitance | 1(   | 00   | nF   | 1, 2  |

1. C<sub>L</sub> must be connected to VREF\_OUT if the VREF\_OUT functionality is being used for either an internal or external reference.

The load capacitance should not exceed +/-25% of the nominal specified C<sub>L</sub> value over the operating temperature range of the device.

| Symbol           | Description                                                                                | Min.   | Тур.  | Max.   | Unit | Notes |

|------------------|--------------------------------------------------------------------------------------------|--------|-------|--------|------|-------|

| V <sub>out</sub> | Voltage reference output with factory trim at nominal $V_{\text{DDA}}$ and temperature=25C | 1.1915 | 1.195 | 1.1977 | V    |       |

Table 27. VREF full-range operating behaviors

Table continues on the next page...

| Symbol Description                                                           |                                                                  | Min. | Тур. | Max.   | Unit | Notes |  |

|------------------------------------------------------------------------------|------------------------------------------------------------------|------|------|--------|------|-------|--|

| V <sub>out</sub>                                                             | Voltage reference output — factory trim                          |      | —    | 1.2376 | V    |       |  |

| V <sub>out</sub>                                                             | vut Voltage reference output — user trim                         |      | _    | 1.197  | V    |       |  |

| V <sub>step</sub>                                                            | Voltage reference trim step                                      | _    | 0.5  | —      | mV   |       |  |

| V <sub>tdrift</sub>                                                          | Temperature drift (Vmax -Vmin across the full temperature range) | _    | —    | 80     | mV   |       |  |

| I <sub>bg</sub>                                                              | Bandgap only current                                             | _    | _    | 80     | μA   | 1     |  |

| I <sub>lp</sub>                                                              | Low-power buffer current                                         | _    | _    | 360    | uA   | 1     |  |

| I <sub>hp</sub>                                                              | High-power buffer current                                        | _    | —    | 1      | mA   | 1     |  |

| $\Delta V_{LOAD}$                                                            | Load regulation                                                  |      |      |        | μV   | 1, 2  |  |

|                                                                              | • current = ± 1.0 mA                                             |      | 200  | _      |      |       |  |

| T <sub>stup</sub>                                                            | Buffer startup time                                              | —    |      | 100    | μs   |       |  |

| V <sub>vdrift</sub> Voltage drift (Vmax -Vmin across the full voltage range) |                                                                  | _    | 2    | —      | mV   | 1     |  |

#### Table 27. VREF full-range operating behaviors (continued)

1. See the chip's Reference Manual for the appropriate settings of the VREF Status and Control register.

2. Load regulation voltage is the difference between the VREF\_OUT voltage with no load vs. voltage with defined load

## Table 28. VREF limited-range operating requirements

| Symbo          | Description | Min. | Max. | Unit | Notes |

|----------------|-------------|------|------|------|-------|

| T <sub>A</sub> | Temperature | 0    | 50   | °C   |       |

## Table 29. VREF limited-range operating behaviors

|   | Symbol           | Description                                | Min.  | Max.  | Unit | Notes |

|---|------------------|--------------------------------------------|-------|-------|------|-------|

| ſ | V <sub>out</sub> | Voltage reference output with factory trim | 1.173 | 1.225 | V    |       |

# 6.7 Timers

See General switching specifications.

# 6.8 Communication interfaces

# 6.8.5.1 Normal Run, Wait and Stop mode performance over the full operating voltage range

This section provides the operating performance over the full operating voltage for the device in Normal Run, Wait and Stop modes.

| Num. | Characteristic                                                    | Min. | Max. | Unit        |  |

|------|-------------------------------------------------------------------|------|------|-------------|--|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |  |

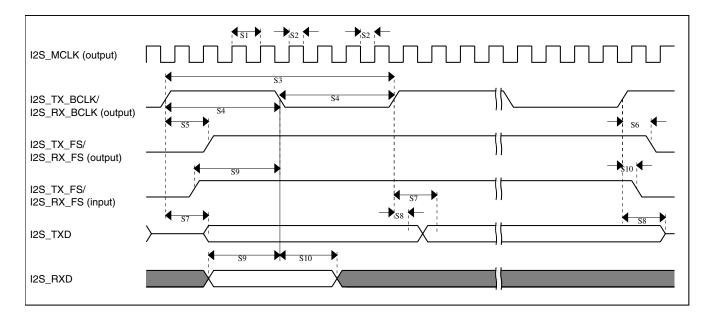

| S1   | I2S_MCLK cycle time                                               | 40   | _    | ns          |  |

| S2   | I2S_MCLK pulse width high/low                                     | 45%  | 55%  | MCLK period |  |

| S3   | I2S_TX_BCLK/I2S_RX_BCLK cycle time (output)                       | 80   | _    | ns          |  |

| S4   | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low                      | 45%  | 55%  | BCLK period |  |

| S5   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output valid   | _    | 15   | ns          |  |

| S6   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output invalid | 0    | -    | ns          |  |

| S7   | I2S_TX_BCLK to I2S_TXD valid                                      | —    | 15   | ns          |  |

| S8   | I2S_TX_BCLK to I2S_TXD invalid                                    | 0    | —    | ns          |  |

| S9   | I2S_RXD/I2S_RX_FS input setup before<br>I2S_RX_BCLK               | 25   | -    | ns          |  |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK                    | 0    | —    | ns          |  |

Table 34. I2S/SAI master mode timing

Figure 19. I2S/SAI timing — master modes

K10 Sub-Family Data Sheet, Rev. 4 5/2012.

#### **Revision History**

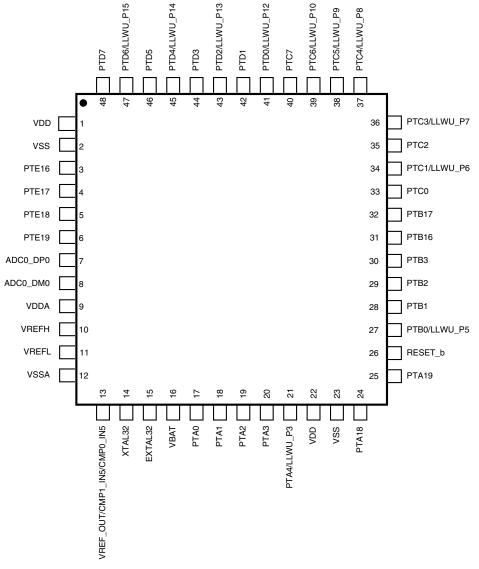

Figure 23. K10 48 LQFP/QFN Pinout Diagram

# 9 Revision History

The following table provides a revision history for this document.

Table 39. Revision History

| Rev. No. | Date   | Substantial Changes    |

|----------|--------|------------------------|

| 2        | 2/2012 | Initial public release |