Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 600                                                          |

| Number of Logic Elements/Cells | 2700                                                         |

| Total RAM Bits                 | 40960                                                        |

| Number of I/O                  | 146                                                          |

| Number of Gates                | 100000                                                       |

| Voltage - Supply               | 1.71V ~ 1.89V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 208-BFQFP                                                    |

| Supplier Device Package        | 208-PQFP (28x28)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s100e-6pq208c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Spartan-IIE Product Availability**

Table 2 shows the maximum user I/Os available on the device and the number of user I/Os available for each device/package combination.

Table 2: Spartan-IIE FPGA User I/O Chart

|          |                     | Available User I/O According to Package Type |                 |                 |                 |                 |  |

|----------|---------------------|----------------------------------------------|-----------------|-----------------|-----------------|-----------------|--|

| Device   | Maximum<br>User I/O | TQ144<br>TQG144                              | PQ208<br>PQG208 | FT256<br>FTG256 | FG456<br>FGG456 | FG676<br>FGG676 |  |

| XC2S50E  | 182                 | 102                                          | 146             | 182             | -               | -               |  |

| XC2S100E | 202                 | 102                                          | 146             | 182             | 202             | -               |  |

| XC2S150E | 265                 | -                                            | 146             | 182             | 265             | -               |  |

| XC2S200E | 289                 | -                                            | 146             | 182             | 289             | -               |  |

| XC2S300E | 329                 | -                                            | 146             | 182             | 329             | -               |  |

| XC2S400E | 410                 | -                                            | -               | 182             | 329             | 410             |  |

| XC2S600E | 514                 | -                                            | -               | -               | 329             | 514             |  |

#### Notes:

<sup>1.</sup> User I/O counts include the four global clock/user input pins.

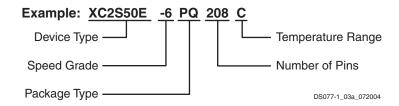

## **Ordering Information**

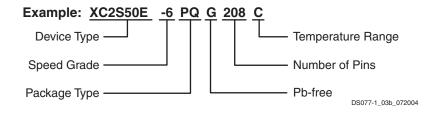

Spartan-IIE devices are available in both standard and Pb-free packaging options for all device/package combinations. The Pb-free packages include a special "G" character in the ordering code.

#### Standard Packaging

#### Pb-Free Packaging

#### **Device Ordering Options**

| Device   |    | Speed Grade                       |  |  |  |

|----------|----|-----------------------------------|--|--|--|

| XC2S50E  | -6 | Standard Performance              |  |  |  |

| XC2S100E | -7 | Higher Performance <sup>(1)</sup> |  |  |  |

| XC2S150E |    |                                   |  |  |  |

| XC2S200E |    |                                   |  |  |  |

| XC2S300E |    |                                   |  |  |  |

| XC2S400E |    |                                   |  |  |  |

| Packag   | Package Type / Number of Pins |  |  |  |  |  |

|----------|-------------------------------|--|--|--|--|--|

| TQ(G)144 | 144-pin Plastic Thin QFP      |  |  |  |  |  |

| PQ(G)208 | 208-pin Plastic QFP           |  |  |  |  |  |

| FT(G)256 | 256-ball Fine Pitch BGA       |  |  |  |  |  |

| FG(G)456 | 456-ball Fine Pitch BGA       |  |  |  |  |  |

| FG(G)676 | 676-ball Fine Pitch BGA       |  |  |  |  |  |

| Temperature Range (T <sub>J</sub> ) <sup>(2)</sup> |                 |  |  |  |

|----------------------------------------------------|-----------------|--|--|--|

| C = Commercial 0°C to +85°C                        |                 |  |  |  |

| I = Industrial                                     | -40°C to +100°C |  |  |  |

#### Notes:

XC2S600E

- The -7 speed grade is exclusively available in the Commercial temperature range.

- See www.xilinx.com for information on automotive temperature range devices.

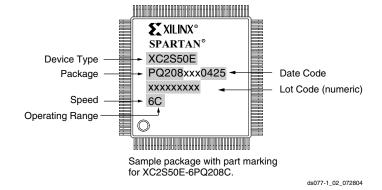

### **Device Part Marking**

Figure 2 is a top marking example for Spartan-IIE FPGAs in the quad-flat packages. The markings for BGA packages are nearly identical to those for the quad-flat packages, except that the marking is rotated with respect to the ball A1 indicator.

The "7C" and "6I" Speed Grade/Temperature Range part combinations may be dual marked as "7C/6I". Devices with the dual mark can be used as either -7C or -6I devices. Devices with a single mark are only guaranteed for the marked speed grade and temperature range.

Figure 2: Spartan-IIE QFP Marking Example

# — OBSOLETE — OBSOLETE — OBSOLETE —

Spartan-IIE FPGA Family: Introduction and Ordering Information

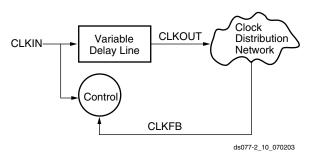

edges arrive at internal flip-flops in synchronism with clock edges arriving at the input.

Figure 12: Delay-Locked Loop Block Diagram

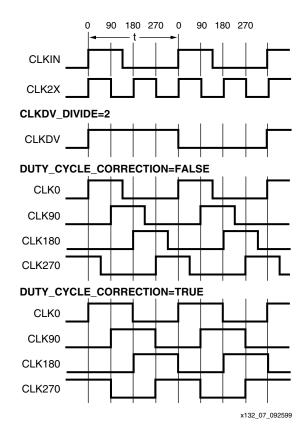

In addition to eliminating clock-distribution delay, the DLL provides advanced control of multiple clock domains. The DLL provides four quadrature phases of the source clock, can double the clock, or divide the clock by 1.5, 2, 2.5, 3, 4, 5, 8, or 16. The phase-shifted output have optional duty-cycle correction (Figure 13).

Figure 13: DLL Output Characteristics

The DLL also operates as a clock mirror. By driving the output from a DLL off-chip and then back on again, the DLL can be used to deskew a board level clock among multiple Spartan-IIE devices.

In order to guarantee that the system clock is operating correctly prior to the FPGA starting up after configuration, the DLL can delay the completion of the configuration process until after it has achieved lock. If the DLL uses external feedback, apply a reset after startup to ensure consistent locking to the external signal. See Xilinx Application Note XAPP174 for more information on DLLs.

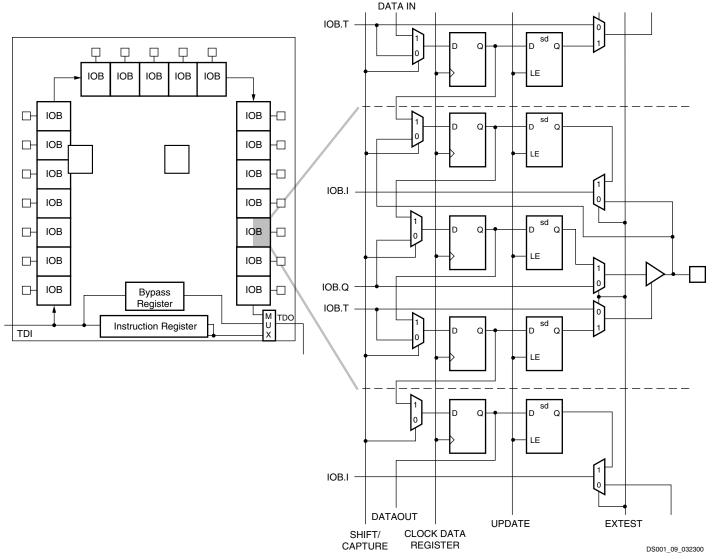

#### **Boundary Scan**

Spartan-IIE devices support all the mandatory boundary-scan instructions specified in the IEEE standard 1149.1. A Test Access Port (TAP) and registers are provided that implement the EXTEST, INTEST, SAMPLE/PRELOAD, BYPASS, IDCODE, and HIGHZ instructions. The TAP also supports two USERCODE instructions, internal scan chains, and configuration/readback of the device.

The TAP uses dedicated package pins that always operate using LVTTL. For TDO to operate using LVTTL, the  $V_{CCO}$  for Bank 2 must be 3.3V. Otherwise, TDO switches rail-to-rail between ground and  $V_{CCO}$ . The boundary-scan input pins (TDI, TMS, TCK) do not have a  $V_{CCO}$  requirement and operate with either 2.5V or 3.3V input signaling levels. TDI, TMS, and TCK hava a default internal weak pull-up resistor, and TDO has no default resistor. Bitstream options allow setting any of the four TAP pins to have an internal pull-up, pull-down, or neither.

Boundary-scan operation is independent of individual IOB configurations, and unaffected by package type. All IOBs, including unbonded ones, are treated as independent 3-state bidirectional pins in a single scan chain. Retention of the bidirectional test capability after configuration facilitates the testing of external interconnections.

Table 8 lists the boundary-scan instructions supported in Spartan-IIE FPGAs. Internal signals can be captured during EXTEST by connecting them to unbonded or unused IOBs. They may also be connected to the unused outputs of IOBs defined as unidirectional input pins.

Table 8: Boundary-Scan Instructions

| Boundary-Scan<br>Command | Binary<br>Code[4:0] | Description                                          |

|--------------------------|---------------------|------------------------------------------------------|

| EXTEST                   | 00000               | Enables boundary-scan EXTEST operation               |

| SAMPLE/<br>PRELOAD       | 00001               | Enables boundary-scan<br>SAMPLE/PRELOAD<br>operation |

| USER1                    | 00010               | Access user-defined register 1                       |

| USER2                    | 00011               | Access user-defined register 2                       |

| CFG_OUT                  | 00100               | Access the configuration bus for Readback            |

| CFG_IN                   | 00101               | Access the configuration bus for Configuration       |

Table 8: Boundary-Scan Instructions (Continued)

| Boundary-Scan<br>Command | Binary<br>Code[4:0] | Description                                                   |

|--------------------------|---------------------|---------------------------------------------------------------|

| INTEST                   | 00111               | Enables boundary-scan INTEST operation                        |

| USERCODE                 | 01000               | Enables shifting out<br>USER code                             |

| IDCODE                   | 01001               | Enables shifting out of ID Code                               |

| HIGHZ                    | 01010               | Disables output pins<br>while enabling the<br>Bypass Register |

| JSTART                   | 01100               | Clock the start-up<br>sequence when<br>StartupClk is TCK      |

| BYPASS                   | 11111               | Enables BYPASS                                                |

| RESERVED                 | All other codes     | Xilinx reserved instructions                                  |

The public boundary-scan instructions are available prior to configuration, except for USER1 and USER2. After configuration, the public instructions remain available together with any USERCODE instructions installed during the configuration. While the SAMPLE/PRELOAD and BYPASS instructions are available during configuration, it is recommended that boundary-scan operations not be performed during this transitional period.

In addition to the test instructions outlined above, the boundary-scan circuitry can be used to configure the FPGA, and also to read back the configuration data.

To facilitate internal scan chains, the User Register provides three outputs (Reset, Update, and Shift) that represent the corresponding states in the boundary-scan internal state machine.

Figure 14 is a diagram of the Spartan-IIE family boundary scan logic. It includes three bits of Data Register per IOB, the IEEE 1149.1 Test Access Port controller, and the Instruction Register with decodes.

Figure 14: Spartan-IIE Family Boundary Scan Logic

design, thus allowing the most convenient entry method to be used for each portion of the design.

### **Design Implementation**

The place-and-route tools automatically provide the implementation flow described in this section. The partitioner takes the EDIF netlist for the design and maps the logic into the architectural resources of the FPGA (CLBs and IOBs, for example). The placer then determines the best locations for these blocks based on their interconnections and the desired performance. Finally, the router interconnects the blocks.

The algorithms support fully automatic implementation of most designs. For demanding applications, however, the user can exercise various degrees of control over the process. User partitioning, placement, and routing information is optionally specified during the design-entry process. The implementation of highly structured designs can benefit greatly from basic floorplanning.

The implementation software incorporates timing-driven placement and routing. Designers specify timing requirements along entire paths during design entry. The timing path analysis routines then recognize these user-specified requirements and accommodate them.

Timing requirements are entered in a form directly relating to the system requirements, such as the targeted clock frequency, or the maximum allowable delay between two registers. In this way, the overall performance of the system along entire signal paths is automatically tailored to user-generated specifications. Specific timing information for individual nets is unnecessary.

#### **Design Verification**

In addition to conventional software simulation, FPGA users can use in-circuit debugging techniques. Because Xilinx devices are infinitely reprogrammable, designs can be verified in real time without the need for extensive sets of software simulation vectors.

The development system supports both software simulation and in-circuit debugging techniques. For simulation, the system extracts the post-layout timing information from the design database, and back-annotates this information into the netlist for use by the simulator. Alternatively, the user can verify timing-critical portions of the design using the static timing analyzer.

For in-circuit debugging, Xilinx offers a download cable, which connects the FPGA in the target system to a PC or workstation. After downloading the design into the FPGA, the designer can read back the contents of the flip-flops, and so observe the internal logic state. Simple modifications can be downloaded into the system in a matter of minutes.

## Configuration

Configuration is the process by which the bitstream of a design, as generated by the Xilinx development software, is loaded into the internal configuration memory of the FPGA. Spartan-IIE devices support both serial configuration, using the master/slave serial and JTAG modes, as well as byte-wide configuration employing the Slave Parallel mode.

#### **Configuration File**

Spartan-IIE devices are configured by sequentially loading frames of data that have been concatenated into a configuration file. Table 10 shows how much nonvolatile storage space is needed for Spartan-IIE devices.

It is important to note that, while a PROM is commonly used to store configuration data before loading them into the FPGA, it is by no means required. Any of a number of different kinds of under populated nonvolatile storage already available either on or off the board (for example, hard drives, FLASH cards, and so on) can be used.

Table 10: Spartan-IIE Configuration File Size

| Device   | Configuration File Size (Bits) |

|----------|--------------------------------|

| XC2S50E  | 630,048                        |

| XC2S100E | 863,840                        |

| XC2S150E | 1,134,496                      |

| XC2S200E | 1,442,016                      |

| XC2S300E | 1,875,648                      |

| XC2S400E | 2,693,440                      |

| XC2S600E | 3,961,632                      |

#### **Modes**

Spartan-IIE devices support the following four configuration modes:

- Slave Serial mode

- Master Serial mode

- Slave Parallel mode

- Boundary-scan mode

The Configuration mode pins (M2, M1, M0) select among these configuration modes with the option in each case of having the IOB pins either pulled up or left floating prior to the end of configuration. The selection codes are listed in Table 11.

Configuration through the boundary-scan port is always available, independent of the mode selection. Selecting the boundary-scan mode simply turns off the other modes. The three mode pins have internal pull-up resistors, and default to a logic High if left unconnected.

**Table 11: Configuration Modes**

| Configuration Mode  | Preconfiguration Pull-ups | МО | M1 | M2 | CCLK<br>Direction | Data Width | Serial D <sub>OUT</sub> |

|---------------------|---------------------------|----|----|----|-------------------|------------|-------------------------|

| Master Serial mode  | No                        | 0  | 0  | 0  | Out               | 1          | Yes                     |

|                     | Yes                       | 0  | 0  | 1  |                   |            |                         |

| Slave Parallel mode | Yes                       | 0  | 1  | 0  | In                | 8          | No                      |

| (SelectMAP)         | No                        | 0  | 1  | 1  |                   |            |                         |

| Boundary-Scan mode  | Yes                       | 1  | 0  | 0  | N/A               | 1          | No                      |

|                     | No                        | 1  | 0  | 1  |                   |            |                         |

| Slave Serial mode   | Yes                       | 1  | 1  | 0  | In                | 1          | Yes                     |

|                     | No                        | 1  | 1  | 1  |                   |            |                         |

#### Notes:

- During power-on and throughout configuration, the I/O drivers will be in a high-impedance state. After configuration, all unused I/Os (those not assigned signals) will remain in a high-impedance state. Pins used as outputs may pulse High at the end of configuration (see <u>Answer 10504</u>).

- 2. If the Mode pins are set for preconfiguration pull-ups, those resistors go into effect once the rising edge of INIT samples the Mode pins. They will stay in effect until GTS is released during startup, after which the UnusedPin bitstream generator option will determine whether the unused I/Os have a pull-up, pull-down, or no resistor.

#### **Signals**

There are two kinds of pins that are used to configure Spartan-IIE devices: Dedicated pins perform only specific configuration-related functions; the other pins can serve as general purpose I/Os once user operation has begun.

The dedicated pins comprise the mode pins (M2, M1, M0), the configuration clock pin (CCLK), the PROGRAM pin, the DONE pin and the boundary-scan pins (TDI, TDO, TMS, TCK). Depending on the selected configuration mode, CCLK may be an output generated by the FPGA, or may be generated externally, and provided to the FPGA as an input.

Note that some configuration pins can act as outputs. For correct operation, these pins require a  $V_{CCO}$  of 3.3V to drive an LVTTL signal or 2.5V to drive an LVCMOS signal. All the relevant pins fall in banks 2 or 3. The  $\overline{\mbox{CS}}$  and  $\overline{\mbox{WRITE}}$  pins for Slave Parallel mode are located in bank 1.

For a more detailed description than that given below, see *Module 1* and <u>XAPP176</u>, *Configuration and Readback of the Spartan-II and Spartan-IIE FPGA Families*.

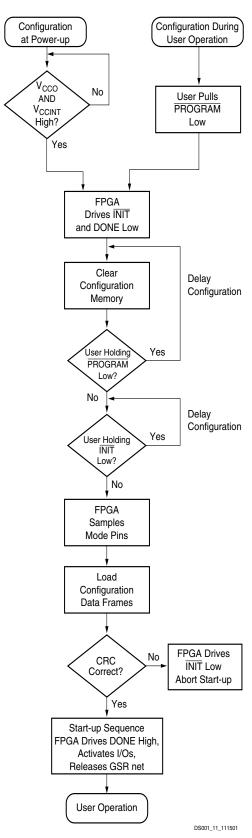

#### The Process

The sequence of steps necessary to configure Spartan-IIE devices are shown in Figure 16. The overall flow can be divided into three different phases.

- Initiating configuration

- Configuration memory clear

- Loading data frames

- Start-up

The memory clearing and start-up phases are the same for all configuration modes; however, the steps for the loading of data frames are different. Thus, the details for data frame loading are described separately in the sections devoted to each mode.

#### **Initiating Configuration**

There are two different ways to initiate the configuration process: applying power to the device or asserting the PROGRAM input.

Configuration on power-up occurs automatically unless it is delayed by the user, as described in a separate section below. The waveform for configuration on power-up is shown in Configuration Switching Characteristics, page 48. Before configuration can begin,  $V_{\rm CCO}$  Bank 2 must be greater than 1.0V. Furthermore, all  $V_{\rm CCINT}$  power pins must be connected to a 1.8V supply. For more information on delaying configuration, see Clearing Configuration Memory, page 23.

Once in user operation, the device can be re-configured simply by pulling the PROGRAM pin Low. The device acknowledges the beginning of the configuration process by driving DONE Low, then enters the memory-clearing phase.

Figure 16: Configuration Flow Diagram

#### **Clearing Configuration Memory**

The device indicates that clearing the configuration memory is in progress by driving INIT Low.

#### **Delaying Configuration**

At this time, the user can delay configuration by holding either  $\overline{PROGRAM}$  or  $\overline{INIT}$  Low, which causes the device to remain in the memory clearing phase. Note that the bidirectional  $\overline{INIT}$  line is driving a Low logic level during memory clearing. Thus, to avoid contention, use an open-drain driver to keep  $\overline{INIT}$  Low.

With no delay in force, the device indicates that the memory is completely clear by driving  $\overline{\text{INIT}}$  High. The FPGA samples its mode pins on this Low-to-High transition.

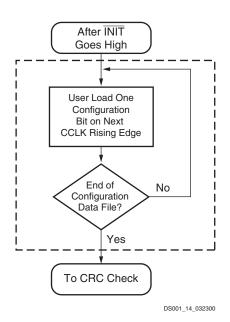

#### Loading Configuration Data

Once INIT is High, the user can begin loading configuration data frames into the device. The details of loading the configuration data are discussed in the sections treating the configuration modes individually. The sequence of operations necessary to load configuration data using the serial modes is shown in Figure 18. Loading data using the Slave Parallel mode is shown in Figure 21, page 28.

#### **CRC Error Checking**

After the loading of configuration data, a CRC value embedded in the configuration file is checked against a CRC value calculated within the FPGA. If the CRC values do not match, the FPGA drives  $\overline{\text{INIT}}$  Low to indicate that an error has occurred and configuration is aborted. Note that attempting to load an incorrect bitstream causes configuration to fail and can damage the device.

To reconfigure the device, the PROGRAM pin should be asserted to reset the configuration logic. Recycling power also resets the FPGA for configuration. See Clearing Configuration Memory.

#### Start-up

The start-up sequence oversees the transition of the FPGA from the configuration state to full user operation. A match of CRC values, indicating a successful loading of the configuration data, initiates the sequence.

Figure 18: Loading Serial Mode Configuration Data

#### Slave Serial Mode

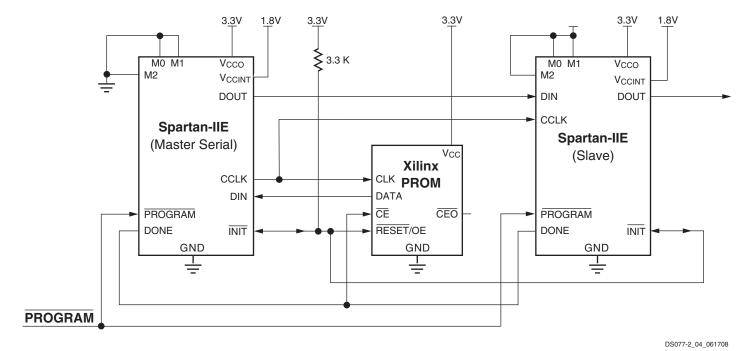

In Slave Serial mode, the FPGA's CCLK pin is driven by an external source, allowing the FPGA to be configured from other logic devices such as microprocessors or in a daisy-chain configuration. Figure 19 shows connections for a Master Serial FPGA configuring a Slave Serial FPGA

from a PROM. A Spartan-IIE device in slave serial mode should be connected as shown for the third device from the left. Slave Serial mode is selected by a <11x> on the mode pins (M0, M1, M2). The weak pull-ups on the mode pins make slave serial the default mode if the pins are left unconnected.

The serial bitstream must be setup at the DIN input pin a short time before each rising edge of an externally generated CCLK.

Timing for Slave Serial mode is shown in Figure 24, page 49.

#### Daisy Chain

Multiple FPGAs in Slave Serial mode can be daisy-chained for configuration from a single source. After an FPGA is configured, data for the next device is sent to the DOUT pin. Data on the DOUT pin changes on the rising edge of CCLK. Note that DOUT changes on the falling edge of CCLK for some Xilinx families but mixed daisy chains are allowed. Configuration must be delayed until  $\overline{\text{INIT}}$  pins of all daisy-chained FPGAs are High. For more information, see Start-up, page 23.

The maximum amount of data that can be sent to the DOUT pin for a serial daisy chain is 2<sup>20</sup>-1 (1,048,575) 32-bit words, or 33,554,400 bits, which is approximately 8 XC2S600E bitstreams. The configuration bitstream of downstream devices is limited to this size.

#### Notes:

1. If the DriveDone configuration option is not active for any of the FPGAs, pull up DONE with a 330 $\Omega$  resistor.

Figure 19: Master/Slave Serial Configuration Circuit Diagram

|                                              |      |                             | All De |     |       |

|----------------------------------------------|------|-----------------------------|--------|-----|-------|

| Symbol                                       |      | Description                 | Min    | Max | Units |

| T <sub>SMDCC</sub> /<br>T <sub>SMCCD</sub>   |      | D0-D7 setup/hold            | 5/1    | -   | ns    |

| T <sub>SMCSCC</sub> /<br>T <sub>SMCCCS</sub> |      | CS setup/hold               | 7/1    | -   | ns    |

| T <sub>SMCCW</sub> / T <sub>SMWCC</sub>      | CCLK | WRITE setup/hold            | 7/1    | -   | ns    |

| T <sub>SMCKBY</sub>                          |      | BUSY propagation delay      | -      | 12  | ns    |

| F <sub>CC</sub>                              |      | Frequency                   | -      | 66  | MHz   |

| F <sub>CCNH</sub>                            |      | Frequency with no handshake | -      | 50  | MHz   |

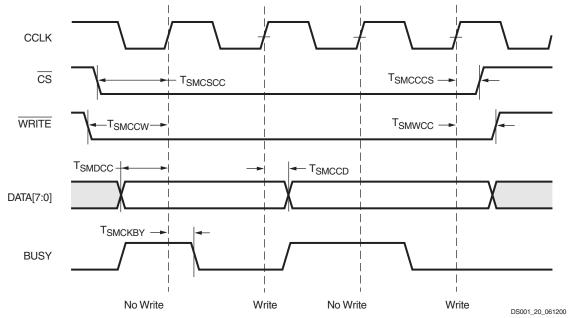

Figure 26: Slave Parallel (SelectMAP) Mode Write Timing

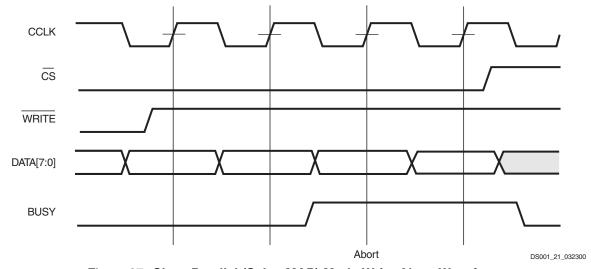

Figure 27: Slave Parallel (SelectMAP) Mode Write Abort Waveforms

Spartan-IIE FPGA Family: DC and Switching Characteristics

# **Revision History**

| Date       | Version | Description                                                                                                                                                                                                                                                    |

|------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/15/2001 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                        |

| 06/28/2002 | 1.1     | Added -7 speed grade and extended DLL specs to Industrial.                                                                                                                                                                                                     |

| 11/18/2002 | 2.0     | Added XC2S400E and XC2S600E. Added minimum specifications. Added reference to XAPP450 for Power-On Requirements. Removed Preliminary designation.                                                                                                              |

| 07/09/2003 | 2.1     | Added I <sub>CCINTQ</sub> typical values. Reduced ICCPO power-on current requirements. Relaxed TCCPO power-on ramp requirements. Added IHSPO to describe current in hot-swap applications. Updated TPSFD / TPHFD description to indicate use of delay element. |

| 06/18/2008 | 2.3     | Updated I/O measurement thresholds. Updated all modules for continuous page, figure, and table numbering. Updated links. Synchronized all modules to v2.3.                                                                                                     |

| 08/09/2013 | 3.0     | This product is obsolete/discontinued per XCN12026.                                                                                                                                                                                                            |

# Low Voltage Differential Signals (LVDS and LVPECL)

The Spartan-IIE family features low-voltage differential signaling (LVDS and LVPECL). Each signal utilizes two pins on the Spartan-IIE device, known as differential pin pairs. Each differential pin pair has a Positive (P) and a Negative (N) pin. These pairs are labeled in the following manner.

I/O, L#[P/N][-/\_Y/\_YY]

where

L = LVDS or LVPECL pin

# = Pin pair number

P = Positive

N = Negative

\_Y = Asynchronous output allowed (device-dependent)

\_YY = Asynchronous output allowed (all devices)

# **Available Differential Pairs According to Package Type**

| Device   | TQ144 | PQ208 | FT256 | FG456 | FG676 |

|----------|-------|-------|-------|-------|-------|

| XC2S50E  | 28    | 50    | 83    | -     | -     |

| XC2S100E | 28    | 50    | 83    | 86    | -     |

| XC2S150E | -     | 50    | 83    | 114   | -     |

| XC2S200E | -     | 50    | 83    | 120   | -     |

| XC2S300E | -     | 50    | 83    | 120   | -     |

| XC2S400E | -     | -     | 83    | 120   | 172   |

| XC2S600E | -     | -     | 1     | 120   | 205   |

## **Synchronous or Asynchronous**

I/O pins for differential signals can either be synchronous or asynchronous, input or output. Differential signaling requires the pins of each pair to switch simultaneously. If the output signals driving the pins are from IOB flip-flops, they are synchronous. If the signals driving the pins are from internal logic, they are asynchronous, and therefore more care must be taken that they are simultaneous. Any differential pairs can be used for synchronous input and output signals as well as asynchronous input signals.

However, only the differential pairs with the \_Y or \_YY suffix can be used for asynchronous output signals.

#### **Asynchronous Output Pad Name Designation**

Because of differences between densities, the differential pairs that can be used for asynchronous outputs vary by device. The pairs that are available in all densities for a given package have the \_YY suffix. These pins should be used for differential asynchronous outputs if the design may later move to a different density. All other differential pairs that can be used for asynchronous outputs have the \_Y suffix.

To simplify the following tables, the "Pad Name" column shows the part of the name that is common across densities. The "Pad Name" column leaves out the \_Y suffix and the "LVDS Asynchronous Output Option" column indicates the densities that allow asynchronous outputs for LVDS or LVPECL on the given pin.

#### **DLL Pins**

Pins labeled "I/O (DLL)" can be used as general-purpose I/O or as inputs to the DLL. Adjacent DLL pins form a differential pair. They reside in two different banks, so if they are outputs the  $V_{CCO}$  level must be the same for both banks. Each DLL pin can also be paired with the adjacent GCK clock pin for a differential clock input. The "I/O (DLL)" pin always becomes the N terminal when paired with GCK, even if it is labeled "P" for its pairing with the adjacent DLL pin.

#### **VREF Pins**

Pins labeled "I/O, VREF" can be used as either an I/O or a VREF pin. If any I/O pin within the bank requires a VREF input, all the VREF pins in the bank must be connected to the same voltage. See the I/O banking rules in the Functional Description module for more detail. If no pin in a given bank requires VREF, then that bank's VREF pins can be used as general I/O.

To simplify the following tables, the "Pad Name" column shows the part of the name that is common across densities. When VREF is only available in limited densities, the "Pad Name" column leaves out the VREF designation and the "VREF Option" column indicates the densities that provide VREF on the given pin.

#### **VCCO Banks**

In the TQ144 and PQ208 packages, the eight banks have VCCO connected together. Thus, only one VCCO is allowed in these packages, although different VREF values are allowed in each of the eight banks. See I/O Banking.

# PQ208 Pinouts (XC2S50E, XC2S100E, XC2S150E, XC2S200E, XC2S300E)

| Pad Nar                  | ne   |                             | LVDS                            |                                  |  |

|--------------------------|------|-----------------------------|---------------------------------|----------------------------------|--|

| Function                 | Bank | Pin                         | Async.<br>Output<br>Option      | V <sub>REF</sub><br>Option       |  |

| I/O, VREF<br>Bank 1, L6P | 1    | P178                        | XC2S50E,<br>200E, 300E          | All                              |  |

| I/O, L6N                 | 1    | P179                        | XC2S50E,<br>200E, 300E          | -                                |  |

| I/O                      | 1    | P180                        | -                               | -                                |  |

| I/O (DLL),<br>L5P        | 1    | P181                        | -                               | -                                |  |

| GCK2, I                  | 1    | P182                        | -                               | -                                |  |

| GND                      | -    | P183                        | -                               | -                                |  |

| VCCO                     | -    | P184                        | -                               | -                                |  |

|                          |      |                             |                                 |                                  |  |

| GCK3, I                  | 0    | P185                        | -                               | -                                |  |

| VCCINT                   | ı    | P186                        | -                               | -                                |  |

| I/O (DLL),<br>L5N        | 0    | P187                        | -                               | -                                |  |

| I/O, L4P                 | 0    | P188 XC2S50E,<br>200E, 300E |                                 | -                                |  |

| I/O, VREF<br>Bank 0, L4N | 0    | P189                        | XC2S50E,<br>200E, 300E          | All                              |  |

| GND                      | ı    | P190                        | -                               | -                                |  |

| I/O, L3P                 | 0    | P191                        | XC2S50E,<br>200E, 300E          | -                                |  |

| I/O, L3N                 | 0    | P192                        | XC2S50E,<br>200E, 300E          | -                                |  |

| I/O, L2P                 | 0    | P193                        | XC2S50E,<br>100E, 200E,<br>300E | -                                |  |

| I/O, L2N                 | 0    | P194                        | XC2S50E,<br>100E, 200E,<br>300E | -                                |  |

| VCCINT                   | -    | P195                        | -                               | -                                |  |

| VCCO                     | -    | P196                        | -                               | -                                |  |

| GND                      | -    | P197                        | -                               | -                                |  |

| I/O, L1P                 | 0    | P198                        | XC2S50E,<br>100E, 200E,<br>300E | -                                |  |

| I/O, L1N                 | 0    | P199                        | XC2S50E,<br>100E, 200E,<br>300E | XC2S100E,<br>150E, 200E,<br>300E |  |

| I/O                      | 0    | P200                        | -                               | -                                |  |

# PQ208 Pinouts (XC2S50E, XC2S100E, XC2S150E, XC2S200E, XC2S300E)

| Pad Nar                        | ne   |      | LVDS                       |                            |

|--------------------------------|------|------|----------------------------|----------------------------|

| Function                       | Bank | Pin  | Async.<br>Output<br>Option | V <sub>REF</sub><br>Option |

| I/O                            | 0    | P201 | -                          | -                          |

| I/O,<br>L0P_YY                 | 0    | P202 | All                        | -                          |

| I/O, VREF<br>Bank 0,<br>LON_YY | 0    | P203 | All                        | All                        |

| I/O                            | 0    | P204 | -                          | -                          |

| I/O                            | 0    | P205 | -                          | XC2S200E,<br>300E          |

| I/O                            | 0    | P206 | -                          | -                          |

| TCK                            | -    | P207 | -                          | -                          |

| VCCO                           | -    | P208 | -                          | -                          |

#### **PQ208 Differential Clock Pins**

|       |      | Р    |         |      | N                  |

|-------|------|------|---------|------|--------------------|

| Clock | Bank | Pin  | Name    | Pin  | Name               |

| GCK0  | 4    | P80  | GCK0, I | P81  | I/O (DLL),<br>L31P |

| GCK1  | 5    | P77  | GCK1, I | P75  | I/O (DLL),<br>L31N |

| GCK2  | 1    | P182 | GCK2, I | P181 | I/O (DLL),<br>L5P  |

| GCK3  | 0    | P185 | GCK3, I | P187 | I/O (DLL),<br>L5N  |

# FT256 Pinouts (XC2S50E, XC2S100E, XC2S150E, XC2S200E, XC2S300E, XC2S400E)

| Pad Nam                   | ie   |     | LVDS                                  |                                        |

|---------------------------|------|-----|---------------------------------------|----------------------------------------|

| Function                  | Bank | Pin | Async.<br>Output<br>Option            | V <sub>REF</sub><br>Option             |

| TMS                       | -    | B1  | -                                     | -                                      |

| I/O                       | 7    | D3  | -                                     | -                                      |

| I/O, L83P                 | 7    | C2  | XC2S100E,<br>150E                     | -                                      |

| I/O, L83N                 | 7    | C1  | XC2S100E,<br>150E                     | XC2S200E,<br>300E, 400E                |

| I/O, L82P_YY              | 7    | D2  | All                                   | -                                      |

| I/O, L82N_YY              | 7    | D1  | All                                   | -                                      |

| I/O, VREF<br>Bank 7, L81P | 7    | E3  | XC2S50E,<br>150E, 200E,<br>300E, 400E | All                                    |

| I/O, L81N                 | 7    | E4  | XC2S50E,<br>150E, 200E,<br>300E, 400E | -                                      |

| I/O, L80P                 | 7    | E2  | XC2S200E,<br>400E                     | -                                      |

| I/O, L80N                 | 7    | E1  | XC2S200E,<br>400E                     | -                                      |

| I/O, L79P                 | 7    | F4  | XC2S50E,<br>300E, 400E                | XC2S100E,<br>150E, 200E,<br>300E, 400E |

| I/O, L79N                 | 7    | F3  | XC2S50E,<br>300E, 400E                | -                                      |

| I/O, L78P_YY              | 7    | F2  | All                                   | -                                      |

| I/O, L78N_YY              | 7    | F1  | All                                   | -                                      |

| I/O, L77P                 | 7    | F5  | XC2S100E,<br>150E                     | -                                      |

| I/O, L77N                 | 7    | G5  | XC2S100E,<br>150E                     | -                                      |

| I/O, L76P_YY              | 7    | G3  | All                                   | -                                      |

| I/O, L76N_YY              | 7    | G4  | All                                   | -                                      |

| I/O, VREF<br>Bank 7, L75P | 7    | G2  | XC2S50E,<br>300E, 400E                | All                                    |

| I/O, L75N                 | 7    | G1  | XC2S50E,<br>300E, 400E                | -                                      |

# FT256 Pinouts (XC2S50E, XC2S100E, XC2S150E, XC2S200E, XC2S300E, XC2S400E) *(Continued)*

| Pad Name                  |      |     | LVDS                                                     |                            |  |

|---------------------------|------|-----|----------------------------------------------------------|----------------------------|--|

| Function                  | Bank | Pin | Async.<br>Output<br>Option                               | V <sub>REF</sub><br>Option |  |

| I/O, L74P                 | 7    | H4  | XC2S100E,<br>150E, 200E                                  | -                          |  |

| I/O, L74N                 | 7    | НЗ  | XC2S100E,<br>150E, 200E                                  | XC2S400E                   |  |

| I/O, L73P_YY              | 7    | H2  | All                                                      | -                          |  |

| I/O (IRDY),<br>L73N_YY    | 7    | H1  | All                                                      | -                          |  |

|                           |      | ,   |                                                          |                            |  |

| I/O (TRDY)                | 6    | J4  | -                                                        | -                          |  |

| I/O, L72P                 | 6    | J2  | XC2S100E,<br>150E, 200E,<br>400E                         | XC2S400E                   |  |

| I/O, L72N                 | 6    | J3  | XC2S100E,<br>150E, 200E,<br>400E                         | -                          |  |

| I/O, L71P                 | 6    | J1  | XC2S50E,<br>300E, 400E                                   | -                          |  |

| I/O, VREF<br>Bank 6, L71N | 6    | K1  | XC2S50E,<br>300E, 400E                                   | All                        |  |

| I/O, L70P_YY              | 6    | K2  | All                                                      | -                          |  |

| I/O, L70N_YY              | 6    | K3  | All                                                      | -                          |  |

| I/O, L69P                 | 6    | L1  | XC2S100E,<br>150E, 400E                                  | -                          |  |

| I/O, L69N                 | 6    | L2  | XC2S100E,<br>150E, 400E                                  | -                          |  |

| I/O, L68P_YY              | 6    | K4  | All                                                      | -                          |  |

| I/O, L68N_YY              | 6    | K5  | All                                                      | -                          |  |

| I/O, L67P                 | 6    | L3  | XC2S50E,<br>300E, 400E                                   | -                          |  |

| I/O, L67N                 | 6    | M2  | XC2S50E,<br>300E, 400E XC2S100<br>150E, 200<br>300E, 400 |                            |  |

| I/O, L66P                 | 6    | M1  | XC2S150E,<br>200E, 400E                                  |                            |  |

| I/O, L66N                 | 6    | N1  | XC2S150E,<br>200E, 400E                                  | -                          |  |

# FT256 Pinouts (XC2S50E, XC2S100E, XC2S150E, XC2S200E, XC2S300E, XC2S400E) *(Continued)*

| Pad Nam                         | е    |     | LVDS                                  |                                        |

|---------------------------------|------|-----|---------------------------------------|----------------------------------------|

| Function                        | Bank | Pin | Async.<br>Output<br>Option            | V <sub>REF</sub><br>Option             |

| I/O, L51P                       | 4    | N9  | XC2S50E,<br>150E, 200E,<br>400E       | -                                      |

| I/O, L50N                       | 4    | T10 | XC2S50E,<br>200E, 300E,<br>400E       | -                                      |

| I/O, VREF<br>Bank 4, L50P       | 4    | R10 | XC2S50E,<br>200E, 300E,<br>400E       | All                                    |

| I/O, L49N                       | 4    | P10 | XC2S50E,<br>200E, 300E,<br>400E       | -                                      |

| I/O, L49P                       | 4    | R11 | XC2S50E,<br>200E, 300E,<br>400E       | -                                      |

| I/O                             | 4    | T11 | -                                     | -                                      |

| I/O, L48N                       | 4    | N10 | XC2S50E,<br>100E, 200E,<br>300E, 400E | -                                      |

| I/O, L48P                       | 4    | M10 | XC2S50E,<br>100E, 200E,<br>300E, 400E | -                                      |

| I/O, L47N                       | 4    | P11 | XC2S50E,<br>100E, 200E,<br>300E, 400E | -                                      |

| I/O, L47P                       | 4    | R12 | XC2S50E,<br>100E, 200E,<br>300E, 400E | XC2S100E,<br>150E, 200E,<br>300E, 400E |

| I/O, L46N                       | 4    | T12 | XC2S50E,<br>100E, 150E,<br>300E       | -                                      |

| I/O, L46P                       | 4    | T13 | XC2S50E,<br>100E, 150E,<br>300E       | -                                      |

| I/O, L45N_YY                    | 4    | N11 | All                                   | -                                      |

| I/O, VREF<br>Bank 4,<br>L45P_YY | 4    | M11 | All                                   | All                                    |

| I/O, L44N_YY                    | 4    | P12 | All                                   | -                                      |

| I/O, L44P_YY                    | 4    | N12 | All                                   | -                                      |

# FT256 Pinouts (XC2S50E, XC2S100E, XC2S150E, XC2S200E, XC2S300E, XC2S400E) (Continued)

| Pad Name                  |      |     | LVDS                                                    |                                        |

|---------------------------|------|-----|---------------------------------------------------------|----------------------------------------|

| Function                  | Bank | Pin | Async.<br>Output<br>Option                              | V <sub>REF</sub><br>Option             |

| I/O, L43N                 | 4    | R13 | XC2S50E,<br>150E                                        | XC2S200E,<br>300E, 400E                |

| I/O, L43P                 | 4    | P13 | XC2S50E,<br>150E                                        | -                                      |

| I/O, L42N_YY              | 4    | T14 | All                                                     | -                                      |

| I/O, L42P_YY              | 4    | R14 | All                                                     | -                                      |

|                           |      |     |                                                         |                                        |

| DONE                      | 3    | T15 | -                                                       | -                                      |

| PROGRAM                   | -    | R16 | -                                                       | -                                      |

| I/O (INIT),<br>L41N_YY    | 3    | P15 | All                                                     | -                                      |

| I/O (D7),<br>L41P_YY      | 3    | P16 | All                                                     | -                                      |

| I/O, L40N                 | 3    | N15 | XC2S100E,<br>150E, 400E                                 | -                                      |

| I/O, L40P                 | 3    | N16 | XC2S100E,<br>150E, 400E                                 | XC2S200E,<br>300E, 400E                |

| I/O, L39N                 | 3    | N14 | XC2S50E,<br>100E, 150E,<br>200E,<br>300E <sup>(1)</sup> | -                                      |

| I/O, L39P                 | 3    | M14 | XC2S50E,<br>100E, 150E,<br>200E,<br>300E <sup>(1)</sup> | -                                      |

| I/O, VREF<br>Bank 3, L38N | 3    | M15 | XC2S50E,<br>150E, 200E,<br>300E, 400E                   | All                                    |

| I/O, L38P                 | 3    | M16 | XC2S50E,<br>150E, 200E,<br>300E, 400E                   | -                                      |

| I/O <sup>(2)</sup>        | 3    | M13 | -                                                       | -                                      |

| I/O <sup>(2)</sup>        | 3    | L14 | -                                                       | -                                      |

| I/O, L36N                 | 3    | L15 | XC2S50E,<br>300E, 400E                                  | XC2S100E,<br>150E, 200E,<br>300E, 400E |

| I/O (D6), L36P            | 3    | L16 | XC2S50E,<br>300E, 400E                                  | -                                      |

# FT256 Pinouts (XC2S50E, XC2S100E, XC2S150E, XC2S200E, XC2S300E, XC2S400E) *(Continued)*

| Pad Nam                           | е    |     | LVDS                                                          |                            |  |

|-----------------------------------|------|-----|---------------------------------------------------------------|----------------------------|--|

| Function                          | Bank | Pin | Async.<br>Output<br>Option                                    | V <sub>REF</sub><br>Option |  |

| I/O, L20P                         | 2    | D14 | XC2S100E,<br>200E, 300E                                       | XC2S200E,<br>300E, 400E    |  |

| I/O (DIN, D0),<br>L19N_YY         | 2    | B16 | All                                                           | -                          |  |

| I/O (DOUT,<br>BUSY),<br>L19P_YY   | 2    | C15 | All                                                           | -                          |  |

| CCLK                              | 2    | A15 | -                                                             | -                          |  |

| TDO                               | 2    | B14 | -                                                             | -                          |  |

| TDI                               | -    | C13 | -                                                             | -                          |  |

|                                   |      |     | 1                                                             |                            |  |

| I/O ( <del>CS</del> ),<br>L18P_YY | 1    | A14 | All                                                           | -                          |  |

| I/O (WRITE),<br>L18N_YY           | 1    | A13 | All                                                           | -                          |  |

| I/O, L17P                         | 1    | B13 | XC2S50E,<br>100E, 200E,<br>300E, 400E                         | XC2S200E,<br>300E, 400E    |  |

| I/O, L17N                         | 1    | C12 | XC2S50E,<br>100E, 200E,<br>300E, 400E                         | -                          |  |

| I/O, L16P_YY                      | 1    | B12 | All                                                           | -                          |  |

| I/O, L16N_YY                      | 1    | A12 | All                                                           | -                          |  |

| I/O, VREF<br>Bank 1,<br>L15P_YY   | 1    | D12 | All                                                           | All                        |  |

| I/O, L15N_YY                      | 1    | E11 | All                                                           | -                          |  |

| I/O, L14P                         | 1    | D11 | XC2S50E,<br>100E, 150E,<br>300E                               | -                          |  |

| I/O, L14N                         | 1    | C11 | XC2S50E,<br>100E, 150E,<br>300E                               | -                          |  |

| I/O, L13P                         | 1    | B11 | XC2S50E, XC2S100<br>100E,200E, 150E,200<br>300E,400E 300E,400 |                            |  |

| I/O, L13N                         | 1    | A11 | XC2S50E,<br>100E, 200E,<br>300E, 400E                         | -                          |  |

# FT256 Pinouts (XC2S50E, XC2S100E, XC2S150E, XC2S200E, XC2S300E, XC2S400E) (Continued)

| Pad Nam                   | е    |     | LVDS                                  |                            |

|---------------------------|------|-----|---------------------------------------|----------------------------|

| Function                  | Bank | Pin | Async.<br>Output<br>Option            | V <sub>REF</sub><br>Option |

| I/O, L12P                 | 1    | E10 | XC2S50E,<br>100E, 200E,<br>300E, 400E | -                          |

| I/O, L12N                 | 1    | D10 | XC2S50E,<br>100E, 200E,<br>300E, 400E | -                          |

| I/O                       | 1    | C10 | -                                     | -                          |

| I/O, L11P                 | 1    | B10 | XC2S50E,<br>200E, 300E,<br>400E       | -                          |

| I/O, L11N                 | 1    | A10 | XC2S50E,<br>200E, 300E,<br>400E       | -                          |

| I/O, VREF<br>Bank 1, L10P | 1    | D9  | XC2S50E,<br>200E, 300E,<br>400E       | All                        |

| I/O, L10N                 | 1    | C9  | XC2S50E,<br>200E, 300E,<br>400E       | -                          |

| I/O, L9P                  | 1    | В9  | XC2S50E,<br>150E, 200E,<br>400E       | -                          |

| I/O, L9N                  | 1    | A9  | XC2S50E,<br>150E, 200E,<br>400E       | XC2S400E                   |

| I/O (DLL), L8P            | 1    | A8  | -                                     | -                          |

| GCK2, I                   | 1    | B8  | -                                     | -                          |

|                           |      |     |                                       |                            |

| GCK3, I                   | 0    | C8  | -                                     | -                          |

| I/O (DLL), L8N            | 0    | D8  | -                                     | -                          |

| I/O                       | 0    | A7  | -                                     | XC2S400E                   |

| I/O, L7P                  | 0    | E7  | XC2S50E,<br>200E, 300E,<br>400E       | -                          |

| I/O, VREF<br>Bank 0, L7N  | 0    | D7  | XC2S50E,<br>200E, 300E,<br>400E       | All                        |

### FG456 Pinouts (XC2S100E, XC2S150E, XC2S200E, XC2S300E, XC2S400E, XC2S600E)

| Pad Nar                        | ne   |      | LVDS                                   |                                  |                                 | De                              | vice-Specific                   | Pinouts: XC                     | 28                              |                                 |

|--------------------------------|------|------|----------------------------------------|----------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|

| Function                       | Bank | Pin  | Async.<br>Output<br>Option             | V <sub>REF</sub><br>Option       | 100E                            | 150E                            | 200E                            | 300E                            | 400E                            | 600E                            |

| I/O, L#N                       | 4    | AA16 | XC2S150E,<br>200E, 400E                | XC2S600E                         | I/O, L46N                       | I/O,<br>L62N_Y                  | I/O,<br>L66N_Y                  | I/O, L66N                       | I/O,<br>L66N_Y                  | I/O, VREF<br>Bank 4,<br>L66N    |

| I/O, L#P                       | 4    | Y16  | XC2S150E,<br>200E, 400E                | -                                | I/O, L46P                       | I/O, L62P_Y                     | I/O, L66P_Y                     | I/O, L66P                       | I/O, L66P_Y                     | I/O, L66P                       |

| I/O, L#N                       | 4    | W16  | XC2S150E,<br>200E                      | -                                | -                               | I/O,<br>L61N_Y                  | I/O,<br>L65N_Y                  | I/O, L65N                       | I/O, L65N                       | I/O, L65N                       |

| I/O, L#P                       | 4    | V16  | XC2S150E,<br>200E                      | -                                | -                               | I/O, L61P_Y                     | I/O, L65P_Y                     | I/O, L65P                       | I/O, L65P                       | I/O, L65P                       |

| I/O,<br>L#N_YY                 | 4    | AA17 | All                                    | -                                | I/O,<br>L45N_YY                 | I/O,<br>L60N_YY                 | I/O,<br>L64N_YY                 | I/O,<br>L64N_YY                 | I/O,<br>L64N_YY                 | I/O,<br>L64N_YY                 |

| I/O, VREF<br>Bank 4,<br>L#P_YY | 4    | Y17  | All                                    | All                              | I/O, VREF<br>Bank 4,<br>L45P_YY | I/O, VREF<br>Bank 4,<br>L60P_YY | I/O, VREF<br>Bank 4,<br>L64P_YY | I/O, VREF<br>Bank 4,<br>L64P_YY | I/O, VREF<br>Bank 4,<br>L64P_YY | I/O, VREF<br>Bank 4,<br>L64P_YY |

| I/O                            | 4    | AB18 | XC2S100E                               | -                                | I/O,<br>L44N_Y                  | I/O                             | I/O                             | I/O                             | I/O                             | I/O                             |

| I/O, L#N                       | 4    | W17  | XC2S100E,<br>400E, 600E                | -                                | I/O, L44P_Y                     | I/O, L59N                       | I/O, L63N                       | I/O, L63N                       | I/O,<br>L63N_Y                  | I/O,<br>L63N_Y                  |

| I/O, L#P                       | 4    | V17  | XC2S400E,<br>600E                      | -                                | -                               | I/O, L59P                       | I/O, L63P                       | I/O, L63P                       | I/O, L63P_Y                     | I/O, L63P_Y                     |

| I/O                            | 4    | AA18 | -                                      | -                                | -                               | -                               | -                               | I/O                             | I/O                             | I/O                             |

| I/O, L#N                       | 4    | Y18  | XC2S100E,<br>200E, 300E,<br>400E, 600E | -                                | I/O,<br>L43N_Y                  | I/O, L58N                       | I/O,<br>L62N_Y                  | I/O,<br>L62N_Y                  | I/O,<br>L62N_Y                  | I/O,<br>L62N_Y                  |

| I/O, L#P                       | 4    | W18  | XC2S100E,<br>200E, 300E,<br>400E, 600E | XC2S200E,<br>300E,<br>400E, 600E | I/O, L43P_Y                     | I/O, L58P                       | I/O, VREF<br>Bank 4,<br>L62P_Y  | I/O, VREF<br>Bank 4,<br>L62P_Y  | I/O, VREF<br>Bank 4,<br>L62P_Y  | I/O, VREF<br>Bank 4,<br>L62P_Y  |

| I/O                            | 4    | AB19 | -                                      | -                                | I/O                             | I/O                             | I/O                             | I/O                             | I/O                             | I/O                             |

| I/O, L#N                       | 4    | AA19 | XC2S150E,<br>400E                      | -                                | -                               | I/O,<br>L57N_Y                  | I/O, L61N                       | I/O, L61N                       | I/O,<br>L61N_Y                  | I/O, L61N                       |

| I/O, L#P                       | 4    | Y19  | XC2S150E,<br>400E                      | -                                | -                               | I/O, L57P_Y                     | I/O, L61P                       | I/O, L61P                       | I/O, L61P_Y                     | I/O, L61P                       |

| I/O                            | 4    | AB21 | -                                      | -                                | -                               | -                               | -                               | I/O                             | I/O                             | I/O                             |

| I/O,<br>L#N_YY                 | 4    | AB20 | All                                    | -                                | I/O,<br>L42N_YY                 | I/O,<br>L56N_YY                 | I/O,<br>L60N_YY                 | I/O,<br>L60N_YY                 | I/O,<br>L60N_YY                 | I/O,<br>L60N_YY                 |

| I/O,<br>L#P_YY                 | 4    | AA20 | All                                    | -                                | I/O,<br>L42P_YY                 | I/O,<br>L56P_YY                 | I/O,<br>L60P_YY                 | I/O,<br>L60P_YY                 | I/O,<br>L60P_YY                 | I/O,<br>L60P_YY                 |

|                                | •    | •    |                                        |                                  |                                 |                                 |                                 |                                 |                                 |                                 |

| DONE                           | 3    | W20  | -                                      | -                                | DONE                            | DONE                            | DONE                            | DONE                            | DONE                            | DONE                            |

| PROGRAM                        | -    | Y21  | -                                      | -                                | PROGRAM                         | PROGRAM                         | PROGRAM                         | PROGRAM                         | PROGRAM                         | PROGRAM                         |

| I/O (INIT),<br>L#N_YY          | 3    | W21  | All                                    | -                                | I/O (INIT),<br>L41N_YY          | I/O (INIT),<br>L55N_YY          | I/O (INIT),<br>L59N_YY          | I/O (INIT),<br>L59N_YY          | I/O (INIT),<br>L59N_YY          | I/O (INIT),<br>L59N_YY          |

| I/O (D7),<br>L#P_YY            | 3    | Y22  | All                                    | -                                | I/O (D7),<br>L41P_YY            | I/O (D7),<br>L55P_YY            | I/O (D7),<br>L59P_YY            | I/O (D7),<br>L59P_YY            | I/O (D7),<br>L59P_YY            | I/O (D7),<br>L59P_YY            |

| I/O                            | 3    | W22  | -                                      | -                                | -                               | -                               | -                               | I/O                             | I/O                             | I/O                             |

| I/O                            | 3    | V21  | -                                      | -                                | -                               | I/O                             | I/O                             | I/O                             | I/O                             | I/O                             |

### FG456 Pinouts (XC2S100E, XC2S150E, XC2S200E, XC2S300E, XC2S400E, XC2S600E)

| Pad Nai                        |      |     | LVDS                                   |                                  |                                 | -                               | evice-Specific                  | •                               |                                 |                                 |

|--------------------------------|------|-----|----------------------------------------|----------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|

| Function                       | Bank | Pin | Async.<br>Output<br>Option             | V <sub>REF</sub><br>Option       | 100E                            | 150E                            | 200E                            | 300E                            | 400E                            | 600E                            |

| I/O<br>(WRITE),<br>L#N_YY      | 1    | A20 | All                                    | -                                | I/O<br>(WRITE),<br>L20N_YY      | I/O<br>(WRITE),<br>L26N_YY      | I/O<br>(WRITE),<br>L28N_YY      | I/O<br>(WRITE),<br>L28N_YY      | I/O<br>(WRITE),<br>L28N_YY      | I/O<br>(WRITE),<br>L28N_YY      |

| I/O                            | 1    | D18 | -                                      | -                                | -                               | -                               | -                               | I/O                             | I/O                             | I/O                             |

| I/O                            | 1    | C18 | -                                      | -                                | -                               | I/O                             | I/O                             | I/O                             | I/O                             | I/O                             |

| I/O, L#P                       | 1    | B19 | XC2S200E,<br>300E, 400E,<br>600E       | -                                | -                               | I/O, L25P                       | I/O, L27P_Y                     | I/O, L27P_Y                     | I/O,L27P_Y                      | I/O,L27P_Y                      |

| I/O, L#N                       | 1    | A19 | XC2S200E,<br>300E, 400E,<br>600E       | -                                | I/O                             | I/O, L25N                       | I/O,<br>L27N_Y                  | I/O,<br>L27N_Y                  | I/O,<br>L27N_Y                  | I/O,<br>L27N_Y                  |

| I/O, L#P                       | 1    | B18 | XC2S100E,<br>200E, 300E,<br>400E, 600E | XC2S200E,<br>300E,<br>400E, 600E | I/O, L19P_Y                     | I/O, L24P                       | I/O, VREF<br>Bank 1,<br>L26P_Y  | I/O, VREF<br>Bank 1,<br>L26P_Y  | I/O, VREF<br>Bank 1,<br>L26P_Y  | I/O, VREF<br>Bank 1,<br>L26P_Y  |

| I/O, L#N                       | 1    | A18 | XC2S100E,<br>200E, 300E,<br>400E, 600E | -                                | I/O,<br>L19N_Y                  | I/O, L24N                       | I/O,<br>L26N_Y                  | I/O,<br>L26N_Y                  | I/O,<br>L26N_Y                  | I/O,<br>L26N_Y                  |

| I/O                            | 1    | D17 | -                                      | -                                | -                               | -                               | -                               | I/O                             | I/O                             | I/O                             |

| I/O                            | 1    | C17 | -                                      | -                                | -                               | I/O                             | I/O                             | I/O                             | I/O                             | I/O                             |

| I/O,<br>L#P_YY                 | 1    | B17 | All                                    | -                                | I/O,<br>L18P_YY                 | I/O,<br>L23P_YY                 | I/O,<br>L25P_YY                 | I/O,<br>L25P_YY                 | I/O,<br>L25P_YY                 | I/O,<br>L25P_YY                 |

| I/O,<br>L#N_YY                 | 1    | A17 | All                                    | -                                | I/O,<br>L18N_YY                 | I/O,<br>L23N_YY                 | I/O,<br>L25N_YY                 | I/O,<br>L25N_YY                 | I/O,<br>L25N_YY                 | I/O,<br>L25N_YY                 |

| I/O, VREF<br>Bank 1,<br>L#P_YY | 1    | E16 | All                                    | All                              | I/O, VREF<br>Bank 1,<br>L17P_YY | I/O, VREF<br>Bank 1,<br>L22P_YY | I/O, VREF<br>Bank 1,<br>L24P_YY | I/O, VREF<br>Bank 1,<br>L24P_YY | I/O, VREF<br>Bank 1,<br>L24P_YY | I/O, VREF<br>Bank 1,<br>L24P_YY |

| I/O,<br>L#N_YY                 | 1    | E17 | All                                    | -                                | I/O,<br>L17N_YY                 | I/O,<br>L22N_YY                 | I/O,<br>L24N_YY                 | I/O,<br>L24N_YY                 | I/O,<br>L24N_YY                 | I/O,<br>L24N_YY                 |

| I/O                            | 1    | E15 | -                                      | -                                | -                               | I/O                             | I/O                             | I/O                             | I/O                             | I/O                             |

| I/O, L#P                       | 1    | D16 | XC2S300E,<br>600E                      | -                                | -                               | I/O, L21P                       | I/O, L23P                       | I/O, L23P_Y                     | I/O, L23P                       | I/O,L23P_Y                      |

| I/O, L#N                       | 1    | C16 | XC2S300E,<br>600E                      | -                                | I/O                             | I/O, L21N                       | I/O, L23N                       | I/O,<br>L23N_Y                  | I/O, L23N                       | I/O,<br>L23N_Y                  |

| I/O, L#P                       | 1    | B16 | XC2S100E,<br>300E, 600E                | XC2S600E                         | I/O, L16P_Y                     | I/O, L20P                       | I/O, L22P                       | I/O, L22P_Y                     | I/O, L22P                       | I/O, VREF<br>Bank 1,<br>L22P_Y  |

| I/O, L#N                       | 1    | A16 | XC2S100E,<br>300E, 600E                | -                                | I/O,<br>L16N_Y                  | I/O, L20N                       | I/O, L22N                       | I/O,<br>L22N_Y                  | I/O, L22N                       | I/O,<br>L22N_Y                  |

| I/O                            | 1    | F14 | -                                      | -                                | -                               | -                               | -                               | I/O                             | I/O                             | I/O                             |

| I/O, VREF<br>Bank 1,<br>L#P    | 1    | D15 | XC2S100E,<br>200E, 300E,<br>400E, 600E | All                              | I/O, VREF<br>Bank 1,<br>L15P_Y  | I/O, VREF<br>Bank 1,<br>L19P    | I/O, VREF<br>Bank 1,<br>L21P_Y  | I/O, VREF<br>Bank 1,<br>L21P_Y  | I/O, VREF<br>Bank 1,<br>L21P_Y  | I/O, VREF<br>Bank 1,<br>L21P_Y  |

| I/O, L#N                       | 1    | C15 | XC2S100E,<br>200E, 300E,<br>400E, 600E | -                                | I/O,<br>L15N_Y                  | I/O, L19N                       | I/O,<br>L21N_Y                  | I/O,<br>L21N_Y                  | I/O,<br>L21N_Y                  | I/O,<br>L21N_Y                  |

| I/O, L#P                       | 1    | B15 | XC2S100E,<br>200E, 300E,<br>400E, 600E | -                                | I/O, L14P_Y                     | I/O, L18P                       | I/O, L20P_Y                     | I/O, L20P_Y                     | I/O,L20P_Y                      | I/O,L20P_Y                      |

### Additional FG456 Package Pins (Continued)

| VCCO Bank 1 F     | Pins              |                    |                    |                     |                    |                   |                    |                     |

|-------------------|-------------------|--------------------|--------------------|---------------------|--------------------|-------------------|--------------------|---------------------|

| F15               | F16               | G13                | G14                | -                   | -                  | -                 | -                  | -                   |

| VCCO Bank 2 F     | Pins              |                    |                    |                     |                    |                   |                    |                     |

| G17               | H17               | J16                | K16                | -                   | -                  | -                 | -                  | -                   |

| VCCO Bank 3 F     | Pins              | 1                  |                    |                     |                    |                   |                    | 1                   |

| N16               | P16               | R17                | T17                | -                   | -                  | -                 | -                  | -                   |

| VCCO Bank 4 F     | Pins              |                    |                    |                     |                    |                   |                    |                     |

| T13               | T14               | U15                | U16                | -                   | -                  | -                 | -                  | -                   |

| VCCO Bank 5 F     | Pins              |                    |                    |                     |                    |                   |                    |                     |

| Т9                | T10               | U7                 | U8                 | -                   | -                  | -                 | -                  | -                   |

| VCCO Bank 6 I     | Pins              | 1                  |                    |                     |                    |                   |                    | 1                   |

| N7                | P7                | R6                 | T6                 | -                   | -                  | -                 | -                  | -                   |

| VCCO Bank 7 I     | Pins              |                    |                    |                     |                    |                   |                    |                     |

| G6                | H6                | J7                 | K7                 | -                   | -                  | -                 | -                  | -                   |

| GND Pins          |                   | <del>'</del>       |                    |                     |                    |                   | <u>-</u> !         | <del>'</del>        |

| A1                | A2 <sup>(2)</sup> | A22                | B1 <sup>(2)</sup>  | B2                  | B21                | C3                | C20                | G11                 |

| G12               | J9                | J10                | J11                | J12                 | J13                | J14               | K9                 | K10                 |

| K11               | K12               | K13                | K14                | L7                  | L9                 | L10               | L11                | L12                 |

| L13               | L14               | L16                | M7                 | M9                  | M10                | M11               | M12                | M13                 |