Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 1176                                                         |

| Number of Logic Elements/Cells | 5292                                                         |

| Total RAM Bits                 | 57344                                                        |

| Number of I/O                  | 146                                                          |

| Number of Gates                | 200000                                                       |

| Voltage - Supply               | 1.71V ~ 1.89V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 208-BFQFP                                                    |

| Supplier Device Package        | 208-PQFP (28x28)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s200e-6pq208c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

DS077-1 (v3.0) August 9, 2013

# Spartan-IIE FPGA Family: Introduction and Ordering Information

#### **Product Specification**

#### Introduction

The Spartan®-IIE Field-Programmable Gate Array family gives users high performance, abundant logic resources, and a rich feature set, all at an exceptionally low price. The seven-member family offers densities ranging from 50,000 to 600,000 system gates, as shown in Table 1. System performance is supported beyond 200 MHz.

Features include block RAM (to 288K bits), distributed RAM (to 221,184 bits), 19 selectable I/O standards, and four DLLs (Delay-Locked Loops). Fast, predictable interconnect means that successive design iterations continue to meet timing requirements.

The Spartan-IIE family is a superior alternative to mask-programmed ASICs. The FPGA avoids the initial cost, lengthy development cycles, and inherent risk of conventional ASICs. Also, FPGA programmability permits design upgrades in the field with no hardware replacement necessary (impossible with ASICs).

### **Features**

- Second generation ASIC replacement technology

- Densities as high as 15,552 logic cells with up to 600,000 system gates

- Streamlined features based on Virtex®-E FPGA architecture

- Unlimited in-system reprogrammability

- Very low cost

- Cost-effective 0.15 micron technology

- System level features

- SelectRAM™ hierarchical memory:

- 16 bits/LUT distributed RAM

- · Configurable 4K-bit true dual-port block RAM

- Fast interfaces to external RAM

- Fully 3.3V PCI compliant to 64 bits at 66 MHz and CardBus compliant

- Low-power segmented routing architecture

- Dedicated carry logic for high-speed arithmetic

- Efficient multiplier support

- Cascade chain for wide-input functions

- Abundant registers/latches with enable, set, reset

- Four dedicated DLLs for advanced clock control

- · Eliminate clock distribution delay

- Multiply, divide, or phase shift

- Four primary low-skew global clock distribution nets

- IEEE 1149.1 compatible boundary scan logic

- Versatile I/O and packaging

- Pb-free package options

- Low-cost packages available in all densities

- Family footprint compatibility in common packages

- 19 high-performance interface standards

- · LVTTL, LVCMOS, HSTL, SSTL, AGP, CTT, GTL

- LVDS and LVPECL differential I/O

- Up to 205 differential I/O pairs that can be input, output, or bidirectional

- Hot swap I/O (CompactPCI friendly)

- Core logic powered at 1.8V and I/Os powered at 1.5V, 2.5V, or 3.3V

- Fully supported by powerful Xilinx<sup>®</sup> ISE<sup>®</sup> development system

- Fully automatic mapping, placement, and routing

- Integrated with design entry and verification tools

- Extensive IP library including DSP functions and soft processors

Table 1: Spartan-IIE FPGA Family Members

| Device   | Logic<br>Cells | Typical<br>System Gate Range<br>(Logic and RAM) | CLB<br>Array<br>(R x C) | Total<br>CLBs | Maximum<br>Available<br>User I/O <sup>(1)</sup> | Maximum<br>Differential<br>I/O Pairs | Distributed<br>RAM Bits | Block RAM<br>Bits |

|----------|----------------|-------------------------------------------------|-------------------------|---------------|-------------------------------------------------|--------------------------------------|-------------------------|-------------------|

| XC2S50E  | 1,728          | 23,000 - 50,000                                 | 16 x 24                 | 384           | 182                                             | 83                                   | 24,576                  | 32K               |

| XC2S100E | 2,700          | 37,000 - 100,000                                | 20 x 30                 | 600           | 202                                             | 86                                   | 38,400                  | 40K               |

| XC2S150E | 3,888          | 52,000 - 150,000                                | 24 x 36                 | 864           | 265                                             | 114                                  | 55,296                  | 48K               |

| XC2S200E | 5,292          | 71,000 - 200,000                                | 28 x 42                 | 1,176         | 289                                             | 120                                  | 75,264                  | 56K               |

| XC2S300E | 6,912          | 93,000 - 300,000                                | 32 x 48                 | 1,536         | 329                                             | 120                                  | 98,304                  | 64K               |

| XC2S400E | 10,800         | 145,000 - 400,000                               | 40 x 60                 | 2,400         | 410                                             | 172                                  | 153,600                 | 160K              |

| XC2S600E | 15,552         | 210,000 - 600,000                               | 48 x 72                 | 3,456         | 514                                             | 205                                  | 221,184                 | 288K              |

#### Notes:

1. User I/O counts include the four global clock/user input pins. See details in Table 2, page 5

© 2001–2013 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

Functional Description

DS077-2 (v3.0) August 9, 2013

# **Architectural Description**

# **Spartan-IIE FPGA Array**

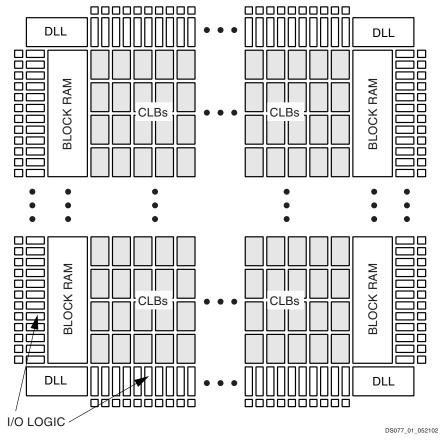

The Spartan®-IIE user-programmable gate array, shown in Figure 3, is composed of five major configurable elements:

- IOBs provide the interface between the package pins and the internal logic

- CLBs provide the functional elements for constructing most logic

- Dedicated block RAM memories of 4096 bits each

- Clock DLLs for clock-distribution delay compensation and clock domain control

- Versatile multi-level interconnect structure

# **Product Specification**

As can be seen in Figure 3, the CLBs form the central logic structure with easy access to all support and routing structures. The IOBs are located around all the logic and memory elements for easy and quick routing of signals on and off the chip.

**Spartan-IIE FPGA Family:**

Values stored in static memory cells control all the configurable logic elements and interconnect resources. These values load into the memory cells on power-up, and can reload if necessary to change the function of the device.

Each of these elements will be discussed in detail in the following sections.

Figure 3: Basic Spartan-IIE Family FPGA Block Diagram

© 2001-2013 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

DS077-2\_05-111501

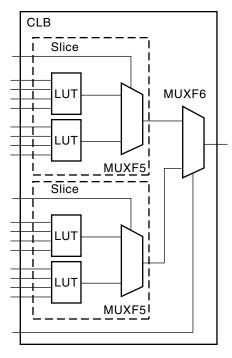

Figure 7: F5 and F6 Multiplexers

Each CLB has four direct feedthrough paths, one per LC. These paths provide extra data input lines or additional local routing that does not consume logic resources.

#### Arithmetic Logic

Dedicated carry logic provides capability for high-speed arithmetic functions. The Spartan-IIE FPGA CLB supports two separate carry chains, one per slice. The height of the carry chains is two bits per CLB.

The arithmetic logic includes an XOR gate that allows a 1-bit full adder to be implemented within an LC. In addition, a dedicated AND gate improves the efficiency of multiplier implementations.

The dedicated carry path can also be used to cascade function generators for implementing wide logic functions.

#### **BUFTs**

Each Spartan-IIE FPGA CLB contains two 3-state drivers (BUFTs) that can drive on-chip busses. The IOBs on the left and right sides can also drive the on-chip busses. See Dedicated Routing, page 17. Each Spartan-IIE FPGA BUFT has an independent 3-state control pin and an independent input pin. The 3-state control pin is an active-Low enable (T). When all BUFTs on a net are disabled, the net is High. There is no need to instantiate a pull-up unless desired for simulation purposes. Simultaneously driving BUFTs onto the same net will not cause contention. If driven both High and Low, the net will be Low.

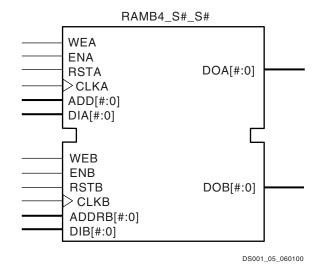

#### **Block RAM**

Spartan-IIE FPGAs incorporate several large block RAM memories. These complement the distributed RAM Look-Up Tables (LUTs) that provide shallow memory structures implemented in CLBs.

Block RAM memory blocks are organized in columns. Most Spartan-IIE devices contain two such columns, one along each vertical edge. The XC2S400E has four block RAM columns and the XC2S600E has six block RAM columns. These columns extend the full height of the chip. Each memory block is four CLBs high, and consequently, a Spartan-IIE device 16 CLBs high will contain four memory blocks per column, and a total of eight blocks.

Table 6: Spartan-IIE Block RAM Amounts

| Spartan-IIE<br>Device | # of Blocks | Total Block RAM<br>Bits |

|-----------------------|-------------|-------------------------|

| XC2S50E               | 8           | 32K                     |

| XC2S100E              | 10          | 40K                     |

| XC2S150E              | 12          | 48K                     |

| XC2S200E              | 14          | 56K                     |

| XC2S300E              | 16          | 64K                     |

| XC2S400E              | 40          | 160K                    |

| XC2S600E              | 72          | 288K                    |

Each block RAM cell, as illustrated in Figure 8, is a fully synchronous dual-ported 4096-bit RAM with independent control signals for each port. The data widths of the two ports can be configured independently, providing built-in bus-width conversion.

Figure 8: Dual-Port Block RAM

Table 7 shows the depth and width aspect ratios for the block RAM.

Table 7: Block RAM Port Aspect Ratios

| Width | Depth | ADDR Bus   | Data Bus   |

|-------|-------|------------|------------|

| 1     | 4096  | ADDR<11:0> | DATA<0>    |

| 2     | 2048  | ADDR<10:0> | DATA<1:0>  |

| 4     | 1024  | ADDR<9:0>  | DATA<3:0>  |

| 8     | 512   | ADDR<8:0>  | DATA<7:0>  |

| 16    | 256   | ADDR<7:0>  | DATA<15:0> |

The Spartan-IIE FPGA block RAM also includes dedicated routing to provide an efficient interface with both CLBs and other block RAMs. See Xilinx Application Note XAPP173 for more information on block RAM.

# **Programmable Routing**

It is the longest delay path that limits the speed of any design. Consequently, the Spartan-IIE FPGA routing architecture and its place-and-route software were defined jointly to minimize long-path delays and yield the best system performance.

The joint optimization also reduces design compilation times because the architecture is software-friendly. Design cycles are correspondingly reduced due to shorter design iteration times.

The software automatically uses the best available routing based on user timing requirements. The details are provided here for reference.

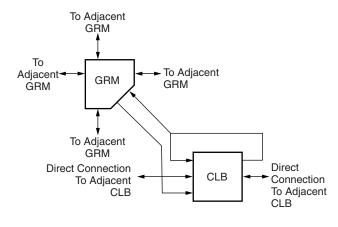

#### Local Routing

The local routing resources, as shown in Figure 9, provide the following three types of connections:

- Interconnections among the LUTs, flip-flops, and General Routing Matrix (GRM), described below.

- Internal CLB feedback paths that provide high-speed connections to LUTs within the same CLB, chaining them together with minimal routing delay

- Direct paths that provide high-speed connections between horizontally adjacent CLBs, eliminating the delay of the GRM

DS001\_06\_032300

Figure 9: Spartan-IIE Local Routing

### General Purpose Routing

Most Spartan-IIE FPGA signals are routed on the general purpose routing, and consequently, the majority of interconnect resources are associated with this level of the routing hierarchy. The general routing resources are located in horizontal and vertical routing channels associated with the rows and columns of CLBs. The general-purpose routing resources are listed below.

- Adjacent to each CLB is a General Routing Matrix (GRM). The GRM is the switch matrix through which horizontal and vertical routing resources connect, and is also the means by which the CLB gains access to the general purpose routing.

- 24 single-length lines route GRM signals to adjacent GRMs in each of the four directions.

- 96 buffered Hex lines route GRM signals to other GRMs six blocks away in each one of the four directions. Organized in a staggered pattern, Hex lines may be driven only at their endpoints. Hex-line signals can be accessed either at the endpoints or at the midpoint (three blocks from the source). One third of the Hex lines are bidirectional, while the remaining ones are unidirectional.

- 12 Longlines are buffered, bidirectional wires that distribute signals across the device quickly and efficiently. Vertical Longlines span the full height of the device, and horizontal ones span the full width of the device.

#### I/O Routing

Spartan-IIE devices have additional routing resources around their periphery that form an interface between the CLB array and the IOBs. This additional routing, called the VersaRing™ routing, facilitates pin-swapping and pin-locking, such that logic redesigns can adapt to existing PCB layouts. Time-to-market is reduced, since PCBs and other system components can be manufactured while the logic design is still in progress.

design, thus allowing the most convenient entry method to be used for each portion of the design.

# **Design Implementation**

The place-and-route tools automatically provide the implementation flow described in this section. The partitioner takes the EDIF netlist for the design and maps the logic into the architectural resources of the FPGA (CLBs and IOBs, for example). The placer then determines the best locations for these blocks based on their interconnections and the desired performance. Finally, the router interconnects the blocks.

The algorithms support fully automatic implementation of most designs. For demanding applications, however, the user can exercise various degrees of control over the process. User partitioning, placement, and routing information is optionally specified during the design-entry process. The implementation of highly structured designs can benefit greatly from basic floorplanning.

The implementation software incorporates timing-driven placement and routing. Designers specify timing requirements along entire paths during design entry. The timing path analysis routines then recognize these user-specified requirements and accommodate them.

Timing requirements are entered in a form directly relating to the system requirements, such as the targeted clock frequency, or the maximum allowable delay between two registers. In this way, the overall performance of the system along entire signal paths is automatically tailored to user-generated specifications. Specific timing information for individual nets is unnecessary.

#### **Design Verification**

In addition to conventional software simulation, FPGA users can use in-circuit debugging techniques. Because Xilinx devices are infinitely reprogrammable, designs can be verified in real time without the need for extensive sets of software simulation vectors.

The development system supports both software simulation and in-circuit debugging techniques. For simulation, the system extracts the post-layout timing information from the design database, and back-annotates this information into the netlist for use by the simulator. Alternatively, the user can verify timing-critical portions of the design using the static timing analyzer.

For in-circuit debugging, Xilinx offers a download cable, which connects the FPGA in the target system to a PC or workstation. After downloading the design into the FPGA, the designer can read back the contents of the flip-flops, and so observe the internal logic state. Simple modifications can be downloaded into the system in a matter of minutes.

# Configuration

Configuration is the process by which the bitstream of a design, as generated by the Xilinx development software, is loaded into the internal configuration memory of the FPGA. Spartan-IIE devices support both serial configuration, using the master/slave serial and JTAG modes, as well as byte-wide configuration employing the Slave Parallel mode.

### **Configuration File**

Spartan-IIE devices are configured by sequentially loading frames of data that have been concatenated into a configuration file. Table 10 shows how much nonvolatile storage space is needed for Spartan-IIE devices.

It is important to note that, while a PROM is commonly used to store configuration data before loading them into the FPGA, it is by no means required. Any of a number of different kinds of under populated nonvolatile storage already available either on or off the board (for example, hard drives, FLASH cards, and so on) can be used.

Table 10: Spartan-IIE Configuration File Size

| Device   | Configuration File Size (Bits) |

|----------|--------------------------------|

| XC2S50E  | 630,048                        |

| XC2S100E | 863,840                        |

| XC2S150E | 1,134,496                      |

| XC2S200E | 1,442,016                      |

| XC2S300E | 1,875,648                      |

| XC2S400E | 2,693,440                      |

| XC2S600E | 3,961,632                      |

#### **Modes**

Spartan-IIE devices support the following four configuration modes:

- Slave Serial mode

- Master Serial mode

- Slave Parallel mode

- Boundary-scan mode

The Configuration mode pins (M2, M1, M0) select among these configuration modes with the option in each case of having the IOB pins either pulled up or left floating prior to the end of configuration. The selection codes are listed in Table 11.

Configuration through the boundary-scan port is always available, independent of the mode selection. Selecting the boundary-scan mode simply turns off the other modes. The three mode pins have internal pull-up resistors, and default to a logic High if left unconnected.

# **Revision History**

| Date       | Version | Description                                                                                                                                                                                                                                                                                                 |

|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/15/2001 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                     |

| 11/18/2002 | 2.0     | Added XC2S400E and XC2S600E. Removed Preliminary designation. Clarified details of I/O standards, boundary scan, and configuration.                                                                                                                                                                         |

| 07/09/2003 | 2.1     | Added hot swap description (see Hot Swap, Hot Insertion, Hot Socketing Support). Added Table 9 containing JTAG IDCODE values. Clarified configuration PROM support.                                                                                                                                         |

| 06/18/2008 | 2.3     | Added note that TDI, TMS, and TCK have a default pull-up resistor. Add note on maximum daisy-chain limit. Updated Figure 19 since Mode pins can be pulled up to either 2.5V or 3.3V. Updated all modules for continuous page, figure, and table numbering. Updated links. Synchronized all modules to v2.3. |

| 08/09/2013 | 3.0     | This product is obsolete/discontinued per XCN12026.                                                                                                                                                                                                                                                         |

# — OBSOLETE — OBSOLETE — OBSOLETE —

**Spartan-IIE FPGA Family: Functional Description**

| Input/Output | V <sub>IL</sub> |                        | Output V <sub>IL</sub> |        | V                       | IH                      | V <sub>OL</sub> | V <sub>OH</sub> | I <sub>OL</sub> | I <sub>OH</sub> |

|--------------|-----------------|------------------------|------------------------|--------|-------------------------|-------------------------|-----------------|-----------------|-----------------|-----------------|

| Standard     | V, Min          | V, Max                 | V, Min                 | V, Max | V, Max                  | V, Min                  | mA              | mA              |                 |                 |

| HSTL I       | -0.5            | V <sub>REF</sub> – 0.1 | V <sub>REF</sub> + 0.1 | 3.6    | 0.4                     | V <sub>CCO</sub> - 0.4  | 8               | -8              |                 |                 |

| HSTL III     | -0.5            | V <sub>REF</sub> - 0.1 | V <sub>REF</sub> + 0.1 | 3.6    | 0.4                     | V <sub>CCO</sub> - 0.4  | 24              | -8              |                 |                 |

| HSTL IV      | -0.5            | V <sub>REF</sub> - 0.1 | V <sub>REF</sub> + 0.1 | 3.6    | 0.4                     | V <sub>CCO</sub> - 0.4  | 48              | -8              |                 |                 |

| SSTL3 I      | -0.5            | V <sub>REF</sub> - 0.2 | V <sub>REF</sub> + 0.2 | 3.6    | V <sub>REF</sub> - 0.6  | V <sub>REF</sub> + 0.6  | 8               | -8              |                 |                 |

| SSTL3 II     | -0.5            | V <sub>REF</sub> - 0.2 | V <sub>REF</sub> + 0.2 | 3.6    | V <sub>REF</sub> - 0.8  | V <sub>REF</sub> + 0.8  | 16              | -16             |                 |                 |

| SSTL2 I      | -0.5            | V <sub>REF</sub> - 0.2 | V <sub>REF</sub> + 0.2 | 3.6    | V <sub>REF</sub> - 0.61 | V <sub>REF</sub> + 0.61 | 7.6             | -7.6            |                 |                 |

| SSTL2 II     | -0.5            | V <sub>REF</sub> - 0.2 | V <sub>REF</sub> + 0.2 | 3.6    | V <sub>REF</sub> - 0.8  | V <sub>REF</sub> + 0.8  | 15.2            | -15.2           |                 |                 |

| CTT          | -0.5            | V <sub>REF</sub> - 0.2 | V <sub>REF</sub> + 0.2 | 3.6    | V <sub>REF</sub> - 0.4  | V <sub>REF</sub> + 0.4  | 8               | -8              |                 |                 |

| AGP          | -0.5            | V <sub>REF</sub> - 0.2 | V <sub>REF</sub> + 0.2 | 3.6    | 10% V <sub>CCO</sub>    | 90% V <sub>CCO</sub>    | Note (2)        | Note (2)        |                 |                 |

#### Notes:

- 1.  $V_{OL}$  and  $V_{OH}$  for lower drive currents are sample tested.

- Tested according to the relevant specifications.

# **LVDS DC Specifications**

| Symbol             | Description                                                                                                                | Conditions                                            | Min   | Тур   | Max   | Units |

|--------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------|-------|-------|-------|

| V <sub>CCO</sub>   | Supply voltage                                                                                                             |                                                       | 2.375 | 2.5   | 2.625 | V     |

| V <sub>OH</sub>    | Output High voltage for Q and Q                                                                                            | $R_T = 100\Omega$ across Q and $\overline{Q}$ signals | 1.25  | 1.425 | 1.6   | V     |

| V <sub>OL</sub>    | Output Low voltage for Q and Q                                                                                             | $R_T = 100\Omega$ across Q and $\overline{Q}$ signals | 0.9   | 1.075 | 1.25  | V     |

| V <sub>ODIFF</sub> | Differential output voltage $(Q - \overline{Q})$ , $Q = \text{High or } (\overline{Q} - Q)$ , $\overline{Q} = \text{High}$ | $R_T = 100\Omega$ across Q and $\overline{Q}$ signals | 250   | 350   | 450   | mV    |

| $V_{OCM}$          | Output common-mode voltage                                                                                                 | $R_T = 100\Omega$ across Q and $\overline{Q}$ signals | 1.125 | 1.25  | 1.375 | V     |

| V <sub>IDIFF</sub> | Differential input voltage $(Q - \overline{Q})$ , $Q = \text{High or } (\overline{Q} - Q)$ , $\overline{Q} = \text{High}$  | Common-mode input voltage = 1.25 V                    | 100   | 350   | -     | mV    |

| V <sub>ICM</sub>   | Input common-mode voltage                                                                                                  | Differential input voltage = ±350 mV                  | 0.2   | 1.25  | 2.2   | V     |

# **LVPECL DC Specifications**

These values are valid at the output of the source termination pack shown under LVPECL, with a 100 $\Omega$  differential load only. The V<sub>OH</sub> levels are 200 mV below standard

LVPECL levels and are compatible with devices tolerant of lower common-mode ranges. The following table summarizes the DC output specifications of LVPECL.

| DC Parameter               | Min  | Max   | Min  | Max   | Min  | Max   | Units |

|----------------------------|------|-------|------|-------|------|-------|-------|

| V <sub>CCO</sub>           | 3    | 3.0   |      | 3.3   |      | 3.6   |       |

| V <sub>OH</sub>            | 1.8  | 2.11  | 1.92 | 2.28  | 2.13 | 2.41  | V     |

| V <sub>OL</sub>            | 0.96 | 1.27  | 1.06 | 1.43  | 1.30 | 1.57  | V     |

| V <sub>IH</sub>            | 1.49 | 2.72  | 1.49 | 2.72  | 1.49 | 2.72  | V     |

| V <sub>IL</sub>            | 0.86 | 2.125 | 0.86 | 2.125 | 0.86 | 2.125 | V     |

| Differential input voltage | 0.3  | -     | 0.3  | -     | 0.3  | -     | V     |

# **IOB Output Switching Characteristics**

Output delays terminating at a pad are specified for LVTTL with 12 mA drive and fast slew rate. For other standards, adjust the delays with the values shown in IOB Output Delay Adjustments for Different Standards(1), page 40.

|                                             |                                                                    |         | Speed | l Grade |     |       |

|---------------------------------------------|--------------------------------------------------------------------|---------|-------|---------|-----|-------|

|                                             |                                                                    | _'      | 7     | -(      | 6   |       |

| Symbol                                      | Description                                                        | Min     | Max   | Min     | Max | Units |

| Propagation Delays                          |                                                                    |         |       |         |     |       |

| T <sub>IOOP</sub>                           | O input to pad                                                     | 1.0     | 2.7   | 1.0     | 2.9 | ns    |

| T <sub>IOOLP</sub>                          | O input to pad via transparent latch                               | 1.2     | 3.1   | 1.2     | 3.4 | ns    |

| 3-state Delays                              |                                                                    |         |       |         |     | 1     |

| T <sub>IOTHZ</sub>                          | T input to pad high impedance <sup>(1)</sup>                       | 0.7     | 1.7   | 0.7     | 1.9 | ns    |

| T <sub>IOTON</sub>                          | T input to valid data on pad                                       | 1.1     | 2.9   | 1.1     | 3.1 | ns    |

| T <sub>IOTLPHZ</sub>                        | T input to pad high impedance via transparent latch <sup>(1)</sup> | 8.0     | 2.0   | 0.8     | 2.2 | ns    |

| T <sub>IOTLPON</sub>                        | T input to valid data on pad via transparent latch                 | 1.2     | 3.2   | 1.2     | 3.4 | ns    |

| T <sub>GTS</sub>                            | GTS to pad high impedance <sup>(1)</sup>                           | 1.9     | 4.6   | 1.9     | 4.9 | ns    |

| Sequential Delays                           |                                                                    |         |       |         |     |       |

| T <sub>IOCKP</sub>                          | Clock CLK to pad                                                   | 0.9     | 2.8   | 0.9     | 2.9 | ns    |

| T <sub>IOCKHZ</sub>                         | Clock CLK to pad high impedance (synchronous) <sup>(1)</sup>       | 0.7     | 2.0   | 0.7     | 2.2 | ns    |

| T <sub>IOCKON</sub>                         | Clock CLK to valid data on pad (synchronous)                       | 1.1     | 3.2   | 1.1     | 3.4 | ns    |

| Setup/Hold Times wit                        | th Respect to Clock CLK                                            |         |       |         |     | 1     |

| T <sub>IOOCK</sub> / T <sub>IOCKO</sub>     | O input                                                            | 1.0 / 0 | -     | 1.1 / 0 | -   | ns    |

| T <sub>IOOCECK</sub> / T <sub>IOCKOCE</sub> | OCE input                                                          | 0.7 / 0 | -     | 0.7 / 0 | -   | ns    |

| T <sub>IOSRCKO</sub> / T <sub>IOCKOSR</sub> | SR input (OFF)                                                     | 0.9 / 0 | -     | 1.0 / 0 | -   | ns    |

| T <sub>IOTCK</sub> / T <sub>IOCKT</sub>     | 3-state setup times, T input                                       | 0.6 / 0 | -     | 0.7 / 0 | -   | ns    |

| T <sub>IOTCECK</sub> / T <sub>IOCKTCE</sub> | 3-state setup times, TCE input                                     | 0.6 / 0 | -     | 0.8 / 0 | -   | ns    |

| T <sub>IOSRCKT</sub> / T <sub>IOCKTSR</sub> | 3-state setup times, SR input (TFF)                                | 0.9 / 0 | -     | 1.0 / 0 | -   | ns    |

| Set/Reset Delays                            |                                                                    |         |       |         |     |       |

| T <sub>IOSRP</sub>                          | SR input to pad (asynchronous)                                     | 1.2     | 3.3   | 1.2     | 3.5 | ns    |

| T <sub>IOSRHZ</sub>                         | SR input to pad high impedance (asynchronous) <sup>(1)</sup>       | 1.0     | 2.4   | 1.0     | 2.7 | ns    |

| T <sub>IOSRON</sub>                         | SR input to valid data on pad (asynchronous)                       | 1.4     | 3.7   | 1.4     | 3.9 | ns    |

| T <sub>IOGSRQ</sub>                         | GSR to pad                                                         | 3.8     | 8.5   | 3.8     | 9.7 | ns    |

#### Notes:

1. Three-state turn-off delays should not be adjusted.

# **IOB Output Delay Adjustments for Different Standards(1)**

Output delays terminating at a pad are specified for LVTTL with 12 mA drive and fast slew rate. For other standards, adjust the delays by the values shown. A delay adjusted in this way constitutes a worst-case limit.

|                         |                                                       |                   | Speed | I Grade |       |

|-------------------------|-------------------------------------------------------|-------------------|-------|---------|-------|

| Symbol                  | Description                                           | Standard          | -7    | -6      | Units |

| Output Delay Adju       | stments (Adj)                                         |                   |       |         |       |

| T <sub>OLVTTL_S2</sub>  | Standard-specific adjustments for                     | LVTTL, Slow, 2 mA | 14.7  | 14.7    | ns    |

| T <sub>OLVTTL_S4</sub>  | output delays terminating at pads                     | 4 mA              | 7.5   | 7.5     | ns    |

| T <sub>OLVTTL_S6</sub>  | (based on standard capacitive load, C <sub>SL</sub> ) | 6 mA              | 4.8   | 4.8     | ns    |

| T <sub>OLVTTL_S8</sub>  | , -3[/                                                | 8 mA              | 3.0   | 3.0     | ns    |

| T <sub>OLVTTL_S12</sub> |                                                       | 12 mA             | 1.9   | 1.9     | ns    |

| T <sub>OLVTTL_S16</sub> |                                                       | 16 mA             | 1.7   | 1.7     | ns    |

| T <sub>OLVTTL_S24</sub> |                                                       | 24 mA             | 1.3   | 1.3     | ns    |

| T <sub>OLVTTL_F2</sub>  |                                                       | LVTTL, Fast, 2 mA | 13.1  | 13.1    | ns    |

| T <sub>OLVTTL_F4</sub>  |                                                       | 4 mA              | 5.3   | 5.3     | ns    |

| T <sub>OLVTTL_F6</sub>  |                                                       | 6 mA              | 3.1   | 3.1     | ns    |

| T <sub>OLVTTL_F8</sub>  |                                                       | 8 mA              | 1.0   | 1.0     | ns    |

| T <sub>OLVTTL_F12</sub> |                                                       | 12 mA             | 0     | 0       | ns    |

| T <sub>OLVTTL_F16</sub> |                                                       | 16 mA             | -0.05 | -0.05   | ns    |

| T <sub>OLVTTL_F24</sub> |                                                       | 24 mA             | -0.20 | -0.20   | ns    |

| T <sub>OLVCMOS2</sub>   |                                                       | LVCMOS2           | 0.09  | 0.09    | ns    |

| T <sub>OLVCMOS18</sub>  |                                                       | LVCMOS18          | 0.7   | 0.7     | ns    |

| T <sub>OLVDS</sub>      |                                                       | LVDS              | -1.2  | -1.2    | ns    |

| T <sub>OLVPECL</sub>    |                                                       | LVPECL            | -0.41 | -0.41   | ns    |

| T <sub>OPCl33_3</sub>   |                                                       | PCI, 33 MHz, 3.3V | 2.3   | 2.3     | ns    |

| T <sub>OPCI66_3</sub>   |                                                       | PCI, 66 MHz, 3.3V | -0.41 | -0.41   | ns    |

| T <sub>OGTL</sub>       |                                                       | GTL               | 0.49  | 0.49    | ns    |

| T <sub>OGTLP</sub>      |                                                       | GTL+              | 0.8   | 0.8     | ns    |

| T <sub>OHSTL_I</sub>    |                                                       | HSTL I            | -0.51 | -0.51   | ns    |

| T <sub>OHSTL_III</sub>  |                                                       | HSTL III          | -0.91 | -0.91   | ns    |

| T <sub>OHSTL_IV</sub>   |                                                       | HSTL IV           | -1.01 | -1.01   | ns    |

| T <sub>OSSTL2_I</sub>   |                                                       | SSTL2 I           | -0.51 | -0.51   | ns    |

| T <sub>OSSLT2_II</sub>  |                                                       | SSTL2 II          | -0.91 | -0.91   | ns    |

| T <sub>OSSTL3_I</sub>   |                                                       | SSTL3 I           | -0.51 | -0.51   | ns    |

| T <sub>OSSTL3_II</sub>  |                                                       | SSTL3 II          | -1.01 | -1.01   | ns    |

| T <sub>OCTT</sub>       |                                                       | CTT               | -0.61 | -0.61   | ns    |

| T <sub>OAGP</sub>       |                                                       | AGP               | -0.91 | -0.91   | ns    |

#### Notes:

Output timing is measured at 1.4V with 35 pF external capacitive load for LVTTL. For other I/O standards and different loads, see the tables Constants for Calculating T<sub>IOOP</sub> and Delay Measurement Methodology, page 41.

Spartan-IIE FPGA Family: DC and Switching Characteristics

# **Revision History**

| Date       | Version | Description                                                                                                                                                                                                                                                    |

|------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/15/2001 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                        |

| 06/28/2002 | 1.1     | Added -7 speed grade and extended DLL specs to Industrial.                                                                                                                                                                                                     |

| 11/18/2002 | 2.0     | Added XC2S400E and XC2S600E. Added minimum specifications. Added reference to XAPP450 for Power-On Requirements. Removed Preliminary designation.                                                                                                              |

| 07/09/2003 | 2.1     | Added I <sub>CCINTQ</sub> typical values. Reduced ICCPO power-on current requirements. Relaxed TCCPO power-on ramp requirements. Added IHSPO to describe current in hot-swap applications. Updated TPSFD / TPHFD description to indicate use of delay element. |

| 06/18/2008 | 2.3     | Updated I/O measurement thresholds. Updated all modules for continuous page, figure, and table numbering. Updated links. Synchronized all modules to v2.3.                                                                                                     |

| 08/09/2013 | 3.0     | This product is obsolete/discontinued per XCN12026.                                                                                                                                                                                                            |

# — OBSOLETE — OBSOLETE — OBSOLETE —

Spartan-IIE FPGA Family: DC and Switching Characteristics

# Low Voltage Differential Signals (LVDS and LVPECL)

The Spartan-IIE family features low-voltage differential signaling (LVDS and LVPECL). Each signal utilizes two pins on the Spartan-IIE device, known as differential pin pairs. Each differential pin pair has a Positive (P) and a Negative (N) pin. These pairs are labeled in the following manner.

I/O, L#[P/N][-/\_Y/\_YY]

where

L = LVDS or LVPECL pin

# = Pin pair number

P = Positive

N = Negative

\_Y = Asynchronous output allowed (device-dependent)

\_YY = Asynchronous output allowed (all devices)

# **Available Differential Pairs According to Package Type**

| Device   | TQ144 | PQ208 | FT256 | FG456 | FG676 |

|----------|-------|-------|-------|-------|-------|

| XC2S50E  | 28    | 50    | 83    | -     | -     |

| XC2S100E | 28    | 50    | 83    | 86    | -     |

| XC2S150E | -     | 50    | 83    | 114   | -     |

| XC2S200E | -     | 50    | 83    | 120   | -     |

| XC2S300E | -     | 50    | 83    | 120   | -     |

| XC2S400E | -     | -     | 83    | 120   | 172   |

| XC2S600E | -     | -     | -     | 120   | 205   |

# **Synchronous or Asynchronous**

I/O pins for differential signals can either be synchronous or asynchronous, input or output. Differential signaling requires the pins of each pair to switch simultaneously. If the output signals driving the pins are from IOB flip-flops, they are synchronous. If the signals driving the pins are from internal logic, they are asynchronous, and therefore more care must be taken that they are simultaneous. Any differential pairs can be used for synchronous input and output signals as well as asynchronous input signals.

However, only the differential pairs with the \_Y or \_YY suffix can be used for asynchronous output signals.

### **Asynchronous Output Pad Name Designation**

Because of differences between densities, the differential pairs that can be used for asynchronous outputs vary by device. The pairs that are available in all densities for a given package have the \_YY suffix. These pins should be used for differential asynchronous outputs if the design may later move to a different density. All other differential pairs that can be used for asynchronous outputs have the \_Y suffix.

To simplify the following tables, the "Pad Name" column shows the part of the name that is common across densities. The "Pad Name" column leaves out the \_Y suffix and the "LVDS Asynchronous Output Option" column indicates the densities that allow asynchronous outputs for LVDS or LVPECL on the given pin.

#### **DLL Pins**

Pins labeled "I/O (DLL)" can be used as general-purpose I/O or as inputs to the DLL. Adjacent DLL pins form a differential pair. They reside in two different banks, so if they are outputs the  $V_{CCO}$  level must be the same for both banks. Each DLL pin can also be paired with the adjacent GCK clock pin for a differential clock input. The "I/O (DLL)" pin always becomes the N terminal when paired with GCK, even if it is labeled "P" for its pairing with the adjacent DLL pin.

#### **VREF Pins**

Pins labeled "I/O, VREF" can be used as either an I/O or a VREF pin. If any I/O pin within the bank requires a VREF input, all the VREF pins in the bank must be connected to the same voltage. See the I/O banking rules in the Functional Description module for more detail. If no pin in a given bank requires VREF, then that bank's VREF pins can be used as general I/O.

To simplify the following tables, the "Pad Name" column shows the part of the name that is common across densities. When VREF is only available in limited densities, the "Pad Name" column leaves out the VREF designation and the "VREF Option" column indicates the densities that provide VREF on the given pin.

#### **VCCO Banks**

In the TQ144 and PQ208 packages, the eight banks have VCCO connected together. Thus, only one VCCO is allowed in these packages, although different VREF values are allowed in each of the eight banks. See I/O Banking.

# TQ144 Pinouts (XC2S50E and XC2S100E) (Continued)

| Pad Name                            | <b>.</b> |     | LVDS                       |                            |  |

|-------------------------------------|----------|-----|----------------------------|----------------------------|--|

| Function                            | Bank     | Pin | Async.<br>Output<br>Option | V <sub>REF</sub><br>Option |  |

| I/O (DLL), L17P                     | 4        | P56 | -                          | -                          |  |

| I/O                                 | 4        | P57 | -                          | -                          |  |

| I/O, VREF<br>Bank 4                 | 4        | P58 | -                          | All                        |  |

| I/O, L16N_YY                        | 4        | P59 | All                        | -                          |  |

| I/O, L16P_YY                        | 4        | P60 | All                        | -                          |  |

| VCCINT                              | -        | P61 | -                          | -                          |  |

| GND                                 | -        | P62 | -                          | -                          |  |

| I/O, L15N_YY                        | 4        | P63 | All                        | -                          |  |

| I/O, L15P_YY                        | 4        | P64 | All                        | XC2S100E                   |  |

| I/O                                 | 4        | P65 | -                          | -                          |  |

| I/O, VREF<br>Bank 4                 | 4        | P66 | -                          | All                        |  |

| I/O                                 | 4        | P67 | -                          | -                          |  |

| I/O, L14N_YY                        | 4        | P68 | All                        | -                          |  |

| I/O, L14P_YY                        | 4        | P69 | All                        | -                          |  |

| GND                                 | -        | P70 | -                          | -                          |  |

|                                     |          |     |                            |                            |  |

| DONE                                | 3        | P71 | -                          | -                          |  |

| VCCO                                | -        | P72 | -                          | -                          |  |

| PROGRAM                             | -        | P73 | -                          | -                          |  |

| I/O ( <del>INIT</del> ),<br>L13N_YY | 3        | P74 | All                        | -                          |  |

| I/O (D7),<br>L13P_YY                | 3        | P75 | All                        | -                          |  |

| I/O                                 | 3        | P76 | -                          | -                          |  |

| I/O, VREF<br>Bank 3                 | 3        | P77 | -                          | All                        |  |

| I/O                                 | 3        | P78 | -                          | -                          |  |

| I/O, L12N                           | 3        | P79 | XC2S50E                    | XC2S100E                   |  |

| I/O (D6), L12P                      | 3        | P80 | XC2S50E                    | -                          |  |

| GND                                 | -        | P81 | -                          | -                          |  |

| I/O (D5),<br>L11N_YY                | 3        | P82 | All                        | -                          |  |

| I/O, L11P_YY                        | 3        | P83 | All                        | -                          |  |

| I/O                                 | 3        | P84 | -                          | -                          |  |

# TQ144 Pinouts (XC2S50E and XC2S100E) (Continued)

| Function         Bank         Pin         Async. Output Option Option         VREF Option           I/O, VREF Bank 3, L10N         3         P85         XC2S50E         All           I/O (D4), L10P         3         P86         XC2S50E         -           I/O (D4), L10P         3         P87         -         -           VCCINT         -         P88         -         -           I/O (TRDY)         3         P89         -         -           VCCO         -         P90         -         -           GND         -         P91         -         -           I/O (IRDY)         2         P92         -         -           I/O (IRDY)         2         P93         -         -           I/O (D3), L9N         2         P94         XC2S50E         -           I/O, VREF Bank 2, L9P         2         P95         XC2S50E         All           I/O, L8N_YY         2         P96         -         -           I/O, L8N_YY         2         P97         All         -           I/O (D1), L7N         2         P100         XC2S50E         -           I/O, VREF Bank 2         2 <td< th=""><th colspan="2">Pad Name</th><th></th><th>LVDS</th><th></th></td<>                                                                                                                                                                                                                                                                                    | Pad Name       |   |      | LVDS    |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---|------|---------|----------|

| I/O, VREF Bank 3, L10N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |   |      | Output  |          |

| Bank 3, L10N         Bank 3, L10N< |                |   |      | -       | -        |

| I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                | 3 | P85  | XC2S50E | All      |

| VCCINT         -         P88         -         -           I/O (TRDY)         3         P89         -         -           VCCO         -         P90         -         -           GND         -         P91         -         -           I/O (IRDY)         2         P91         -         -           I/O (IRDY)         2         P92         -         -           I/O (D3), L9N         2         P93         -         -           I/O (D3), L9N         2         P94         XC2S50E         -           I/O, VREF Bank 2, L9P         2         P95         XC2S50E         All           I/O         2         P96         -         -         -           I/O (D2), L8N_YY         2         P97         All         -           I/O (D2), L8N_YY         2         P98         All         -           I/O (D2), L8N_YY         2         P98         All         -           I/O (D1), L7N         2         P100         XC2S50E         -           I/O, L7P         2         P101         XC2S50E         XC2S100E           I/O, VREF Bank 2         2                                                                                                                                                                                                                                                                                                                                                                                                   | I/O (D4), L10P | 3 | P86  | XC2S50E | -        |

| I/O (TRDY)   3   P89   -   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O            | 3 | P87  | -       | -        |

| VCCO         -         P90         -         -           GND         -         P91         -         -           BND         -         P91         -         -           I/O (IRDY)         2         P92         -         -           I/O         2         P93         -         -           I/O (D3), L9N         2         P94         XC2S50E         -           I/O, VREF Bank 2, L9P         2         P95         XC2S50E         All           I/O, L8N_YY         2         P96         -         -           I/O, L8N_YY         2         P98         All         -           I/O (D2), L8P_YY         2         P98         All         -           I/O (D2), L8P_YY         2         P98         All         -           I/O (D1), L7N         2         P100         XC2S50E         XC2S100E           I/O, L7P         2         P101         XC2S50E         XC2S100E           I/O, VREF Bank 2         2         P103         -         All           I/O (DIN, D0), L6N_YY         2         P105         All         -           I/O (DOUT, BUSY), L6P_YY         2         P106                                                                                                                                                                                                                                                                                                                                                                    | VCCINT         | - | P88  | -       | -        |

| I/O (IRDY)   2   P92   -   -     I/O (D3), L9N   2   P94   XC2S50E   -     I/O, VREF   2   P95   XC2S50E   All     I/O, L8N_YY   2   P97   All   -     I/O (D2), L8P_YY   2   P98   All   -     I/O (D1), L7N   2   P100   XC2S50E   -     I/O, VREF   2   P98   All   -     I/O (D1), L7N   2   P100   XC2S50E   -     I/O, VREF   2   P101   XC2S50E   XC2S100E     I/O (D1), L7N   2   P102   -   -     I/O, VREF   2   P103   -   All     I/O (DIN, D0), L6N_YY   2   P105   All   -     I/O (DOUT, BUSY), L6P_YY   CCLK   2   P107   -   -     CCLK   2   P108   -   -     TDO   2   P109   -   -     GND   -   P110   -   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I/O (TRDY)     | 3 | P89  | -       | -        |

| I/O (IRDY)   2   P92   -   -       I/O (D3), L9N   2   P94   XC2S50E   -     I/O, VREF   2   P95   XC2S50E   All     I/O, L8N_YY   2   P96   -     -     I/O (D2), L8P_YY   2   P98   All   -     I/O (D1), L7N   2   P100   XC2S50E   -     I/O, L7P   2   P101   XC2S50E   XC2S100E     I/O (D1), L7N   2   P102   -       I/O, VREF   2   P103   -   All     Bank 2   I/O   2   P104   -   -     I/O (DIN, D0), L6N_YY   2   P105   All   -     I/O (DOUT, BUSY), L6P_YY   CCLK   2   P107   -       VCCO   -   P108   -   -     TDO   2   P109   -   -     GND   -   P110   -   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VCCO           | - | P90  | -       | -        |

| I/O         2         P93         -         -           I/O (D3), L9N         2         P94         XC2S50E         -           I/O, VREF Bank 2, L9P         2         P95         XC2S50E         All           I/O         2         P96         -         -           I/O, L8N_YY         2         P97         All         -           I/O (D2), L8P_YY         2         P98         All         -           GND         -         P99         -         -           I/O (D1), L7N         2         P100         XC2S50E         -           I/O, L7P         2         P101         XC2S50E         XC2S100E           I/O, VREF Bank 2         2         P102         -         -           I/O, VREF Bank 2         2         P103         -         All           I/O (DIN, D0), L6N_YY         2         P105         All         -           I/O (DIN, D0), L6N_YY         2         P105         All         -           I/O (DOUT, BUSY), L6P_YY         2         P106         All         -           CCLK         2         P107         -         -           VCCO         -         P108                                                                                                                                                                                                                                                                                                                                                                 | GND            | - | P91  | -       | -        |

| I/O         2         P93         -         -           I/O (D3), L9N         2         P94         XC2S50E         -           I/O, VREF Bank 2, L9P         2         P95         XC2S50E         All           I/O         2         P96         -         -           I/O, L8N_YY         2         P97         All         -           I/O (D2), L8P_YY         2         P98         All         -           GND         -         P99         -         -           I/O (D1), L7N         2         P100         XC2S50E         -           I/O, L7P         2         P101         XC2S50E         XC2S100E           I/O, VREF Bank 2         2         P102         -         -           I/O, VREF Bank 2         2         P103         -         All           I/O (DIN, D0), L6N_YY         2         P105         All         -           I/O (DIN, D0), L6N_YY         2         P105         All         -           I/O (DOUT, BUSY), L6P_YY         2         P106         All         -           CCLK         2         P107         -         -           VCCO         -         P108                                                                                                                                                                                                                                                                                                                                                                 |                |   |      |         |          |

| I/O (D3), L9N         2         P94         XC2S50E         -           I/O, VREF Bank 2, L9P         2         P95         XC2S50E         All           I/O         2         P96         -         -           I/O, L8N_YY         2         P97         All         -           I/O (D2), L8P_YY         2         P98         All         -           I/O (D2), L8P_YY         2         P98         All         -           I/O (D1), L7N         2         P100         XC2S50E         -           I/O, L7P         2         P101         XC2S50E         XC2S100E           I/O, L7P         2         P102         -         -           I/O, VREF Bank 2         P103         -         All           I/O, VREF Bank 2         P104         -         -           I/O (DIN, D0), L6N_YY         2         P105         All         -           I/O (DOUT, BUSY), L6P_YY         2         P106         All         -           CCLK         2         P107         -         -           VCCO         -         P108         -         -           TDO         2         P109         -         -                                                                                                                                                                                                                                                                                                                                                                | I/O (IRDY)     | 2 | P92  | -       | -        |

| I/O, VREF   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I/O            | 2 | P93  | -       | -        |

| Bank 2, L9P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O (D3), L9N  | 2 | P94  | XC2S50E | -        |

| I/O, L8N_YY       2       P97       All       -         I/O (D2), L8P_YY       2       P98       All       -         GND       -       P99       -       -         I/O (D1), L7N       2       P100       XC2S50E       -         I/O, L7P       2       P101       XC2S50E       XC2S100E         I/O       2       P102       -       -         I/O, VREF Bank 2       2       P103       -       All         I/O (DIN, D0), L6N_YY       2       P105       All       -         I/O (DOUT, BUSY), L6P_YY       2       P106       All       -         CCLK       2       P107       -       -         VCCO       -       P108       -       -         TDO       2       P109       -       -         GND       -       P110       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                | 2 | P95  | XC2S50E | All      |

| I/O (D2),<br>L8P_YY       2       P98       All       -         GND       -       P99       -       -         I/O (D1), L7N       2       P100       XC2S50E       -         I/O, L7P       2       P101       XC2S50E       XC2S100E         I/O       2       P102       -       -         I/O, VREF<br>Bank 2       2       P103       -       All         I/O (DIN, D0),<br>L6N_YY       2       P104       -       -         I/O (DOUT,<br>BUSY),<br>L6P_YY       2       P106       All       -         CCLK       2       P107       -       -         VCCO       -       P108       -       -         TDO       2       P109       -       -         GND       -       P110       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I/O            | 2 | P96  | -       | -        |

| L8P_YY       -       P99       -       -         I/O (D1), L7N       2       P100       XC2S50E       -         I/O, L7P       2       P101       XC2S50E       XC2S100E         I/O       2       P102       -       -         I/O, VREF Bank 2       2       P103       -       All         I/O (DIN, D0), L6N_YY       2       P104       -       -         I/O (DOUT, BUSY), L6P_YY       2       P106       All       -         CCLK       2       P107       -       -         VCCO       -       P108       -       -         TDO       2       P109       -       -         GND       -       P110       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I/O, L8N_YY    | 2 | P97  | All     | -        |

| I/O (D1), L7N       2       P100       XC2S50E       -         I/O, L7P       2       P101       XC2S50E       XC2S100E         I/O       2       P102       -       -         I/O, VREF Bank 2       2       P103       -       All         I/O (DIN, D0), L6N_YY       2       P104       -       -         I/O (DOUT, BUSY), L6P_YY       2       P106       All       -         CCLK       2       P107       -       -         VCCO       -       P108       -       -         TDO       2       P109       -       -         GND       -       P110       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                | 2 | P98  | All     | -        |

| I/O, L7P       2       P101       XC2S50E       XC2S100E         I/O       2       P102       -       -         I/O, VREF Bank 2       2       P103       -       All         I/O       2       P104       -       -         I/O (DIN, D0), L6N_YY       2       P105       All       -         I/O (DOUT, BUSY), L6P_YY       2       P106       All       -         CCLK       2       P107       -       -         VCCO       -       P108       -       -         TDO       2       P109       -       -         GND       -       P110       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GND            | - | P99  | -       | -        |