Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 384                                                         |

| Number of Logic Elements/Cells | 1728                                                        |

| Total RAM Bits                 | 32768                                                       |

| Number of I/O                  | 102                                                         |

| Number of Gates                | 50000                                                       |

| Voltage - Supply               | 1.71V ~ 1.89V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 144-LQFP                                                    |

| Supplier Device Package        | 144-TQFP (20x20)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2s50e-6tq144c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

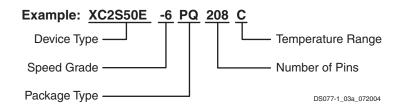

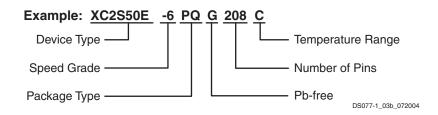

# Ordering Information

Spartan-IIE devices are available in both standard and Pb-free packaging options for all device/package combinations. The Pb-free packages include a special "G" character in the ordering code.

# Standard Packaging

# Pb-Free Packaging

# **Device Ordering Options**

| Device   | Speed Grade |                      |  |  |  |

|----------|-------------|----------------------|--|--|--|

| XC2S50E  | -6          | Standard Performance |  |  |  |

| XC2S100E | -7          | Higher Performand    |  |  |  |

| XC2S150E |             |                      |  |  |  |

| XC2S200E |             |                      |  |  |  |

| XC2S300E |             |                      |  |  |  |

| XC2S400F |             |                      |  |  |  |

| Package Type / Number of Pins |                               |  |  |  |  |  |

|-------------------------------|-------------------------------|--|--|--|--|--|

| TQ(G)14                       | TQ(G)144 144-piastic Thin QFP |  |  |  |  |  |

| PQ(G)208                      | 208-pin Plastic QFP           |  |  |  |  |  |

| FT(G)256                      | 256-ball Fine Pitch BGA       |  |  |  |  |  |

| FG(G)456                      | 456-ball Fine Pitch BGA       |  |  |  |  |  |

| FG(G)676                      | 676-ball Fine Pitch BGA       |  |  |  |  |  |

| Temperature Range (Ţ) <sup>(2)</sup> |              |  |  |  |  |  |

|--------------------------------------|--------------|--|--|--|--|--|

| C = Commercial                       | 0°C to +85°C |  |  |  |  |  |

| I = Industrial 40°C to +10           |              |  |  |  |  |  |

### Notes:

XC2S600E

- 1. The -7 speed grade is exclusively available in the Commercial temperature range.

- 2. See www.xilinx.comfor information on automotive temperature range devices.

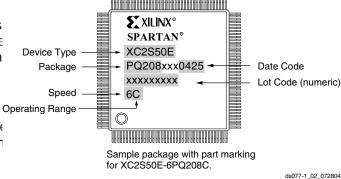

# Device Part Marking

Figure 2 is a top marking example for Spartan-IIE FPGAs in the quad-flat packages. The markings for BGA packages are nearly identical to those for the quad-flat package except that the marking is rotated with respect to the ba indicator.

The "7c" and "b" Speed Grade/Temperature Range part combinations may be dual marked asc"/61". Devices with the dual mark can be used as either -7C or -6I device Devices with a single mark are only guaranteed for the marked speed grade and temperature range.

Figure 2: Spartan-IIE QFP Marking Example

Spartan-IIE FPGA Family: Introduction and Ordering Information

# **Revision History**

| Date       | Version | Description                                                                                                                                                           |

|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06/27/200  | 2 1.1   | Updated -7 availability.                                                                                                                                              |

| 11/18/2002 | 2 2.0   | Added XC2S400E and XC2S600E. Correct XC2S150E max I/O count and XC2S50E differential I/O count dappdated availability.                                                |

| 07/09/200  | 3 2.1   | Noted hot-swap capability. Updated Tableto show that all products are available. Clarified device part marking.                                                       |

| 07/28/200  | 4 2.2   | Added information on Pb-free packaging options.                                                                                                                       |

| 06/18/200  | 8 2.3   | Added dual mark information Device Part MarkingUpdated all modules for continuous page, figure, and table numbering. Updated links. Synchronized all modules to v2.3. |

| 08/09/201  | 3 3.0   | This product is obsolete/discontinued MGM12026                                                                                                                        |

### OBSOLETE OBSOLETE

Spartan-IIE FPGA Family: Functional Description

# Configurable Logic Block

logic cell (LC). An LC includes a 4-input function generator carry logic, and storage element. The output from the function generator is contained by the carry logic carry logic. tion generator in each LC drives the CLB output or tstorage Elements D input of the flip-flop. Each Spartan-IIE FPGA CLB con Storage elements in the Spartan-IIE FPGA slice can be is shown in Figure 6.

contains logic that combines function generators to provinguts, bypassing the function generators. functions of five or six inputs.

### Look-Up Tables

Spartan-IIE FPGA function generators are implemented a function generator, each LUT can provide ax116bit syn chronous RAM. Furthermore, the two LUTs within a slice operate asynchronously. can be combined to create a \$12-bit or 321-bit syn chronous RAM, or a 161-bit dual-port synchronous RAM. shared by the two flip-flops within the slice.

The Spartan-IIE FPGA LUT can also provide a 16-bit shift The basic building block of the Spartan-IIE FPGA CLB is the data. This register that is ideal for capturing high-speed or burst-mode

tains four LCs, organized in two similar slices; a single slice configured either as edge-triggered D-type flip-flops or as level-sensitive latches. The Dpats can be driven either by In addition to the four basic LCs, the Spartan-IIE FPGA CLIfunction generators within the slice or directly from slice

In addition to Clock and Clock Enable signals, each slice has synchronous set and reset signals (SR and BY). SR forces a storage element into the initialization state speci fied for it in the configuration. BY forces it into the opposite 4-input look-up tables (LUTs). In addition to operating as state. Alternatively, these signals may be configured to

All control signals are independently invertible, and are

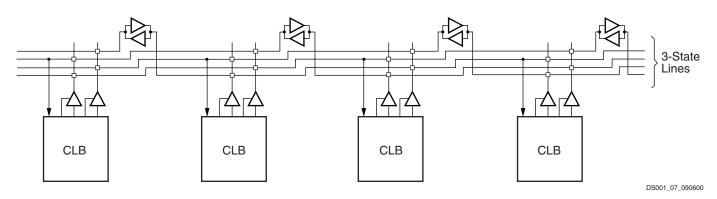

### **Dedicated Routing**

Some classes of signal require dedicated routing resources to maximize performance. In the Spartan-IIE FPGA archi tecture, dedicated routing resources are provided for two classes of signal.

Horizontal routing resources are provided for on-chip 3-state busses. Four partitionable bus lines are provided per CLB row, permitting multiple busses within a row, as shownFigure 10.

Two dedicated nets per CLB propagate carry signals vertically to the adjacent CLB.

Figure 10: BUFT Connections to Dedicated Horizontal Bus Lines

# Global Routing

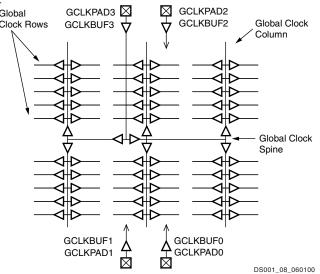

Global Routing resources distribute clocks and other signal purpose routing. nals with very high fanout throughout the device- Spar tan-IIE devices include two tiers of global routing resources referred to as primary and secondary global routing Glock Rows resources.

The primary global routing resources are four dedicated global nets with dedicated input pins that are designed to distribute high-fanout clock signals with minimal skew. Each global clock net can drive all CLB, IOB, and block RAM clock pins. The primary global nets may only be driven by global buffers. There are four global buffers, one for each global net.

The secondary global routing resources consist of 24 backbone lines, 12 across the top of the chip and 12 across the bottom. From these lines, up to 12 unique signals per column can be distributed via the 12 longlines in the column. These secondary resources are more flexible than the primary resources since they are not restricted to routing only to clock pins.

selected either from these pads or from signals in the gen

Figure 11: Global Clock Distribution Network

### Clock Distribution

The Spartan-IIE family provides high-speed, low-skew clock Pelay-Locked Loop (DLL) distribution through the primary global routing resour Associated with each global clock input buffer is a fully digi Figure 11.

primary global nets that in turn drive any clock pin.

described above. A typical clock distribution net is showntiand Delay-Locked Loop (DLL) that can eliminate skew between the clock input pad and internal clock-input pins Four global buffers are provided, two at the top center of throughout the device. Each DLL can drive two global clock device and two at the bottom center. These drive the four works. The DLL monitors the input clock and the distrib uted clock, and automatically adjusts a clock delay element (Figure 12). Additional delay is introduced such that clock Four dedicated clock pads are provided, one adjacent todges reach internal flip-flops exactly one clock period after each of the global buffers. The input to the global bufferthey arrive at the input. The input is sed-loop system effectively eliminates clock-distribution delay by ensuring that clock

Table 8: Boundary-Scan Instructions (Continued)

|                          | •                   | ,                                                             |

|--------------------------|---------------------|---------------------------------------------------------------|

| Boundary-Scan<br>Command | Binary<br>Code[4:0] | Description                                                   |

| INTEST                   | 00111               | Enables boundary-scan INTEST operation                        |

| USERCODE                 | 01000               | Enables shifting out USER code                                |

| IDCODE                   | 01001               | Enables shifting out of ID Code                               |

| HIGHZ                    | 01010               | Disables output pins<br>while enabling the<br>Bypass Register |

| JSTART                   | 01100               | Clock the start-up<br>sequence when<br>StartupClk is TCK      |

| BYPASS                   | 11111               | Enables BYPASS                                                |

| RESERVED                 | All other codes     | Xilinx reserved instructions                                  |

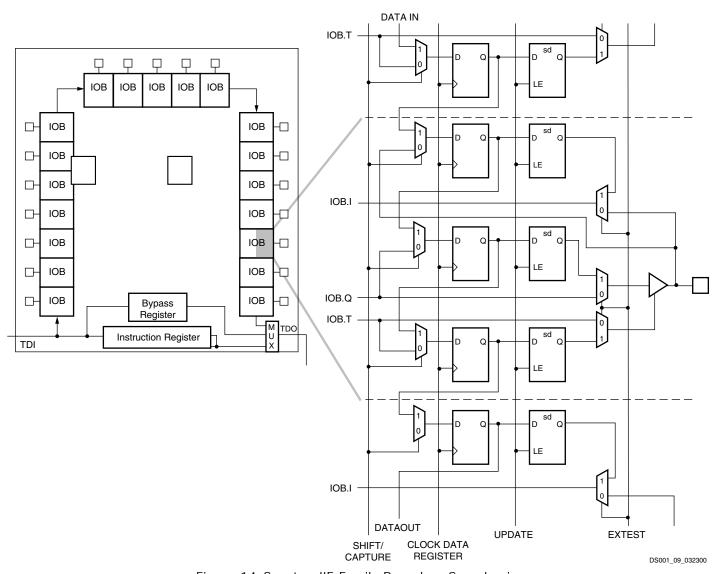

The public boundary-scan instructions are available prior to configuration, except for USER1 and USER2. After configuration, the public instructions and available together with any USERCODE instructions intalled during the configuration. While the SAMPLE/PRELOAD and BYPASS instructions are available during configuration, it is recommended that boundary-scan operations not be performed during this transitional period.

In addition to the test instructions outlined above, the boundary-scan circuitry can be used to configure the FPGA, and also to read back the configuration data.

To facilitate internal scan chains, the User Register provides three outputs (Reset, Update, and Shift) that represent the corresponding states in the boundary-scan internal state machine.

Figure 14 is a diagram of the Spartan-IIE family boundary scan logic. It includes three bits of Data Register per IOB, the IEEE 1149.1 Test Access Port controller, and the Instruction Register with decodes.

Figure 14: Spartan-IIE Family Boundary Scan Logic

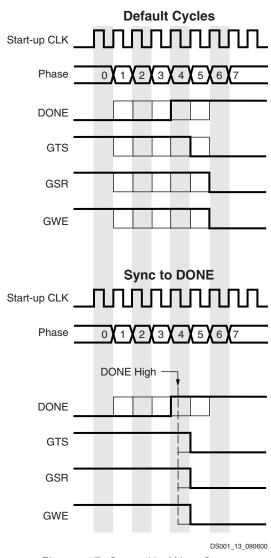

During start-up, the device performs four operations:

- 1. The assertion of DONE. Theallure of DONE to go High may indicate the unsuccessful loading of configuration data.

- The release of the Global Three State (GTS). This activates all the I/Os to which signals are assigned. The remaining I/Os stay in a high-impedance state with internal weak pull-up resistors present.

- 3. The release of the Global Set Reset (GSR). This allows all flip-flops to change state.

- 4. The assertion of Global Write Enable (GWE). This allows all RAMs and flip-flops to change state.

By default, these operations are synchronized to CCLK. The entire start-up sequence lasts eight cycles, called CO-C7, after which the loaded design is fully functional. The four operations can be selected to switch on any CCLK through settings C1-C6 in the DevelopmentSoftware. The default timing for start-up is shown in the top halfForfure 17; heavy lines show default settinas.

The default Start-up sequence is that one CCLK cycle after DONE goes High, the global 3-state signal (GTS) is released. This permits device outputs to turn on as neces sary.

One CCLK cycle later, the Global Set/Reset (GSR) and Global Write Enable (GWE) signals are released. This per mits the internal storage elements to begin changing state in response to the logic and the user clock.

The bottom half of figure 17 shows another commonly used version of the start-up timing known as Sync-to-DONE. This version makes the GTS, GSR, and GWE events conditional uporthe DONE pin going High. This timing is important foodaisy chain of multiple FPGAs in serial mode, since it ensures that all FPGAs go through start-up together, after all their DONE pins have gone High.

Sync-to-DONE timing is selected by setting the GTS, GSR, Serial Modes cycle after DONE externally transitions High.

has been achieved on any or all DLLs.

Figure 17: Start-Up Waveforms

and GWE cycles to a value of DONE in the configuration here are two serial configuration modes. In Master Serial options. This causes these signals to transition one clockode, the FPGA controls the configuration process by driv ing CCLK as an output. In Slave Serial mode, the FPGA The sequence can also be paused at any stage until lookassively receives CCLK as an input from an external agent (e.g., a microprocessor, CPLD, or second FPGA in master mode) that is controlling then formuration process. In both

modes, the FPGA is configured by loading one bit per CCLK cycle. The MSB of each configuration data byte is always written to the DIN pin first.

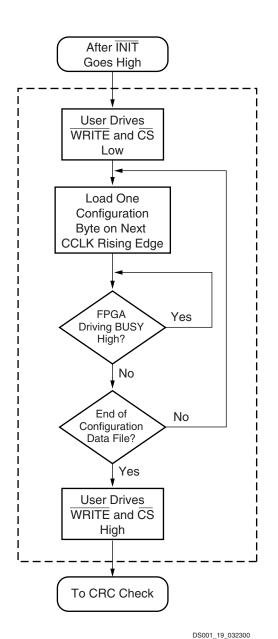

See Figure 18 for the sequence for loading data into the Spartan-IIE FPGA serially. This is an expansion of the "Load Configuration Data Frames" block Fingure 16, page 23 Note tha CS and WRITE are not normally used during serial configuration. To ensure successful loading of the FPGA, do not toggleVRITE with CS Low during serial configuration.

If CCLK is slower than CENH, the FPGA will never assert tions. However, to avoid aborting configurational times assert tions. BUSY. In this case, the above handshake is unnecessary, must continue to be asserted working and data can simply be entered into the FPGA every CCLKCCLK transitions. cycle.

Figure 21: Loading Configuration Data for the Slave Parallel Mode

A configuration packet does not have to be written in Readback continuous stretch, rathercath be split into many write The configuration data stored in the Spartan-IIE FPGA con sequences. Each sequence would involve assertion contains

loaded into the Slave Paralleltierface, a new byte of data RAMs. This capability is usefor real-time debugging. may not be ready for each consecutive CCLK edge. In suchor more detailed information at the consecutive CCLK edge. In suchor more detailed information at the consecutive CCLK edge. is valid on DO-D7. Whiles is High, the Slave Parallel inter and Spartan-IIE FPGA Families.

To abort configuration during a write sequence, deassert WRITE while holding Low. The abort operation is initi ated at the rising edge 6CLK. The device will remain BUSY until the aborted operation is complete. After aborting configuration, data is assumed to be unaligned to word boundaries and the FPGA requires a new synchronization word prior to accepting any new packets.

# Boundary-Scan Configuration Mode

In the boundary-scan mode, no nondedicated pins are required, configuration being done entirely through the IEEE 1149.1 TestAccess Port (TAP).

Configuration through the TAP uses the special CFG\_IN instruction. This instruction be converted into data packets for the internal configuration

The following steps are required to configure the FPGA through the boundary-scan port.

- 1. Load the CFG\_IN instruction into the boundary-scan instruction register (IR)

- 2. Enter the Shift-DR (SDR) state

- 3. Shift a standard configuration bitstream into TDI

- 4. Return to Run-Test-Idle (RTI)

- 5. Load the JSTART instruction into IR

- 6. Enter the SDR state

- Clock TCK (if selected) through the startup sequence (the length is programmable)

- 8. Return to RTI

Configuration and readback via the TAP is always available. The boundary-scan mode simply locks out the other modes. The boundary-scan mode is selected by a <10x> on the mode pins (MO, M1, M2). Note that PROGRAM pin must be pulled High prior to reconfiguration. A Low on Robe GRAM pin resets the TAP controller and no boundary scan operations can be performedee Xilinx Application Note XAPP188 for more information on boundary-scan configu ration.

figuration memory can be read back for verification. Along In applications where multiputeock cycles may be required with the configuration datasipossible to read back the to access the configuration data before each byte can contents of all flip-flops/latches, LUT RAMs, and block a case the Signal may be deasserted until the next byte APP176, Configuration and Readback of the Spartan-II face does not expect any data and ignores all CCLK transi

# **DLL Timing Parameters**

Because of the difficulty in directly measuring many intermatrst-case values across the recommended operating con timing parameters, those parameters are derived froditions. benchmark timing patterns. The following guidelines reflect

|                      |                                  |                    | Speed Grade |     |     |     |       |

|----------------------|----------------------------------|--------------------|-------------|-----|-----|-----|-------|

|                      |                                  | Ī                  | -           | 7   | -   | 6   |       |

| Symbol               | Description                      | F <sub>CLKIN</sub> | Min         | Max | Min | Max | Units |

| F <sub>CLKINHF</sub> | Input clock frequency (CLKDLLHF) | -                  | 60          | 320 | 60  | 275 | MHz   |

| F <sub>CLKINLF</sub> | Input clock frequency (CLKDLL)   | -                  | 25          | 160 | 25  | 135 | MHz   |

| T <sub>DLLPW</sub>   | Input clock pulse width          | 25 MHz             | 5.0         | -   | 5.0 | -   | ns    |

|                      |                                  | 50 MHz             | 3.0         | -   | 3.0 | -   | ns    |

|                      |                                  | 100 MHz            | 2.4         | -   | 2.4 | -   | ns    |

|                      |                                  | 150 MHz            | 2.0         | -   | 2.0 | -   | ns    |

|                      |                                  | 200 MHz            | 1.8         | -   | 1.8 | -   | ns    |

|                      |                                  | 250 MHz            | 1.5         | -   | 1.5 | -   | ns    |

|                      |                                  | 300 MHz            | 1.3         | -   | NA  | -   |       |

# DLL Clock Tolerance, Jitter, and Phase Information

All DLL output jitter and phase specifications were-detergure 22, page 44, provides definitions for various parame mined through statistical measurement at the package pites in the table below. using a clock mirror configuration and matched drivers.

|                     |                                               |                    | CLKDI | LLHF  | CLKI | DLL   |       |

|---------------------|-----------------------------------------------|--------------------|-------|-------|------|-------|-------|

| Symbol              | Description                                   | F <sub>CLKIN</sub> | Min   | Max   | Min  | Max   | Units |

| T <sub>IPTOL</sub>  | Input clock period tolerance                  |                    | -     | 1.0   | -    | 1.0   | ns    |

| T <sub>IJITCC</sub> | Input clock jitter tolerance (cycle-to-cycle) |                    | -     | -150  | -    | - 300 | ps    |

| T <sub>LOCK</sub>   | Time required for DLL to acquire 160k         | > 60 MHz           | -     | 20    | -    | 20    | μs    |

|                     |                                               | 50-60 MHz          | -     | -     | -    | 25    | μs    |

|                     |                                               | 40-50 MHz          | -     | -     | -    | 50    | μs    |

|                     |                                               | 30-40 MHz          | -     | -     | -    | 90    | μs    |

|                     |                                               | 25-30 MHz          | -     | -     | -    | 120   | μs    |

| T <sub>OJITCC</sub> | Output jitter (cycle-to-cycle) for any DLL c  | lock Wtput         | -     | - 60  | -    | - 60  | ps    |

| T <sub>PHIO</sub>   | Phase offset between CLKIN and CLK®           |                    | -     | -100  | -    | -100  | ps    |

| T <sub>PHOO</sub>   | Phase offset between clock outputs on the DLL |                    | -     | -140  | -    | -140  | ps    |

| T <sub>PHIOM</sub>  | Phase difference between CLKIN and CLK®       |                    | -     | -160  | -    | -160  | ps    |

| T <sub>PHOOM</sub>  | Phase difference between clock outputs or     | n théÓDLL          | -     | - 200 | -    | - 200 | ps    |

### Notes:

- 1. Commercial operating conditions. Add 30% for Industrial operating conditions.

- 2. Output Jitteris cycle-to-cycle jitter meæsuon the DLLoutput clockexcludinginput clock jitter.

- Phase Offset between CLKIN and CLKO is the worst-case fixed time differ between rising edges of CLKIN and CLKO, excluding output jitter and input clock jitter.

- 4. Phase Offset between Clok Outputs on the DLLis the worst-case fixed time difference between rising edges of any two DLL outputsexcluding output jitter and input clock jitter.

- 5. Maximum Phase Differencebetween CLKIN and CLKO is the sum of output jitter and phase offset between CLKIN and CLKO, or the greatest difference between CLKIN and CLKO rising edges due to DLL akaded(nginput clock jitter).

- 6. Maximum Phase Difference between Clock Outputs on the DLLis the sum of output jitted phase offset between any DLL clock outputs, or the greatest difference between any two DLL output rising edges due to Addualingenout clock jitter).

Spartan-IIE FPGA Family: DC and Switching Characteristics

52