Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | F <sup>2</sup> MC-16FX                                                         |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, UART/USART                                      |

| Peripherals                | DMA, LCD, LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 50                                                                             |

| Program Memory Size        | 96KB (96K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                    |

| Data Converters            | A/D 12x8/10b                                                                   |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-LQFP                                                                        |

| Supplier Device Package    | 64-LQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb96f673abpmc1-gse1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Built-in On Chip Debugger (OCD)

□ One-wire debug tool interface

Break function:

- Hardware break: 6 points (shared with code event)

- Software break: 4096 points

□ Event function

- Code event: 6 points (shared with hardware break)

- Data event: 6 points

- Event sequencer: 2 levels + reset

- Execution time measurement function

- □ Trace function: 42 branches

- □ Security function

- Flash Memory

- □ Dual operation flash allowing reading of one Flash bank while programming or erasing the other bank

- Command sequencer for automatic execution of programming algorithm and for supporting DMA for programming of the Flash Memory

- □ Supports automatic programming, Embedded Algorithm

- UVrite/Erase/Erase-Suspend/Resume commands

- □ A flag indicating completion of the automatic algorithm

- □ Erase can be performed on each sector individually □ Sector protection

- □ Flash Security feature to protect the content of the Flash

- □ Low voltage detection during Flash erase or write

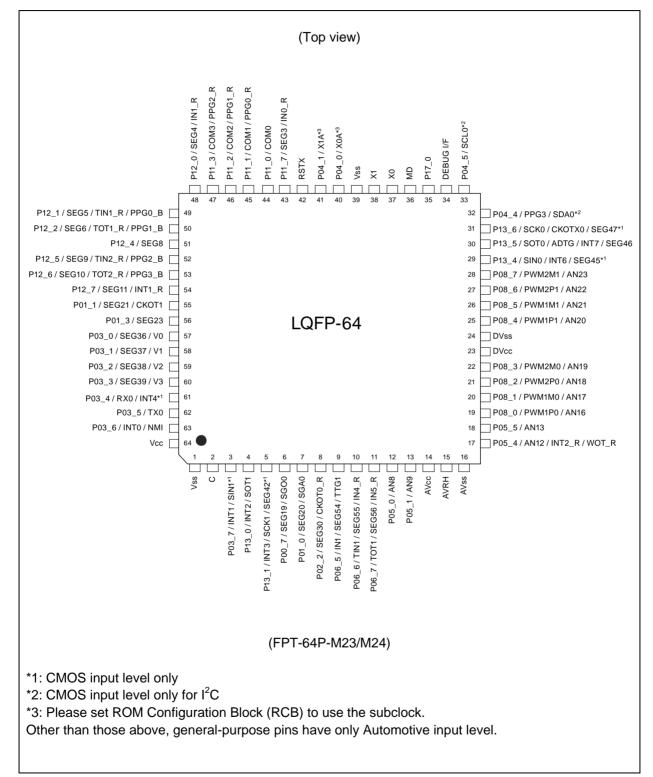

## 3. Pin Assignment

| Pin name | Feature | Description                          |  |  |

|----------|---------|--------------------------------------|--|--|

| Vn       | LCD     | LCD voltage reference pin            |  |  |

| Vcc      | Supply  | Power supply pin                     |  |  |

| Vss      | Supply  | Power supply pin                     |  |  |

| WOT_R    | RTC     | Relocated Real Time clock output pin |  |  |

| X0       | Clock   | Oscillator input pin                 |  |  |

| X0A      | Clock   | Subclock Oscillator input pin        |  |  |

| X1       | Clock   | Oscillator output pin                |  |  |

| X1A      | Clock   | Subclock Oscillator output pin       |  |  |

| Pin no. | I/O circuit type* | Pin name                        |

|---------|-------------------|---------------------------------|

| 33      | N                 | P04_5 / SCL0                    |

| 34      | 0                 | DEBUG I/F                       |

| 35      | н                 | P17_0                           |

| 36      | С                 | MD                              |

| 37      | A                 | X0                              |

| 38      | A                 | X1                              |

| 39      | Supply            | Vss                             |

| 40      | В                 | P04_0 / X0A                     |

| 41      | В                 | P04_1 / X1A                     |

| 42      | С                 | RSTX                            |

| 43      | J                 | P11_7 / SEG3 / IN0_R            |

| 44      | J                 | P11_0 / COM0                    |

| 45      | J                 | P11_1 / COM1 / PPG0_R           |

| 46      | J                 | P11_2 / COM2 / PPG1_R           |

| 47      | J                 | P11_3 / COM3 / PPG2_R           |

| 48      | J                 | P12_0 / SEG4 / IN1_R            |

| 49      | J                 | P12_1 / SEG5 / TIN1_R / PPG0_B  |

| 50      | J                 | P12_2 / SEG6 / TOT1_R / PPG1_B  |

| 51      | J                 | P12_4 / SEG8                    |

| 52      | J                 | P12_5 / SEG9 / TIN2_R / PPG2_B  |

| 53      | J                 | P12_6 / SEG10 / TOT2_R / PPG3_B |

| 54      | J                 | P12_7 / SEG11 / INT1_R          |

| 55      | J                 | P01_1 / SEG21 / CKOT1           |

| 56      | J                 | P01_3 / SEG23                   |

| 57      | L                 | P03_0 / SEG36 / V0              |

| 58      | L                 | P03_1 / SEG37 / V1              |

| 59      | L                 | P03_2 / SEG38 / V2              |

| 60      | L                 | P03_3 / SEG39 / V3              |

| 61      | М                 | P03_4 / RX0 / INT4              |

| 62      | н                 | P03_5 / TX0                     |

| 63      | н                 | P03_6 / INT0 / NMI              |

| 64      | Supply            | Vcc                             |

\*: See "I/O CIRCUIT TYPE" for details on the I/O circuit types.

## 7. Memory Map

| FF:FFF <sub>H</sub><br>USER ROM*1<br>DD:FFFF <sub>H</sub>  |  |

|------------------------------------------------------------|--|

|                                                            |  |

|                                                            |  |

| 10:0000 <sub>H</sub>                                       |  |

| 0F:C000 <sub>H</sub> Boot-ROM                              |  |

| 0E:9000 <sub>H</sub> Peripheral                            |  |

| Reserved                                                   |  |

| 01:0000 <sub>H</sub>                                       |  |

| 00:8000 <sub>H</sub> ROM/RAM                               |  |

| RAMSTART0*2 Internal RAM<br>bank0                          |  |

| Reserved                                                   |  |

| 00:0C00 <sub>H</sub><br>00:0380 <sub>H</sub><br>Регipheral |  |

| 00:0180 <sub>H</sub> GPR* <sup>3</sup>                     |  |

| 00:0100 <sub>H</sub> DMA                                   |  |

| 00:00F0 <sub>H</sub> Reserved                              |  |

| 00:0000 <sub>H</sub> Peripheral                            |  |

\*1: For details about USER ROM area, see "User ROM Memory Map For Flash Devices" on the following pages.

\*2: For RAMSTART addresses, see the table on the next page.

\*3: Unused GPR banks can be used as RAM area.

GPR: General-Purpose Register

The DMA area is only available if the device contains the corresponding resource.

The available RAM and ROM area depends on the device.

# 9. User ROM Memory Map For Flash Devices

| CPU mode<br>address              | Flash memory mode address        | MB96F673<br>Flash size<br>64.5KB + 32KB | MB96F675<br>Flash size<br>128.5KB + 32KB |                   |

|----------------------------------|----------------------------------|-----------------------------------------|------------------------------------------|-------------------|

| FF:FFFFH<br>FF:0000H             | 3F:FFFFн<br>3F:0000н             | SA39 - 64KB                             | SA39 - 64KB                              | Donk A of Floob A |

| FE:FFFFH<br>FE:0000H             | 3E:FFFFн<br>3E:0000н             |                                         | SA38 - 64KB                              | Bank A of Flash A |

| DF:A000H                         |                                  | Reserved                                | Reserved                                 |                   |

| DF:9FFFH<br>DF:8000H             | 1F:9FFFн<br>1F:8000н             | SA4 - 8KB                               | SA4 - 8KB                                |                   |

| DF:7FFFH<br>DF:6000H             | 1F:7FFFн<br>1F:6000н             | SA3 - 8KB                               | SA3 - 8KB                                | Bank B of Flash / |

| DF:5FFFH<br>DF:4000H             | 1F:5FFFн<br>1F:4000н             | SA2 - 8KB                               | SA2 - 8KB                                |                   |

| DF:3FFFH<br>DF:2000H             | 1F:3FFFн<br>1F:2000н             | SA1 - 8KB                               | SA1 - 8KB                                |                   |

| DF:2000н<br>DF:1FFFн<br>DF:0000н | 1F:2000н<br>1F:1FFFн<br>1F:0000н | SAS - 512B*                             | SAS - 512B*                              | Bank A of Flash   |

|                                  |                                  | Reserved                                | Reserved                                 |                   |

Sector SAS contains the ROM configuration block RCBA at CPU address DF:0000H -DF:01FFH. SAS can not be used for  $E^2$ PROM emulation.

# **10. Serial Programming Communication Interface**

USART pins for Flash serial programming (MD = 0, DEBUG I/F = 0, Serial Communication mode)

| MB96670    |              |                 |  |  |  |  |  |

|------------|--------------|-----------------|--|--|--|--|--|

| Pin Number | USART Number | Normal Function |  |  |  |  |  |

| 29         |              | SIN0            |  |  |  |  |  |

| 30         | USART0       | SOT0            |  |  |  |  |  |

| 31         |              | SCK0            |  |  |  |  |  |

| 3          |              | SIN1            |  |  |  |  |  |

| 4          | USART1       | SOT1            |  |  |  |  |  |

| 5          |              | SCK1            |  |  |  |  |  |

# 11. Interrupt Vector Table

| Vector<br>number | Offset in vector table | Vector name | Cleared by<br>DMA | Index in<br>ICR to<br>program | Description                     |

|------------------|------------------------|-------------|-------------------|-------------------------------|---------------------------------|

| 0                | 3FC <sub>H</sub>       | CALLV0      | No                | -                             | CALLV instruction               |

| 1                | 3F8 <sub>H</sub>       | CALLV1      | No                | -                             | CALLV instruction               |

| 2                | 3F4 <sub>H</sub>       | CALLV2      | No                | -                             | CALLV instruction               |

| 3                | 3F0 <sub>H</sub>       | CALLV3      | No                | -                             | CALLV instruction               |

| 4                | 3EC <sub>H</sub>       | CALLV4      | No                | -                             | CALLV instruction               |

| 5                | 3E8 <sub>H</sub>       | CALLV5      | No                | -                             | CALLV instruction               |

| 6                | 3E4 <sub>H</sub>       | CALLV6      | No                | -                             | CALLV instruction               |

| 7                | 3E0 <sub>Н</sub>       | CALLV7      | No                | -                             | CALLV instruction               |

| 8                | 3DC <sub>H</sub>       | RESET       | No                | -                             | Reset vector                    |

| 9                | 3D8 <sub>H</sub>       | INT9        | No                | -                             | INT9 instruction                |

| 10               | 3D4 <sub>H</sub>       | EXCEPTION   | No                | -                             | Undefined instruction execution |

| 11               | 3D0 <sub>Н</sub>       | NMI         | No                | -                             | Non-Maskable Interrupt          |

| 12               | 3CC <sub>H</sub>       | DLY         | No                | 12                            | Delayed Interrupt               |

| 13               | 3C8 <sub>Н</sub>       | RC_TIMER    | No                | 13                            | RC Clock Timer                  |

| 14               | 3C4 <sub>H</sub>       | MC_TIMER    | No                | 14                            | Main Clock Timer                |

| 15               | 3C0 <sub>Н</sub>       | SC_TIMER    | No                | 15                            | Sub Clock Timer                 |

| 16               | 3BC <sub>H</sub>       | LVDI        | No                | 16                            | Low Voltage Detector            |

| 17               | 3B8 <sub>Н</sub>       | EXTINT0     | Yes               | 17                            | External Interrupt 0            |

| 18               | 3B4 <sub>H</sub>       | EXTINT1     | Yes               | 18                            | External Interrupt 1            |

| 19               | 3B0 <sub>Н</sub>       | EXTINT2     | Yes               | 19                            | External Interrupt 2            |

| 20               | 3AC <sub>H</sub>       | EXTINT3     | Yes               | 20                            | External Interrupt 3            |

| 21               | 3А8 <sub>Н</sub>       | EXTINT4     | Yes               | 21                            | External Interrupt 4            |

| 22               | 3A4 <sub>H</sub>       | -           | -                 | 22                            | Reserved                        |

| 23               | 3A0 <sub>H</sub>       | EXTINT6     | Yes               | 23                            | External Interrupt 6            |

| 24               | 39C <sub>H</sub>       | EXTINT7     | Yes               | 24                            | External Interrupt 7            |

| 25               | 398 <sub>н</sub>       | -           | -                 | 25                            | Reserved                        |

| 26               | 394 <sub>Н</sub>       | -           | -                 | 26                            | Reserved                        |

| 27               | 390 <sub>Н</sub>       | -           | -                 | 27                            | Reserved                        |

| 28               | 38C <sub>H</sub>       | -           | -                 | 28                            | Reserved                        |

| 29               | 388 <sub>H</sub>       | -           | -                 | 29                            | Reserved                        |

| 30               | 384 <sub>H</sub>       | -           | -                 | 30                            | Reserved                        |

| 31               | 380 <sub>Н</sub>       | -           | -                 | 31                            | Reserved                        |

| 32               | 37C <sub>H</sub>       | -           | -                 | 32                            | Reserved                        |

| 33               | 378 <sub>H</sub>       | CAN0        | No                | 33                            | CAN Controller 0                |

| 34               | 374 <sub>H</sub>       | -           | -                 | 34                            | Reserved                        |

| 35               | 370 <sub>H</sub>       | -           | -                 | 35                            | Reserved                        |

| 36               | 36C <sub>H</sub>       | -           | -                 | 36                            | Reserved                        |

| 37               | 368 <sub>H</sub>       | -           | -                 | 37                            | Reserved                        |

| 38               | 364 <sub>H</sub>       | PPG0        | Yes               | 38                            | Programmable Pulse Generator 0  |

| 39               | 360н                   | PPG1        | Yes               | 39                            | Programmable Pulse Generator 1  |

| Vector<br>number | Offset in vector table | Vector name | Cleared by<br>DMA | Index in<br>ICR to<br>program | Description                  |

|------------------|------------------------|-------------|-------------------|-------------------------------|------------------------------|

| 81               | 2В8 <sub>Н</sub>       | -           | -                 | 81                            | Reserved                     |

| 82               | 2B4 <sub>H</sub>       | -           | -                 | 82                            | Reserved                     |

| 83               | 2B0 <sub>Н</sub>       | -           | -                 | 83                            | Reserved                     |

| 84               | 2AC <sub>H</sub>       | -           | -                 | 84                            | Reserved                     |

| 85               | 2А8 <sub>Н</sub>       | -           | -                 | 85                            | Reserved                     |

| 86               | 2A4 <sub>H</sub>       | -           | -                 | 86                            | Reserved                     |

| 87               | 2A0 <sub>H</sub>       | -           | -                 | 87                            | Reserved                     |

| 88               | 29C <sub>H</sub>       | -           | -                 | 88                            | Reserved                     |

| 89               | 298 <sub>H</sub>       | FRT0        | Yes               | 89                            | Free-Running Timer 0         |

| 90               | 294 <sub>H</sub>       | FRT1        | Yes               | 90                            | Free-Running Timer 1         |

| 91               | 290 <sub>H</sub>       | -           | -                 | 91                            | Reserved                     |

| 92               | 28C <sub>H</sub>       | -           | -                 | 92                            | Reserved                     |

| 93               | 288 <sub>H</sub>       | RTC0        | No                | 93                            | Real Time Clock              |

| 94               | 284 <sub>H</sub>       | CAL0        | No                | 94                            | Clock Calibration Unit       |

| 95               | 280 <sub>H</sub>       | SG0         | No                | 95                            | Sound Generator 0            |

| 96               | 27C <sub>H</sub>       | IIC0        | Yes               | 96                            | I <sup>2</sup> C interface 0 |

| 97               | 278 <sub>H</sub>       | -           | -                 | 97                            | Reserved                     |

| 98               | 274 <sub>H</sub>       | ADC0        | Yes               | 98                            | A/D Converter 0              |

| 99               | 270 <sub>H</sub>       | -           | -                 | 99                            | Reserved                     |

| 100              | 26C <sub>H</sub>       | -           | -                 | 100                           | Reserved                     |

| 101              | 268 <sub>H</sub>       | LINR0       | Yes               | 101                           | LIN USART 0 RX               |

| 102              | 264 <sub>H</sub>       | LINT0       | Yes               | 102                           | LIN USART 0 TX               |

| 103              | 260 <sub>H</sub>       | LINR1       | Yes               | 103                           | LIN USART 1 RX               |

| 104              | 25C <sub>H</sub>       | LINT1       | Yes               | 104                           | LIN USART 1 TX               |

| 105              | 258 <sub>H</sub>       | -           | -                 | 105                           | Reserved                     |

| 106              | 254 <sub>H</sub>       | -           | -                 | 106                           | Reserved                     |

| 107              | 250 <sub>H</sub>       | -           | -                 | 107                           | Reserved                     |

| 108              | 24C <sub>H</sub>       | -           | -                 | 108                           | Reserved                     |

| 109              | 248 <sub>H</sub>       | -           | -                 | 109                           | Reserved                     |

| 110              | 244 <sub>H</sub>       | -           | -                 | 110                           | Reserved                     |

| 111              | 240 <sub>H</sub>       | -           | -                 | 111                           | Reserved                     |

| 112              | 23C <sub>H</sub>       | -           | -                 | 112                           | Reserved                     |

| 113              | 238 <sub>H</sub>       | -           | -                 | 113                           | Reserved                     |

| 114              | 234 <sub>H</sub>       | -           | -                 | 114                           | Reserved                     |

| 115              | 230 <sub>H</sub>       | -           | -                 | 115                           | Reserved                     |

| 116              | 22C <sub>H</sub>       | -           | -                 | 116                           | Reserved                     |

| 117              | 228 <sub>H</sub>       | -           | -                 | 117                           | Reserved                     |

| 118              | 224 <sub>H</sub>       | -           | -                 | 118                           | Reserved                     |

| 119              | 220 <sub>H</sub>       | -           | -                 | 119                           | Reserved                     |

| 120              | 21C <sub>H</sub>       | -           | -                 | 120                           | Reserved                     |

## **13. Handling Devices**

### Special care is required for the following when handling the device:

- Latch-up prevention

- · Unused pins handling

- · External clock usage

- · Notes on PLL clock mode operation

- Power supply pins (Vcc/Vss)

- · Crystal oscillator and ceramic resonator circuit

- Turn on sequence of power supply to A/D converter and analog inputs

- · Pin handling when not using the A/D converter

- · Notes on Power-on

- Stabilization of power supply voltage

- SMC power supply pins

- Serial communication

- Mode Pin (MD)

## 13.1 Latch-up prevention

CMOS IC chips may suffer latch-up under the following conditions:

- A voltage higher than V<sub>CC</sub> or lower than V<sub>SS</sub> is applied to an input or output pin.

- A voltage higher than the rated voltage is applied between Vcc pins and Vss pins.

- The AV<sub>CC</sub> power supply is applied before the  $V_{CC}$  voltage.

Latch-up may increase the power supply current dramatically, causing thermal damages to the device.

For the same reason, extra care is required to not let the analog power-supply voltage (AV<sub>CC</sub>, AVRH) exceed the digital power-supply voltage.

## 13.2 Unused pins handling

Unused input pins can be left open when the input is disabled (corresponding bit of Port Input Enable register PIER = 0).

Leaving unused input pins open when the input is enabled may result in misbehavior and possible permanent

damage of the device. To prevent latch-up, they must therefore be pulled up or pulled down through resistors which should be more than  $2k\Omega$ .

Unused bidirectional pins can be set either to the output state and be then left open, or to the input state with

either input disabled or external pull-up/pull-down resistor as described above.

### 13.6 Crystal oscillator and ceramic resonator circuit

Noise at X0, X1 pins or X0A, X1A pins might cause abnormal operation. It is required to provide bypass capacitors with shortest possible distance to X0, X1 pins and X0A, X1A pins, crystal oscillator (or ceramic resonator) and ground lines, and, to the utmost effort, that the lines of oscillation circuit do not cross the lines of other circuits.

It is highly recommended to provide a printed circuit board art work surrounding X0, X1 pins and X0A, X1A pins with a ground area for stabilizing the operation.

It is highly recommended to evaluate the quartz/MCU or resonator/MCU system at the quartz or resonator manufacturer, especially when using low-Q resonators at higher frequencies.

#### 13.7 Turn on sequence of power supply to A/D converter and analog inputs

It is required to turn the A/D converter power supply (AV<sub>CC</sub>, AVRH) and analog inputs (ANn) on after turning the digital power supply (V<sub>CC</sub>) on.

It is also required to turn the digital power off after turning the A/D converter supply and analog inputs off. In this case, AVRH must not exceed  $AV_{CC}$ . Input voltage for ports shared with analog input ports also must not exceed  $AV_{CC}$  (turning the analog and digital power supplies simultaneously on or off is acceptable).

#### 13.8 Pin handling when not using the A/D converter

If the A/D converter is not used, the power supply pins for A/D converter should be connected such as  $AV_{CC} = V_{CC}$ ,  $AV_{SS} = AVRH = V_{SS}$ .

#### 13.9 Notes on Power-on

To prevent malfunction of the internal voltage regulator, supply voltage profile while turning the power supply on should be slower than  $50\mu s$  from 0.2V to 2.7V.

#### 13.10Stabilization of power supply voltage

If the power supply voltage varies acutely even within the operation safety range of the V<sub>CC</sub> power supply voltage, a malfunction may occur. The V<sub>CC</sub> power supply voltage must therefore be stabilized. As stabilization guidelines, the power supply voltage must be stabilized in such a way that V<sub>CC</sub> ripple fluctuations (peak to peak value) in the commercial frequencies (50Hz to 60Hz) fall within 10% of the standard V<sub>CC</sub> power supply voltage and the transient fluctuation rate becomes  $0.1V/\mu s$  or less in instantaneous fluctuation for power supply switching.

#### 13.11SMC power supply pins

All DVcc /DVss pins must be set to the same level as the Vcc /Vss pins.

Note that the SMC I/O pin state is undefined if  $DV_{CC}$  is powered on and  $V_{CC}$  is below 3V. To avoid this,  $V_{CC}$  must always be powered on before  $DV_{CC}$ .

DVcc/DVss must be applied when using SMC I/O pin as GPIO.

#### **13.12Serial communication**

There is a possibility to receive wrong data due to noise or other causes on the serial communication.

Therefore, design a printed circuit board so as to avoid noise.

Consider receiving of wrong data when designing the system. For example apply a checksum and retransmit the data if an error occurs.

#### 13.13Mode Pin (MD)

Connect the mode pin directly to Vcc or Vss pin. To prevent the device unintentionally entering test mode due to noise, lay out the printed circuit board so as to minimize the distance from the mode pin to Vcc or Vss pin and provide a low-impedance connection.

- <sup>\*1</sup>: This parameter is based on  $V_{SS} = AV_{SS} = DV_{SS} = 0V$ .

- <sup>\*2</sup>: AV<sub>CC</sub> and V<sub>CC</sub> and DV<sub>CC</sub> must be set to the same voltage. It is required that AV<sub>CC</sub> does not exceed V<sub>CC</sub>, DV<sub>CC</sub> and that the voltage at the analog inputs does not exceed AV<sub>CC</sub> when the power is switched on.

- \*<sup>3</sup>: V<sub>I</sub> and V<sub>O</sub> should not exceed V<sub>CC</sub> + 0.3V. V<sub>I</sub> should also not exceed the specified ratings. However if the maximum current to/from an input is limited by some means with external components, the I<sub>CLAMP</sub> rating supersedes the V<sub>I</sub> rating. Input/Output voltages of high current ports depend on DV<sub>CC</sub>. Input/Output voltages of standard ports depend on V<sub>CC</sub>.

- <sup>\*4</sup>: Applicable to all general purpose I/O pins (Pnn\_m).

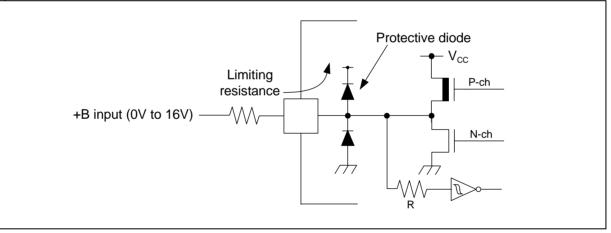

- · Use within recommended operating conditions.

- Use at DC voltage (current).

- The +B signal should always be applied a limiting resistance placed between the +B signal and the microcontroller.

- The value of the limiting resistance should be set so that when the +B signal is applied the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the V<sub>CC</sub> pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller power supply is off (not fixed at 0V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power supply is provided from the pins and the resulting supply voltage may not be sufficient to operate the Power reset.

- The DEBUG I/F pin has only a protective diode against V<sub>SS</sub>. Hence it is only permitted to input a negative clamping current (4mA). For protection against positive input voltages, use an external clamping diode which limits the input voltage to maximum 6.0V.

- · Sample recommended circuits:

<sup>\*5</sup>: The maximum permitted power dissipation depends on the ambient temperature, the air flow velocity and the thermal conductance of the package on the PCB.

The actual power dissipation depends on the customer application and can be calculated as follows:  $P_D = P_{IO} + P_{INT}$

$P_{IO}$  =  $\Sigma$  (V<sub>OL</sub> × I<sub>OL</sub> + V<sub>OH</sub> × I<sub>OH</sub>) (I/O load power dissipation, sum is performed on all I/O ports)

$P_{INT} = V_{CC} \times (I_{CC} + I_A)$  (internal power dissipation)

$I_{CC}$  is the total core current consumption into  $V_{CC}$  as described in the "DC characteristics" and depends on the selected operation mode and clock frequency and the usage of functions like Flash programming.

$I_A$  is the analog current consumption into AV<sub>CC</sub>.

<sup>\*6</sup>: Worst case value for a package mounted on single layer PCB at specified T<sub>A</sub> without air flow.

### WARNING

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

| Parameter                                               | Symbol              | Pin  | Conditions                                                                                   | Value |      |      | Unit | Remarks                 |

|---------------------------------------------------------|---------------------|------|----------------------------------------------------------------------------------------------|-------|------|------|------|-------------------------|

| Farameter                                               | Symbol              | name | Conditions                                                                                   | Min   | Тур  | Max  | Unit | Reillaiks               |

| Power supply<br>current in Sleep<br>modes <sup>*1</sup> | ICCSPLL             |      | PLL Sleep mode with<br>CLKS1/2 = CLKP1/2 =<br>32MHz                                          |       | 6.5  | -    | mA   | T <sub>A</sub> = +25°C  |

|                                                         |                     |      | (CLKRC and CLKSC stopped)                                                                    | -     | -    | 13   | mA   | T <sub>A</sub> = +105°C |

|                                                         | Iccsmain            |      | Main Sleep mode with<br>CLKS1/2 = CLKP1/2 =<br>4MHz,<br>SMCR:LPMSS = 0                       | -     | 0.9  | -    | mA   | T <sub>A</sub> = +25°C  |

|                                                         |                     |      | (CLKPLL, CLKRC and<br>CLKSC stopped)                                                         | -     | -    | 4    | mA   | T <sub>A</sub> = +105°C |

|                                                         | Іссягсн             |      | RC Sleep mode with<br>CLKS1/2 = CLKP1/2 =<br>CLKRC = 2MHz,<br>SMCR:LPMSS = 0                 | -     | 0.5  | -    | mA   | T <sub>A</sub> = +25°C  |

|                                                         |                     |      | (CLKMC, CLKPLL and<br>CLKSC stopped)                                                         | -     | -    | 3.5  | mA   | T <sub>A</sub> = +105°C |

|                                                         |                     |      | RC Sleep mode with<br>CLKS1/2 = CLKP1/2 =<br>CLKRC = 100kHz                                  | -     | 0.06 | -    | mA   | T <sub>A</sub> = +25°C  |

|                                                         |                     |      | (CLKMC, CLKPLL and<br>CLKSC stopped)                                                         | -     | -    | 2.7  | mA   | T <sub>A</sub> = +105°C |

|                                                         | I <sub>CCSSUB</sub> | Vcc  | Sub Sleep mode with<br>CLKS1/2 = CLKP1/2 =<br>32kHz,<br>(CLKMC, CLKPLL and<br>CLKRC stopped) | -     | 0.04 | -    | mA   | T <sub>A</sub> = +25°C  |

|                                                         |                     |      |                                                                                              | -     | -    | 2.5  | mA   | T <sub>A</sub> = +105°C |

|                                                         | I <sub>CCTPLL</sub> |      | PLL Timer mode with<br>CLKPLL = 32MHz (CLKRC<br>and CLKSC stopped)                           | -     | 1800 | 2245 | μA   | T <sub>A</sub> = +25°C  |

|                                                         |                     |      |                                                                                              | -     | -    | 3140 | μA   | T <sub>A</sub> = +105°C |

|                                                         |                     | -    | Main Timer mode with<br>CLKMC = 4MHz,<br>SMCR:LPMSS = 0                                      | -     | 285  | 325  | μΑ   | T <sub>A</sub> = +25°C  |

|                                                         |                     |      | (CLKPLL, CLKRC and<br>CLKSC stopped)                                                         | -     | -    | 1055 | μA   | T <sub>A</sub> = +105°C |

| Power supply current in                                 | I <sub>CCTRCH</sub> |      | RC Timer mode with<br>CLKRC = 2MHz,<br>SMCR:LPMSS = 0                                        | -     | 160  | 210  | μΑ   | T <sub>A</sub> = +25°C  |

| Timer modes <sup>*2</sup>                               |                     |      | (CLKPLL, CLKMC and<br>CLKSC stopped)                                                         | -     | -    | 970  | μA   | T <sub>A</sub> = +105°C |

|                                                         | ICCTRCL             |      | RC Timer mode with<br>CLKRC = 100kHz                                                         | -     | 30   | 70   | μA   | T <sub>A</sub> = +25°C  |

|                                                         |                     |      | (CLKPLL, CLKMC and<br>CLKSC stopped)                                                         | -     | -    | 820  | μA   | T <sub>A</sub> = +105°C |

|                                                         | I <sub>CCTSUB</sub> |      | Sub Timer mode with<br>CLKSC = 32kHz                                                         | -     | 25   | 55   | μΑ   | T <sub>A</sub> = +25°C  |

|                                                         |                     |      | (CLKMC, CLKPLL and<br>CLKRC stopped)                                                         | -     | -    | 800  | μΑ   | T <sub>A</sub> = +105°C |

### 14.4.8 USART Timing

| Devenuetor                                  | Symbo               | Pin                 | Conditions                   | 4.5V ≤ V <sub>0</sub>         | <sub>cc</sub> < 5.5V        | 2.7V ≤ V <sub>0</sub>         | Uni                         |    |

|---------------------------------------------|---------------------|---------------------|------------------------------|-------------------------------|-----------------------------|-------------------------------|-----------------------------|----|

| Parameter                                   | 1                   | name Conditions Min |                              | Max                           | Min                         | Max                           | t                           |    |

| Serial clock cycle time                     | t <sub>SCYC</sub>   | SCKn                |                              | 4t <sub>CLKP1</sub>           | -                           | 4t <sub>CLKP1</sub>           | -                           | ns |

| SCK $\downarrow \rightarrow$ SOT delay time | t <sub>SLOVI</sub>  | SCKn<br>,<br>SOTn   |                              | - 20                          | + 20                        | - 30                          | + 30                        | ns |

| $SOT \to SCK \uparrow delay \text{ time}$   | t <sub>ovsн</sub> ı | SCKn<br>,<br>SOTn   | Internal shift<br>clock mode | N×t <sub>CLKP1</sub><br>– 20  | -                           | N×t <sub>CLKP1</sub><br>– 30  | -                           | ns |

| $SIN \to SCK \uparrow setup  time$          | t <sub>i∨SHI</sub>  | SCKn<br>,<br>SINn   |                              | t <sub>CLKP1</sub><br>+ 45    | -                           | t <sub>CLKP1</sub><br>+ 55    | -                           | ns |

| SCK $\uparrow \rightarrow$ SIN hold time    | t <sub>SHIXI</sub>  | SCKn<br>,<br>SINn   |                              | 0                             | -                           | 0                             | -                           | ns |

| Serial clock "L" pulse width                | t <sub>SLSH</sub>   | SCKn                |                              | t <sub>CLKP1</sub><br>+ 10    | -                           | t <sub>CLKP1</sub><br>+ 10    | -                           | ns |

| Serial clock "H" pulse width                | t <sub>SHSL</sub>   | SCKn                |                              | t <sub>CLKP1</sub><br>+ 10    | -                           | t <sub>CLKP1</sub><br>+ 10    | -                           | ns |

| SCK $\downarrow \rightarrow$ SOT delay time | t <sub>SLOVE</sub>  | SCKn<br>,<br>SOTn   | External                     | -                             | 2t <sub>CLKP1</sub><br>+ 45 | -                             | 2t <sub>CLKP1</sub><br>+ 55 | ns |

| $SIN \to SCK \uparrow setup  time$          | t <sub>IVSHE</sub>  | SCKn<br>,<br>SINn   | shift<br>clock mode          | t <sub>CLKP1</sub> /2<br>+ 10 | -                           | t <sub>CLKP1</sub> /2<br>+ 10 | -                           | ns |

| SCK $\uparrow \rightarrow$ SIN hold time    | t <sub>SHIXE</sub>  | SCKn<br>,<br>SINn   |                              | t <sub>CLKP1</sub><br>+ 10    | -                           | t <sub>CLKP1</sub><br>+ 10    | -                           | ns |

| SCK fall time                               | t⊨                  | SCKn                | ļ                            | -                             | 20                          | -                             | 20                          | ns |

| SCK rise time                               | t <sub>R</sub>      | SCKn                |                              | -                             | 20                          | -                             | 20                          | ns |

$(V_{CC} = AV_{CC} = DV_{CC} = 2.7V$  to 5.5V,  $V_{SS} = AV_{SS} = DV_{SS} = 0V$ ,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ ,  $C_L=50pF$ )

### Notes:

- AC characteristic in CLK synchronized mode.

- C<sub>L</sub> is the load capacity value of pins when testing.

- Depending on the used machine clock frequency, the maximum possible baud rate can be limited by some parameters. These parameters are shown in "MB96600 series HARDWARE MANUAL".

- t<sub>CLKP1</sub> indicates the peripheral clock 1 (CLKP1), Unit: ns

- These characteristics only guarantee the same relocate port number.

For example, the combination of SCKn and SOTn\_R is not guaranteed.

\*: Parameter N depends on  $t_{\mbox{\scriptsize SCYC}}$  and can be calculated as follows:

• If  $t_{SCYC} = 2 \times k \times t_{CLKP1}$ , then N = k, where k is an integer > 2

• If  $t_{SCYC} = (2 \times k + 1) \times t_{CLKP1}$ , then N = k + 1, where k is an integer > 1

Examples:

| tscyc                                    | Ν |

|------------------------------------------|---|

| $4 	imes t_{CLKP1}$                      | 2 |

| $5 \times t_{CLKP1}, 6 \times t_{CLKP1}$ | 3 |

| $7 \times t_{CLKP1}, 8 \times t_{CLKP1}$ | 4 |

|                                          |   |

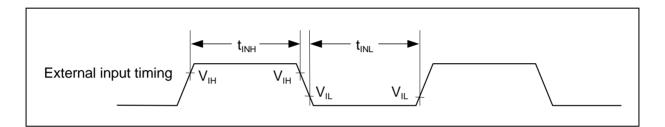

## 14.4.9 External Input Timing

|                   | out mining                                   | $(V_{CC} = AV_{CC})$ | $= DV_{CC} = 2.7V$ to 5.8 | 5V, V <sub>SS</sub> = AV | / <sub>SS</sub> = DV <sub>S</sub> | <sub>S</sub> = 0V, T <sub>A</sub> = - 40°C to + 105°C |

|-------------------|----------------------------------------------|----------------------|---------------------------|--------------------------|-----------------------------------|-------------------------------------------------------|

| Parameter         | Symbol                                       | Pin name             | Value                     | 9                        | Unit                              | Remarks                                               |

| Faranielei        | Symbol                                       | Finitianie           | Min                       | Max                      | Unit                              | Reillarks                                             |

|                   |                                              | Pnn_m                |                           |                          |                                   | General Purpose I/O                                   |

|                   | vidth t <sub>INH</sub> ,<br>t <sub>INL</sub> | ADTG                 | 2t <sub>CLKP1</sub> +200  |                          |                                   | A/D Converter trigger input                           |

|                   |                                              | TINn, TINn_R         | (t <sub>CLKP1</sub> =     | -                        | ns                                | Reload Timer                                          |

| Input pulse width |                                              | TTGn                 | 1/f <sub>CLKP1</sub> )*   | /t <sub>CLKP1</sub> )*   |                                   | PPG trigger input                                     |

|                   |                                              | INn, INn_R           |                           |                          |                                   | Input Capture                                         |

|                   |                                              | INTn, INTn_R         | 200                       |                          | ns                                | External Interrupt                                    |

|                   |                                              | NMI                  | 200                       | -                        |                                   | Non-Maskable Interrupt                                |

\*: t<sub>CLKP1</sub> indicates the peripheral clock1 (CLKP1) cycle time except stop when in stop mode.

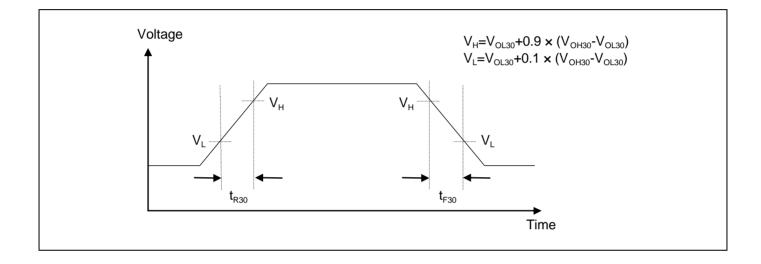

## 14.6 High Current Output Slew Rate

|                          |                                        |             | (100 11                                         |       |     | ,   | 00   | 00 - , , ,           |

|--------------------------|----------------------------------------|-------------|-------------------------------------------------|-------|-----|-----|------|----------------------|

| Parameter                | Symbol                                 | Pin<br>name | Conditions                                      | Value |     |     | Unit | Remarks              |

| Farameter                |                                        |             |                                                 | Min   | Тур | Max | Unit | Rellidiks            |

| Output rise/fall<br>time | t <sub>R30</sub> ,<br>t <sub>F30</sub> | P08_m       | Outputs<br>driving<br>strength set<br>to "30mA" | 15    | -   | 75  | ns   | C <sub>L</sub> =85pF |

$(V_{CC} = AV_{CC} = DV_{CC} = 2.7V$  to 5.5V,  $V_{SS} = AV_{SS} = DV_{SS} = 0V$ ,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ )

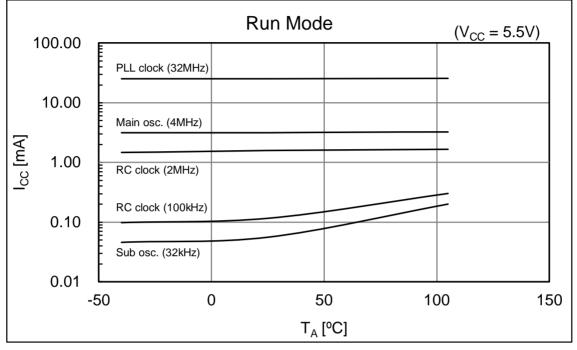

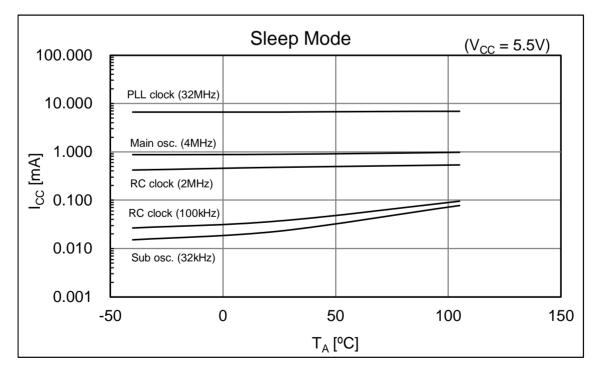

## **15. Example Characteristics**

This characteristic is an actual value of the arbitrary sample. It is not the guaranteed value.

## ■MB96F675

## ■Used setting

| Mode       | Selected Source<br>Clock | Clock/Regulator and FLASH Settings                                                                                                            |  |  |  |

|------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Run mode   | PLL                      | CLKS1 = CLKS2 = CLKB = CLKP1 = CLKP2 = 32MHz                                                                                                  |  |  |  |

|            | Main osc.                | CLKS1 = CLKS2 = CLKB = CLKP1 = CLKP2 = 4MHz                                                                                                   |  |  |  |

|            | RC clock fast            | CLKS1 = CLKS2 = CLKB = CLKP1 = CLKP2 = 2MHz                                                                                                   |  |  |  |

|            | RC clock slow            | CLKS1 = CLKS2 = CLKB = CLKP1 = CLKP2 = 100kHz                                                                                                 |  |  |  |

|            | Sub osc.                 | CLKS1 = CLKS2 = CLKB = CLKP1 = CLKP2 = 32kHz                                                                                                  |  |  |  |

| Sleep mode | PLL                      | CLKS1 = CLKS2 = CLKP1 = CLKP2 = 32MHz<br>Regulator in High Power Mode,<br>(CLKB is stopped in this mode)                                      |  |  |  |

|            | Main osc.                | CLKS1 = CLKS2 = CLKP1 = CLKP2 = 4MHz<br>Regulator in High Power Mode,<br>(CLKB is stopped in this mode)                                       |  |  |  |

|            | RC clock fast            | CLKS1 = CLKS2 = CLKP1 = CLKP2 = 2MHz<br>Regulator in High Power Mode,<br>(CLKB is stopped in this mode)                                       |  |  |  |

|            | RC clock slow            | CLKS1 = CLKS2 = CLKP1 = CLKP2 = 100kHz<br>Regulator in Low Power Mode,<br>(CLKB is stopped in this mode)                                      |  |  |  |

|            | Sub osc.                 | CLKS1 = CLKS2 = CLKP1 = CLKP2 = 32kHz<br>Regulator in Low Power Mode,<br>(CLKB is stopped in this mode)                                       |  |  |  |

| Timer mode | PLL                      | CLKMC = 4MHz, CLKPLL = 32MHz<br>(System clocks are stopped in this mode)<br>Regulator in High Power Mode,<br>FLASH in Power-down / reset mode |  |  |  |

|            | Main osc.                | CLKMC = 4MHz<br>(System clocks are stopped in this mode)<br>Regulator in High Power Mode,<br>FLASH in Power-down / reset mode                 |  |  |  |

|            | RC clock fast            | CLKMC = 2MHz<br>(System clocks are stopped in this mode)<br>Regulator in High Power Mode,<br>FLASH in Power-down / reset mode                 |  |  |  |

|            | RC clock slow            | CLKMC = 100kHz<br>(System clocks are stopped in this mode)<br>Regulator in Low Power Mode,<br>FLASH in Power-down / reset mode                |  |  |  |

|            | Sub osc.                 | CLKMC = 32 kHz<br>(System clocks are stopped in this mode)<br>Regulator in Low Power Mode,<br>FLASH in Power-down / reset mode                |  |  |  |

| Stop mode  | stopped                  | (All clocks are stopped in this mode)<br>Regulator in Low Power Mode,<br>FLASH in Power-down / reset mode                                     |  |  |  |

# 16. Ordering Information

MCU with CAN controller

| Part number         | Flash memory | Package*                             |  |  |

|---------------------|--------------|--------------------------------------|--|--|

| MB96F673RBPMC-GSE1  |              | 64-pin plastic LQFP                  |  |  |

| MB96F673RBPMC-GSE2  | Flash A      | (FPT-64P-M23)                        |  |  |

| MB96F673RBPMC1-GSE1 | (96.5KB)     | 64-pin plastic LQFP                  |  |  |

| MB96F673RBPMC1-GSE2 |              | (FPT-64P-M24)                        |  |  |

| MB96F675RBPMC-GSE1  |              | 64-pin plastic LQFP<br>(FPT-64P-M23) |  |  |

| MB96F675RBPMC-GSE2  | Flash A      |                                      |  |  |

| MB96F675RBPMC1-GSE1 | (160.5KB)    | 64-pin plastic LQFP                  |  |  |

| MB96F675RBPMC1-GSE2 |              | (FPT-64P-M24)                        |  |  |

\*: For details about package, see "■PACKAGE DIMENSION".

MCU without CAN controller

| Part number         | Flash memory | Package*                             |  |  |

|---------------------|--------------|--------------------------------------|--|--|

| MB96F673ABPMC-GSE1  |              | 64-pin plastic LQFP<br>(FPT-64P-M23) |  |  |

| MB96F673ABPMC-GSE2  | Flash A      |                                      |  |  |

| MB96F673ABPMC1-GSE1 | (96.5KB)     | 64-pin plastic LQFP<br>(FPT-64P-M24) |  |  |

| MB96F673ABPMC1-GSE2 |              |                                      |  |  |

| MB96F675ABPMC-GSE1  |              | 64-pin plastic LQFP<br>(FPT-64P-M23) |  |  |

| MB96F675ABPMC-GSE2  | Flash A      |                                      |  |  |

| MB96F675ABPMC1-GSE1 | (160.5KB)    | 64-pin plastic LQFP                  |  |  |

| MB96F675ABPMC1-GSE2 |              | (FPT-64P-M24)                        |  |  |

\*: For details about package, see "

PACKAGE DIMENSION".

## **Document History**

## Document Title: MB96670 Series F<sup>2</sup>MC-16FX 16-Bit Microcontroller

Document Number: 002-04703

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                    |

|----------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------|

| **       | -       | TORS               | 01/31/2014         | Migrated to Cypress and assigned document number 002-04703.<br>No change to document contents or format. |

| *A       | 5135634 | TORS               | 02/18/2016         | Updated to Cypress format.                                                                               |