Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| 2 014110                   |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | F <sup>2</sup> MC-16FX                                                         |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, UART/USART                              |

| Peripherals                | DMA, LCD, LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 50                                                                             |

| Program Memory Size        | 160KB (160K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                    |

| Data Converters            | A/D 12x8/10b                                                                   |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-LQFP                                                                        |

| Supplier Device Package    | 64-LQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb96f675rbpmc1-gse1 |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Built-in On Chip Debugger (OCD)

□ One-wire debug tool interface

Break function:

- Hardware break: 6 points (shared with code event)

- Software break: 4096 points

□ Event function

- Code event: 6 points (shared with hardware break)

- Data event: 6 points

- Event sequencer: 2 levels + reset

- Execution time measurement function

- □ Trace function: 42 branches

- □ Security function

- Flash Memory

- □ Dual operation flash allowing reading of one Flash bank while programming or erasing the other bank

- Command sequencer for automatic execution of programming algorithm and for supporting DMA for programming of the Flash Memory

- □ Supports automatic programming, Embedded Algorithm

- UVrite/Erase/Erase-Suspend/Resume commands

- □ A flag indicating completion of the automatic algorithm

- □ Erase can be performed on each sector individually □ Sector protection

- □ Flash Security feature to protect the content of the Flash

- □ Low voltage detection during Flash erase or write

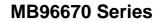

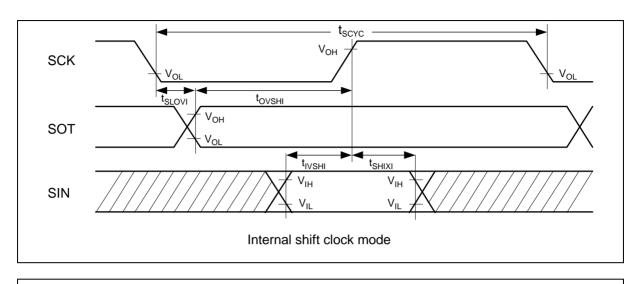

| 14.4.8 USART Timing                                            |

|----------------------------------------------------------------|

| 14.4.9 External Input Timing                                   |

| 14.4.10 I <sup>2</sup> C Timing                                |

| 14.5 A/D Converter                                             |

| 14.5.1 Electrical Characteristics for the A/D Converter        |

| 14.5.2 Accuracy and Setting of the A/D Converter Sampling Time |

| 14.5.3 Definition of A/D Converter Terms                       |

| 14.6 High Current Output Slew Rate                             |

| 14.7 Low Voltage Detection Function Characteristics            |

| 14.8 Flash Memory Write/Erase Characteristics                  |

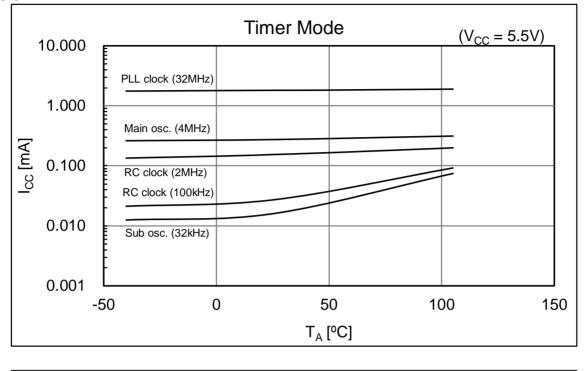

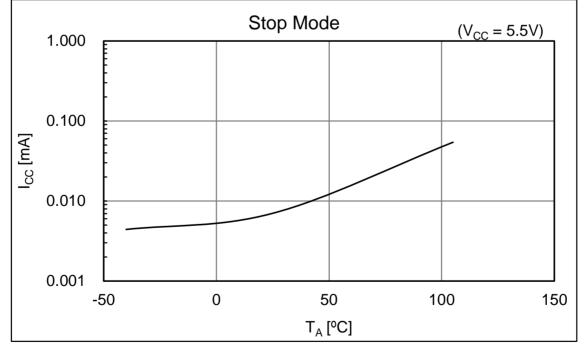

| 15. Example Characteristics                                    |

| 16. Ordering Information                                       |

| 17. Package Dimension                                          |

| 18. Major Changes                                              |

| Document History                                               |

| Pin name | Feature | Description                          |  |

|----------|---------|--------------------------------------|--|

| Vn       | LCD     | LCD voltage reference pin            |  |

| Vcc      | Supply  | Power supply pin                     |  |

| Vss      | Supply  | Power supply pin                     |  |

| WOT_R    | RTC     | Relocated Real Time clock output pin |  |

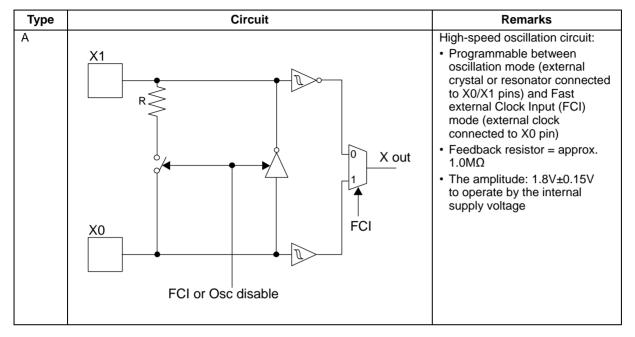

| X0       | Clock   | Oscillator input pin                 |  |

| X0A      | Clock   | Subclock Oscillator input pin        |  |

| X1       | Clock   | Oscillator output pin                |  |

| X1A      | Clock   | Subclock Oscillator output pin       |  |

# 6. I/O Circuit Type

| Туре | Circuit                                                                                                                                | Remarks                                                                                                                                                                                                              |

|------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

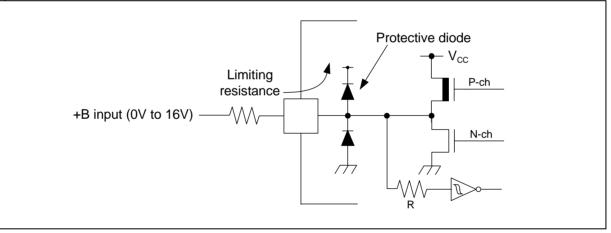

| F    | P-ch<br>N-ch                                                                                                                           | Power supply input protection circuit                                                                                                                                                                                |

| G    | P-ch<br>N-ch                                                                                                                           | <ul> <li>A/D converter ref+ (AVRH)<br/>power supply input pin with<br/>protection circuit</li> <li>Without protection circuit<br/>against V<sub>CC</sub> for pins AVRH</li> </ul>                                    |

| H    | P-ch P-ch Pout<br>P-ch Pout<br>P-ch Nout<br>Standby control                                                                            | <ul> <li>CMOS level output<br/>(I<sub>OL</sub> = 4mA, I<sub>OH</sub> = -4mA)</li> <li>Automotive input with input<br/>shutdown function</li> <li>Programmable pull-up resistor</li> </ul>                            |

| J    | Pull-up control<br>P-ch<br>P-ch<br>P-ch<br>P-ch<br>P-ch<br>Pout<br>Nout<br>Automotive input<br>for input shutdown<br>SEG or COM output | <ul> <li>CMOS level output<br/>(I<sub>OL</sub> = 4mA, I<sub>OH</sub> = -4mA)</li> <li>Automotive input with input<br/>shutdown function</li> <li>Programmable pull-up resistor</li> <li>SEG or COM output</li> </ul> |

| Туре | Circuit                                | Remarks                                                                                                                                                                                                        |

|------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| К    | Pull-up control                        | <ul> <li>CMOS level output         <ul> <li>(I<sub>OL</sub> = 4mA, I<sub>OH</sub> = -4mA)</li> </ul> </li> <li>Automotive input with input shutdown function</li> <li>Programmable pull-up resistor</li> </ul> |

|      | P-ch P-ch P-ch Pout                    | Analog input                                                                                                                                                                                                   |

|      | Standby control                        |                                                                                                                                                                                                                |

|      | Analog input                           |                                                                                                                                                                                                                |

| L    | Pull-up control                        | <ul> <li>CMOS level output         <ul> <li>(I<sub>OL</sub> = 4mA, I<sub>OH</sub> = -4mA)</li> </ul> </li> <li>Automotive input with input shutdown function</li> </ul>                                        |

|      | P-ch P-ch Pout                         | <ul> <li>Programmable pull-up resistor</li> <li>Vn input or SEG output</li> </ul>                                                                                                                              |

|      | Standby control                        |                                                                                                                                                                                                                |

|      | ······································ |                                                                                                                                                                                                                |

| M    | Pull-up control                        | <ul> <li>CMOS level output<br/>(I<sub>OL</sub> = 4mA, I<sub>OH</sub> = -4mA)</li> <li>CMOS hysteresis input with<br/>input shutdown function</li> <li>Programmable pull-up resistor</li> </ul>                 |

|      | P-ch P-ch Pout                         |                                                                                                                                                                                                                |

|      | Standby control<br>for input shutdown  |                                                                                                                                                                                                                |

| Vector<br>number | Offset in vector table | Vector name | Cleared by<br>DMA | Index in<br>ICR to<br>program | Description                    |

|------------------|------------------------|-------------|-------------------|-------------------------------|--------------------------------|

| 40               | 35C <sub>Н</sub>       | PPG2        | Yes               | 40                            | Programmable Pulse Generator 2 |

| 41               | 358 <sub>н</sub>       | PPG3        | Yes               | 41                            | Programmable Pulse Generator 3 |

| 42               | 354 <sub>Н</sub>       | -           | -                 | 42                            | Reserved                       |

| 43               | 350 <sub>Н</sub>       | -           | -                 | 43                            | Reserved                       |

| 44               | 34C <sub>H</sub>       | -           | -                 | 44                            | Reserved                       |

| 45               | 348 <sub>H</sub>       | -           | -                 | 45                            | Reserved                       |

| 46               | 344 <sub>H</sub>       | -           | -                 | 46                            | Reserved                       |

| 47               | 340 <sub>н</sub>       | -           | -                 | 47                            | Reserved                       |

| 48               | 33C <sub>H</sub>       | -           | -                 | 48                            | Reserved                       |

| 49               | 338 <sub>Н</sub>       | -           | -                 | 49                            | Reserved                       |

| 50               | 334 <sub>н</sub>       | -           | -                 | 50                            | Reserved                       |

| 51               | 330 <sub>н</sub>       | -           | -                 | 51                            | Reserved                       |

| 52               | 32C <sub>H</sub>       | -           | -                 | 52                            | Reserved                       |

| 53               | 328 <sub>H</sub>       | -           | -                 | 53                            | Reserved                       |

| 54               | 324 <sub>H</sub>       | -           | -                 | 54                            | Reserved                       |

| 55               | 320 <sub>H</sub>       | -           | -                 | 55                            | Reserved                       |

| 56               | 31C <sub>H</sub>       | -           | -                 | 56                            | Reserved                       |

| 57               | 318 <sub>Н</sub>       | -           | -                 | 57                            | Reserved                       |

| 58               | 314 <sub>H</sub>       | -           | -                 | 58                            | Reserved                       |

| 59               | 310 <sub>Н</sub>       | RLT1        | Yes               | 59                            | Reload Timer 1                 |

| 60               | 30C <sub>H</sub>       | RLT2        | Yes               | 60                            | Reload Timer 2                 |

| 61               | 308 <sub>Н</sub>       | -           | -                 | 61                            | Reserved                       |

| 62               | 304 <sub>н</sub>       | -           | -                 | 62                            | Reserved                       |

| 63               | 300 <sub>Н</sub>       | -           | -                 | 63                            | Reserved                       |

| 64               | 2FC <sub>H</sub>       | RLT6        | Yes               | 64                            | Reload Timer 6                 |

| 65               | 2F8 <sub>H</sub>       | ICU0        | Yes               | 65                            | Input Capture Unit 0           |

| 66               | 2F4 <sub>H</sub>       | ICU1        | Yes               | 66                            | Input Capture Unit 1           |

| 67               | 2F0 <sub>H</sub>       | -           | -                 | 67                            | Reserved                       |

| 68               | 2EC <sub>H</sub>       | -           | -                 | 68                            | Reserved                       |

| 69               | 2E8 <sub>H</sub>       | ICU4        | Yes               | 69                            | Input Capture Unit 4           |

| 70               | 2E4 <sub>H</sub>       | ICU5        | Yes               | 70                            | Input Capture Unit 5           |

| 71               | 2E0 <sub>H</sub>       | -           | -                 | 71                            | Reserved                       |

| 72               | 2DC <sub>H</sub>       | -           | -                 | 72                            | Reserved                       |

| 73               | 2D8 <sub>H</sub>       | -           | -                 | 73                            | Reserved                       |

| 74               | 2D4 <sub>H</sub>       | -           | -                 | 74                            | Reserved                       |

| 75               | 2D0 <sub>H</sub>       | -           | -                 | 75                            | Reserved                       |

| 76               | 2CC <sub>H</sub>       | -           | -                 | 76                            | Reserved                       |

| 77               | 2C8 <sub>H</sub>       | -           | -                 | 77                            | Reserved                       |

| 78               | 2C4 <sub>H</sub>       | -           | -                 | 78                            | Reserved                       |

| 79               | 2C0 <sub>H</sub>       | -           | -                 | 79                            | Reserved                       |

| 80               | 2BC <sub>H</sub>       | -           | -                 | 80                            | Reserved                       |

# **12. Handling Precautions**

Any semiconductor devices have inherently a certain rate of failure. The possibility of failure is greatly affected by the conditions in which they are used (circuit conditions, environmental conditions, etc.). This page describes precautions that must be observed to minimize the chance of failure and to obtain higher reliability from your Cypress semiconductor devices.

### **12.1 Precautions for Product Design**

This section describes precautions when designing electronic equipment using semiconductor devices.

## Absolute Maximum Ratings

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of certain established limits, called absolute maximum ratings. Do not exceed these ratings.

#### Recommended Operating Conditions

Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their sales representative beforehand.

### Processing and Protection of Pins

These precautions must be followed when handling the pins which connect semiconductor devices to power supply and input/output functions.

1. Preventing Over-Voltage and Over-Current Conditions

Exposure to voltage or current levels in excess of maximum ratings at any pin is likely to cause deterioration within the device, and in extreme cases leads to permanent damage of the device. Try to prevent such overvoltage or over-current conditions at the design stage.

2. Protection of Output Pins

Shorting of output pins to supply pins or other output pins, or connection to large capacitance can cause large current flows. Such conditions if present for extended periods of time can damage the device. Therefore, avoid this type of connection.

3. Handling of Unused Input Pins

Unconnected input pins with very high impedance levels can adversely affect stability of operation. Such pins should be connected through an appropriate resistance to a power supply pin or ground pin.

#### ■Latch-up

Semiconductor devices are constructed by the formation of P-type and N-type areas on a substrate. When subjected to abnormally high voltages, internal parasitic PNPN junctions (called thyristor structures) may be formed, causing large current levels in excess of several hundred mA to flow continuously at the power supply pin. This condition is called latch-up.

CAUTION: The occurrence of latch-up not only causes loss of reliability in the semiconductor device, but can cause injury or damage from high heat, smoke or flame. To prevent this from happening, do the following:

- 1. Be sure that voltages applied to pins do not exceed the absolute maximum ratings. This should include attention to abnormal noise, surge levels, etc.

- 2. Be sure that abnormal current flows do not occur during the power-on sequence.

### ■Observance of Safety Regulations and Standards

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

#### ■Fail-Safe Design

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

- <sup>\*1</sup>: This parameter is based on  $V_{SS} = AV_{SS} = DV_{SS} = 0V$ .

- <sup>\*2</sup>: AV<sub>CC</sub> and V<sub>CC</sub> and DV<sub>CC</sub> must be set to the same voltage. It is required that AV<sub>CC</sub> does not exceed V<sub>CC</sub>, DV<sub>CC</sub> and that the voltage at the analog inputs does not exceed AV<sub>CC</sub> when the power is switched on.

- \*<sup>3</sup>: V<sub>I</sub> and V<sub>O</sub> should not exceed V<sub>CC</sub> + 0.3V. V<sub>I</sub> should also not exceed the specified ratings. However if the maximum current to/from an input is limited by some means with external components, the I<sub>CLAMP</sub> rating supersedes the V<sub>I</sub> rating. Input/Output voltages of high current ports depend on DV<sub>CC</sub>. Input/Output voltages of standard ports depend on V<sub>CC</sub>.

- <sup>\*4</sup>: Applicable to all general purpose I/O pins (Pnn\_m).

- · Use within recommended operating conditions.

- Use at DC voltage (current).

- The +B signal should always be applied a limiting resistance placed between the +B signal and the microcontroller.

- The value of the limiting resistance should be set so that when the +B signal is applied the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the V<sub>CC</sub> pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller power supply is off (not fixed at 0V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power supply is provided from the pins and the resulting supply voltage may not be sufficient to operate the Power reset.

- The DEBUG I/F pin has only a protective diode against V<sub>SS</sub>. Hence it is only permitted to input a negative clamping current (4mA). For protection against positive input voltages, use an external clamping diode which limits the input voltage to maximum 6.0V.

- · Sample recommended circuits:

<sup>\*5</sup>: The maximum permitted power dissipation depends on the ambient temperature, the air flow velocity and the thermal conductance of the package on the PCB.

The actual power dissipation depends on the customer application and can be calculated as follows:  $P_D = P_{IO} + P_{INT}$

$P_{IO}$  =  $\Sigma$  (V<sub>OL</sub> × I<sub>OL</sub> + V<sub>OH</sub> × I<sub>OH</sub>) (I/O load power dissipation, sum is performed on all I/O ports)

$P_{INT} = V_{CC} \times (I_{CC} + I_A)$  (internal power dissipation)

$I_{CC}$  is the total core current consumption into  $V_{CC}$  as described in the "DC characteristics" and depends on the selected operation mode and clock frequency and the usage of functions like Flash programming.

$I_A$  is the analog current consumption into AV<sub>CC</sub>.

<sup>\*6</sup>: Worst case value for a package mounted on single layer PCB at specified T<sub>A</sub> without air flow.

## WARNING

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

## 14.3 DC Characteristics

## 14.3.1 Current Rating

| <b>_</b>                    |                    | Pin  |                                                                                |     | Value | 00 - |      | ,                       |  |  |  |  |  |  |  |                                                                                  |   |      |   |    |                        |

|-----------------------------|--------------------|------|--------------------------------------------------------------------------------|-----|-------|------|------|-------------------------|--|--|--|--|--|--|--|----------------------------------------------------------------------------------|---|------|---|----|------------------------|

| Parameter                   | Symbol             | name | Conditions                                                                     | Min | Тур   | Max  | Unit | Remarks                 |  |  |  |  |  |  |  |                                                                                  |   |      |   |    |                        |

|                             |                    |      | PLL Run mode with CLKS1/2 =<br>CLKB = CLKP1/2 = 32MHz<br>Flash 0 wait          | -   | 25    | -    | mA   | T <sub>A</sub> = +25°C  |  |  |  |  |  |  |  |                                                                                  |   |      |   |    |                        |

|                             |                    |      | (CLKRC and CLKSC stopped)                                                      | -   | -     | 34   | mA   | T <sub>A</sub> = +105°C |  |  |  |  |  |  |  |                                                                                  |   |      |   |    |                        |

|                             |                    |      | Main Run mode with CLKS1/2 =<br>CLKB = CLKP1/2 = 4MHz<br>Flash 0 wait          | -   | 3.5   | -    | mA   | T <sub>A</sub> = +25°C  |  |  |  |  |  |  |  |                                                                                  |   |      |   |    |                        |

|                             |                    |      | (CLKPLL, CLKSC and CLKRC stopped)                                              | -   | -     | 7.5  | mA   | T <sub>A</sub> = +105°C |  |  |  |  |  |  |  |                                                                                  |   |      |   |    |                        |

| Power supply current in Run | I <sub>CCRCH</sub> | Vcc  | RC Run mode with CLKS1/2 =<br>CLKB = CLKP1/2 = CLKRC =<br>2MHz<br>Flash 0 wait | -   | 1.7   | -    | mA   | T <sub>A</sub> = +25°C  |  |  |  |  |  |  |  |                                                                                  |   |      |   |    |                        |

| modes <sup>*1</sup>         |                    |      | (CLKMC, CLKPLL and CLKSC stopped)                                              | -   | -     | 5.5  | mA   | T <sub>A</sub> = +105°C |  |  |  |  |  |  |  |                                                                                  |   |      |   |    |                        |

|                             | ICCRCL             |      |                                                                                |     |       |      |      |                         |  |  |  |  |  |  |  | RC Run mode with CLKS1/2 =<br>CLKB = CLKP1/2 = CLKRC =<br>100kHz<br>Flash 0 wait | - | 0.15 | - | mA | T <sub>A</sub> = +25°C |

|                             |                    |      | (CLKMC, CLKPLL and CLKSC stopped)                                              | -   | -     | 3.2  | mA   | T <sub>A</sub> = +105°C |  |  |  |  |  |  |  |                                                                                  |   |      |   |    |                        |

|                             | Іссѕив             |      | Sub Run mode with CLKS1/2 =<br>CLKB = CLKP1/2 = 32kHz<br>Flash 0 wait          | -   | 0.1   | -    | mA   | T <sub>A</sub> = +25°C  |  |  |  |  |  |  |  |                                                                                  |   |      |   |    |                        |

|                             |                    |      | (CLKMC, CLKPLL and CLKRC stopped)                                              | -   | -     | 3    | mA   | T <sub>A</sub> = +105°C |  |  |  |  |  |  |  |                                                                                  |   |      |   |    |                        |

## 14.4 AC Characteristics

## 14.4.1 Main Clock Input Characteristics

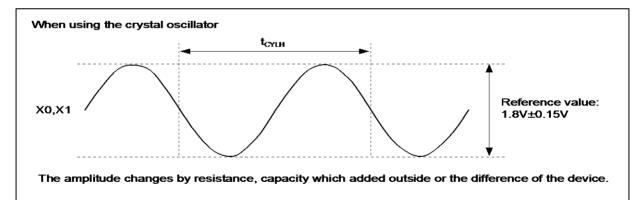

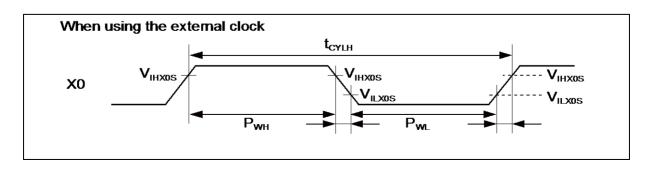

$(V_{CC} = AV_{CC} = DV_{CC} = 2.7V \text{ to } 5.5V, VD=1.8V\pm0.15V, V_{SS} = AV_{SS} = DV_{SS} = 0V, T_A = -40^{\circ}C \text{ to } + 105^{\circ}C)$

| <b>D</b>                | Ormalia Dia                          |          | Value |     |     |      | <b>D</b>                                                                              |

|-------------------------|--------------------------------------|----------|-------|-----|-----|------|---------------------------------------------------------------------------------------|

| Parameter               | Symbol                               | Pin name | Min   | Тур | Max | Unit | Remarks                                                                               |

|                         |                                      |          | 4     | -   | 8   | MHz  | When using a crystal oscillator, PLL off                                              |

| Input frequency         | fc                                   | X0,      | -     | -   | 8   | MHz  | When using an opposite<br>phase external<br>clock, PLL off                            |

|                         |                                      | X1       | 4     | -   | 8   | MHz  | When using a crystal<br>oscillator or opposite<br>phase external clock, PLL<br>on     |

| laput fraguanay         | f <sub>FCI</sub> X0                  |          | -     | -   | 8   | MHz  | When using a single phase<br>external<br>clock in "Fast Clock Input<br>mode", PLL off |

| Input frequency         |                                      | ×0       | 4     | -   | 8   | MHz  | When using a single phase<br>external<br>clock in "Fast Clock Input<br>mode", PLL on  |

| Input clock cycle       | t <sub>CYLH</sub>                    | -        | 125   | -   | -   | ns   |                                                                                       |

| Input clock pulse width | P <sub>WH</sub> ,<br>P <sub>WL</sub> | -        | 55    | -   | -   | ns   |                                                                                       |

## 14.4.3 Built-in RC Oscillation Characteristics

| $(V_{CC} = AV_{CC} = DV_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = AV_{SS} = DV_{SS} = 0V, T_A = -40^{\circ}\text{C to} + 105^{\circ}\text{C})$ |                 |     |       |     |      |                                                                        |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-------|-----|------|------------------------------------------------------------------------|--|--|--|

| Boromotor                                                                                                                                   | Symbol          |     | Value |     | Unit | Remarks                                                                |  |  |  |

| Parameter                                                                                                                                   | Symbol          | Min | Тур   | Max | Unit | Remarks                                                                |  |  |  |

| Clock frequency                                                                                                                             | f               | 50  | 100   | 200 | kHz  | When using slow frequency of RC oscillator                             |  |  |  |

|                                                                                                                                             | f <sub>RC</sub> | 1   | 2     | 4   | MHz  | When using fast frequency of RC oscillator                             |  |  |  |

| RC clock stabilization time                                                                                                                 | <b>t</b>        | 80  | 160   | 320 | μs   | When using slow frequency of RC oscillator (16 RC clock cycles)        |  |  |  |

|                                                                                                                                             | <b>t</b> RCSTAB | 64  | 128   | 256 | μs   | When using fast frequency of RC<br>oscillator<br>(256 RC clock cycles) |  |  |  |

## 14.4.4 Internal Clock Timing

| $(V_{CC} = AV_{CC} = DV_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = AV_{SS} = DV_{SS} = 0V, T_A = -40^{\circ}\text{C to} + 105^{\circ}\text{C})$ |                                         |     |      |      |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|------|------|--|--|--|--|--|--|

| Parameter                                                                                                                                   | Symbol                                  | Va  | Unit |      |  |  |  |  |  |  |

| Farameter                                                                                                                                   | Symbol                                  | Min | Max  | Unit |  |  |  |  |  |  |

| Internal System clock frequency<br>(CLKS1 and CLKS2)                                                                                        | f <sub>CLKS1</sub> , f <sub>CLKS2</sub> | -   | 54   | MHz  |  |  |  |  |  |  |

| Internal CPU clock frequency (CLKB),<br>Internal peripheral clock frequency (CLKP1)                                                         | f <sub>clkb</sub> , f <sub>clkp1</sub>  | -   | 32   | MHz  |  |  |  |  |  |  |

| Internal peripheral clock frequency (CLKP2)                                                                                                 | fclkp2                                  | -   | 32   | MHz  |  |  |  |  |  |  |

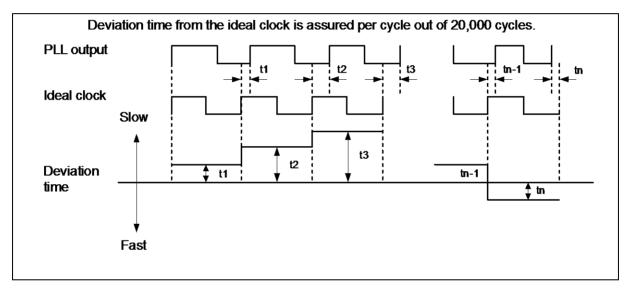

## 14.4.5 Operating Conditions of PLL

| (Vo                                     | $_{\rm CC} = AV_{\rm CC} = D$ | V <sub>CC</sub> = 2. | 7V to 5. | 5V, V <sub>SS</sub> = | AV <sub>SS</sub> = D | $V_{\rm SS} = 0$ V, $T_{\rm A} = -40^{\circ}$ C to + 105°C) |  |

|-----------------------------------------|-------------------------------|----------------------|----------|-----------------------|----------------------|-------------------------------------------------------------|--|

| Parameter                               | Symbol                        | Value                |          |                       | Unit                 | Remarks                                                     |  |

| Farameter                               | Symbol                        | Min                  | Тур      | Max                   | Onit                 | Remarks                                                     |  |

| PLL oscillation stabilization wait time | t <sub>LOCK</sub>             | 1                    | -        | 4                     | ms                   | For CLKMC = 4MHz                                            |  |

| PLL input clock frequency               | f <sub>PLLI</sub>             | 4                    | -        | 8                     | MHz                  |                                                             |  |

| PLL oscillation clock frequency         | f <sub>CLKVCO</sub>           | 56                   | -        | 108                   | MHz                  | Permitted VCO output<br>frequency of PLL (CLKVCO)           |  |

| PLL phase jitter                        | t <sub>PSKEW</sub>            | -5                   | -        | +5                    | ns                   | For CLKMC (PLL input clock)<br>≥ 4MHz                       |  |

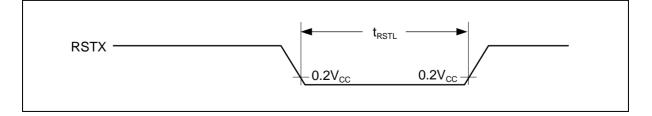

## 14.4.6 Reset Input

$(V_{CC} = AV_{CC} = DV_{CC} = 2.7V$  to 5.5V,  $V_{SS} = AV_{SS} = DV_{SS} = 0V$ ,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ )

| Parameter                     | Symbol            | Pin name   | Va  | Unit |    |  |

|-------------------------------|-------------------|------------|-----|------|----|--|

| i arameter                    | Cymbol            | T III Hame | Min | Max  |    |  |

| Reset input time              |                   | RSTX       | 10  | -    | μS |  |

| Rejection of reset input time | t <sub>RSTL</sub> | ROIN       | 1   | -    | μS |  |

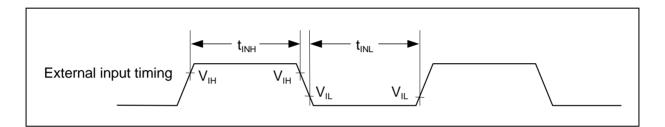

## 14.4.9 External Input Timing

| $(V_{CC} = AV_{CC} = DV_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = AV_{SS} = DV_{SS} = 0V, T_A = -40^{\circ}\text{C to } + 10^{\circ}\text{C}$ |                                        |              |                          |     |      |                            |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------|--------------------------|-----|------|----------------------------|--|

| Parameter                                                                                                                                  | Symbol                                 | Pin name     | Value                    |     | Unit | Remarks                    |  |

| Falameter                                                                                                                                  | Symbol                                 |              | Min                      | Max | Unit | Reindiks                   |  |

|                                                                                                                                            | t <sub>INH</sub> ,<br>t <sub>INL</sub> | Pnn_m        |                          |     | ns   | General Purpose I/O        |  |

| Input pulse width                                                                                                                          |                                        | ADTG         | 2t <sub>CLKP1</sub> +200 | -   |      | A/D Converter trigger inpu |  |

|                                                                                                                                            |                                        | TINn, TINn_R | (t <sub>CLKP1</sub> =    |     |      | Reload Timer               |  |

|                                                                                                                                            |                                        | TTGn         | 1/f <sub>CLKP1</sub> )*  |     |      | PPG trigger input          |  |

|                                                                                                                                            |                                        | INn, INn_R   |                          |     |      | Input Capture              |  |

|                                                                                                                                            |                                        | INTn, INTn_R | 200                      |     | ns   | External Interrupt         |  |

|                                                                                                                                            |                                        | NMI          | 200                      | -   |      | Non-Maskable Interrupt     |  |

\*: t<sub>CLKP1</sub> indicates the peripheral clock1 (CLKP1) cycle time except stop when in stop mode.

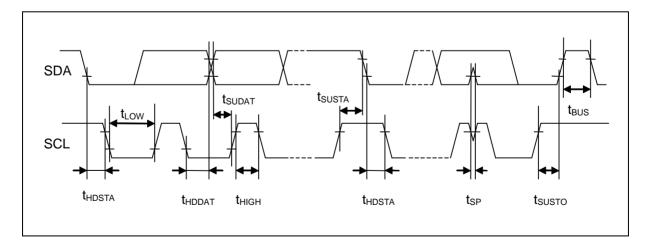

## 14.4.10 <sup>2</sup>C Timing

| Devementer                                                                        |                    |                                                                  |     | Typical mode                                           |     | High-speed mode*4                                      |      |

|-----------------------------------------------------------------------------------|--------------------|------------------------------------------------------------------|-----|--------------------------------------------------------|-----|--------------------------------------------------------|------|

| Parameter                                                                         | Symbol             | Conditions                                                       | Min | Max                                                    | Min | Max                                                    | Unit |

| SCL clock frequency                                                               | f <sub>SCL</sub>   |                                                                  | 0   | 100                                                    | 0   | 400                                                    | kHz  |

| (Repeated) START condition hold time $SDA \downarrow \rightarrow SCL \downarrow$  | t <sub>HDSTA</sub> |                                                                  | 4.0 | -                                                      | 0.6 | -                                                      | μs   |

| SCL clock "L" width                                                               | t <sub>LOW</sub>   |                                                                  | 4.7 | -                                                      | 1.3 | -                                                      | μS   |

| SCL clock "H" width                                                               | t <sub>HIGH</sub>  |                                                                  | 4.0 | -                                                      | 0.6 | -                                                      | μS   |

| (Repeated) START condition setup time SCL $\uparrow \rightarrow$ SDA $\downarrow$ | t <sub>SUSTA</sub> |                                                                  | 4.7 | -                                                      | 0.6 | -                                                      | μs   |

| Data hold time SCL $\downarrow \rightarrow$ SDA $\downarrow \uparrow$             | t <sub>HDDAT</sub> | $C_L = 50 \text{pF},$<br>R = (Vp/I <sub>OL</sub> ) <sup>*1</sup> | 0   | 3.45* <sup>2</sup>                                     | 0   | 0.9* <sup>3</sup>                                      | μS   |

| Data setup time $SDA \downarrow \uparrow \rightarrow SCL \uparrow$ $t_{SUDAT}$    |                    |                                                                  | 250 | -                                                      | 100 | -                                                      | ns   |

| STOP condition setup time SCL $\uparrow \rightarrow$ SDA $\uparrow$               | t <sub>susto</sub> |                                                                  | 4.0 | -                                                      | 0.6 | -                                                      | μS   |

| Bus free time between<br>"STOP condition" and<br>"START condition"                | t <sub>BUS</sub>   |                                                                  | 4.7 | -                                                      | 1.3 | -                                                      | μS   |

| Pulse width of spikes which will be<br>suppressed by input noise filter           | t <sub>SP</sub>    | -                                                                | 0   | ( <b>1-1.5)</b> ×<br>t <sub>СLКР1</sub> * <sup>5</sup> | 0   | ( <b>1-1.5)</b> ×<br>t <sub>CLКР1</sub> * <sup>5</sup> | ns   |

(V\_{CC} = AV\_{CC} = DV\_{CC} = 2.7V to 5.5V, V\_{SS} = AV\_{SS} = DV\_{SS} = 0V, T\_A = -40^{\circ}C to + 105°C)

<sup>\*1</sup>: R and C<sub>L</sub> represent the pull-up resistance and load capacitance of the SCL and SDA lines, respectively. Vp indicates the power supply voltage of the pull-up resistance and I<sub>OL</sub> indicates V<sub>OL</sub> guaranteed current.

$^{*2}$ : The maximum t<sub>HDDAT</sub> only has to be met if the device does not extend the "L" width (t<sub>LOW</sub>) of the SCL signal.

\*3: A high-speed mode I<sup>2</sup>C bus device can be used on a standard mode I<sup>2</sup>C bus system as long as the device satisfies the requirement of "t<sub>SUDAT</sub> ≥ 250ns".

<sup>\*4</sup>: For use at over 100kHz, set the peripheral clock1 (CLKP1) to at least 6MHz.

<sup>\*5</sup>: t<sub>CLKP1</sub> indicates the peripheral clock1 (CLKP1) cycle time.

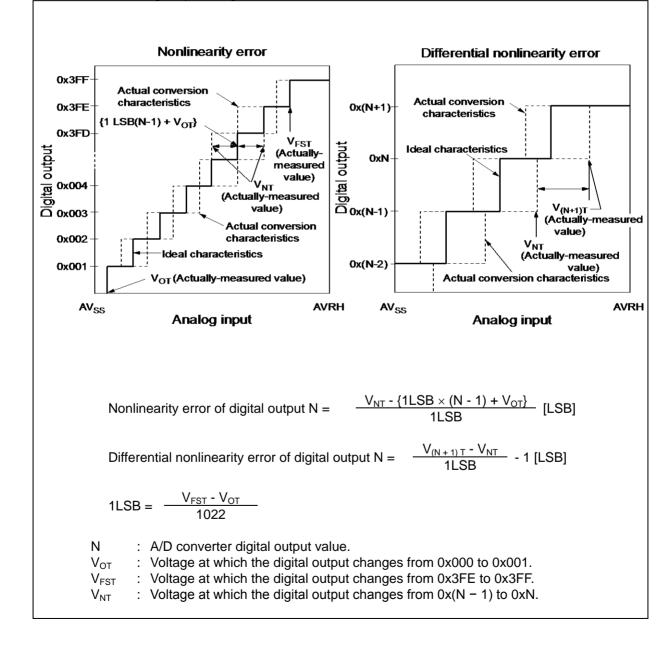

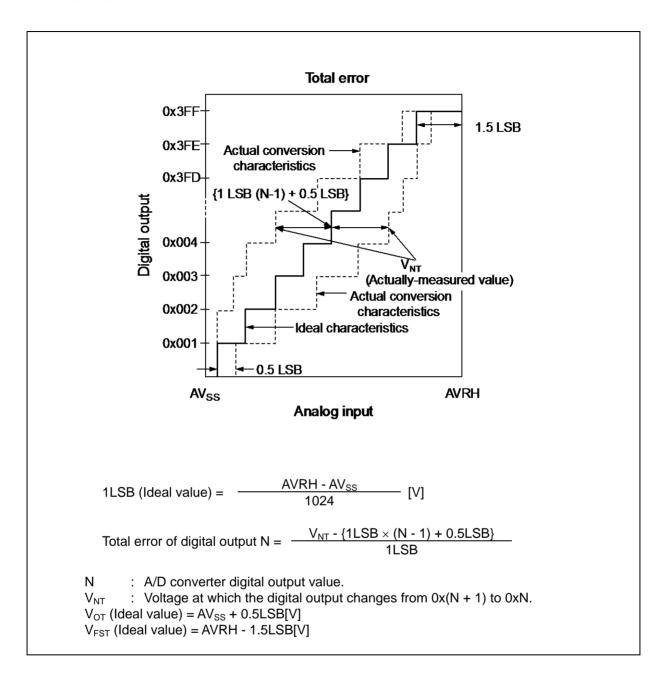

### 14.5.3 Definition of A/D Converter Terms

- Resolution : Analog variation that is recognized by an A/D converter.

- Nonlinearity error transition point

Deviation of the actual conversion characteristics from a straight line that connects the zero (0b000000000 ←→ 0b000000001) to the full-scale transition point (0b1111111110 ←→ 0b111111111).

- Differential nonlinearity error : Deviation from the ideal value of the input voltage that is required to change the output code by 1LSB.

- Total error : Difference between the actual value and the theoretical value. The total error includes zero transition error, full-scale transition error and nonlinearity error.

- Zero transition voltage : Input voltage which results in the minimum conversion value.

- Full scale transition voltage: Input voltage which results in the maximum conversion value.

## ■MB96F675

| Page     | Section                                                                            | Change Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40       | ELECTRICAL CHARACTERISTICS<br>3. DC Characteristics<br>(1) Current Rating          | Changed the annotation *2<br>Power supply for "On Chip Debugger" part is not included.<br>Power supply current in Run mode does not include<br>Flash Write / Erase current.<br>→<br>The current for "On Chip Debugger" part is not included.<br>Added the description to annotation *2, *3<br>When Flash is not in Power-down / reset mode, I <sub>CCFLASHPD</sub><br>must be added to the Power supply current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 52       | 4. AC Characteristics<br>(10) I <sup>2</sup> C timing                              | Added parameter, "Noise filter" and an annotation $*5$ for it<br>Added t <sub>SP</sub> to the figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 54       | 5. A/D Converter<br>(2) Accuracy and Setting of the A/D<br>Converter Sampling Time | Deleted the unit "[Min]" from approximation formula of Sampling time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 57       | 6. High Current Output Slew Rate                                                   | Changed the condition<br>$(V_{CC} = AV_{CC} = DV_{CC} = 2.7V \text{ to } 5.5V, VD=1.8V\pm0.15V, V_{SS} = AV_{SS} = DV_{SS} = 0V, T_A = -40^{\circ}\text{C to } + 105^{\circ}\text{C})$<br>$\rightarrow$<br>$(V_{CC} = AV_{CC} = DV_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = AV_{SS} = DV_{SS} = 0V, T_A = -40^{\circ}\text{C to } + 105^{\circ}\text{C})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 60       | 8. Flash Memory Write/Erase<br>Characteristics                                     | Changed the condition<br>$(V_{CC} = AV_{CC} = DV_{CC} = 2.7V \text{ to } 5.5V, VD=1.8V\pm0.15V, V_{SS} = AV_{SS} = DV_{SS} = 0V, T_A = -40^{\circ}\text{C to} + 105^{\circ}\text{C})$<br>$\rightarrow$<br>$(V_{CC} = AV_{CC} = DV_{CC} = 2.7V \text{ to } 5.5V, V_{SS} = AV_{SS} = DV_{SS} = 0V, T_A = -40^{\circ}\text{C to} + 105^{\circ}\text{C})$<br>Changed the Note<br>While the Flash memory is written, shutdown of the external<br>power (V <sub>CC</sub> ) is prohibited. In the application system where the<br>external power (V <sub>CC</sub> ) might be shut down while writing, be<br>sure to turn the power off by using an external voltage<br>detector.<br>$\rightarrow$<br>While the Flash memory is written or erased, shutdown of the<br>external power (V <sub>CC</sub> ) is prohibited. In the application system<br>where the external power (V <sub>CC</sub> ) might be shut down while<br>writing or erasing, be sure to turn the power off by using a low<br>voltage detection function. |

| Revision |                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -        | -                                                                                  | Company name and layout design change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

NOTE: Please see "Document History" about later revised information.