Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

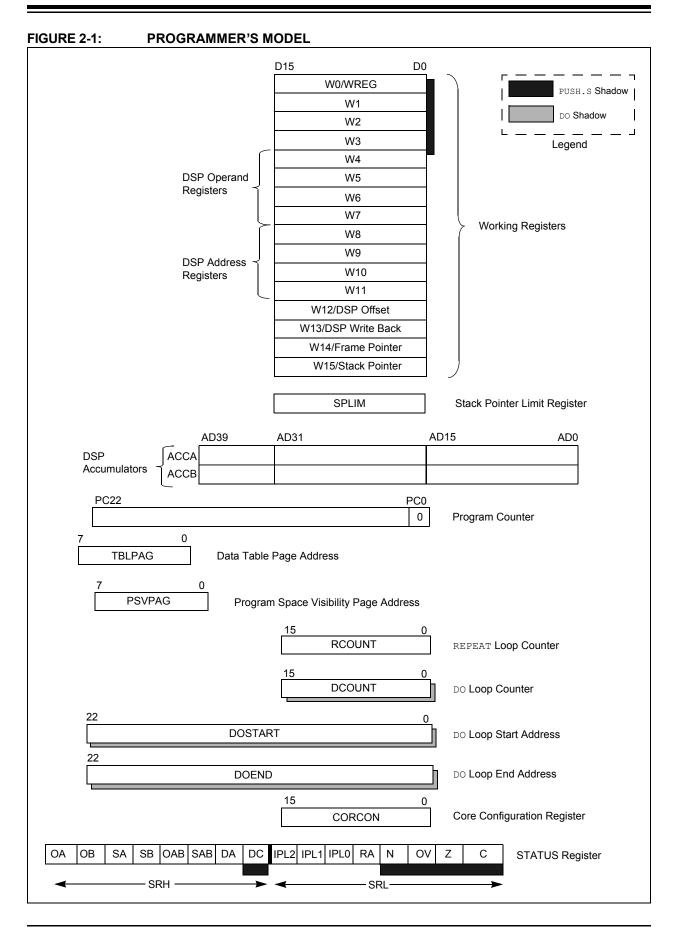

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 30 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | AC'97, Brown-out Detect/Reset, I <sup>2</sup> S, LVD, POR, PWM, WDT            |

| Number of I/O              | 52                                                                             |

| Program Memory Size        | 144KB (48K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 4K x 8                                                                         |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 16x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6012a-30i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1-1 provides a brief description of device I/O pinouts and the functions that may be multiplexed to a port pin. Multiple functions may exist on one port pin. When multiplexing occurs, the peripheral module's functional requirements may force an override of the data direction of the port pin.

| Pin Name     | e Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                    |

|--------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN15     |               | Analog         | Analog input channels.<br>AN0 and AN1 are also used for device programming data and clock inputs,<br>respectively.                                                                                                             |

| AVdd         | Р             | Р              | Positive supply for analog module. This pin must be connected at all times.                                                                                                                                                    |

| AVss         | Р             | Р              | Ground reference for analog module. This pin must be connected at all times.                                                                                                                                                   |

| CLKI         | I             | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator                                                                    |

| CLKO         | 0             | _              | mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function.                                                                                                                               |

| CN0-CN23     | 3             | ST             | Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                      |

| COFS         | I/O           | ST             | Data Converter Interface frame synchronization pin.                                                                                                                                                                            |

| CSCK         | I/O           | ST             | Data Converter Interface serial clock input/output pin.                                                                                                                                                                        |

| CSDI         |               | ST             | Data Converter Interface serial data input pin.                                                                                                                                                                                |

| CSDO         | 0             |                | Data Converter Interface serial data output pin.                                                                                                                                                                               |

| C1RX         |               | ST             | CAN1 bus receive pin.                                                                                                                                                                                                          |

| C1TX         | 0             |                | CAN1 bus transmit pin.                                                                                                                                                                                                         |

| C2RX<br>C2TX | 0             | ST             | CAN2 bus receive pin.<br>CAN2 bus transmit pin                                                                                                                                                                                 |

| EMUD         | 1/O           | ST             | ICD Primary Communication Channel data input/output pin.                                                                                                                                                                       |

| EMUC         | I/O           | ST             | ICD Primary Communication Channel clock input/output pin.                                                                                                                                                                      |

| EMUD1        | I/O           | ST             | ICD Secondary Communication Channel data input/output pin.                                                                                                                                                                     |

| EMUC1        | I/O           | ST             | ICD Secondary Communication Channel clock input/output pin.                                                                                                                                                                    |

| EMUD2        | I/O           | ST             | ICD Tertiary Communication Channel data input/output pin.                                                                                                                                                                      |

| EMUC2        | I/O           | ST             | ICD Tertiary Communication Channel clock input/output pin.                                                                                                                                                                     |

| EMUD3        | I/O           | ST             | ICD Quaternary Communication Channel data input/output pin.                                                                                                                                                                    |

| EMUC3        | I/O           | ST             | ICD Quaternary Communication Channel clock input/output pin.                                                                                                                                                                   |

| IC1-IC8      | I             | ST             | Capture inputs 1 through 8.                                                                                                                                                                                                    |

| INT0         | I             | ST             | External interrupt 0.                                                                                                                                                                                                          |

| INT1         | I             | ST             | External interrupt 1.                                                                                                                                                                                                          |

| INT2         |               | ST             | External interrupt 2.                                                                                                                                                                                                          |

| INT3         |               | ST             | External interrupt 3.                                                                                                                                                                                                          |

| INT4         |               | ST             | External interrupt 4.                                                                                                                                                                                                          |

| LVDIN        |               | Analog         | Low-Voltage Detect Reference Voltage input pin.                                                                                                                                                                                |

| MCLR         | I/P           | ST             | Master Clear (Reset) input or programming voltage input. This pin is an active-low Reset to the device.                                                                                                                        |

| OCFA         | I             | ST             | Compare Fault A input (for Compare channels 1, 2, 3 and 4).                                                                                                                                                                    |

| OCFB         | I.            | ST             | Compare Fault B input (for Compare channels 5, 6, 7 and 8).                                                                                                                                                                    |

| 0C1-0C8      | 0             | —              | Compare outputs 1 through 8.                                                                                                                                                                                                   |

| OSC1<br>OSC2 | I<br>I/O      | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. |

| Legend:      | CMOS =        | CMOS co        | mpatible input or output Analog = Analog input                                                                                                                                                                                 |

|              | ST =          |                | rigger input with CMOS levels O = Output                                                                                                                                                                                       |

|              | =             | Input          | P = Power                                                                                                                                                                                                                      |

## TABLE 1-1:PINOUT I/O DESCRIPTIONS

## 3.0 MEMORY ORGANIZATION

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

## 3.1 Program Address Space

The program address space is 4M instruction words. It is addressable by a 24-bit value from either the 23-bit PC, table instruction Effective Address (EA), or data space EA, when program space is mapped into data space as defined by Table 3-1. Note that the program space address is incremented by two between successive program words in order to provide compatibility with data space addressing. User program space access is restricted to the lower 4M instruction word address range (0x000000 to 0x7FFFFE) for all accesses other than TBLRD/TBLWT, which use TBLPAG<7> to determine user or configuration space access. In Table 3-1, Program Space Address Construction, bit 23 allows access to the Device ID, the Unit ID and the configuration bits. Otherwise, bit 23 is always clear.

Note: The address map shown in Figure 3-1 and Figure 3-2 is conceptual, and the actual memory configuration may vary across individual devices depending on available memory.

### 3.1.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

This architecture fetches 24-bit wide program memory. Consequently, instructions are always aligned. However, as the architecture is modified Harvard, data can also be present in program space.

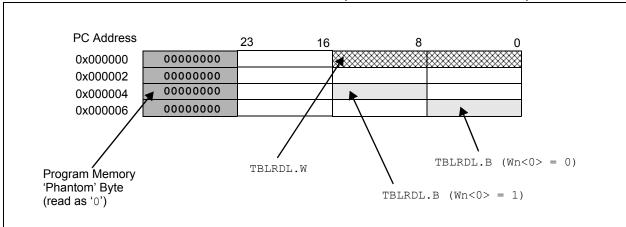

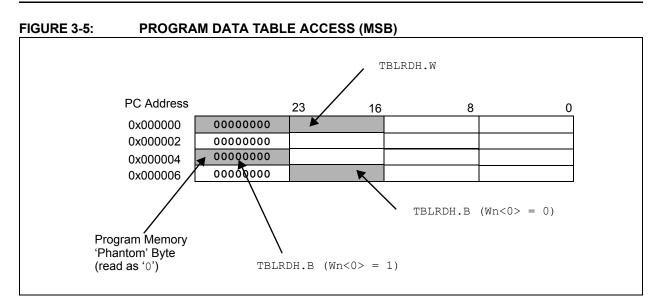

There are two methods by which program space can be accessed: via special table instructions, or through the remapping of a 16K word program space page into the upper half of data space (see Section 3.1.2 "Data Access From Program Memory using Program Space Visibility"). The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lsw of any address within program space, without going through data space. The TBLRDH and TBLWTH instructions are the only method whereby the upper 8 bits of a program space word can be accessed as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the Least Significant Data Word, and TBLRDH and TBLWTH access the space which contains the Most Significant Data Byte.

Figure 3-3 shows how the EA is created for table operations and data space accesses (PSV = 1). Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word. A set of table instructions are provided to move byte or word sized data to and from program space.

TBLRDL: Table Read Low Word: Read the lsw of the program address; P<15:0> maps to D<15:0>.

Byte: Read one of the LSBs of the program address; P<7:0> maps to the destination byte when byte

P<7:0> maps to the destination byte when byte select = 0;

P < 15:8> maps to the destination byte when byte select = 1.

- TBLWTL: Table Write Low (refer to Section 6.0 "Flash Program Memory" for details on Flash Programming)

- TBLRDH: Table Read High Word: Read the most significant word of the program address; P<23:16> maps to D<7:0>; D<15:8> will always be = 0. Byte: Read one of the MSBs of the program

address;

P<23:16> maps to the destination byte when byte select = 0;

The destination byte will always be = 0 when byte select = 1.

TBLWTH: Table Write High (refer to Section 6.0 "Flash Program Memory" for details on Flash Programming).

## FIGURE 3-4: PROGRAM DATA TABLE ACCESS (LEAST SIGNIFICANT WORD)

#### 3.1.2 DATA ACCESS FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

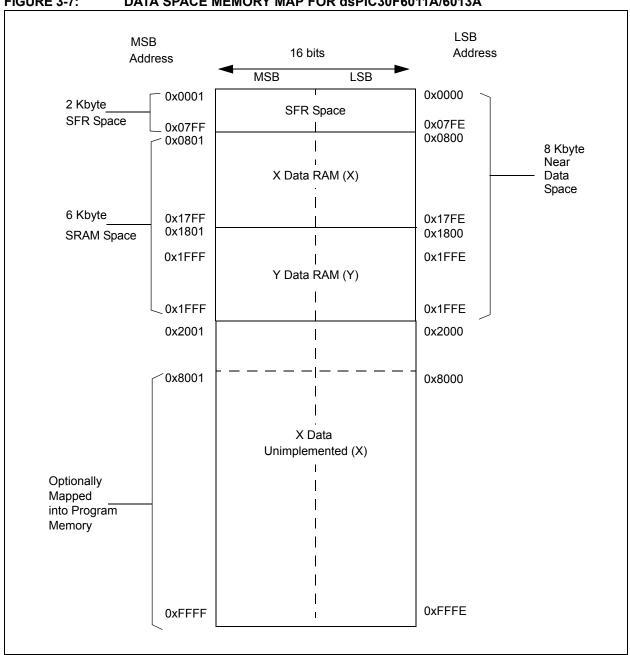

The upper 32 Kbytes of data space may optionally be mapped into any 16K word program space page. This provides transparent access of stored constant data from X data space without the need to use special instructions (i.e., TBLRDL/H, TBLWTL/H instructions).

Program space access through the data space occurs if the MSb of the data space EA is set and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON). The functions of CORCON are discussed in **Section 2.4** "**DSP Engine**".

Data accesses to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Note that the upper half of addressable data space is always part of the X data space. Therefore, when a DSP operation uses program space mapping to access this memory region, Y data space should typically contain state (variable) data for DSP operations, whereas X data space should typically contain coefficient (constant) data.

Although each data space address, 0x8000 and higher, maps directly into a corresponding program memory address (see Figure 3-6), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits should be programmed to force an illegal instruction to maintain machine robustness. Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for details on instruction encoding. Note that by incrementing the PC by 2 for each program memory word, the Least Significant 15 bits of data space addresses directly map to the Least Significant 15 bits in the corresponding program space addresses. The remaining bits are provided by the Program Space Visibility Page register, PSVPAG<7:0>, as shown in Figure 3-6.

Note: PSV access is temporarily disabled during table reads/writes.

For instructions that use PSV which are executed outside a REPEAT loop:

- The following instructions will require one instruction cycle in addition to the specified execution time:

- MAC class of instructions with data operand prefetch

- MOV instructions

- MOV.D instructions

- All other instructions will require two instruction cycles in addition to the specified execution time of the instruction.

For instructions that use PSV which are executed inside a  $\ensuremath{\mathtt{REPEAT}}$  loop:

- The following instances will require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

- Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

## FIGURE 3-7: DATA SPACE MEMORY MAP FOR dsPIC30F6011A/6013A

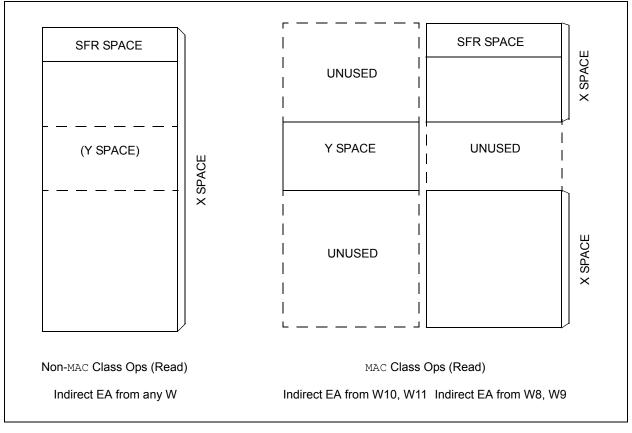

## FIGURE 3-9: DATA SPACE FOR MCU AND DSP (MAC CLASS) INSTRUCTIONS EXAMPLE

# TABLE 3-2:EFFECT OF INVALID<br/>MEMORY ACCESSES

| Attempted Operation                                         | Data Returned         |

|-------------------------------------------------------------|-----------------------|

| EA = an unimplemented address                               | 0x0000 <sup>(1)</sup> |

| W8 or W9 used to access Y data space in a MAC instruction   | 0x0000                |

| W10 or W11 used to access X data space in a MAC instruction | 0x0000                |

Note 1: An address error trap is generated when an unimplemented memory address is accessed.

All effective addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes or 32K words.

## 3.2.3 DATA SPACE WIDTH

The core data width is 16 bits. All internal registers are organized as 16-bit wide words. Data space memory is organized in byte addressable, 16-bit wide blocks.

## 3.2.4 DATA ALIGNMENT

To help maintain backward compatibility with PIC® MCU devices and improve data space memory usage efficiency, the dsPIC30F instruction set supports both word and byte operations. Data is aligned in data memory and registers as words, but all data space EAs resolve to bytes. Data byte reads will read the complete word which contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the X data path (no byte accesses are possible from the Y data path as the MAC class of instruction can only fetch words). That is, data memory and registers are organized as two parallel byte wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address.

As a consequence of this byte accessibility, all Effective Address calculations (including those generated by the DSP operations which are restricted to word-sized data) are internally scaled to step through word aligned memory. For example, the core would recognize that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

## 6.6 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. A programming operation is nominally 2 msec in duration and the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

#### 6.6.1 PROGRAMMING ALGORITHM FOR PROGRAM FLASH

The user can erase and program one row of program Flash memory at a time. The general process is:

- 1. Read one row of program Flash (32 instruction words) and store into data RAM as a data "image".

- 2. Update the data image with the desired new data.

- 3. Erase program Flash row.

- a) Set up NVMCON register for multi-word, program Flash, erase, and set WREN bit.

- b) Write address of row to be erased into NVMADRU/NVMADR.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

EXAMPLE 6-1:

- e) Set the WR bit. This will begin erase cycle.

- f) CPU will stall for the duration of the erase cycle.

- g) The WR bit is cleared when erase cycle ends.

- Write 32 instruction words of data from data RAM "image" into the program Flash write latches.

- 5. Program 32 instruction words into program Flash.

- a) Set up NVMCON register for multi-word, program Flash, program, and set WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. This will begin program cycle.

- e) CPU will stall for duration of the program cycle.

- f) The WR bit is cleared by the hardware when program cycle ends.

- 6. Repeat steps 1 through 5 as needed to program desired amount of program Flash memory.

# 6.6.2 ERASING A ROW OF PROGRAM MEMORY

Example 6-1 shows a code sequence that can be used to erase a row (32 instructions) of program memory.

| program | n memor | y selected, and writes enable       | d |                                           |

|---------|---------|-------------------------------------|---|-------------------------------------------|

| М       | IOV     | #0x4041,W0                          | ; |                                           |

| М       | IOV     | W0,NVMCON                           | ; | Init NVMCON SFR                           |

| Init po | ointer  | to row to be ERASED                 |   |                                           |

| М       | IOV     | <pre>#tblpage(PROG_ADDR),W0</pre>   | ; |                                           |

| М       | IOV     | W0,NVMADRU                          | ; | Initialize PM Page Boundary SFR           |

| М       | IOV     | <pre>#tbloffset(PROG_ADDR),W0</pre> | ; | Intialize in-page EA[15:0] pointer        |

| М       | IOV     | W0, NVMADR                          | ; | Initialize NVMADR SFR                     |

| D       | ISI     | #5                                  | ; | Block all interrupts with priority <7 for |

|         |         |                                     | ; | next 5 instructions                       |

| М       | IOV     | #0x55,W0                            |   |                                           |

| М       | IOV     | W0,NVMKEY                           | ; | Write the 0x55 key                        |

| М       | IOV     | #OxAA,W1                            | ; |                                           |

| М       | IOV     | W1,NVMKEY                           | ; | Write the OxAA key                        |

| В       | SET     | NVMCON, #WR                         | ; | Start the erase sequence                  |

| Ν       | IOP     |                                     | ; | Insert two NOPs after the erase           |

| Ν       | IOP     |                                     | ; | command is asserted                       |

**ERASING A ROW OF PROGRAM MEMORY**

NOTES:

| SFR Name     Addr.     Bit 15       OC1RS     0180 |        |        |        | -      | -      |        |           |           |                                     |       |       |        |       | _        |       |                     |

|----------------------------------------------------|--------|--------|--------|--------|--------|--------|-----------|-----------|-------------------------------------|-------|-------|--------|-------|----------|-------|---------------------|

| 0180                                               | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8     | Bit 7     | Bit 6                               | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 Bi | Bit 0 | Reset State         |

|                                                    |        |        |        |        |        | Output | Compare   | 1 Secon   | Output Compare 1 Secondary Register | ster  |       |        |       |          | 0000  | 0 0000 0000 0000 0  |

| 0182                                               |        |        |        |        |        | Outp   | out Comp. | are 1 Ma  | Output Compare 1 Main Register      |       |       |        |       |          | 000   | 0000 0000 0000 0000 |

| 0184 —                                             | I      | OCSIDL |        |        | I      | I      |           | I         | Ι                                   | I     | OCFLT | OCTSEL |       | OCM<2:0> | 0000  | 0 0000 0000 0000 0  |

| 0186                                               |        |        |        |        |        | Output | Compare   | 2 Secon   | Output Compare 2 Secondary Register | ster  |       |        |       |          | 000   | 0000 0000 0000 0000 |

| 0188                                               |        |        |        |        |        | Out    | out Comp. | are 2 Ma  | Output Compare 2 Main Register      |       |       |        |       |          | 0000  | 0 0000 0000 0000 0  |

| 018A —                                             |        | OCSIDL |        |        | 1      | I      |           | Ι         | -                                   | Ι     | OCFLT | OCTSE  |       | OCM<2:0> | 0000  | 0 0000 0000 0000 0  |

| 018C                                               |        |        |        |        |        | Output | Compare   | 3 Secon   | Output Compare 3 Secondary Register | ster  |       |        |       |          | 000   | 0000 0000 0000 0000 |

| 018E                                               |        |        |        |        |        | Out    | out Comp. | are 3 Mai | Output Compare 3 Main Register      |       |       |        |       |          | 0000  | 0 0000 0000 0000 0  |

| 0190 —                                             | I      | OCSIDL |        | I      | 1      |        |           | I         | I                                   | I     | OCFLT | OCTSEL |       | OCM<2:0> | 000   | 0000 0000 0000 0000 |

| 0192                                               |        |        |        |        |        | Output | Compare   | e 4 Secon | Output Compare 4 Secondary Register | ster  |       |        |       |          | 000   | 0000 0000 0000 0000 |

| 0194                                               |        |        |        |        |        | Out    | out Comp. | are 4 Ma  | Output Compare 4 Main Register      |       |       |        |       |          | 0000  | 0 0000 0000 0000 0  |

| 0196 —                                             | I      | OCSIDL |        |        | I      | 1      |           | I         | Ι                                   | I     | OCFLT | OCTSEL |       | OCM<2:0> | 000   | 0000 0000 0000 0000 |

| 0198                                               |        |        |        |        |        | Output | Compare   | 5 Secon   | Output Compare 5 Secondary Register | ster  |       |        |       |          | 000   | 0000 0000 0000 0000 |

| 019A                                               |        |        |        |        |        | Out    | out Comp. | are 5 Mai | Output Compare 5 Main Register      | ·     |       |        |       |          | 000   | 0000 0000 0000 0000 |

| 019C —                                             |        | OCSIDL |        |        | 1      | I      |           | I         | -                                   | Ι     | OCFLT | OCTSEL |       | OCM<2:0> | 0000  | 0 0000 0000 0000 0  |

| 019E                                               |        |        |        |        |        | Output | Compare   | e Secon   | Output Compare 6 Secondary Register | ster  |       |        |       |          | 0000  | 0 0000 0000 0000 0  |

| 01A0                                               |        |        |        |        |        | Outp   | out Comp. | are 6 Mai | Output Compare 6 Main Register      |       |       |        |       |          | 000   | 0000 0000 0000 0000 |

| 01A2 —                                             | Ι      | OCSIDL |        |        |        |        |           | Ι         | Ι                                   | Ι     | OCFLT | OCTSEL |       | OCM<2:0> | 0000  | 0 0000 0000 0000 0  |

| 01A4                                               |        |        |        |        |        | Output | Compare   | 7 Secon   | Output Compare 7 Secondary Register | ster  |       |        |       |          | 000   | 0000 0000 0000 0000 |

| 01A6                                               |        |        |        |        |        | Out    | out Comp. | are 7 Mai | Output Compare 7 Main Register      | ·     |       |        |       |          | 000   | 0000 0000 0000 0000 |

| 01A8 —                                             |        | OCSIDL |        |        | 1      | I      |           | Ι         | -                                   | Ι     | OCFLT | OCTSEL |       | OCM<2:0> | 0000  | 0 0000 0000 0000 0  |

| 01AA                                               |        |        |        |        |        | Output | Compare   | 8 Secon   | Output Compare 8 Secondary Register | ster  |       |        |       |          | 000   | 0000 0000 0000 0000 |

| 01AC                                               |        |        |        |        |        | Outp   | out Comp. | are 8 Ma  | Output Compare 8 Main Register      |       |       |        |       |          | 0000  | 0 0000 0000 0000 0  |

| 01AE                                               |        | OCSIDL | I      |        | I      |        | I         | I         | Ι                                   | Ι     | OCFLT | OCTSEL |       | OCM<2:0> | 000   | 0000 0000 0000 0000 |

## 15.12.3 BAUD RATE GENERATOR

In I<sup>2</sup>C Master mode, the reload value for the BRG is located in the I2CBRG register. When the BRG is loaded with this value, the BRG counts down to '0' and stops until another reload has taken place. If clock arbitration is taking place, for instance, the BRG is reloaded when the SCL pin is sampled high.

As per the I<sup>2</sup>C standard, FSCK may be 100 kHz or 400 kHz. However, the user can specify any baud rate up to 1 MHz. I2CBRG values of '0' or '1' are illegal.

$I2CBRG = \left(\frac{FCY}{FSCK} - \frac{FCY}{1,111,111}\right) - 1$

## 15.12.4 CLOCK ARBITRATION

Clock arbitration occurs when the master deasserts the SCL pin (SCL allowed to float high) during any receive, transmit, or Restart/Stop condition. When the SCL pin is allowed to float high, the Baud Rate Generator is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of I2CBRG and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device.

### 15.12.5 MULTI-MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-master operation support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high while another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the MI2CIF pulse and reset the master portion of the I<sup>2</sup>C port to its Idle state.

If a transmit was in progress when the bus collision occurred, the transmission is halted, the TBF flag is cleared, the SDA and SCL lines are deasserted and a value can now be written to I2CTRN. When the user services the  $I^2C$  master event Interrupt Service Routine, if the  $I^2C$  bus is free (i.e., the P bit is set), the user can resume communication by asserting a Start condition.

If a Start, Restart, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted, and the respective control bits in the I2CCON register are cleared to '0'. When the user services the bus collision Interrupt Service Routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins, and if a Stop condition occurs, the MI2CIF bit will be set.

A write to the I2CTRN will start the transmission of data at the first data bit regardless of where the transmitter left off when bus collision occurred.

In a multi-master environment, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$ bus can be taken when the P bit is set in the I2CSTAT register, or the bus is Idle and the S and P bits are cleared.

## 15.13 I<sup>2</sup>C Module Operation During CPU Sleep and Idle Modes

## 15.13.1 I<sup>2</sup>C OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shutdown and stay at logic '0'. If Sleep occurs in the middle of a transmission and the state machine is partially into a transmission as the clocks stop, then the transmission is aborted. Similarly, if Sleep occurs in the middle of a reception, then the reception is aborted.

# 15.13.2 I<sup>2</sup>C OPERATION DURING CPU IDLE MODE

For the I<sup>2</sup>C, the I2CSIDL bit selects if the module will stop on Idle or continue on Idle. If I2CSIDL = 0, the module will continue operation on assertion of the Idle mode. If I2CSIDL = 1, the module will stop on Idle.

NOTES:

Receive Error Interrupts:

A receive error interrupt will be indicated by the ERRIF bit. This bit shows that an error condition occurred. The source of the error can be determined by checking the bits in the CAN Interrupt status register, CiINTF.

- Invalid Message Received:

If any type of error occurred during reception of the last message, an error will be indicated by the IVRIF bit.

- Receiver Overrun:

The RXnOVR bit indicates that an overrun condition occurred.

- Receiver Warning:

The RXWAR bit indicates that the receive error counter (RERRCNT<7:0>) has reached the warning limit of 96.

- Receiver Error Passive:

The RXEP bit indicates that the receive error counter has exceeded the error passive limit of 127 and the module has gone into error passive state.

## 17.5 Message Transmission

## 17.5.1 TRANSMIT BUFFERS

The CAN module has three transmit buffers. Each of the three buffers occupies 14 bytes of data. Eight of the bytes are the maximum 8 bytes of the transmitted message. Five bytes hold the standard and extended identifiers and other message arbitration information.

## 17.5.2 TRANSMIT MESSAGE PRIORITY

Transmit priority is a prioritization within each node of the pending transmittable messages. There are 4 levels of transmit priority. If TXPRI<1:0> (CiTXnCON<1:0>, where n = 0, 1 or 2 represents a particular transmit buffer) for a particular message buffer is set to '11', that buffer has the highest priority. If TXPRI<1:0> for a particular message buffer is set to '10' or '01', that buffer has an intermediate priority. If TXPRI<1:0> for a particular message buffer is '00', that buffer has the lowest priority.

## 17.5.3 TRANSMISSION SEQUENCE

To initiate transmission of the message, the TXREQ bit (CiTXnCON<3>) must be set. The CAN bus module resolves any timing conflicts between setting of the TXREQ bit and the Start of Frame (SOF), ensuring that if the priority was changed, it is resolved correctly before the SOF occurs. When the TXREQ is set, the TXABT (CiTXnCON<6>), TXLARB (CiTXnCON<5>) and TXERR (CiTXnCON<4>) flag bits are automatically cleared.

Setting the TXREQ bit simply flags a message buffer as enqueued for transmission. When the module detects an available bus, it begins transmitting the message which has been determined to have the highest priority.

If the transmission completes successfully on the first attempt, the TXREQ bit is cleared automatically, and an interrupt is generated if TXIE was set.

If the message transmission fails, one of the error condition flags will be set, and the TXREQ bit will remain set indicating that the message is still pending for transmission. If the message encountered an error condition during the transmission attempt, the TXERR bit will be set, and the error condition may cause an interrupt. If the message loses arbitration during the transmission attempt, the TXLARB bit is set. No interrupt is generated to signal the loss of arbitration.

## 17.5.4 ABORTING MESSAGE TRANSMISSION

The system can also abort a message by clearing the TXREQ bit associated with each message buffer. Setting the ABAT bit (CiCTRL<12>) will request an abort of all pending messages. If the message has not yet started transmission, or if the message started but is interrupted by loss of arbitration or an error, the abort will be processed. The abort is indicated when the module sets the TXABT bit and the TXnIF flag is not automatically set.

## 17.5.5 TRANSMISSION ERRORS

The CAN module will detect the following transmission errors:

- Acknowledge Error

- Form Error

- Bit Error

These transmission errors will not necessarily generate an interrupt but are indicated by the transmission error counter. However, each of these errors will cause the transmission error counter to be incremented by one. Once the value of the error counter exceeds the value of 96, the ERRIF (CiINTF<5>) and the TXWAR bit (CiINTF<10>) are set. Once the value of the error counter exceeds the value of 96, an interrupt is generated and the TXWAR bit in the Error Flag register is set.

# 18.0 DATA CONVERTER INTERFACE (DCI) MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

## 18.1 Module Introduction

The dsPIC30F Data Converter Interface (DCI) module allows simple interfacing of devices, such as audio coder/decoders (Codecs), ADC and DAC. The following interfaces are supported:

- Framed Synchronous Serial Transfer (Single or Multi-Channel)

- Inter-IC Sound (I<sup>2</sup>S) Interface

- AC-Link Compliant mode

The DCI module provides the following general features:

- Programmable word size up to 16 bits

- Support for up to 16 time slots, for a maximum frame size of 256 bits

- Data buffering for up to 4 samples without CPU overhead

## 18.2 Module I/O Pins

There are four I/O pins associated with the module. When enabled, the module controls the data direction of each of the four pins.

## 18.2.1 CSCK PIN

The CSCK pin provides the serial clock for the DCI module. The CSCK pin may be configured as an input or output using the CSCKD control bit in the DCICON1 SFR. When configured as an output, the serial clock is provided by the dsPIC30F. When configured as an input, the serial clock must be provided by an external device.

## 18.2.2 CSDO PIN

The serial data output (CSDO) pin is configured as an output only pin when the module is enabled. The CSDO pin drives the serial bus whenever data is to be transmitted. The CSDO pin is tri-stated or driven to '0' during CSCK periods when data is not transmitted, depending on the state of the CSDOM control bit. This allows other devices to place data on the serial bus during transmission periods not used by the DCI module.

## 18.2.3 CSDI PIN

The serial data input (CSDI) pin is configured as an input only pin when the module is enabled.

## 18.2.3.1 COFS PIN

The Codec Frame Synchronization (COFS) pin is used to synchronize data transfers that occur on the CSDO and CSDI pins. The COFS pin may be configured as an input or an output. The data direction for the COFS pin is determined by the COFSD control bit in the DCICON1 register.

The DCI module accesses the shadow registers while the CPU is in the process of accessing the memory mapped buffer registers.

## 18.2.4 BUFFER DATA ALIGNMENT

Data values are always stored left justified in the buffers since most Codec data is represented as a signed 2's complement fractional number. If the received word length is less than 16 bits, the unused LSbs in the receive buffer registers are set to '0' by the module. If the transmitted word length is less than 16 bits, the unused LSbs in the transmit buffer register are ignored by the module. The word length setup is described in subsequent sections of this document.

### 18.2.5 TRANSMIT/RECEIVE SHIFT REGISTER

The DCI module has a 16-bit shift register for shifting serial data in and out of the module. Data is shifted in/ out of the shift register MSb first, since audio PCM data is transmitted in signed 2's complement format.

## 18.2.6 DCI BUFFER CONTROL

The DCI module contains a buffer control unit for transferring data between the shadow buffer memory and the serial shift register. The buffer control unit is a simple 2-bit address counter that points to word locations in the shadow buffer memory. For the receive memory space (high address portion of DCI buffer memory), the address counter is concatenated with a '0' in the MSb location to form a 3-bit address. For the transmit memory space (high portion of DCI buffer memory), the address counter is concatenated with a '1' in the MSb location.

Note: The DCI buffer control unit always accesses the same relative location in the transmit and receive buffers, so only one address counter is provided.

| Base<br>Instr # | Assembly<br>Mnemonic |            | Assembly Syntax   | Description                               | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|-----------------|----------------------|------------|-------------------|-------------------------------------------|---------------|----------------|--------------------------|

| 1               | ADD                  | ADD        | Acc               | Add Accumulators                          | 1             | 1              | OA,OB,SA,SB              |

|                 |                      | ADD        | f                 | f = f + WREG                              | 1             | 1              | C,DC,N,OV,Z              |

|                 |                      | ADD        | f,WREG            | WREG = f + WREG                           | 1             | 1              | C,DC,N,OV,Z              |

|                 |                      | ADD        | #lit10,Wn         | Wd = lit10 + Wd                           | 1             | 1              | C,DC,N,OV,Z              |

|                 |                      | ADD        | Wb,Ws,Wd          | Wd = Wb + Ws                              | 1             | 1              | C,DC,N,OV,Z              |

|                 |                      | ADD        | Wb,#lit5,Wd       | Wd = Wb + lit5                            | 1             | 1              | C,DC,N,OV,Z              |

|                 |                      | ADD        | Wso,#Slit4,Acc    | 16-bit Signed Add to Accumulator          | 1             | 1              | OA,OB,SA,SB              |

| 2               | ADDC                 | ADDC       | f                 | f = f + WREG + (C)                        | 1             | 1              | C,DC,N,OV,Z              |

|                 |                      | ADDC       | f,WREG            | WREG = f + WREG + (C)                     | 1             | 1              | C,DC,N,OV,Z              |

|                 |                      | ADDC       | #lit10,Wn         | Wd = lit10 + Wd + (C)                     | 1             | 1              | C,DC,N,OV,Z              |

|                 |                      | ADDC       | Wb,Ws,Wd          | Wd = Wb + Ws + (C)                        | 1             | 1              | C,DC,N,OV,Z              |

|                 |                      | ADDC       | Wb,#lit5,Wd       | Wd = Wb + lit5 + (C)                      | 1             | 1              | C,DC,N,OV,Z              |

| 3               | AND                  | AND        | f                 | f = f .AND. WREG                          | 1             | 1              | N,Z                      |

|                 |                      | AND        | f,WREG            | WREG = f .AND. WREG                       | 1             | 1              | N,Z                      |

|                 |                      | AND        | #lit10,Wn         | Wd = lit10 .AND. Wd                       | 1             | 1              | N,Z                      |

|                 |                      | AND        | Wb,Ws,Wd          | Wd = Wb .AND. Ws                          | 1             | 1              | N,Z                      |

|                 |                      | AND        | Wb,#lit5,Wd       | Wd = Wb .AND. lit5                        | 1             | 1              | N,Z                      |

| 4               | ASR                  | ASR        | f                 | f = Arithmetic Right Shift f              | 1             | 1              | C,N,OV,Z                 |

|                 |                      | ASR        | f,WREG            | WREG = Arithmetic Right Shift f           | 1             | 1              | C,N,OV,Z                 |

|                 |                      | ASR        | Ws,Wd             | Wd = Arithmetic Right Shift Ws            | 1             | 1              | C,N,OV,Z                 |

|                 |                      | ASR        | Wb,Wns,Wnd        | Wnd = Arithmetic Right Shift Wb by Wns    | 1             | 1              | N,Z                      |

|                 |                      | ASR        | Wb,#lit5,Wnd      | Wnd = Arithmetic Right Shift Wb by lit5   | 1             | 1              | N,Z                      |

| 5               | BCLR                 | BCLR       | f,#bit4           | Bit Clear f                               | 1             | 1              | None                     |

|                 |                      | BCLR       | Ws,#bit4          | Bit Clear Ws                              | 1             | 1              | None                     |

| 6               | BRA                  | BRA        | C,Expr            | Branch if Carry                           | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | GE, Expr          | Branch if greater than or equal           | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | GEU,Expr          | Branch if unsigned greater than or equal  | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | GT, Expr          | Branch if greater than                    | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | GTU, Expr         | Branch if unsigned greater than           | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | LE, Expr          | Branch if less than or equal              | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | LEU, Expr         | Branch if unsigned less than or equal     | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | LT, Expr          | Branch if less than                       | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | LTU, Expr         | Branch if unsigned less than              | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | N,Expr            | Branch if Negative                        | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | NC,Expr           | Branch if Not Carry                       | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | NN, Expr          | Branch if Not Negative                    | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | NOV, Expr         | Branch if Not Overflow                    | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | NZ, Expr          | Branch if Not Zero                        | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | OA, Expr          | Branch if Accumulator A overflow          | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | OB, Expr          | Branch if Accumulator B overflow          | 1             | 1 (2)          | None                     |

|                 |                      | BRA        | -                 | Branch if Overflow                        | 1             | 1 (2)          | None                     |

|                 |                      |            | OV, Expr          | Branch if Accumulator A saturated         | 1             |                |                          |

|                 |                      | BRA        | SA, Expr          | Branch if Accumulator B saturated         | 1             | 1 (2)          | None<br>None             |

|                 |                      | BRA<br>BRA | SB, Expr          | Branch Unconditionally                    | 1             | 1 (2)<br>2     | None                     |

|                 |                      |            | Expr<br>7 Evpr    | Branch if Zero                            | 1             |                | None                     |

|                 |                      | BRA        | Z,Expr            |                                           |               | 1 (2)          |                          |

| 7               | DODE                 | BRA        | Wn                | Computed Branch                           | 1             | 2              | None                     |

| 7               | BSET                 | BSET       | f,#bit4           | Bit Set f                                 | 1             | 1              | None                     |

|                 |                      | BSET       | Ws,#bit4<br>Ws,Wb | Bit Set Ws<br>Write C bit to Ws <wb></wb> | 1             | 1              | None                     |

| 8               | BSW                  | BSW.C      |                   |                                           |               |                | None                     |

## TABLE 21-2: INSTRUCTION SET OVERVIEW

# 22.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

## 22.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- · A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- · Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

| АС СНА       | RACTERI | STICS (unles                      | ard Operating<br>s otherwise<br>ting temperat | <b>stated)</b><br>ure -40° | °C ≤Ta ≤+8          | 5°C for | Industrial<br>r Extended          |

|--------------|---------|-----------------------------------|-----------------------------------------------|----------------------------|---------------------|---------|-----------------------------------|

| Param<br>No. | Symbol  | Characteristic <sup>(1)</sup>     | Min                                           | Тур <sup>(2)</sup>         | Max                 | Units   | Conditions                        |

| OS50         | Fplli   | PLL Input Frequency Range         |                                               | _                          | 10                  | MHz     | EC with 4x PLL                    |

|              |         |                                   | 4                                             | -                          | 10                  | MHz     | EC with 8x PLL                    |

|              |         |                                   | 4                                             | -                          | 7.5 <sup>(4)</sup>  | MHz     | EC with 16x PLL                   |

|              |         |                                   | 4                                             | -                          | 10                  | MHz     | XT with 4x PLL                    |

|              |         |                                   | 4                                             | -                          | 10                  | MHz     | XT with 8x PLL                    |

|              |         |                                   | 4                                             | —                          | 7.5 <sup>(4)</sup>  | MHz     | XT with 16x PLL                   |

|              |         |                                   | 5 <sup>(3)</sup>                              | —                          | 10                  | MHz     | HS/2 with 4x PLL                  |

|              |         |                                   | 5 <sup>(3)</sup>                              | —                          | 10                  | MHz     | HS/2 with 8x PLL                  |

|              |         |                                   | 5 <sup>(3)</sup>                              | —                          | 7.5 <sup>(4)</sup>  | MHz     | HS/2 with 16x PLL                 |

|              |         |                                   | 4                                             | —                          | 8.33 <sup>(3)</sup> | MHz     | HS/3 with 4x PLL                  |

|              |         |                                   | 4                                             | —                          | 8.33 <sup>(3)</sup> | MHz     | HS/3 with 8x PLL                  |

|              |         |                                   | 4                                             | -                          | 7.5 <sup>(4)</sup>  | MHz     | HS/3 with 16x PLL                 |

| OS51         | Fsys    | On-Chip PLL Output <sup>(2)</sup> | 16                                            |                            | 120                 | MHz     | EC, XT, HS/2, HS/3 modes with PLL |

| OS52         | TLOC    | PLL Start-up Time (Lock Tim       | e) —                                          | 20                         | 50                  | μs      |                                   |

#### TABLE 23-15: PLL CLOCK TIMING SPECIFICATIONS (VDD = 2.5 TO 5.5 V)

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** Limited by oscillator frequency range.

- 4: Limited by device operating frequency range.

### TABLE 23-16: PLL JITTER

| AC CHAI      | RACTERISTICS   | (unless | Standard Operating Conditions: 2.5V to 5.5V     (unless otherwise stated)     Operating temperature   -40°C ≤TA ≤+85°C for Industrial     -40°C ≤TA ≤+125°C for Extended |       |       |                   |                   |  |  |  |  |  |

|--------------|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------------------|-------------------|--|--|--|--|--|

| Param<br>No. | Characteristic | Min     | Typ <sup>(1)</sup>                                                                                                                                                       | Max   | Units | Condi             | tions             |  |  |  |  |  |

| OS61         | x4 PLL         | —       | 0.251                                                                                                                                                                    | 0.413 | %     | -40°C ≤TA ≤+85°C  | VDD = 3.0 to 3.6V |  |  |  |  |  |

|              |                |         | 0.251                                                                                                                                                                    | 0.413 | %     | -40°C ≤TA ≤+125°C | VDD = 3.0 to 3.6V |  |  |  |  |  |

|              |                |         | 0.256                                                                                                                                                                    | 0.47  | %     | -40°C ≤TA ≤+85°C  | VDD = 4.5 to 5.5V |  |  |  |  |  |

|              |                |         | 0.256                                                                                                                                                                    | 0.47  | %     | -40°C ≤TA ≤+125°C | VDD = 4.5 to 5.5V |  |  |  |  |  |

|              | x8 PLL         | _       | 0.355                                                                                                                                                                    | 0.584 | %     | -40°C ≤TA ≤+85°C  | VDD = 3.0 to 3.6V |  |  |  |  |  |

|              |                | _       | 0.355                                                                                                                                                                    | 0.584 | %     | -40°C ≤TA ≤+125°C | VDD = 3.0 to 3.6V |  |  |  |  |  |

|              |                | —       | 0.362                                                                                                                                                                    | 0.664 | %     | -40°C ≤TA ≤+85°C  | VDD = 4.5 to 5.5V |  |  |  |  |  |

|              |                | _       | 0.362                                                                                                                                                                    | 0.664 | %     | -40°C ≤TA ≤+125°C | VDD = 4.5 to 5.5V |  |  |  |  |  |

|              | x16 PLL        |         | 0.67                                                                                                                                                                     | 0.92  | %     | -40°C ≤TA ≤+85°C  | VDD = 3.0 to 3.6V |  |  |  |  |  |

|              |                |         | 0.632                                                                                                                                                                    | 0.956 | %     | -40°C ≤TA ≤+85°C  | VDD = 4.5 to 5.5V |  |  |  |  |  |

|              |                | _       | 0.632                                                                                                                                                                    | 0.956 | %     | -40°C ≤TA ≤+125°C | VDD = 4.5 to 5.5V |  |  |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

### TABLE 23-21: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET TIMING REQUIREMENTS

| АС СНА       | RACTER                  | ISTICS                                                      | Standard Operating Conditions: 2.5V to 5.5V     (unless otherwise stated)     Operating temperature   -40°C ≤TA ≤+85°C for Industria     -40°C ≤TA ≤+125°C for Extended |                    |                   | ⊴+85°C for Industrial |                                                  |

|--------------|-------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|-----------------------|--------------------------------------------------|

| Param<br>No. | Symbol                  | Characteristic <sup>(1)</sup>                               | Min                                                                                                                                                                     | Тур <sup>(2)</sup> | Мах               | Units                 | Conditions                                       |

| SY10         | TmcL                    | MCLR Pulse Width (low)                                      | 2                                                                                                                                                                       | _                  | _                 | μs                    | -40°C to +85°C                                   |

| SY11         | TPWRT                   | Power-up Timer Period                                       | 2<br>8<br>32                                                                                                                                                            | 4<br>16<br>64      | 6<br>24<br>96     | ms                    | -40°C to +85°C, VDD =<br>5V<br>User programmable |

| SY12         | TPOR                    | Power-on Reset Delay <sup>(3)</sup>                         | 3                                                                                                                                                                       | 10                 | 30                | μs                    | -40°C to +85°C                                   |

| SY13         | Tioz                    | I/O high-impedance from MCLR<br>Low or Watchdog Timer Reset | —                                                                                                                                                                       | 0.8                | 1.0               | μs                    |                                                  |

| SY20         | Twdt1<br>Twdt2<br>Twdt3 | Watchdog Timer Time-out Period<br>(No Prescaler)            | 0.6<br>0.8<br>1.0                                                                                                                                                       | 2.0<br>2.0<br>2.0  | 3.4<br>3.2<br>3.0 | ms<br>ms<br>ms        | VDD = 2.5V<br>VDD = 3.3V, ±10%<br>VDD = 5V, ±10% |

| SY25         | TBOR                    | Brown-out Reset Pulse Width <sup>(4)</sup>                  | 100                                                                                                                                                                     |                    | _                 | μs                    | Vdd ⊴Vbor (D034)                                 |

| SY30         | Tost                    | Oscillation Start-up Timer Period                           | —                                                                                                                                                                       | 1024 Tosc          | _                 | _                     | Tosc = OSC1 period                               |

| SY35         | TFSCM                   | Fail-Safe Clock Monitor Delay                               | _                                                                                                                                                                       | 500                | 900               | μs                    | -40°C to +85°C                                   |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ" column is at 5V, 25°C unless otherwise stated.

3: Characterized by design but not tested

4: Refer to Figure 23-2 and Table 23-11 for BOR.

## TABLE 23-35: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA       | RACTER  | ISTICS           |                           | (unless otherwise  | Standard Operating Conditions: 2.5V to 5.5V     (unless otherwise stated)     Operating temperature   -40°C ≤TA ≤+85°C for Industrial     -40°C ≤TA ≤+125°C for Extended |       |                        |  |  |  |  |

|--------------|---------|------------------|---------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------|--|--|--|--|

| Param<br>No. | Symbol  | Charac           | teristic                  | Min <sup>(1)</sup> | Max                                                                                                                                                                      | Units | Conditions             |  |  |  |  |

| IM10         | TLO:SCL | Clock Low Time   | 100 kHz mode              | Tcy / 2 (BRG + 1)  | —                                                                                                                                                                        | μs    |                        |  |  |  |  |

|              |         |                  | 400 kHz mode              | TCY / 2 (BRG + 1)  | _                                                                                                                                                                        | μs    |                        |  |  |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY / 2 (BRG + 1)  | —                                                                                                                                                                        | μs    |                        |  |  |  |  |

| IM11         | THI:SCL | Clock High Time  | 100 kHz mode              | Tcy / 2 (BRG + 1)  | —                                                                                                                                                                        | μs    |                        |  |  |  |  |

|              |         |                  | 400 kHz mode              | Tcy / 2 (BRG + 1)  | —                                                                                                                                                                        | μs    |                        |  |  |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY / 2 (BRG + 1)  | —                                                                                                                                                                        | μs    |                        |  |  |  |  |

| IM20         | TF:SCL  | SDA and SCL      | 100 kHz mode              | —                  | 300                                                                                                                                                                      | ns    | CB is specified to be  |  |  |  |  |

|              |         | Fall Time        | 400 kHz mode              | 20 + 0.1 Св        | 300                                                                                                                                                                      | ns    | from 10 to 400 pF      |  |  |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                  | 100                                                                                                                                                                      | ns    |                        |  |  |  |  |

| IM21         | TR:SCL  | SDA and SCL      | 100 kHz mode              | _                  | 1000                                                                                                                                                                     | ns    | CB is specified to be  |  |  |  |  |

|              |         | Rise Time        | 400 kHz mode              | 20 + 0.1 Св        | 300                                                                                                                                                                      | ns    | from 10 to 400 pF      |  |  |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                  | 300                                                                                                                                                                      | ns    |                        |  |  |  |  |

| IM25         | TSU:DAT | Data Input       | 100 kHz mode              | 250                | _                                                                                                                                                                        | ns    |                        |  |  |  |  |

|              |         | Setup Time       | 400 kHz mode              | 100                | —                                                                                                                                                                        | ns    |                        |  |  |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                  | _                                                                                                                                                                        | ns    |                        |  |  |  |  |

| IM26         | THD:DAT | Data Input       | 100 kHz mode              | 0                  | _                                                                                                                                                                        | ns    |                        |  |  |  |  |

|              |         | Hold Time        | 400 kHz mode              | 0                  | 0.9                                                                                                                                                                      | μs    |                        |  |  |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                  | _                                                                                                                                                                        | ns    |                        |  |  |  |  |

| IM30         | TSU:STA | Start Condition  | 100 kHz mode              | Tcy / 2 (BRG + 1)  | —                                                                                                                                                                        | μs    | Only relevant for      |  |  |  |  |

|              |         | Setup Time       | 400 kHz mode              | Tcy / 2 (BRG + 1)  | —                                                                                                                                                                        | μs    | repeated Start         |  |  |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY / 2 (BRG + 1)  | _                                                                                                                                                                        | μs    | condition              |  |  |  |  |