Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 30 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | AC'97, Brown-out Detect/Reset, I <sup>2</sup> S, LVD, POR, PWM, WDT             |

| Number of I/O              | 52                                                                              |

| Program Memory Size        | 144KB (48K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 4K x 8                                                                          |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

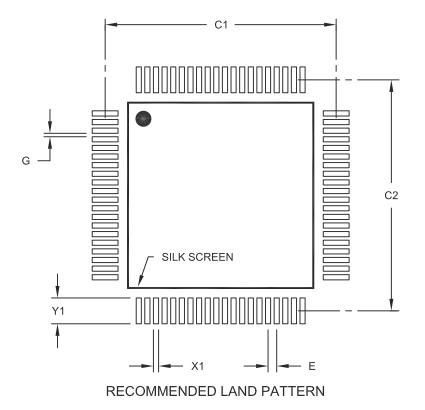

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6012at-30i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 CPU ARCHITECTURE OVERVIEW

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

### 2.1 Core Overview

This section contains a brief overview of the CPU architecture of the dsPIC30F. For additional hardware and programming information, please refer to the "*dsPIC30F Family Reference Manual*" (DS70046) and the "*16-bit MCU and DSC Programmer*'s *Reference Manual*" (DS70157), respectively.

The core has a 24-bit instruction word. The Program Counter (PC) is 23-bits wide with the Least Significant bit (LSb) always clear (refer to **Section 3.1 "Program Address Space"**), and the Most Significant bit (MSb) is ignored during normal program execution, except for certain specialized instructions. Thus, the PC can address up to 4M instruction words of user program space. An instruction prefetch mechanism is used to help maintain throughput. Program loop constructs, free from loop count management overhead, are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The working register array consists of 16 x 16-bit registers, each of which can act as data, address or offset registers. One working register (W15) operates as a software Stack Pointer for interrupts and calls.

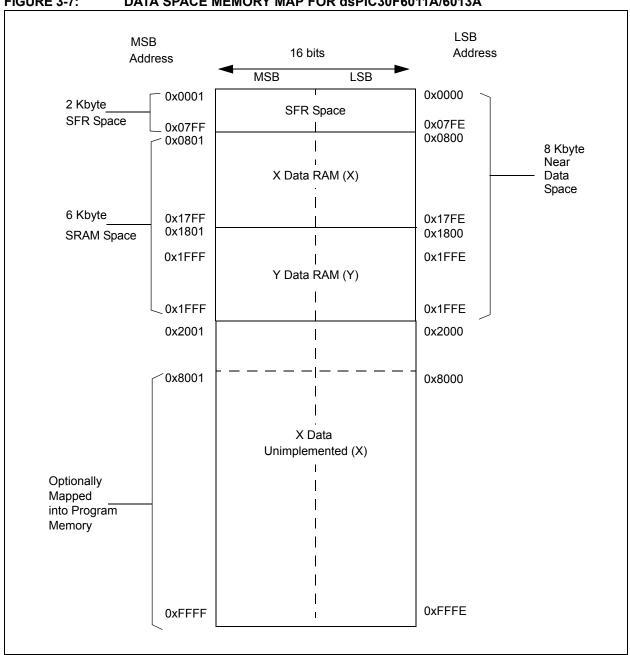

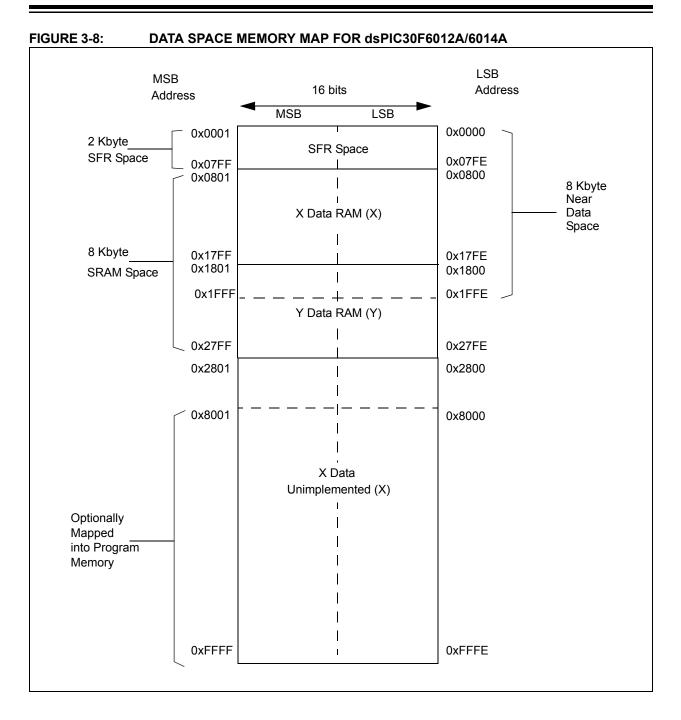

The data space is 64 Kbytes (32K words) and is split into two blocks, referred to as X and Y data memory. Each block has its own independent Address Generation Unit (AGU). Most instructions operate solely through the X memory, AGU, which provides the appearance of a single unified data space. The Multiply-Accumulate (MAC) class of dual source DSP instructions operate through both the X and Y AGUs, splitting the data address space into two parts (see **Section 3.2 "Data Address Space"**). The X and Y data space boundary is device specific and cannot be altered by the user. Each data word consists of 2 bytes, and most instructions can address data either as words or bytes. There are two methods of accessing data stored in program memory:

- The upper 32 Kbytes of data space memory can be mapped into the lower half (user space) of program space at any 16K program word boundary, defined by the 8-bit Program Space Visibility Page (PSVPAG) register. This lets any instruction access program space as if it were data space, with a limitation that the access requires an additional cycle. Moreover, only the lower 16 bits of each instruction word can be accessed using this method.

- Linear indirect access of 32K word pages within program space is also possible using any working register, via table read and write instructions.

Table read and write instructions can be used to access all 24 bits of an instruction word.

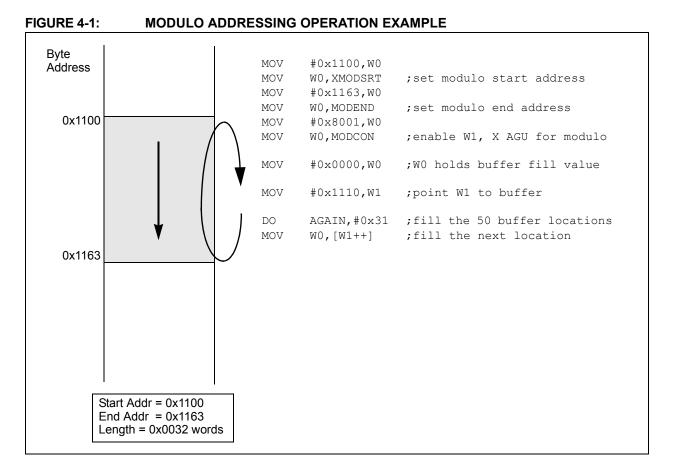

Overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. This is primarily intended to remove the loop overhead for DSP algorithms.

The X AGU also supports Bit-Reversed Addressing on destination effective addresses to greatly simplify input or output data reordering for radix-2 FFT algorithms. Refer to **Section 4.0 "Address Generator Units"** for details on modulo and Bit-Reversed Addressing.

The core supports Inherent (no operand), Relative, Literal, Memory Direct, Register Direct, Register Indirect, Register Offset and Literal Offset Addressing modes. Instructions are associated with predefined addressing modes, depending upon their functional requirements.

For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, 3-operand instructions are supported, allowing C = A + B operations to be executed in a single cycle.

A DSP engine has been included to significantly enhance the core arithmetic capability and throughput. It features a high-speed 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. Data in the accumulator or any working register can be shifted up to 16 bits right, or 16 bits left in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC class of instructions can concurrently fetch two data operands from memory while multiplying two W registers. To enable this concurrent fetching of data operands, the data space has been split for these instructions and linear for all others. This has been achieved in a transparent and flexible manner, by dedicating certain working registers to each address space for the MAC class of instructions.

### 3.0 MEMORY ORGANIZATION

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

### 3.1 Program Address Space

The program address space is 4M instruction words. It is addressable by a 24-bit value from either the 23-bit PC, table instruction Effective Address (EA), or data space EA, when program space is mapped into data space as defined by Table 3-1. Note that the program space address is incremented by two between successive program words in order to provide compatibility with data space addressing. User program space access is restricted to the lower 4M instruction word address range (0x000000 to 0x7FFFFE) for all accesses other than TBLRD/TBLWT, which use TBLPAG<7> to determine user or configuration space access. In Table 3-1, Program Space Address Construction, bit 23 allows access to the Device ID, the Unit ID and the configuration bits. Otherwise, bit 23 is always clear.

Note: The address map shown in Figure 3-1 and Figure 3-2 is conceptual, and the actual memory configuration may vary across individual devices depending on available memory.

# dsPIC30F6011A/6012A/6013A/6014A

### FIGURE 3-7: DATA SPACE MEMORY MAP FOR dsPIC30F6011A/6013A

# dsPIC30F6011A/6012A/6013A/6014A

### 4.2.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and an ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT, YMODEND (see Table 3-3).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

### 4.2.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register MODCON<15:0> contains enable flags as well as a W register field to specify the W address registers. The XWM and YWM fields select which registers will operate with Modulo Addressing. If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled. Similarly, if YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 3-3). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

#### 4.2.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address calculation associated with any W register. It is important to realize that the address boundaries check for addresses less than, or greater than the upper (for incrementing buffers), and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes may, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (e.g., [W7+W2]) is used, modulo address correction is performed but the contents of the register remain unchanged.

### 4.3 Bit-Reversed Addressing

Bit-Reversed Addressing is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which may be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

### 4.3.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing is enabled when:

- 1. BWM (W register selection) in the MODCON register is any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing) **and**

- 2. the BREN bit is set in the XBREV register and

- 3. the Addressing mode used is Register Indirect with Pre-Increment or Post-Increment.

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, then the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the bit-reversed address modifier or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing will only be executed for register indirect with pre-increment or post-increment addressing and word sized data writes. It will not function for any other addressing mode or for byte sized data, and normal addresses will be generated instead. When Bit-Reversed Addressing is active, the W address pointer will always be added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode will be ignored. In addition, as word sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed            |

|-------|-----------------------------------------------|

|       | Addressing should not be enabled              |

|       | together. In the event that the user          |

|       | attempts to do this, Bit-Reversed Address-    |

|       | ing will assume priority when active for the  |

|       | X WAGU, and X WAGU Modulo Address-            |

|       | ing will be disabled. However, Modulo         |

|       | Addressing will continue to function in the X |

|       | RAGU.                                         |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, then a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the bit-reversed pointer.

NVM REGISTER MAP<sup>(1)</sup> **TABLE 6-1**:

| File Name Addr.    | Addr.                        | Bit 15                       | Bit 14                   | Bit 15 Bit 14 Bit 13 Bit 12 Bi                                                                                                                                           | Bit 12                | Bit 11         | sit 11 Bit 10 Bit 9 Bit 8 Bit 7 | Bit 9    | Bit 8      | Bit 7        | Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 | Bit 5 | Bit 4    | Bit 3         | Bit 2 | Bit 1 | Bit 0 | AII RESETS          |

|--------------------|------------------------------|------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|---------------------------------|----------|------------|--------------|-------------------------------------------|-------|----------|---------------|-------|-------|-------|---------------------|

| NVMCON             | 0260                         | WR                           | WREN                     | WRERR                                                                                                                                                                    | Ι                     | I              | 1                               | - TWRI   | TWRI       | I            |                                           |       | PR(      | PROGOP<6:0>   | 6     |       |       | 0000 0000 0000 0000 |

| NVMADR             | 0762                         |                              |                          |                                                                                                                                                                          |                       |                |                                 | z        | VMADF      | NVMADR<15:0> |                                           |       |          |               |       |       |       | nnnn nnnn nnnn nnnn |

| NVMADRU 0764       | 0764                         | -                            | -                        | Ι                                                                                                                                                                        |                       | Ι              |                                 | I        |            |              |                                           |       | VMADF    | NVMADR<23:16> |       |       |       | 0000 0000 nnnn nnnn |

| NVMKEY             | 0766                         | -                            | -                        | Ι                                                                                                                                                                        |                       | Ι              |                                 | I        |            |              |                                           |       | KEY<7:0> | <7:0>         |       |       |       | 0000 0000 0000 0000 |

| Legend:<br>Note 1: | u = uninitis<br>Refer to the | alized bit; —<br>s "dsPIC30F | = unimpler<br>Family Ret | u = uninitialized bit; — = unimplemented bit, read as '0'<br>Refer to the " <i>dsPIC30F Family Reference Manual</i> " (DS70046) for descriptions of register bit fields. | ead as 'c<br>ual" (DS | ,<br>70046) f( | or descri                       | ptions o | of registe | er bit field | s.                                        |       |          |               |       |       |       |                     |

| SFR Name Addr. Bit 15 |   |          |          |          |        |        |        |          |           |                                     |        |       |        |       |          |       |                     |

|-----------------------|---|----------|----------|----------|--------|--------|--------|----------|-----------|-------------------------------------|--------|-------|--------|-------|----------|-------|---------------------|

| 0010                  |   | Bit 14 B | Bit 13 E | Bit 12 E | Bit 11 | Bit 10 | Bit 9  | Bit 8    | Bit 7     | Bit 6                               | Bit 5  | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | Reset State         |

| 0180                  |   |          |          |          |        |        | Output | Compare  | 1 Secon   | Output Compare 1 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 0182                  |   |          |          |          |        |        | Out    | out Comp | are 1 Ma  | Output Compare 1 Main Register      | _      |       |        |       |          |       | 0000 0000 0000 0000 |

| 0184 —                |   | 0        | OCSIDL   |          |        | 1      | 1      |          | Ι         | I                                   | I      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 0186                  |   |          |          |          |        |        | Output | Compare  | 2 Secon   | Output Compare 2 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 0188                  |   |          |          |          |        |        | Out    | out Comp | are 2 Ma  | Output Compare 2 Main Register      | _      |       |        |       |          |       | 0000 0000 0000 0000 |

| 018A —                |   | 0        | OCSIDL   |          |        | 1      | 1      |          | Ι         | I                                   | I      | OCFLT | OCTSE  |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 018C                  |   |          |          |          |        |        | Output | Compare  | 3 Secon   | Output Compare 3 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 018E                  |   |          |          |          |        |        | Out    | out Comp | are 3 Mai | Output Compare 3 Main Register      | L      |       |        |       |          |       | 0000 0000 0000 0000 |

| 0190 —                |   |          | OCSIDL   |          |        | 1      |        | I        | I         | I                                   | I      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 0192                  |   |          |          |          |        |        | Output | Compare  | 4 Secon   | Output Compare 4 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 0194                  |   |          |          |          |        |        | Out    | out Comp | are 4 Ma  | Output Compare 4 Main Register      |        |       |        |       |          |       | 0000 0000 0000 0000 |

| 0196 —                |   | 00       | OCSIDL   |          |        | 1      | 1      |          | Ι         | I                                   | I      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 0198                  |   |          |          |          |        |        | Output | Compare  | 5 Secon   | Output Compare 5 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 019A                  |   |          |          |          |        |        | Out    | out Comp | are 5 Mai | Output Compare 5 Main Register      |        |       |        |       |          |       | 0000 0000 0000 0000 |

| 019C —                |   | 00       | OCSIDL   |          |        | 1      |        |          | Ι         |                                     | -      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 019E                  |   |          |          |          |        |        | Output | Compare  | 6 Secon   | Output Compare 6 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 01A0                  |   |          |          |          |        |        | Out    | out Comp | are 6 Mai | Output Compare 6 Main Register      | _      |       |        |       |          |       | 0000 0000 0000 0000 |

| 01A2 —                |   |          | OCSIDL   |          |        |        |        |          | Ι         |                                     | Ι      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 01A4                  |   |          |          |          |        |        | Output | Compare  | 7 Secon   | Output Compare 7 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 01A6                  |   |          |          |          |        |        | Out    | out Comp | are 7 Mai | Output Compare 7 Main Register      |        |       |        |       |          |       | 0000 0000 0000 0000 |

| 01A8 —                |   | 00       | OCSIDL   |          |        | 1      |        |          | Ι         |                                     | -      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 01AA                  |   |          |          |          |        |        | Output | Compare  | 8 Secon   | Output Compare 8 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 01AC                  |   |          |          |          |        |        | Out    | out Comp | are 8 Ma  | Output Compare 8 Main Register      | -<br>- |       |        |       |          |       | 0000 0000 0000 0000 |

| 01AE                  | I | 00       | OCSIDL   |          |        |        |        | I        | Ι         | Ι                                   | -      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

### 14.3 Slave Select Synchronization

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be configured in SPI Slave mode with  $\overline{SSx}$  pin control enabled (SSEN = 1). When the  $\overline{SSx}$  pin is low, transmission and reception are enabled and the SDOx pin is driven. When  $\overline{SSx}$  pin goes high, the SDOx pin is no longer driven. Also, the SPI module is resynchronized, and all counters/control circuitry are reset. Therefore, when the  $\overline{SSx}$  pin is asserted low again, transmission/reception will begin at the MSb even if  $\overline{SSx}$  had been deasserted in the middle of a transmit/receive.

### 14.4 SPI Operation During CPU Sleep Mode

During Sleep mode, the SPI module is shutdown. If the CPU enters Sleep mode while an SPI transaction is in progress, then the transmission and reception is aborted.

The transmitter and receiver will stop in Sleep mode. However, register contents are not affected by entering or exiting Sleep mode.

### 14.5 SPI Operation During CPU Idle Mode

When the device enters Idle mode, all clock sources remain functional. The SPISIDL bit (SPIxSTAT<13>) selects if the SPI module will stop or continue on Idle. If SPISIDL = 0, the module will continue to operate when the CPU enters Idle mode. If SPISIDL = 1, the module will stop when the CPU enters Idle mode.

|   | Ś        |  |

|---|----------|--|

|   | <u></u>  |  |

|   | Ψ        |  |

|   | ij       |  |

|   | -        |  |

|   | ä        |  |

|   | Bi       |  |

|   | ē        |  |

|   | Ĕ        |  |

|   | ŝ        |  |

|   | Ë        |  |

|   | Ë        |  |

|   | Ë        |  |

|   | SCI      |  |

|   | g        |  |

|   | ĩ        |  |

|   | 9        |  |

|   | ତ        |  |

|   | 2        |  |

|   | õ        |  |

|   | ŝ        |  |

|   | 9        |  |

|   | <u> </u> |  |

|   | пa       |  |

|   | Ĩ        |  |

|   | Ň        |  |

|   | Ð        |  |

|   | 2        |  |

|   | ē        |  |

|   | £,       |  |

|   | å        |  |

| • | ž        |  |

|   | Ē        |  |

|   | an       |  |

|   | Ľ,       |  |

|   | C30F     |  |

|   | IsPIC30  |  |

|   | Š        |  |

|   | ŝ        |  |

|   | ġ,       |  |

|   | ē        |  |

|   | the      |  |

|   | 9        |  |

|   | Ъ        |  |

|   | efe      |  |

|   | Ŕ        |  |

|   |          |  |

|   | ÷        |  |

|   | ~        |  |

|   |          |  |

Note

© 2011 Microchip Technology Inc.

| TABLE 17-1: |                      | SAN1 R                 | CAN1 REGISTER MAP <sup>(1)</sup> (CON                       | R MAP        | (1) (CC           |                               | ED)    |             |              |                                             |                                             |                          |                          |                                              |            |             |                |                     |

|-------------|----------------------|------------------------|-------------------------------------------------------------|--------------|-------------------|-------------------------------|--------|-------------|--------------|---------------------------------------------|---------------------------------------------|--------------------------|--------------------------|----------------------------------------------|------------|-------------|----------------|---------------------|

| SFR Name    | Addr                 | Bit 15                 | Bit 14                                                      | Bit 13       | Bit 12            |                               | Bit 10 | Bit 9       | Bit 8        | Bit 7                                       | Bit 6                                       | Bit 5                    | Bit 4                    | Bit 3                                        | Bit 2 B    | Bit 1 Bit 0 | 0              | Reset State         |

| C1TX1B1     | 0356                 |                        |                                                             | Trar         | Transmit Buffer 1 | er 1 Byte 1                   |        |             |              |                                             |                                             | Tran                     | Transmit Buffer 1 Byte 0 | r 1 Byte 0                                   |            |             | uuuu           | uuuu uuuu           |

| C1TX1B2     | 0358                 |                        |                                                             | Trar         | Transmit Buffer 1 | er 1 Byte 3                   |        |             |              |                                             |                                             | Tran;                    | Transmit Buffer 1 Byte 2 | r 1 Byte 2                                   |            |             | nnnn           | nnnn nnnn nnnn      |

| C1TX1B3     | 035A                 |                        |                                                             | Trar         | Transmit Buffer 1 | er 1 Byte 5                   |        |             |              |                                             |                                             | Tran;                    | Transmit Buffer 1 Byte 4 | r 1 Byte 4                                   |            |             | nnnn           | nnnn nnnn nnnn      |

| C1TX1B4     | 035C                 |                        |                                                             | Trar         | Transmit Buffer 1 | er 1 Byte 7                   |        |             |              |                                             |                                             | Tran                     | Transmit Buffer 1 Byte 6 | r 1 Byte 6                                   |            |             | nnnn           | nnnn nnnn nnnn      |

| C1TX1CON    | 035E                 | I                      | Ι                                                           | I            | Ι                 | I                             |        |             | I            | Ι                                           | TXABT                                       | TXABT TXLARB TXERR TXREQ | TXERR                    | TXREQ                                        |            | TXPRI<1:0>  |                | 0000 0000 0000 0000 |

| C1TX0SID    | 0360                 | Transr                 | Transmit Buffer 0 Standard Identifier <10:6>                | Standard Ic  | dentifier <       | 10:6>                         | I      |             |              | Tre                                         | Transmit Buffer 0 Standard Identifier <5:0> | fer 0 Stan               | dard Ident               | ifier <5:0>                                  | 5          | SRR TXIDE   |                | nnnn nnnn 000n nnnn |

| C1TX0EID    | 0362 Tr <sub>8</sub> | ansmit But             | 0362 Transmit Buffer 0 Extended Identifier <17:14>          | and Identifi | er <17:14:        |                               | Ι      | Ι           |              |                                             | Trans                                       | smit Buffe               | r 0 Extend               | Transmit Buffer 0 Extended Identifier <13:6> | r <13:6>   |             | nnnn           | nnnn nnnn 0000 nnnn |

| C1TX0DLC    | 0364                 | F                      | Transmit Buffer 0 Extended Identifier                       | fer 0 Exter  | Ided Ident        | ifier <5:0>                   |        | TXRTR       | TXRB1        | TXRB0                                       |                                             | DLC                      | DLC<3:0>                 |                                              | I          |             | nnnn           | 000n nnnn nnnn nnnn |

| C1TX0B1     | 0366                 |                        |                                                             | Trar         | Transmit Buffer 0 | er 0 Byte 1                   |        |             |              |                                             |                                             | Tran                     | Transmit Buffer 0 Byte 0 | r 0 Byte 0                                   |            |             | nnnn           | nnnn nnnn nnnn nnnn |

| C1TX0B2     | 0368                 |                        |                                                             | Trar         | Transmit Buffer 0 | er 0 Byte 3                   |        |             |              |                                             |                                             | Tran                     | Transmit Buffer 0 Byte 2 | r 0 Byte 2                                   |            |             | nnnn           | nnnn nnnn nnnn nnnn |

| C1TX0B3     | 036A                 |                        |                                                             | Trar         | Transmit Buffer 0 | er 0 Byte 5                   |        |             |              |                                             |                                             | Tran                     | Transmit Buffer 0 Byte 4 | r 0 Byte 4                                   |            |             | nnnn           | nnnn nnnn nnnn nnnn |

| C1TX0B4     | 036C                 |                        |                                                             | Trar         | Transmit Buffer 0 | er 0 Byte 7                   |        |             |              |                                             |                                             | Tran                     | Transmit Buffer 0 Byte 6 | r 0 Byte 6                                   |            |             | nnnn           | nnnn nnnn nnnn nnnn |

| C1TX0CON    | 036E                 |                        | Ι                                                           |              | Ι                 | I                             |        | Ι           |              | Ι                                           | TXABT                                       | TXLARB TXERR             | TXERR                    | TXREQ                                        | 1          | TXPRI<1:0>  |                | 0000 0000 0000 0000 |

| C1RX1SID    | 0370                 | I                      | Ι                                                           | Ι            |                   |                               |        | Rece        | ive Buffer   | Receive Buffer 1 Standard Identifier <10:0> | lentifier <1                                | <0:0                     |                          |                                              | 0          | SRR RXIDE   |                | nnnn nnnn nnnn n000 |

| C1RX1EID    | 0372                 |                        | Ι                                                           |              | Ι                 |                               |        |             | Ŗ            | Receive Buffer 1 Extended Identifier <17:6> | · 1 Extend∈                                 | ∋d Identifi∈             | sr <17:6>                |                                              |            |             | 0000           | nnnn nnnn nnnn 0000 |

| C1RX1DLC    | 0374                 |                        | Receive Buffer 1 Extended Identifier                        | fer 1 Exten  | ided Identi       | ifier <5:0>                   |        | RXRTR       | RXRB1        | I                                           | I                                           | I                        | <b>RXRB0</b>             |                                              | DLC<3:0>   |             | nnnn           | nnnn n000 nnnn nnnn |

| C1RX1B1     | 0376                 |                        |                                                             | Rec          | Receive Buffer 1  | er 1 Byte 1                   |        |             |              |                                             |                                             | Rect                     | Receive Buffer 1 Byte    | r 1 Byte 0                                   |            |             | nnnn           | nnnn nnnn nnnn      |

| C1RX1B2     | 0378                 |                        |                                                             | Rec          | Receive Buffer 1  | er 1 Byte 3                   |        |             |              |                                             |                                             | Rect                     | Receive Buffer 1 Byte 2  | r 1 Byte 2                                   |            |             | nnnn           | nnnn nnnn nnnn      |

| C1RX1B3     | 037A                 |                        |                                                             | Rec          | Receive Buffer 1  | er 1 Byte 5                   |        |             |              |                                             |                                             | Rect                     | Receive Buffer 1 Byte 4  | r 1 Byte 4                                   |            |             | nnnn           | nnnn nnnn nnnn      |

| C1RX1B4     | 037C                 |                        |                                                             | Rec          | Receive Buffer 1  | er 1 Byte 7                   |        |             |              |                                             |                                             | Rect                     | Receive Buffer 1 Byte 6  | r 1 Byte 6                                   |            |             | nnnn           | nnnn nnnn nnnn nnnn |

| C1RX1CON    | 037E                 |                        | Ι                                                           |              | Ι                 | Ι                             |        | Ι           |              | RXFUL                                       |                                             | Ι                        |                          | RXRTRRO                                      | FILF       | FILHIT<2:0> | 0000           | 0000 0000 0000 0000 |

| C1RX0SID    | 0380                 |                        | Ι                                                           | Ι            |                   |                               |        | Rece        | ive Buffer ( | Receive Buffer 0 Standard Identifier <10:0> | lentifier <1                                | <0:0                     |                          |                                              | 0          | SRR RXIDE   |                | nnnn nnnn nnnn n000 |

| C1RX0EID    | 0382                 |                        | Ι                                                           | Ι            | Ι                 |                               |        |             | Rŧ           | Receive Buffer 0 Extended Identifier <17:6> | . 0 Extend€                                 | ∋d Identifi€             | sr <17:6>                |                                              |            |             | 0000           | nnnn nnnn nnnn 0000 |

| C1RX0DLC    | 0384                 | -                      | Receive Buffer 0 Extended Identifier                        | fer 0 Exten  | ided Identi       | ifier <5:0>                   |        | RXRTR       | RXRTR RXRB1  | Ι                                           | I                                           | I                        | <b>RXRB0</b>             |                                              | DLC<3:0>   | •           | nnnn           | nnnn n000 nnnn nnnn |

| C1RX0B1     | 0386                 |                        |                                                             | Rec          | Receive Buffer 0  | er 0 Byte 1                   |        |             |              |                                             |                                             | Rect                     | Receive Buffer 0 Byte 0  | r 0 Byte 0                                   |            |             | nnnn           | nnnn nnnn nnnn nnnn |

| C1RX0B2     | 0388                 |                        |                                                             | Rec          | Receive Buffer 0  | er 0 Byte 3                   |        |             |              |                                             |                                             | Rect                     | Receive Buffer 0 Byte 2  | r 0 Byte 2                                   |            |             | nnnn           | nnnn nnnn nnnn nnnn |

| C1RX0B3     | 038A                 |                        |                                                             | Rec          | Receive Buffer 0  | er 0 Byte 5                   |        |             |              |                                             |                                             | Rect                     | Receive Buffer 0 Byte 4  | r 0 Byte 4                                   |            |             | nnnn           | nnnn nnnn nnnn nnnn |

| C1RX0B4     | 038C                 |                        |                                                             | Rec          | Receive Buffer 0  | er 0 Byte 7                   |        |             |              |                                             |                                             | Rect                     | Receive Buffer 0 Byte 6  | r 0 Byte 6                                   |            |             | nnnn           | nnnn nnnn nnnn nnnn |

| C1RX0CON    | 038E                 |                        | Ι                                                           | Ι            | Ι                 | I                             |        | Ι           | Ι            | RXFUL                                       | I                                           | Ι                        |                          | RXRTRRO DBEN JTOFF FILHITO                   | DBEN JI    | OFF FILHI   | <b>ΤΟ</b> 0000 | 0000 0000 0000      |

| C1CTRL      | 0390 C               | CANCAP                 | Ι                                                           | CSIDL        | ABAT              | CANCKS                        |        | REQOP<2:0>  | <0:          | ΛOD                                         | OPMODE<2:0>                                 | ^                        | 1                        | ICOI                                         | ICODE<2:0> |             | 0000           | 0100 1000 0000      |

| C1CFG1      | 0392                 |                        | Ι                                                           |              | I                 |                               |        | Ι           |              | SJW<1:0>                                    | 1:0>                                        |                          |                          | BRP<5:0>                                     | <0         |             | 0000           | 0000 0000 0000      |

| C1CFG2      | 0394                 |                        | WAKFIL                                                      | I            | I                 |                               | •      | SEG2PH<2:0> | -05          | <b>SEG2PHTS</b>                             | SAM                                         | St                       | SEG1PH<2:0>              | <0:                                          | PRS        | PRSEG<2:0>  | 0000           | Оиии ииии ииии      |

| C1INTF      | 0396 R               | <b>RX00VR</b>          | RX10VR                                                      | TXBO         | TXEP              | RXEP                          | TXWAR  | RXWAR       | RXWAR EWARN  | IVRIF                                       | WAKIF                                       | ERRIF                    | TX2IF                    | TX1IF                                        | TX0IF R    | RX1IF RX0IF | IF 0000        | 0000 0000 0000      |

| C1INTE      | 0398                 | Ι                      | Ι                                                           | Ι            | Ι                 | Ι                             | Ι      | Ι           | Ι            | IVRIE                                       | WAKIE                                       | ERRIE                    | TX2IE                    | TX1IE                                        | TX0IE R    | RX1E RX0IE  |                | 0000 0000 0000 0000 |

| C1EC        | 039A                 |                        |                                                             | Transn       | hit Error C       | Transmit Error Count Register | er     |             |              |                                             |                                             | Receive                  | e Error Co               | Receive Error Count Register                 | ir         |             | 0000           | 0000 0000 0000      |

| Legend:     | u = uniniti          | u = uninitialized bit; | $\frac{1}{2}$ — = unimplemented bit, read as $\frac{10}{2}$ | emented t    | bit, read as      | ,0, \$                        | <br>   |             |              | :                                           |                                             |                          |                          |                                              |            |             |                |                     |

# dsPIC30F6011A/6012A/6013A/6014A

DS70143E-page 119

| <b>TABLE 17-2</b> :  |                        | CAN2 R                                 | CAN2 REGISTER MAP <sup>(1)</sup> (CON                                                                                                                                  | R MAP <sup>()</sup>       | <sup>1)</sup> (co        | NTINUED                  | ED)          |             |                   |                                             |             |                                             |                          |                                              |            |             |              |                     |

|----------------------|------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|--------------------------|--------------|-------------|-------------------|---------------------------------------------|-------------|---------------------------------------------|--------------------------|----------------------------------------------|------------|-------------|--------------|---------------------|

| SFR Name             | Addr.                  | Bit 15                                 | Bit 14                                                                                                                                                                 | Bit 13                    | Bit 12                   |                          | Bit 10       | Bit 9       | Bit 8             | Bit 7                                       | Bit 6       | Bit 5                                       | Bit 4                    | Bit 3                                        | Bit 2 E    | Bit 1 E     | Bit 0        | Reset State         |

| C2TX1B1              | 0416                   |                                        |                                                                                                                                                                        | Transı                    | Transmit Buffer 1        | r 1 Byte 1               |              |             |                   |                                             |             | Trans                                       | Transmit Buffer 1 Byte 0 | 1 Byte 0                                     |            |             | 2            | uuuu uuuu uuuu      |

| C2TX1B2              | 0418                   |                                        |                                                                                                                                                                        | Transı                    | Transmit Buffer 1        | r 1 Byte 3               |              |             |                   |                                             |             | Trans                                       | Transmit Buffer 1 Byte 2 | 1 Byte 2                                     |            |             | r.           | uuuu uuuu uuuu      |

| C2TX1B3              | 041A                   |                                        |                                                                                                                                                                        | Transi                    | Transmit Buffer 1        | r 1 Byte 5               |              |             |                   |                                             |             | Trans                                       | Transmit Buffer 1 Byte 4 | 1 Byte 4                                     |            |             | n .          | uuuu uuuu uuuu      |

| C2TX1B4              | 041C                   |                                        |                                                                                                                                                                        | Transı                    | Transmit Buffer 1        | r 1 Byte 7               |              |             |                   |                                             |             | Trans                                       | Transmit Buffer 1 Byte 6 | 1 Byte 6                                     |            |             | 2            | uuuu uuuu uuuu      |

| C2TX1CON             | 041E                   | I                                      | Ι                                                                                                                                                                      | Ι                         | Ι                        | Ι                        | Ι            | Ι           | 1                 |                                             | TXABT       | TXLARB                                      | TXERR                    | TXREQ                                        | Ι          | TXPRI<1:0>  |              | 0000 0000 0000 0000 |

| C2TX0SID             |                        | Transn                                 | Transmit Buffer 0 Standard Identifier <10:6>                                                                                                                           | tandard Id∈               | sntifier <'              | 10:6>                    | 1            | Ι           | Ι                 | Trai                                        | nsmit Buffe | Transmit Buffer 0 Standard Identifier <5:0> | ard Identi               | ier <5:0>                                    |            | SRR T       | TXIDE U      | uuuu uuuu 000n uuuu |

| C2TX0EID             | 0422 T                 | Transmit Buf                           | Transmit Buffer 0 Extended Identifier <17:14>                                                                                                                          | ed Identifier             | <17:14>                  | Ι                        |              |             | Ι                 |                                             | Trans       | mit Buffer                                  | 0 Extend                 | Transmit Buffer 0 Extended Identifier <13:6> | <13:6>     |             | 2            | uuuu 0000 uuuu      |

| C2TX0DLC             | 0424                   | Ē                                      | Transmit Buffer 0 Extended Identifier                                                                                                                                  | er 0 Extend               | ed Identi                | fier <5:0>               |              | TXRTR       | TXRB1             | TXRB0                                       |             | DLC                                         | DLC<3:0>                 |                                              |            |             | 1            | uuuu uuuu u000      |

| C2TX0B1              | 0426                   |                                        |                                                                                                                                                                        | Transı                    | Transmit Buffer 0        | r 0 Byte 1               |              |             |                   |                                             |             | Trans                                       | Transmit Buffer 0 Byte 0 | 0 Byte 0                                     |            |             | 2            | uuuu uuuu uuuu      |

| C2TX0B2              | 0428                   |                                        |                                                                                                                                                                        | Transı                    | Transmit Buffer 0        | r 0 Byte 3               |              |             |                   |                                             |             | Trans                                       | Transmit Buffer 0 Byte 2 | 0 Byte 2                                     |            |             | 2            | uuuu uuuu uuuu      |

| C2TX0B3              | 042A                   |                                        |                                                                                                                                                                        | Transı                    | Transmit Buffer 0        | r 0 Byte 5               |              |             |                   |                                             |             | Trans                                       | Transmit Buffer 0 Byte 4 | 0 Byte 4                                     |            |             | 2            | uuuu uuuu uuuu      |

| C2TX0B4              | 042C                   |                                        |                                                                                                                                                                        | Transı                    | mit Buffe                | Transmit Buffer 0 Byte 7 |              |             |                   |                                             |             | Trans                                       | Transmit Buffer 0 Byte 6 | 0 Byte 6                                     |            |             | 2            | uuuu uuuu uuuu      |

| C2TX0CON             | 042E                   | I                                      | Ι                                                                                                                                                                      | Ι                         | Ι                        | Ι                        | Ι            | Ι           | Ι                 | 1                                           | TXABT       | TXLARB                                      | TXERR                    | TXREQ                                        | Ι          | TXPRI<1:0>  |              | 0000 0000 0000 0000 |

| C2RX1SID             | 0430                   | I                                      | Ι                                                                                                                                                                      | Ι                         |                          |                          |              | Rece        | ive Buffer        | Receive Buffer 1 Standard Identifier <10:0> | dentifier < | 10:0>                                       |                          |                                              |            | SRR R       | <b>RXIDE</b> | 000u uuuu uuuu      |

| C2RX1EID             | 0432                   | I                                      | Ι                                                                                                                                                                      | 1                         | Ι                        |                          |              |             | Ŕ                 | Receive Buffer 1 Extended Identifier <17:6> | 1 Extend∈   | sd Identifie                                | r <17:6>                 |                                              |            |             | 0            | 0000 nnnn nnnn 0000 |

| C2RX1DLC             | 0434                   | Ľ                                      | Receive Buffer 1 Extended Identifier                                                                                                                                   | sr 1 Extend               | ed Identii               | fier <5:0>               |              | RXRTR       | RXRTR RXRB1       | 1                                           | Ι           |                                             | <b>RXRB0</b>             |                                              | DLC<3:0>   | Δ           | 2            | uuuu u000 uuuu uuuu |

| C2RX1B1              | 0436                   |                                        |                                                                                                                                                                        | Recei                     | Receive Buffer 1         |                          |              |             |                   |                                             |             | Rece                                        | Receive Buffer 1 Byte 0  | 1 Byte 0                                     |            |             | 2            | uuuu uuuu uuuu      |

| C2RX1B2              | 0438                   |                                        |                                                                                                                                                                        | Recei                     | Receive Buffer           | r 1 Byte 3               |              |             |                   |                                             |             | Rece                                        | Receive Buffer 1 Byte 2  | 1 Byte 2                                     |            |             | Ω            | uuuu uuuu uuuu      |

| C2RX1B3              | 043A                   |                                        |                                                                                                                                                                        | Recei                     | Receive Buffer           | r 1 Byte 5               |              |             |                   |                                             |             | Rece                                        | Receive Buffer 1 Byte 4  | 1 Byte 4                                     |            |             | n l          | uuuu uuuu uuuu      |

| C2RX1B4              | 043C                   |                                        |                                                                                                                                                                        | Recei                     | Receive Buffer           | r 1 Byte 7               |              |             |                   |                                             |             | Rece                                        | Receive Buffer 1 Byte 6  | 1 Byte 6                                     |            |             | n.           | uuuu uuuu uuuu      |

| C2RX1CON             | 043E                   | I                                      | Ι                                                                                                                                                                      | Ι                         | Ι                        | Ι                        | I            | Ι           | Ι                 | RXFUL                                       | 1           | 1                                           |                          | RXRTRRO                                      | FILI       | FILHIT<2:0> |              | 0000 0000 0000 0000 |

| <b>C2RX0SID</b>      | 0440                   | I                                      | Ι                                                                                                                                                                      | I                         |                          |                          |              | Rece        | ive Buffer        | Receive Buffer 0 Standard Identifier <10:0> | dentifier < | 10:0>                                       |                          |                                              |            | SRR R       | <b>RXIDE</b> | 000u uuuu uuuu      |

| <b>C2RX0EID</b>      | 0442                   | I                                      | Ι                                                                                                                                                                      | Ι                         | I                        |                          |              |             | Ŕ                 | Receive Buffer 0 Extended Identifier <17:6> | 0 Extende   | ed Identifie                                | r <17:6>                 |                                              |            |             | 0            | 0000 uuuu uuuu 0000 |

| C2RX0DLC             | 0444                   | œ                                      | Receive Buffer 0 Extended Identifier                                                                                                                                   | sr 0 Extend               | ed Identii               | fier <5:0>               |              | RXRTR       | RXRTR RXRB1       |                                             | Ι           |                                             | <b>RXRB0</b>             |                                              | DLC<3:0>   | ۸           | 2            | uuuu 0000 uuuu      |

| C2RX0B1              | 0446                   |                                        |                                                                                                                                                                        | Recei                     | Receive Buffer 0         | r 0 Byte 1               |              |             |                   |                                             |             | Rece                                        | Receive Buffer 0 Byte 0  | 0 Byte 0                                     |            |             | 2            | uuuu uuuu uuuu      |

| C2RX0B2              | 0448                   |                                        |                                                                                                                                                                        | Recei                     | Receive Buffer 0         | r 0 Byte 3               |              |             |                   |                                             |             | Rece                                        | Receive Buffer 0 Byte    | 0 Byte 2                                     |            |             | n.           | uuuu uuuu uuuu      |

| C2RX0B3              | 044A                   |                                        |                                                                                                                                                                        | Recei                     | Receive Buffer 0         | r 0 Byte 5               |              |             |                   |                                             |             | Rece                                        | Receive Buffer 0 Byte 4  | 0 Byte 4                                     |            |             | n.           | uuuu uuuu uuuu      |

| C2RX0B4              | 044C                   |                                        |                                                                                                                                                                        | Recei                     | Receive Buffer 0         | r 0 Byte 7               |              |             |                   |                                             |             | Rece                                        | Receive Buffer 0 Byte 6  | 0 Byte 6                                     |            |             | 2            | uuuu uuuu uuuu      |

| C2RX0CON             | 044E                   | I                                      | Ι                                                                                                                                                                      | I                         | I                        |                          | I            |             | I                 | RXFUL                                       | I           | I                                           | 1                        | RXRTRRO DBEN JTOFF                           | DBEN J     |             | FILHITO 0    | 0000 0000 0000 0000 |

| <b>C2CTRL</b>        | 0450                   | CANCAP                                 | Ι                                                                                                                                                                      | CSIDLE                    | ABAT                     | CANCKS                   |              | REQOP<2:0>  | <0                | OPM                                         | OPMODE<2:0> |                                             | 1                        | ICOD                                         | ICODE<2:0> |             | 1            | 0000 0100 1000 0000 |

| C2CFG1               | 0452                   | I                                      | Ι                                                                                                                                                                      | Ι                         |                          | Ι                        |              |             | Ι                 | SJW<1:0>                                    | ė.          |                                             |                          | BRP<5:0>                                     | ۸          |             | 0            | 0000 0000 0000 0000 |

| C2CFG2               | 0454                   | I                                      | WAKFIL                                                                                                                                                                 |                           |                          |                          | SE           | SEG2PH<2:0> | <0:               | <b>SEG2PHTS</b>                             |             | SE                                          | SEG1PH<2:0>              |                                              | PRS        | PRSEG<2:0>  |              | 0000 0uuu uuuu      |

| C2INTF               | 0456                   | <b>RX00VR</b>                          | RX10VR                                                                                                                                                                 | TXBO                      | TXEP                     | RXEP                     | TXWAR        | RXWAR       | TXWAR RXWAR EWARN | IVRIF                                       | WAKIF       |                                             | TX2IF                    | TX1IF                                        |            | RX1IF R     |              | 0000 0000 0000 0000 |

| C2INTE               | 0458                   | Ι                                      | Ι                                                                                                                                                                      |                           |                          |                          |              | Ι           |                   | IVRIE                                       | WAKIE       | ERRIE                                       | TX2IE                    | TX1IE <sup>-</sup>                           | TX0IE      | RX1E R      | <b>RX0IE</b> | 0000 0000 0000 0000 |

| C2EC                 | 045A                   |                                        |                                                                                                                                                                        | Transmit Error Count      | Error Cc                 | ount Register            | er           |             |                   |                                             |             | Receive                                     | Error Col                | Receive Error Count Register                 |            |             | 0            | 0000 0000 0000 0000 |

| Legend:<br>Note 1: F | u = unin<br>Refer to t | itialized bit;<br>the <i>"dsPIC3</i> , | u = uninitialized bit; — = unimplemented bit, read as '0'<br>Refer to the <i>"dsPIC30F Family Reference Manual"</i> (DS70046) for descriptions of register bit fields. | emented bit<br>eference M | t, read as<br>'anual" (D | \$ '0'<br>)S70046) f(    | or descripti | ons of re-  | aister bit fi     | elds.                                       |             |                                             |                          |                                              |            |             |              |                     |

|                      |                        |                                        |                                                                                                                                                                        |                           |                          |                          | ·            |             | Sicore 212        |                                             |             |                                             |                          |                                              |            |             |              |                     |

| ш        |

|----------|

|          |

| =        |

| <u> </u> |

| F        |

| 5        |

| 5        |

| Q        |

| C        |

| Ľ        |

|          |

| Ξ        |

| Δ        |

| Z        |

| 2        |

| 2        |

| ~        |

|          |

|          |

| H        |

| S        |

| G        |

|          |

| щ        |

| R        |

|          |

| 2        |

| z        |

| <        |

| Ó        |

| -        |

|          |

|          |

| Ņ        |

| <u>_</u> |

| ~        |

| ~        |

| 111      |

| <b>TABLE 18-2</b> : | 18-2: | DCI R  | EGISTE        | DCI REGISTER MAP <sup>(1)</sup>                                                                              | 1)     |           |        |                                 |                                |             |           |            |        |        |       |         |        |                            |

|---------------------|-------|--------|---------------|--------------------------------------------------------------------------------------------------------------|--------|-----------|--------|---------------------------------|--------------------------------|-------------|-----------|------------|--------|--------|-------|---------|--------|----------------------------|

| SFR Name            | Addr. | Bit 15 | Bit 14        | Bit 13                                                                                                       | Bit 12 | Bit 11    | Bit 10 | Bit 9                           | Bit 8                          | Bit 7       | Bit 6     | Bit 5      | Bit 4  | Bit 3  | Bit 2 | Bit 1   | Bit 0  | Reset State                |

| DCICON1             | 0240  | DCIEN  | I             | DCISIDL                                                                                                      | I      | DLOOP     | CSCKD  | CSCKE                           | COFSD                          | UNFM CSDOM  |           | DJST       | I      |        |       | COFSM1  | COFSM0 | COFSM0 0000 0000 0000 0000 |

| DCICON2             | 0242  | Ι      |               | Ι                                                                                                            | Ι      | BLEN1     | BLENO  | I                               |                                | COFSG<3:0>  | <3:0>     |            |        |        | ŝM    | WS<3:0> |        | 0000 0000 0000 0000        |

| DCICON3             | 0244  | Ι      |               | Ι                                                                                                            | Ι      |           |        |                                 |                                |             | BCG<11:0> | < <u>0</u> |        |        |       |         |        | 0000 0000 0000 0000        |

| DCISTAT             | 0246  | I      | 1             | Ι                                                                                                            | 1      | SLOT3     | SLOT2  | SLOT1                           | SLOT0                          |             | I         | I          | I      | ROV F  | RFUL  | TUNF    | тмртү  | 0000 0000 0000 0000        |

| TSCON               | 0248  | TSE15  | TSE14         | TSE13                                                                                                        | TSE12  | TSE11     | TSE10  | TSE9                            | TSE8                           | TSE7        | TSE6      | TSE5       | TSE4   | TSE3   | TSE2  | TSE1    | TSE0   | 0000 0000 0000 0000        |

| RSCON               | 024C  | RSE15  | RSE14         | RSE13                                                                                                        | RSE12  | RSE11     | RSE10  | RSE9                            | RSE8                           | RSE7        | RSE6      | RSE5       | RSE4 F | RSE3 F | RSE2  | RSE1    | RSE0   | 0000 0000 0000 0000        |

| <b>RXBUF0</b>       | 0250  |        |               |                                                                                                              |        |           |        | Receive B                       | Receive Buffer 0 Data Register | ta Regist∈  | ЭĽ        |            |        |        |       |         |        | 0000 0000 0000 0000        |

| RXBUF1              | 0252  |        |               |                                                                                                              |        |           |        | Receive B                       | Receive Buffer 1 Data Register | ta Regist∈  | ЭĽ        |            |        |        |       |         |        | 0000 0000 0000 0000        |

| <b>RXBUF2</b>       | 0254  |        |               |                                                                                                              |        |           |        | Receive B                       | Receive Buffer 2 Data Register | ta Regist∈  | ЭĽ        |            |        |        |       |         |        | 0000 0000 0000 0000        |

| <b>RXBUF3</b>       | 0256  |        |               |                                                                                                              |        |           |        | Receive B                       | Receive Buffer 3 Data Register | ta Regist∈  | ЭĽ        |            |        |        |       |         |        | 0000 0000 0000 0000        |

| <b>TXBUF0</b>       | 0258  |        |               |                                                                                                              |        |           |        | Transmit Buffer 0 Data Register | Suffer 0 Da                    | Ita Regist  | er        |            |        |        |       |         |        | 0000 0000 0000 0000        |

| TXBUF1              | 025A  |        |               |                                                                                                              |        |           |        | Transmit Buffer 1 Data Register | suffer 1 Da                    | ita Registi | er        |            |        |        |       |         |        | 0000 0000 0000 0000        |