Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20 MIPS                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 68                                                                             |

| Program Memory Size        | 132KB (44K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 2K x 8                                                                         |

| RAM Size                   | 6K x 8                                                                         |

| /oltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 16x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6013a-20e-pf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, Keeloq, Keeloq logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

@ 2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-60932-883-2

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002 ===

#### **Table of Contents**

| 1.0   | Device Overview                                           | 11  |

|-------|-----------------------------------------------------------|-----|

| 2.0   | CPU Architecture Overview                                 | 17  |

| 3.0   | Memory Organization                                       | 25  |

| 4.0   | Address Generator Units                                   | 39  |

| 5.0   | Interrupts                                                | 45  |

| 6.0   | Flash Program Memory                                      | 51  |

| 7.0   | Data EEPROM Memory                                        | 57  |

| 8.0   | I/O Ports                                                 | 61  |

| 9.0   | Timer1 Module                                             | 67  |

| 10.0  | Timer2/3 Module                                           | 71  |

|       | Timer4/5 Module                                           |     |

| 12.0  | Input Capture Module                                      | 81  |

| 13.0  | Output Compare Module                                     | 85  |

| 14.0  | SPI <sup>M</sup> Module                                   | 91  |

|       | I2C™ Module                                               |     |

| 16.0  | Universal Asynchronous Receiver Transmitter (UART) Module | 103 |

|       | CAN Module                                                |     |

| 18.0  | Data Converter Interface (DCI) Module                     | 123 |

| 19.0  | 12-bit Analog-to-Digital Converter (ADC) Module           | 133 |

| 20.0  | System Integration                                        | 143 |

| 21.0  | Instruction Set Summary                                   | 161 |

| 22.0  | Development Support                                       | 169 |

|       | Electrical Characteristics                                |     |

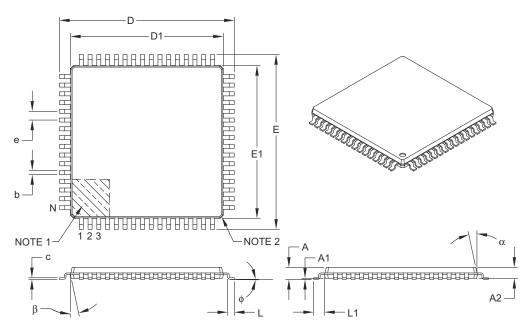

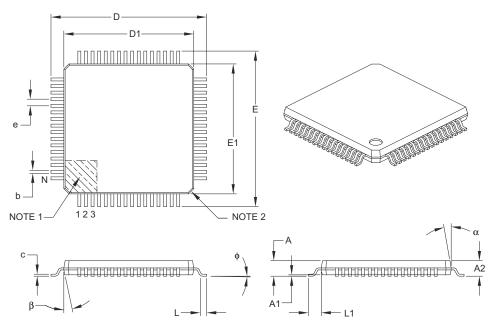

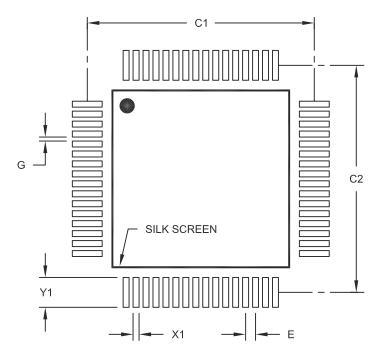

| 24.0  | Packaging Information                                     | 213 |

| Appe  | endix A: Revision History                                 | 223 |

|       | · · · · · · · · · · · · · · · · · · ·                     |     |

| The I | Microchip Web Site                                        | 231 |

| Custo | omer Change Notification Service                          | 231 |

| Custo | omer Support                                              | 231 |

| Read  | der Response                                              | 232 |

| Prod  | uct Identification System                                 | 233 |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. Should a misaligned read or write be attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed, whereas if it occurred on a write, the instruction will be executed but the write will not occur. In either case, a trap will then be executed, allowing the system and/or user to examine the machine state prior to execution of the address fault.

FIGURE 3-10: DATA ALIGNMENT

| ,    | 15 | MSB   | 8 | 7 | LSB    | 0 |      |

|------|----|-------|---|---|--------|---|------|

| 0001 |    | Byte1 |   |   | Byte 0 |   | 0000 |

| 0003 |    | Byte3 |   |   | Byte 2 |   | 0002 |

| 0005 |    | Byte5 |   |   | Byte 4 |   | 0004 |

|      |    |       |   | • |        |   |      |

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A sign-extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions, including the DSP instructions, operate only on words.

### 3.2.5 NEAR DATA SPACE

An 8 Kbyte 'near' data space is reserved in X address memory space between 0x0000 and 0x1FFF, which is directly addressable via a 13-bit absolute address field within all memory direct instructions. The remaining X address space and all of the Y address space is addressable indirectly. Additionally, the whole of X data space is addressable using  ${\tt MOV}$  instructions, which support memory direct addressing with a 16-bit address field.

#### 3.2.6 SOFTWARE STACK

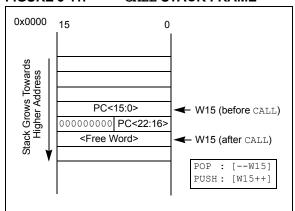

The dsPIC DSC devices contain a software stack. W15 is used as the Stack Pointer.

The Stack Pointer always points to the first available free word and grows from lower addresses towards higher addresses. It pre-decrements for stack pops and post-increments for stack pushes as shown in Figure 3-11. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

Note: A PC push during exception processing will concatenate the SRL register to the MSB of the PC prior to the push.

There is a Stack Pointer Limit register (SPLIM) associated with the Stack Pointer. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word aligned. Whenever an Effective Address (EA) is generated using W15 as a source or destination pointer, the address thus generated is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a Stack Error Trap will not occur. The Stack Error Trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a Stack Error Trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value, 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800, thus preventing the stack from interfering with the Special Function Register (SFR) space

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

FIGURE 3-11: CALL STACK FRAME

### 3.2.7 DATA RAM PROTECTION FEATURE

The dsPIC30F6011A/6012A/6013A/6014A devices support data RAM protection features which enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled.

See Table 3-3 for an overview of the BSRAM and SSRAM SFRs.

NOTES:

### 7.0 DATA EEPROM MEMORY

Note:

This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

The Data EEPROM Memory is readable and writable during normal operation over the entire VDD range. The data EEPROM memory is directly mapped in the program memory address space.

The four SFRs used to read and write the program Flash memory are used to access data EEPROM memory, as well. As described in **Section 6.5 "Control Registers"**, these registers are:

- NVMCON

- NVMADR

- NVMADRU

- NVMKEY

The EEPROM data memory allows read and write of single words and 16-word blocks. When interfacing to data memory, NVMADR in conjunction with the NVMADRU register are used to address the EEPROM location being accessed. TBLRDL and TBLWTL instructions are used to read and write data EEPROM. The dsPIC30F devices have up to 8 Kbytes (4K words) of data EEPROM with an address range from 0x7FF000 to 0x7FFFFE.

A word write operation should be preceded by an erase of the corresponding memory location(s). The write typically requires 2 ms to complete but the write time will vary with voltage and temperature.

A program or erase operation on the data EEPROM does not stop the instruction flow. The user is responsible for waiting for the appropriate duration of time before initiating another data EEPROM write/erase operation. Attempting to read the data EEPROM while a programming or erase operation is in progress results in unspecified data.

Control bit WR initiates write operations similar to program Flash writes. This bit cannot be cleared, only set, in software. They are cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The address register NVMADR remains unchanged.

**Note:** Interrupt flag bit NVMIF in the IFS0 register is set when write is complete. It must be cleared in software.

### 7.1 Reading the Data EEPROM

A TBLRD instruction reads a word at the current program word address. This example uses W0 as a pointer to data EEPROM. The result is placed in register W4 as shown in Example 7-1.

#### **EXAMPLE 7-1:** DATA EEPROM READ

MOV #LOW\_ADDR\_WORD,W0 ; Init Pointer

MOV #HIGH\_ADDR\_WORD,W1

MOV W1,TBLPAG

TBLRDL [ W0 ], W4 ; read data EEPROM

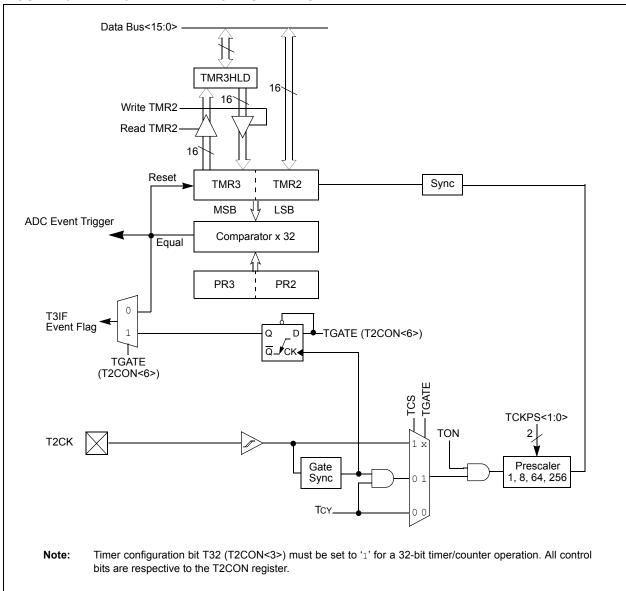

FIGURE 10-1: 32-BIT TIMER2/3 BLOCK DIAGRAM

### 10.1 Timer Gate Operation

The 32-bit timer can be placed in the Gated Time Accumulation mode. This mode allows the internal TCY to increment the respective timer when the gate input signal (T2CK pin) is asserted high. Control bit TGATE (T2CON<6>) must be set to enable this mode. When in this mode, Timer2 is the originating clock source. The TGATE setting is ignored for Timer3. The timer must be enabled (TON = 1) and the timer clock source set to internal (TCS = 0).

The falling edge of the external signal terminates the count operation but does not reset the timer. The user must reset the timer in order to start counting from zero.

### 10.2 ADC Event Trigger

When a match occurs between the 32-bit timer (TMR3/TMR2) and the 32-bit combined period register (PR3/PR2), or between the 16-bit timer TMR3 and the 16-bit period register PR3, a special ADC trigger event signal is generated by Timer3.

#### 10.3 Timer Prescaler

The input clock (Fosc/4 or external clock) to the timer has a prescale option of 1:1, 1:8, 1:64 and 1:256, selected by control bits TCKPS<1:0> (T2CON<5:4> and T3CON<5:4>). For the 32-bit timer operation, the originating clock source is Timer2. The prescaler operation for Timer3 is not applicable in this mode. The prescaler counter is cleared when any of the following occurs:

- · A write to the TMR2/TMR3 register

- · A write to the T2CON/T3CON register

- · A device Reset, such as a POR and BOR

However, if the timer is disabled (TON = 0), then the Timer 2 prescaler cannot be reset since the prescaler clock is halted.

TMR2/TMR3 is not cleared when T2CON/T3CON is written.

## 10.4 Timer Operation During Sleep Mode

During CPU Sleep mode, the timer will not operate because the internal clocks are disabled.

### 10.5 Timer Interrupt

The 32-bit timer module can generate an interrupt on period match or on the falling edge of the external gate signal. When the 32-bit timer count matches the respective 32-bit period register, or the falling edge of the external "gate" signal is detected, the T3IF bit (IFSO<7>) is asserted and an interrupt will be generated if enabled. In this mode, the T3IF interrupt flag is used as the source of the interrupt. The T3IF bit must be cleared in software.

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T3IE (IECO<7>).

#### 12.1.2 CAPTURE BUFFER OPERATION

Each capture channel has an associated FIFO buffer which is four 16-bit words deep. There are two status flags which provide status on the FIFO buffer:

- · ICBFNE Input Capture Buffer Not Empty

- · ICOV Input Capture Overflow

The ICBFNE will be set on the first input capture event and remain set until all capture events have been read from the FIFO. As each word is read from the FIFO, the remaining words are advanced by one position within the buffer.

In the event that the FIFO is full with four capture events and a fifth capture event occurs prior to a read of the FIFO, an overflow condition will occur and the ICOV bit will be set to a logic '1'. The fifth capture event is lost and is not stored in the FIFO. No additional events will be captured until all four events have been read from the buffer.

If a FIFO read is performed after the last read and no new capture event has been received, the read will yield indeterminate results.

### 12.1.3 TIMER2 AND TIMER3 SELECTION MODE

The input capture module consists of up to 8 input capture channels. Each channel can select between one of two timers for the time base, Timer2 or Timer3.

Selection of the timer resource is accomplished through SFR bit, ICTMR (ICxCON<7>). Timer3 is the default timer resource available for the input capture module.

### 12.1.4 HALL SENSOR MODE

When the input capture module is set for capture on every edge, rising and falling, ICM<2:0> = 001, the following operations are performed by the input capture logic:

- The input capture interrupt flag is set on every edge, rising and falling.

- The interrupt on Capture mode setting bits, ICI<1:0>, is ignored since every capture generates an interrupt.

- A capture overflow condition is not generated in this mode.

# 12.2 Input Capture Operation During Sleep and Idle Modes

An input capture event will generate a device wake-up or interrupt, if enabled, if the device is in CPU Idle or Sleep mode.

Independent of the timer being enabled, the input capture module will wake-up from the CPU Sleep or Idle mode when a capture event occurs if ICM<2:0> = 111 and the interrupt enable bit is asserted. The same wake-up can generate an interrupt if the conditions for processing the interrupt have been satisfied. The wake-up feature is useful as a method of adding extra external pin interrupts.

## 12.2.1 INPUT CAPTURE IN CPU SLEEP MODE

CPU Sleep mode allows input capture module operation with reduced functionality. In the CPU Sleep mode, the ICI<1:0> bits are not applicable and the input capture module can only function as an external interrupt source.

The capture module must be configured for interrupt only on rising edge (ICM<2:0> = 111) in order for the input capture module to be used while the device is in Sleep mode. The prescale settings of 4:1 or 16:1 are not applicable in this mode.

# 12.2.2 INPUT CAPTURE IN CPU IDLE MODE

CPU Idle mode allows input capture module operation with full functionality. In the CPU Idle mode, the Interrupt mode selected by the ICI<1:0> bits is applicable, as well as the 4:1 and 16:1 capture prescale settings which are defined by control bits ICM<2:0>. This mode requires the selected timer to be enabled. Moreover, the ICSIDL bit must be asserted to a logic '0'.

If the input capture module is defined as ICM<2:0> = 111 in CPU Idle mode, the input capture pin will serve only as an external interrupt pin.

### 12.3 Input Capture Interrupts

The input capture channels have the ability to generate an interrupt based upon the selected number of capture events. The selection number is set by control bits ICI<1:0> (ICxCON<6:5>).

Each channel provides an interrupt flag (ICxIF) bit. The respective capture channel interrupt flag is located in the corresponding IFSx status register.

Enabling an interrupt is accomplished via the respective capture channel interrupt enable (ICxIE) bit. The capture interrupt enable bit is located in the corresponding IEC control register.

| _             |

|---------------|

| MAP(1         |

| <b>SISTER</b> |

| N1 RE         |

| .:<br>CA      |

| -E 17-1       |

| TABI          |

| IABLE 1/-1:     |          | CANTR                                                     | CAN1 REGISTER MAP                             | K MAP         |                                                       |              |          |           |            |                |                                                        |                                              |                          |             |         |            |                     |

|-----------------|----------|-----------------------------------------------------------|-----------------------------------------------|---------------|-------------------------------------------------------|--------------|----------|-----------|------------|----------------|--------------------------------------------------------|----------------------------------------------|--------------------------|-------------|---------|------------|---------------------|

| SFR Name        | Addr     | Bit 15                                                    | Bit 14                                        | Bit 13        | Bit 12                                                | Bit 11       | Bit 10   | Bit 9     | Bit 8      | Bit 7          | Bit 6 B                                                | Bit 5 Bit 4                                  | Bit 3                    | Bit 2       | 2 Bit 1 | Bit 0      | Reset State         |

| C1RXF0SID       | 0300     | Ι                                                         | 1                                             | 1             |                                                       |              | Rec      | eive Acce | ptance F   | ilter 0 Stand  | Receive Acceptance Filter 0 Standard Identifier <10:0> | <10:0>                                       |                          |             | I       | EXIDE      | 000n nnnn nnnn n000 |

| C1RXF0EIDH      | 0302     | _                                                         | -                                             | -             | _                                                     |              |          |           | Receive,   | Acceptance     | Receive Acceptance Filter 0 Extended Identifier <17:6> | nded Identifie                               | er <17:6>                |             |         |            | 0000 nnnn nnnn 0000 |

| C1RXF0EIDL      | 0304     | Receiv                                                    | e Acceptano                                   | ce Filter 0 L | Receive Acceptance Filter 0 Extended Identifier <5:0> | ntifier <5:0 | ^        | 1         | I          | _              | 1                                                      |                                              | _                        | _           | 1       | Ι          | 0000 0000 00nn nnnn |

| C1RXF1SID       | 9080     | Ι                                                         | I                                             | I             |                                                       |              | Rec      | eive Acce | sptance F  | ilter 1 Stand  | Receive Acceptance Filter 1 Standard Identifier <10:0> | <10:0>                                       |                          |             | ı       | EXIDE      | nonn nnnn nooo      |

| C1RXF1EIDH      | 030A     | I                                                         | I                                             | I             | I                                                     |              |          |           | Receive,   | Acceptance     | Receive Acceptance Filter 1 Extended Identifier <17:6> | nded Identifie                               | er <17:6>                |             |         |            | nnnn nnnn nnnn 0000 |

| C1RXF1EIDL      | 030C     | Receiv                                                    | e Acceptano                                   | ce Filter 1 E | Receive Acceptance Filter 1 Extended Identifier <5:0> | ntifier <5:0 | Δ        | 1         | I          | Ι              | I                                                      | 1                                            | I                        | -           | 1       | I          | 0000 0000 00nn nnnn |

| C1RXF2SID       | 0310     | I                                                         | I                                             | I             |                                                       |              | Rec      | eive Acce | sptance F  | ilter 2 Stand  | Receive Acceptance Filter 2 Standard Identifier <10:0> | <10:0>                                       |                          |             | 1       | EXIDE      | nonn nnnn nooo      |

| C1RXF2EIDH      | 0312     | I                                                         | I                                             | I             | I                                                     |              |          |           | Receive,   | Acceptance     | Receive Acceptance Filter 2 Extended Identifier <17:6> | nded Identifie                               | er <17:6>                |             |         |            | nnnn nnnn nnnn 0000 |

| C1RXF2EIDL      | 0314     | Receiv                                                    | e Acceptano                                   | ce Filter 2 E | Receive Acceptance Filter 2 Extended Identifier <5:0> | ntifier <5:0 | Δ        | I         | 1          | 1              | 1                                                      | 1                                            | 1                        | -           | 1       | 1          | 0000 0000 00nn nnnn |

| C1RXF3SID       | 0318     | I                                                         | I                                             | I             |                                                       |              | Rec      | eive Acce | sptance F  | ilter 3 Standa | Receive Acceptance Filter 3 Standard Identifier <10:0> | <10:0>                                       |                          |             | 1       | EXIDE      | nonn nnnn nooo      |

| C1RXF3EIDH      | 031A     | 1                                                         | I                                             | I             | ı                                                     |              |          |           | Receive,   | Acceptance     | Receive Acceptance Filter 3 Extended Identifier <17:6> | nded Identifie                               | er <17:6>                |             |         |            | nnnn nnnn nnnn 0000 |

| C1RXF3EIDL      | 031C     | Receiv                                                    | e Acceptano                                   | ce Filter 3 E | Receive Acceptance Filter 3 Extended Identifier <5:0> | ntifier <5:0 | <u> </u> | ı         | ı          | 1              | ı                                                      | 1                                            | 1                        | -           | 1       | 1          | 0000 0000 00nn nnnn |

| C1RXF4SID       | 0320     | I                                                         | I                                             | I             |                                                       |              | Rec      | eive Acce | sptance F  | ilter 4 Standa | Receive Acceptance Filter 4 Standard Identifier <10:0> | <10:0>                                       |                          |             | I       | EXIDE      | nonn nnnn nooo      |

| C1RXF4EIDH      | 0322     | 1                                                         | I                                             | I             | I                                                     |              |          |           | Receive,   | Acceptance     | Receive Acceptance Filter 4 Extended Identifier <17:6> | nded Identifie                               | er <17:6>                |             |         |            | nnnn nnnn nnnn 0000 |

| C1RXF4EIDL      | 0324     | Receiv                                                    | e Acceptano                                   | ce Filter 4 E | Receive Acceptance Filter 4 Extended Identifier <5:0> | ntifier <5:0 | <u>^</u> | I         | I          | 1              | ı                                                      | 1                                            | 1                        | -           | 1       | I          | 0000 0000 00nn nnnn |

| C1RXF5SID       | 0328     | I                                                         | 1                                             |               |                                                       |              | Rec      | eive Acce | sptance Fi | ilter 5 Standa | Receive Acceptance Filter 5 Standard Identifier <10:0> | <10:0>                                       |                          |             | 1       | EXIDE      | nonn nnnn nooo      |

| C1RXF5EIDH 032A | 032A     | I                                                         | 1                                             | I             | I                                                     |              |          |           | Receive,   | Acceptance     | Receive Acceptance Filter 5 Extended Identifier <17:6> | nded Identifie                               | er <17:6>                |             |         |            | nnnn nnnn nnnn 0000 |

| C1RXF5EIDL      | 032C     | Receiv                                                    | e Acceptano                                   | ce Filter 5 E | Receive Acceptance Filter 5 Extended Identifier <5:0> | ntifier <5:0 | <u> </u> | I         | ı          | 1              | ı                                                      | 1                                            | 1                        |             | -       | 1          | 0000 0000 00nn nnnn |

| C1RXM0SID       | 0330     | I                                                         | I                                             | I             |                                                       |              | Rec      | eive Acce | ptance M   | ask 0 Stand    | Receive Acceptance Mask 0 Standard Identifier <10:0>   | <10:0>                                       |                          |             | 1       | MIDE       | nonn nnnn nooo      |

| C1RXM0EIDH 0332 | 1 0332   | I                                                         | I                                             | I             | I                                                     |              |          |           | Receive,   | Acceptance     | Receive Acceptance Mask 0 Extended Identifier <17:6>   | nded Identifie                               | er <17:6>                |             |         |            | nnnn nnnn 0000      |

| C1RXM0EIDL 0334 | . 0334   | Receiv                                                    | e Acceptanc                                   | ce Mask 0 I   | Receive Acceptance Mask 0 Extended Identifier <5:0>   | ntifier <5:0 | <u>^</u> | 1         | 1          | 1              | 1                                                      | 1                                            | 1                        |             | 1       | 1          | 0000 0000 00nn nnnn |

| C1RXM1SID       | 0338     | I                                                         | I                                             | I             |                                                       |              | Rec      | eive Acce | ptance M   | ask 1 Stand    | Receive Acceptance Mask 1 Standard Identifier <10:0>   | <10:0>                                       |                          |             | 1       | MIDE       | nonn nnnn nooo      |

| C1RXM1EIDH 033A | 4 033A   | Ι                                                         | I                                             | Ι             | I                                                     |              |          |           | Receive,   | Acceptance     | Receive Acceptance Mask 1 Extended Identifier <17:6>   | nded Identifie                               | er <17:6>                |             |         |            | nnnn nnnn nonn 0000 |

| C1RXM1EIDL 033C | _ 033C   | Receiv                                                    | e Acceptanc                                   | ce Mask 1 I   | Receive Acceptance Mask 1 Extended Identifier <5:0>   | ntifier <5:0 | <u>^</u> | 1         | I          | Ι              | I                                                      | 1                                            | I                        | -           | 1       | I          | 0000 0000 00nn nnnn |

| C1TX2SID        | 0340     | Transn                                                    | nit Buffer 2 S                                | Standard Id   | Transmit Buffer 2 Standard Identifier <10:6           | <9:          | 1        | I         | Ι          | Tra            | Transmit Buffer 2 Standard Identifier <5:0>            | 2 Standard Io                                | dentifier <5:0           | <u>^</u>    | SRR     | TXIDE      | nnnn nnnn 000n nnnn |

| C1TX2EID        | 0345     | 0342 Transmit Buffer 2 Extended Identifier <17:14>        | fer 2 Extend                                  | led Identifie | yr <17:14>                                            | -            | 1        | 1         | 1          |                | Transmi                                                | Transmit Buffer 2 Extended Identifier <13:6> | ended Ideni              | tifier <13: | <9      |            | uuuu 0000 uuuu      |

| C1TX2DLC        | 0344     | T.                                                        | ransmit Buff                                  | fer 2 Extent  | Transmit Buffer 2 Extended Identifier                 | <0:5>        |          | TXRTR     | TXRB1      | TXRB0          |                                                        | DLC<3:0>                                     |                          | I           | I       | I          | nunn nunn nonn      |

| C1TX2B1         | 0346     |                                                           |                                               | Tran          | Transmit Buffer 2                                     | Byte 1       |          |           |            |                |                                                        | Transmit B                                   | Transmit Buffer 2 Byte 0 | 0           |         |            | nnnn nnnn nnnn      |

| C1TX2B2         | 0348     |                                                           |                                               | Tran          | Transmit Buffer 2                                     | Byte 3       |          |           |            |                |                                                        | Transmit B                                   | Transmit Buffer 2 Byte 2 | 2           |         |            | nnnn nnnn nnnn nnnn |

| C1TX2B3         | 034A     |                                                           |                                               | Tran.         | Transmit Buffer 2                                     | Byte 5       |          |           |            |                |                                                        | Transmit B                                   | Transmit Buffer 2 Byte 4 | 4           |         |            | nnnn nnnn nnnn      |

| C1TX2B4         | 034C     |                                                           |                                               | Tran.         | Transmit Buffer 2                                     | 2 Byte 7     |          |           |            |                |                                                        | Transmit B                                   | Transmit Buffer 2 Byte 6 | 9           |         |            | nnnn nnnn nnnn      |

| C1TX2CON        | 034E     | Ι                                                         | I                                             | 1             | 1                                                     | I            | 1        | I         | 1          | 1              | TXABT TX                                               | TXABT TXLARB TXERR                           | R TXREQ                  | ا<br>ر      | X       | TXPRI<1:0> | 0000 0000 0000 0000 |

| C1TX1SID        | 0320     | Transn                                                    | Transmit Buffer 1 Standard Identifier <10:    | Standard Id   | lentifier <10:6                                       | <9           | ı        | I         | I          | Tra            | Transmit Buffer 1 Standard Identifier <5:0>            | 1 Standard Io                                | dentifier <5:0           | <u>^</u>    | SRR     | TXIDE      | nnnn nnnn 000n nnnn |

| C1TX1EID        | 0352     | Transmit But                                              | Transmit Buffer 1 Extended Identifier <17:14> | led Identifie | r <17:14>                                             | I            | 1        | 1         | I          |                | Transmi                                                | Transmit Buffer 1 Extended Identifier <13:6> | ended Ident              | tifier <13: | <9      |            | nnnn nnnn 0000 nnnn |

| C1TX1DLC        | 0354     | Ē                                                         | ransmit Buff                                  | fer 1 Extent  | Fransmit Buffer 1 Extended Identifier                 | <2:0>        |          | TXRTR     | TXRB1      | TXRB0          |                                                        | DLC<3:0>                                     |                          | 1           | 1       | 1          | 000n nnnn nnnn nnnn |

| Legend:         | u = unii | u = uninitialized bit; — = unimplemented bit, read as '0' | — = unimple                                   | emented bi    | it, read as '0'                                       |              |          |           |            |                |                                                        |                                              |                          |             |         |            |                     |

egend: u = uninitialized bit; — = unimplemented bit, read as '0'

ote 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

| <b>TABLE 17-2</b> : | <b>.</b> | CAN2 R           | CAN2 REGISTER MAP <sup>(1)</sup> (CON         | R MAP         | 1) (CO                  | NTINUED)                      | <u>(</u>  |                   |             |                                             |                                             |                    |                         |                                              |            |             |          |                     |

|---------------------|----------|------------------|-----------------------------------------------|---------------|-------------------------|-------------------------------|-----------|-------------------|-------------|---------------------------------------------|---------------------------------------------|--------------------|-------------------------|----------------------------------------------|------------|-------------|----------|---------------------|

| SFR Name            | Addr.    | Bit 15           | Bit 14                                        | Bit 13        | Bit 12                  | Bit 11                        | Bit 10    | Bit 9             | Bit 8       | Bit 7                                       | Bit 6                                       | Bit 5              | Bit 4                   | Bit 3                                        | Bit 2      | Bit 1       | Bit 0    | Reset State         |

| C2TX1B1             | 0416     |                  |                                               | Transı        | <b>Fransmit Buffer</b>  | · 1 Byte 1                    |           |                   |             |                                             |                                             | Trans              | mit Buffe               | Fransmit Buffer 1 Byte 0                     |            |             |          | nnnn nnnn nnnn nnnn |

| C2TX1B2             | 0418     |                  |                                               | Trans         | Transmit Buffer         | 1 Byte 3                      |           |                   |             |                                             |                                             | Trans              | smit Buffe              | Transmit Buffer 1 Byte 2                     |            |             |          | nnnn nnnn nnnn      |

| C2TX1B3             | 041A     |                  |                                               | Trans         | Transmit Buffer         | 1 Byte 5                      |           |                   |             |                                             |                                             | Trans              | mit Buffe               | Transmit Buffer 1 Byte 4                     |            |             |          | nnnn nnnn nnnn nnnn |

| C2TX1B4             | 041C     |                  |                                               | Trans         | Transmit Buffer 1       | · 1 Byte 7                    |           |                   |             |                                             |                                             | Trans              | mit Buffe               | Transmit Buffer 1 Byte 6                     |            |             |          | nnnn nnnn nnnn nnnn |

| C2TX1CON            | 041E     | I                | Ι                                             | Ι             | I                       | 1                             | I         | I                 | 1           | I                                           | TXABT 1                                     | TXLARB             | TXERR                   | TXREQ                                        | I          | TXPRI<1:0>  |          | 0000 0000 0000 0000 |

| C2TX0SID            | 0450     | Transn           | Transmit Buffer 0 Standard Identifier <10:6>  | tandard Ide   | ntifier <1              | <9:0                          | I         | I                 | 1           | Trar                                        | Transmit Buffer 0 Standard Identifier <5:0> | ۶۲ 0 Stand         | ard Identi              | fier <5:0>                                   |            | SRR         | TXIDE    | nnnn nnnn 000n nnnn |

| C2TX0EID            |          | Transmit Buf     | Transmit Buffer 0 Extended Identifier <17:14> | 3d Identifier | <17:14>                 | 1                             | I         | I                 | 1           |                                             | Trans                                       | mit Buffer         | · 0 Extend              | Transmit Buffer 0 Extended Identifier <13:6> | <13:6>     |             |          | nnnn nnnn 0000 nnnn |

| C2TX0DLC            | 0424     | T.               | Transmit Buffer 0 Extended Identifier         | er 0 Extend   | ed Identif.             | ier <5:0>                     |           | TXRTR             | TXRB1       | TXRB0                                       |                                             | DLC                | DLC<3:0>                |                                              | 1          | 1           | 1        | nnnn nnnn nnnn      |

| C2TX0B1             | 0426     |                  |                                               | Trans         | Transmit Buffer 0       | · 0 Byte 1                    |           |                   |             |                                             |                                             | Trans              | mit Buffe               | Transmit Buffer 0 Byte 0                     |            |             |          | nnnn nnnn nnnn nnnn |

| C2TX0B2             | 0428     |                  |                                               | Trans         | Transmit Buffer 0       | r 0 Byte 3                    |           |                   |             |                                             |                                             | Trans              | mit Buffe               | Transmit Buffer 0 Byte 2                     |            |             |          | nnnn nnnn nnnn nnnn |

| C2TX0B3             | 042A     |                  |                                               | Trans         | Transmit Buffer 0       | · 0 Byte 5                    |           |                   |             |                                             |                                             | Trans              | mit Buffe               | Transmit Buffer 0 Byte 4                     |            |             |          | nnnn nnnn nnnn nnnn |

| C2TX0B4             | 042C     |                  |                                               | Trans         | Transmit Buffer 0       | · 0 Byte 7                    |           |                   |             |                                             |                                             | Trans              | smit Buffe              | Transmit Buffer 0 Byte 6                     |            |             |          | nnnn nnnn nnnn nnnn |

| 7                   | 042E     | I                | ı                                             | I             | I                       | ı                             | I         | I                 | I           | I                                           | TXABT                                       | TXABT TXLARB TXERR | TXERR                   | TXREQ                                        | ı          | TXPRI<1:0>  | <1:0>    | 0000 0000 0000 0000 |

| C2RX1SID            | 0430     | I                | I                                             | 1             |                         |                               |           | Receiv            | ve Buffer   | Receive Buffer 1 Standard Identifier <10:0> | entifier <1                                 | <0:0               |                         |                                              |            | SRR         | RXIDE    | nnnn nnnn nnnn n000 |

| C2RX1EID            | 0432     | 1                | 1                                             | Ι             | I                       |                               |           |                   | Re          | Receive Buffer 1 Extended Identifier <17:6> | 1 Extende                                   | d Identifie        | yr <17:6>               |                                              |            |             |          | nnnn nnnn nonn 0000 |

| C2RX1DLC            | 0434     | מצ               | Receive Buffer                                | r 1 Extend    | 1 Extended Identifie    | ier <5:0>                     |           | RXRTR RXRB1       | RXRB1       | I                                           | I                                           | I                  | RXRB0                   |                                              | DLC<3:0>   | <0          |          | nnnn n000 nnnn nnnn |

| C2RX1B1             | 0436     |                  |                                               | Recei         | Receive Buffer          | $\overline{}$                 |           |                   |             |                                             |                                             | Rece               | Receive Buffer 1 Byte 0 | r 1 Byte 0                                   |            |             |          | nnnn nnnn nnnn      |

| C2RX1B2             | 0438     |                  |                                               | Recei         | Receive Buffer          | 1 Byte 3                      |           |                   |             |                                             |                                             | Rece               | Receive Buffer 1 Byte 2 | r 1 Byte 2                                   |            |             |          | nnnn nnnn nnnn nnnn |

| C2RX1B3             | 043A     |                  |                                               | Recei         | Receive Buffer          | $\overline{}$                 |           |                   |             |                                             |                                             | Rece               | ive Buffe               | Receive Buffer 1 Byte 4                      |            |             |          | nnnn nnnn nnnn nnnn |

| C2RX1B4             | 043C     |                  |                                               | Recei         | Receive Buffer          | 1 Byte 7                      |           |                   |             |                                             |                                             | Rece               | ive Buffe,              | Receive Buffer 1 Byte 6                      |            |             |          | nnnn nnnn nnnn nnnn |

| C2RX1CON            | 043E     | I                | 1                                             | I             | I                       | I                             | I         | I                 | I           | RXFUL                                       | I                                           | I                  | I                       | RXRTRRO                                      | FIL        | FILHIT<2:0> | ٨        | 0000 0000 0000 0000 |

| C2RX0SID            | 0440     | I                | I                                             | 1             |                         |                               |           | Receiv            | ve Buffer ( | Receive Buffer 0 Standard Identifier <10:0> | entifier <1                                 | <0:0               |                         |                                              |            | SRR         | RXIDE    | nnnn nnnn nnnn n000 |

| C2RX0EID            | 0442     | I                | I                                             | I             | I                       |                               |           |                   | Re          | Receive Buffer 0 Extended Identifier <17:6> | 0 Extende                                   | d Identifie        | ÷r <17:6>               |                                              |            |             |          | nnnn nnnn nnnn 0000 |

| C2RX0DLC            | 0444     | צ                | Receive Buffer 0 Extended Identifier          | ır 0 Extend   | ed Identifi             | ier <5:0>                     |           | RXRTR             | RXRB1       | I                                           | I                                           | -                  | RXRB0                   |                                              | DLC<3:0>   | <0.         |          | nnnn n000 nnnn nnnn |

| C2RX0B1             | 0446     |                  |                                               | Recei         | Receive Buffer 0 Byte 1 | 0 Byte 1                      |           |                   |             |                                             |                                             | Rece               | Receive Buffer 0 Byte 0 | r 0 Byte 0                                   |            |             |          | nnnn nnnn nnnn nnnn |

| C2RX0B2             | 0448     |                  |                                               | Recei         | Receive Buffer 0 Byte 3 | 0 Byte 3                      |           |                   |             |                                             |                                             | Rece               | ive Buffe,              | Receive Buffer 0 Byte 2                      |            |             |          | nnnn nnnn nnnn nnnn |

| C2RX0B3             | 044A     |                  |                                               | Recei         | Receive Buffer 0 Byte 5 | 0 Byte 5                      |           |                   |             |                                             |                                             | Rece               | ive Buffe               | Receive Buffer 0 Byte 4                      |            |             |          | nnnn nnnn nnnn nnnn |

| C2RX0B4             | 044C     |                  |                                               | Recei         | Receive Buffer 0        | 0 Byte 7                      |           |                   |             |                                             |                                             | Rece               | ive Buffe               | Receive Buffer 0 Byte 6                      |            |             |          | nnnn nnnn nnnn nnnn |

| C2RX0CON            | 044E     | I                | I                                             | I             | I                       | I                             | I         | I                 | I           | RXFUL                                       | I                                           | I                  | I                       | RXRTRRO DBEN JTOFF                           | DBEN       |             | FILHIT0  | 0000 0000 0000 0000 |

| C2CTRL              | 0420     | CANCAP           | 1                                             | CSIDLE        | ABAT                    | CANCKS                        | RE        | REQOP<2:0>        | ^           | OPM                                         | OPMODE<2:0>                                 | ^                  | 1                       | ICOL                                         | ICODE<2:0> |             | 1        | 0000 0100 1000 0000 |

| C2CFG1              | 0452     | I                | I                                             | 1             | I                       | I                             | 1         | I                 | I           | SJW<1:0>                                    | <0:                                         |                    |                         | BRP<5:0>                                     | ^(         |             |          | 0000 0000 0000 0000 |

| C2CFG2              | 0454     | 1                | WAKFIL                                        | 1             | 1                       | 1                             | SE        | SEG2PH<2:0>       | <(          | SEG2PHTS                                    |                                             | SE                 | SEG1PH<2:0>             |                                              | PR         | PRSEG<2:0>  | <b>^</b> | 0000 0uuu uuuu      |

| C2INTF              | 0456     | RX00VR           | RX10VR                                        | TXBO          | TXEP                    | RXEP                          | TXWAR     | TXWAR RXWAR EWARN | EWARN       | IVRIF                                       | WAKIF                                       | ERRIF              | TX2IF                   |                                              | TX0IF F    | RX1IF       | RX0IF    | 0000 0000 0000 0000 |

| CZINTE              | 0458     | I                | Ι                                             | I             | Ι                       | 1                             | I         | Ι                 | Ι           | IVRIE                                       | WAKIE                                       | ERRIE              | TX2IE                   |                                              | TX0E       | RX1E        | RX0IE    | 0000 0000 0000 0000 |

| CZEC                | 045A     |                  |                                               | Transmit      | Error Co.               | Transmit Error Count Register | <u>ار</u> |                   |             |                                             |                                             | Receive            | Error Co                | Receive Error Count Register                 |            |             |          | 0000 0000 0000 0000 |

| - 20000             | 1        | tid Politication | 1                                             | tid bottom.   | 2000                    | , ,                           |           |                   |             |                                             |                                             |                    |                         |                                              |            |             |          |                     |

u = uninitialized bit; — = unimplemented bit, read as '0'

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields. Legend: Note 1:

SYSTEM INTEGRATION REGISTER MAP FOR dsPIC30F601XA<sup>(1)</sup> **TABLE 20-7**:

|                                                | :    | •      |                                           | )         |        | !      | 1     |           | •     |       |       |                                                 |        |        |       |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------|------|--------|-------------------------------------------|-----------|--------|--------|-------|-----------|-------|-------|-------|-------------------------------------------------|--------|--------|-------|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SFR Addr<br>Name .                             | Addr | Bit 15 | Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 | Bit 13    | Bit 12 | Bit 11 |       | Bit 9     | Bit 8 | Bit 7 | Bit 6 | Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 | Bit 4  | Bit 3  | Bit 2 | Bit 1    | Bit 0 | Reset State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RCON 0740 TRAPR IOPUWR BGST LVDEN              | 0740 | TRAPR  | IOPUWR                                    | BGST      | LVDEN  |        | LVDL  | /DL<3:0>  |       | EXTR  | SWR   | SWDTEN                                          | WDTO   | SLEEP  | IDLE  | BOR      | POR   | EXTR SWR SWDTEN WDTO SLEEP IDLE BOR POR Depends on type of Reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OSCCON 0742                                    | 0742 | I      | 00                                        | COSC<2:0> | ٨      | 1      | Z     | NOSC<2:0> | Δ     | POST. | <1:0> | POST<1:0> LOCK                                  | ı      | CF     | 1     | LPOSCEN  | OSWEN | <ul> <li>LPOSCEN OSWEN Depends on Configuration bits.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OSCTUN 0744                                    | 0744 | I      | I                                         | -         | I      | 1      | 1     | I         | 1     | Ι     | I     | 1                                               | I      |        | TUT   | TUN<3:0> |       | 0000 0000 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |