Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20 MIPS                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 68                                                                             |

| Program Memory Size        | 132KB (44K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 2K x 8                                                                         |

| RAM Size                   | 6K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 16x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6013a-20e-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **High-Performance, 16-bit Digital Signal Controllers**

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

# High-Performance Modified RISC CPU:

- · Modified Harvard architecture

- · C compiler optimized instruction set architecture

- Flexible addressing modes

- 83 base instructions

- 24-bit wide instructions, 16-bit wide data path

- · Up to 144 Kbytes on-chip Flash program space

- · Up to 48K instruction words

- · Up to 8 Kbytes of on-chip data RAM

- Up to 4 Kbytes of nonvolatile data EEPROM

- 16 x 16-bit working register array

- Up to 30 MIPS operation:

- DC to 40 MHz external clock input

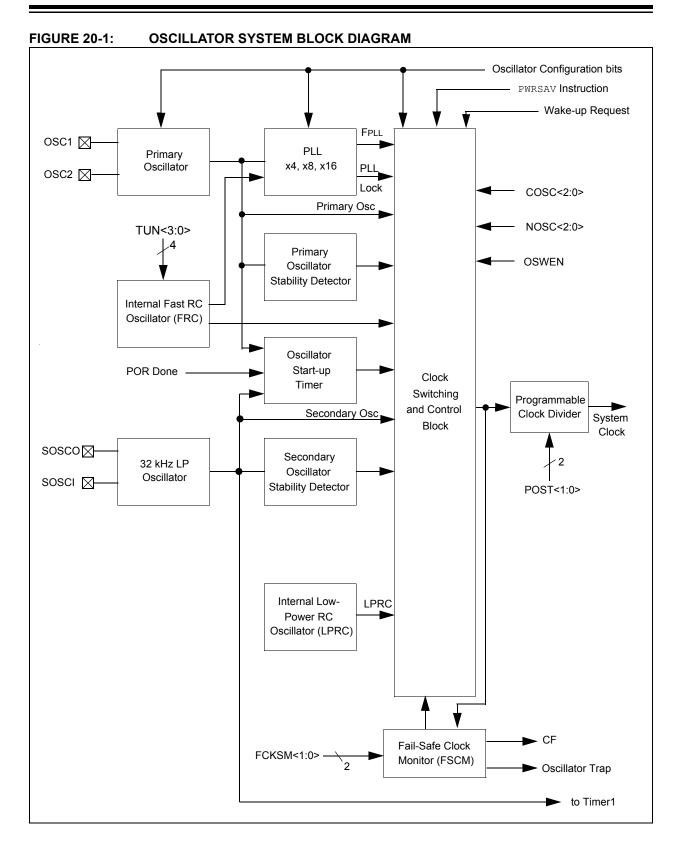

- 4 MHz-10 MHz oscillator input with PLL active (4x, 8x, 16x)

- Up to 41 interrupt sources:

- Eight user-selectable priority levels

- Five external interrupt sources

- Four processor traps

### **DSP Features:**

- · Dual data fetch

- Modulo and Bit-Reversed modes

- Two 40-bit wide accumulators with optional saturation logic

- 17-bit x 17-bit single-cycle hardware fractional/ integer multiplier

- All DSP instructions are single cycle:

- Multiply-Accumulate (MAC) operation

- Single-cycle ±16 shift

# **Peripheral Features:**

- · High-current sink/source I/O pins: 25 mA/25 mA

- Five 16-bit timers/counters; optionally pair up 16-bit timers into 32-bit timer modules

- 16-bit Capture input functions

- · 16-bit Compare/PWM output functions:

- Data Converter Interface (DCI) supports common audio Codec protocols, including I<sup>2</sup>S and AC'97

- 3-wire SPI modules (supports four Frame modes)

- I<sup>2</sup>C<sup>™</sup> module supports Multi-Master/Slave mode and 7-bit/10-bit addressing

- Two addressable UART modules with FIFO buffers

- Two CAN bus modules compliant with CAN 2.0B standard

## **Analog Features:**

- 12-bit Analog-to-Digital Converter (ADC) with:

- 200 Ksps conversion rate

- Up to 16 input channels

- Conversion available during Sleep and Idle

- Programmable Low-Voltage Detection (PLVD)

- · Programmable Brown-out Reset

### **Special Microcontroller Features:**

- Enhanced Flash program memory:

- 10,000 erase/write cycle (min.) for

- industrial temperature range, 100K (typical)

- Data EEPROM memory:

- 100,000 erase/write cycle (min.) for industrial temperature range, 1M (typical)

- · Self-reprogrammable under software control

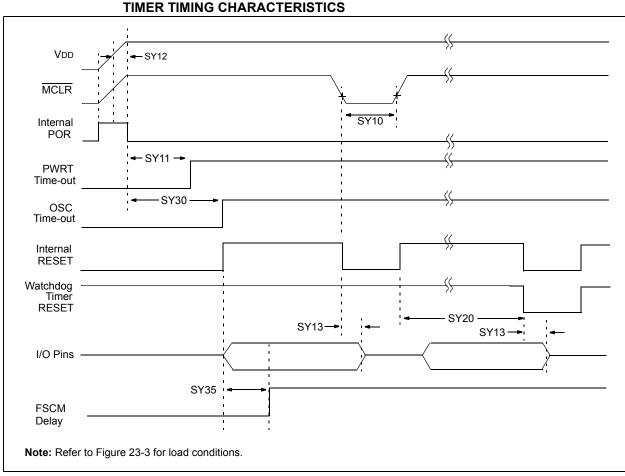

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT) with on-chip low-power RC oscillator for reliable operation

- Fail-Safe Clock Monitor operation:

- Detects clock failure and switches to on-chip low-power RC oscillator

- · Programmable code protection

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Selectable Power Management modes:

- Sleep, Idle and Alternate Clock modes

NOTES:

# 6.4 RTSP Operation

The dsPIC30F Flash program memory is organized into rows and panels. Each row consists of 32 instructions or 96 bytes. Each panel consists of 128 rows or 4K x 24 instructions. RTSP allows the user to erase one row (32 instructions) at a time and to program four instructions at one time. RTSP may be used to program multiple program memory panels, but the table pointer must be changed at each panel boundary.

Each panel of program memory contains write latches that hold 32 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the panel write latches. The data to be programmed into the panel is loaded in sequential order into the write latches: instruction 0, instruction 1, etc. The instruction words loaded must always be from a group of 32 boundary.

The basic sequence for RTSP programming is to set up a table pointer, then do a series of TBLWT instructions to load the write latches. Programming is performed by setting the special bits in the NVMCON register. Four TBLWTL and four TBLWTH instructions are required to load the four instructions. If multiple panel programming is required, the table pointer needs to be changed and the next set of multiple write latches written.

All of the table write operations are single word writes (2 instruction cycles) because only the table latches are written. A programming cycle is required for programming each row.

The Flash program memory is readable, writable, and erasable during normal operation over the entire VDD range.

# 6.5 Control Registers

The four SFRs used to read and write the program Flash memory are:

- NVMCON

- NVMADR

- NVMADRU

- NVMKEY

#### 6.5.1 NVMCON REGISTER

The NVMCON register controls which blocks are to be erased, which memory type is to be programmed and start of the programming cycle.

#### 6.5.2 NVMADR REGISTER

The NVMADR register is used to hold the lower two bytes of the Effective Address. The NVMADR register captures the EA<15:0> of the last table instruction that has been executed and selects the row to write.

#### 6.5.3 NVMADRU REGISTER

The NVMADRU register is used to hold the upper byte of the Effective Address. The NVMADRU register captures the EA<23:16> of the last table instruction that has been executed.

#### 6.5.4 NVMKEY REGISTER

NVMKEY is a write only register that is used for write protection. To start a programming or an erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 6.6 "Programming Operations"** for further details.

Note: The user can also directly write to the NVMADR and NVMADRU registers to specify a program memory address for erasing or programming.

# 10.0 TIMER2/3 MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the 32-bit General Purpose Timer module (Timer2/3) and associated Operational modes. Figure 10-1 depicts the simplified block diagram of the 32-bit Timer2/3 module. Figure 10-2 and Figure 10-3 show Timer2/3 configured as two independent 16-bit timers, Timer2 and Timer3, respectively.

The Timer2/3 module is a 32-bit timer (which can be configured as two 16-bit timers) with selectable Operating modes. These timers are utilized by other peripheral modules, such as:

- Input Capture

- · Output Compare/Simple PWM

The following sections provide a detailed description, including setup and control registers, along with associated block diagrams for the Operational modes of the timers.

The 32-bit timer has the following modes:

- Two independent 16-bit timers (Timer2 and Timer3) with all 16-bit Operating modes (except Asynchronous Counter mode)

- Single 32-bit timer operation

- · Single 32-bit synchronous counter

Further, the following operational characteristics are supported:

- ADC event trigger

- Timer gate operation

- Selectable prescaler settings

- Timer operation during Idle and Sleep modes

- · Interrupt on a 32-bit period register match

These Operating modes are determined by setting the appropriate bit(s) in the 16-bit T2CON and T3CON SFRs.

For 32-bit timer/counter operation, Timer2 is the lsw and Timer3 is the most significant word (msw) of the 32-bit timer.

Note: For 32-bit timer operation, T3CON control bits are ignored. Only T2CON control bits are used for setup and control. Timer2 clock and gate inputs are utilized for the 32-bit timer module but an interrupt is generated with the Timer3 interrupt flag (T3IF) and the interrupt is enabled with the Timer3 interrupt enable bit (T3IE).

**16-bit Timer Mode:** In the 16-bit mode, Timer2 and Timer3 can be configured as two independent 16-bit timers. Each timer can be set up in either 16-bit Timer mode or 16-bit Synchronous Counter mode. See **Section 9.0 "Timer1 Module"**, Timer1 Module for details on these two Operating modes.

The only functional difference between Timer2 and Timer3 is that Timer2 provides synchronization of the clock prescaler output. This is useful for high frequency external clock inputs.

**32-bit Timer Mode:** In the 32-bit Timer mode, the timer increments on every instruction cycle, up to a match value preloaded into the combined 32-bit Period register PR3/PR2, then resets to '0' and continues to count.

For synchronous 32-bit reads of the Timer2/Timer3 pair, reading the Isw (TMR2 register) will cause the msw to be read and latched into a 16-bit holding register, termed TMR3HLD.

For synchronous 32-bit writes, the holding register (TMR3HLD) must first be written to. When followed by a write to the TMR2 register, the contents of TMR3HLD will be transferred and latched into the MSB of the 32-bit timer (TMR3).

**32-bit Synchronous Counter Mode:** In the 32-bit Synchronous Counter mode, the timer increments on the rising edge of the applied external clock signal which is synchronized with the internal phase clocks. The timer counts up to a match value preloaded in the combined 32-bit period register PR3/PR2, then resets to '0' and continues.

When the timer is configured for the Synchronous Counter mode of operation and the CPU goes into the Idle mode, the timer will stop incrementing unless the the TSIDL bit (T2CON<13>) = 0. If TSIDL = 1, the timer module logic will resume the incrementing sequence upon termination of the CPU Idle mode.

NOTES:

# 14.3 Slave Select Synchronization

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be configured in SPI Slave mode with  $\overline{SSx}$  pin control enabled (SSEN = 1). When the  $\overline{SSx}$  pin is low, transmission and reception are enabled and the SDOx pin is driven. When  $\overline{SSx}$  pin goes high, the SDOx pin is no longer driven. Also, the SPI module is resynchronized, and all counters/control circuitry are reset. Therefore, when the  $\overline{SSx}$  pin is asserted low again, transmission/reception will begin at the MSb even if  $\overline{SSx}$  had been deasserted in the middle of a transmit/receive.

# 14.4 SPI Operation During CPU Sleep Mode

During Sleep mode, the SPI module is shutdown. If the CPU enters Sleep mode while an SPI transaction is in progress, then the transmission and reception is aborted.

The transmitter and receiver will stop in Sleep mode. However, register contents are not affected by entering or exiting Sleep mode.

# 14.5 SPI Operation During CPU Idle Mode

When the device enters Idle mode, all clock sources remain functional. The SPISIDL bit (SPIxSTAT<13>) selects if the SPI module will stop or continue on Idle. If SPISIDL = 0, the module will continue to operate when the CPU enters Idle mode. If SPISIDL = 1, the module will stop when the CPU enters Idle mode.

# 15.0 I<sup>2</sup>C<sup>™</sup> MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

The Inter-Integrated Circuit  $(I^2C^{TM})$  module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

This module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and will arbitrate accordingly

# 15.1 Operating Function Description

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

Thus, the  $l^2C$  module can operate either as a slave or a master on an  $l^2C$  bus.

# 15.1.1 VARIOUS I<sup>2</sup>C MODES

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

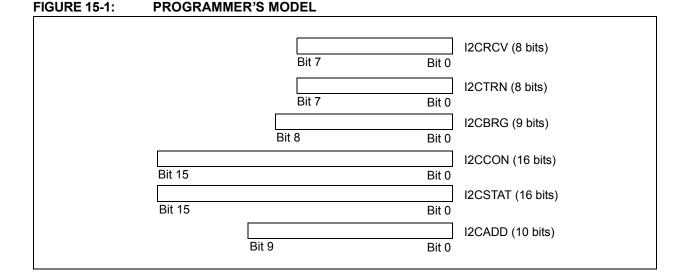

See the I<sup>2</sup>C programmer's model in Figure 15-1.

## 15.1.2 PIN CONFIGURATION IN I<sup>2</sup>C MODE

$\mathsf{I}^2\mathsf{C}$  has a 2-pin interface: the SCL pin is clock and the SDA pin is data.

# 15.1.3 I<sup>2</sup>C REGISTERS

I2CCON and I2CSTAT are control and status registers, respectively. The I2CCON register is readable and writable. The lower 6 bits of I2CSTAT are read only. The remaining bits of the I2CSTAT are read/write.

I2CRSR is the shift register used for shifting data, whereas I2CRCV is the buffer register to which data bytes are written, or from which data bytes are read. I2CRCV is the receive buffer as shown in Figure 15-1. I2CTRN is the transmit register to which bytes are written during a transmit operation, as shown in Figure 15-2.

The I2CADD register holds the slave address. A status bit, ADD10, indicates 10-bit Address mode. The I2CBRG acts as the Baud Rate Generator (BRG) reload value.

In receive operations, I2CRSR and I2CRCV together form a double-buffered receiver. When I2CRSR receives a complete byte, it is transferred to I2CRCV and an interrupt pulse is generated. During transmission, the I2CTRN is not double-buffered.

**Note:** Following a Restart condition in 10-bit mode, the user only needs to match the first 7-bit address.

# 15.12.3 BAUD RATE GENERATOR

In I<sup>2</sup>C Master mode, the reload value for the BRG is located in the I2CBRG register. When the BRG is loaded with this value, the BRG counts down to '0' and stops until another reload has taken place. If clock arbitration is taking place, for instance, the BRG is reloaded when the SCL pin is sampled high.

As per the I<sup>2</sup>C standard, FSCK may be 100 kHz or 400 kHz. However, the user can specify any baud rate up to 1 MHz. I2CBRG values of '0' or '1' are illegal.

$I2CBRG = \left(\frac{FCY}{FSCK} - \frac{FCY}{1,111,111}\right) - 1$

# 15.12.4 CLOCK ARBITRATION

Clock arbitration occurs when the master deasserts the SCL pin (SCL allowed to float high) during any receive, transmit, or Restart/Stop condition. When the SCL pin is allowed to float high, the Baud Rate Generator is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of I2CBRG and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device.

#### 15.12.5 MULTI-MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-master operation support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high while another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the MI2CIF pulse and reset the master portion of the I<sup>2</sup>C port to its Idle state.

If a transmit was in progress when the bus collision occurred, the transmission is halted, the TBF flag is cleared, the SDA and SCL lines are deasserted and a value can now be written to I2CTRN. When the user services the  $I^2C$  master event Interrupt Service Routine, if the  $I^2C$  bus is free (i.e., the P bit is set), the user can resume communication by asserting a Start condition.

If a Start, Restart, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted, and the respective control bits in the I2CCON register are cleared to '0'. When the user services the bus collision Interrupt Service Routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins, and if a Stop condition occurs, the MI2CIF bit will be set.

A write to the I2CTRN will start the transmission of data at the first data bit regardless of where the transmitter left off when bus collision occurred.

In a multi-master environment, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$ bus can be taken when the P bit is set in the I2CSTAT register, or the bus is Idle and the S and P bits are cleared.

# 15.13 I<sup>2</sup>C Module Operation During CPU Sleep and Idle Modes

## 15.13.1 I<sup>2</sup>C OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shutdown and stay at logic '0'. If Sleep occurs in the middle of a transmission and the state machine is partially into a transmission as the clocks stop, then the transmission is aborted. Similarly, if Sleep occurs in the middle of a reception, then the reception is aborted.

# 15.13.2 I<sup>2</sup>C OPERATION DURING CPU IDLE MODE

For the I<sup>2</sup>C, the I2CSIDL bit selects if the module will stop on Idle or continue on Idle. If I2CSIDL = 0, the module will continue operation on assertion of the Idle mode. If I2CSIDL = 1, the module will stop on Idle.

# 16.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART) MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the Universal Asynchronous Receiver Transmitter communications module.

# 16.1 UART Module Overview

The key features of the UART module are:

- Full-duplex, 8 or 9-bit data communication

- Even, odd or no parity options (for 8-bit data)

- · One or two Stop bits

- Fully integrated Baud Rate Generator with 16-bit prescaler

- Baud rates range from 38 bps to 1.875 Mbps at a 30 MHz instruction rate

- · 4-word deep transmit data buffer

- · 4-word deep receive data buffer

- · Parity, framing and buffer overrun error detection

- Support for interrupt only on address detect (9th bit = 1)

- Separate transmit and receive interrupts

- Loopback mode for diagnostic support

#### Internal Data Bus Control and Status bits Write Write Transmit Control UTX8 UxTXREG Low Byte - Control TSR - Control Buffer - Generate Flags Generate Interrupt Load TSR UxTXIF UTXBRK Data Transmit Shift Register (UxTSR) '0' (Start) UxTX -'1' (Stop) 16x Baud Clock Parity 16 Divider Parity Generator from Baud Rate Generator Control Signals Note: x = 1 or 2.

### FIGURE 16-1: UART TRANSMITTER BLOCK DIAGRAM

NOTES:

#### REGISTER 20-2: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0      | U-0   | U-0   | U-0   |  |  |  |

|--------|-----|-----|-----|----------|-------|-------|-------|--|--|--|

| —      | —   | —   | —   |          | —     | —     | —     |  |  |  |

| bit 15 |     |     |     |          |       |       | bit 8 |  |  |  |

|        |     |     |     |          |       |       |       |  |  |  |

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |  |  |  |

| —      | —   | —   | —   | TUN<3:0> |       |       |       |  |  |  |

|        |     |     |     |          |       |       | bit 0 |  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15 -4 Unimplemented: Read as '0'

bit 3-0 **TUN<3:0>:** Lower two bits of TUN field. The four bit field specified by TUN<3:0> specifies the user tuning capability for the internal fast RC oscillator (nominal 7.37 MHz).

| 0111 = Maximum Frequency                                               |

|------------------------------------------------------------------------|

| 0110 =                                                                 |

| 0101 =                                                                 |

| 0100 =                                                                 |

| 0011 =                                                                 |

| 0010 =                                                                 |

| 0001 =                                                                 |

| 0000 = Center Frequency, Oscillator is running at calibrated frequency |

| 1111 =                                                                 |

| 1110 =                                                                 |

| 1101 =                                                                 |

| 1100 =                                                                 |

| 1011 =                                                                 |

| 1010 =                                                                 |

| 1001 =                                                                 |

| 1000 = Minimum Frequency                                               |

|                                                                        |

| Field                                                                                                                                                                                                                                                                          | Description                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Wb                                                                                                                                                                                                                                                                             | Base W register ∈ {W0W15}                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Wd                                                                                                                                                                                                                                                                             | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                                                                                                                                                                                    |  |  |  |  |  |  |

| Wdo                                                                                                                                                                                                                                                                            | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] }                                                                                                                                                                 |  |  |  |  |  |  |

| Wm,Wn                                                                                                                                                                                                                                                                          | Dividend, Divisor working register pair (direct addressing)                                                                                                                                                                                          |  |  |  |  |  |  |

| Wm*Wm                                                                                                                                                                                                                                                                          | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                        |  |  |  |  |  |  |

| Wm*Wn                                                                                                                                                                                                                                                                          | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                        |  |  |  |  |  |  |

| Wn                                                                                                                                                                                                                                                                             | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                |  |  |  |  |  |  |

| Wnd                                                                                                                                                                                                                                                                            | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                                    |  |  |  |  |  |  |

| Wns                                                                                                                                                                                                                                                                            | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                         |  |  |  |  |  |  |

| WREG                                                                                                                                                                                                                                                                           | W0 (working register used in file register instructions)                                                                                                                                                                                             |  |  |  |  |  |  |

| Ws                                                                                                                                                                                                                                                                             | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                         |  |  |  |  |  |  |

| Wso                                                                                                                                                                                                                                                                            | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                      |  |  |  |  |  |  |

| Wx                                                                                                                                                                                                                                                                             | X data space prefetch address register for DSP instructions<br>∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2,<br>[W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2,<br>[W9 + W12],none} |  |  |  |  |  |  |

| Wxd                                                                                                                                                                                                                                                                            | X data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                             |  |  |  |  |  |  |

| Wy     Y data space prefetch address register for DSP instructions       ∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - =       [W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - =       [W11 + W12], none} |                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Wyd                                                                                                                                                                                                                                                                            | Y data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                             |  |  |  |  |  |  |

## TABLE 21-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

### TABLE 23-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACTERISTICS |               |     | Standard Operating Conditions: 2.5V to 5.5V     (unless otherwise stated)     Operating temperature   -40°C ≤TA ≤+85°C for Industrial     -40°C ≤TA ≤+125°C for Extended |       |      |                                                   |  |  |

|--------------------|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|---------------------------------------------------|--|--|

| Parameter<br>No.   | Typical       | Мах | Units                                                                                                                                                                    |       |      | Conditions                                        |  |  |

| Power Down (       | Current (IPD) |     |                                                                                                                                                                          |       |      |                                                   |  |  |

| DC60a              | 0.5           | _   | μA                                                                                                                                                                       | 25°C  |      |                                                   |  |  |

| DC60b              | 1             | 40  | μA                                                                                                                                                                       | 85°C  | 3.3V |                                                   |  |  |

| DC60c              | 24            | 65  | μA                                                                                                                                                                       | 125°C |      | Base Power Down Current <sup>(1)</sup>            |  |  |

| DC60e              | 0.7           | _   | μA                                                                                                                                                                       | 25°C  |      | Base Power Down Currents?                         |  |  |

| DC60f              | 4             | 55  | μA                                                                                                                                                                       | 85°C  | 5V   |                                                   |  |  |

| DC60g              | 35            | 90  | μA                                                                                                                                                                       | 125°C |      |                                                   |  |  |

| DC61a              | 9             | 20  | μA                                                                                                                                                                       | 25°C  |      |                                                   |  |  |

| DC61b              | 9             | 20  | μA                                                                                                                                                                       | 85°C  | 3.3V |                                                   |  |  |

| DC61c              | 8             | 20  | μA                                                                                                                                                                       | 125°C |      | - Watchdog Timer Current: ∆IwDT <sup>(2)</sup>    |  |  |

| DC61e              | 18            | 40  | μA                                                                                                                                                                       | 25°C  |      |                                                   |  |  |

| DC61f              | 16            | 40  | μA                                                                                                                                                                       | 85°C  | 5V   |                                                   |  |  |

| DC61g              | 15            | 40  | μA                                                                                                                                                                       | 125°C |      |                                                   |  |  |

| DC62a              | 4             | 10  | μA                                                                                                                                                                       | 25°C  |      |                                                   |  |  |

| DC62b              | 5             | 10  | μA                                                                                                                                                                       | 85°C  | 3.3V |                                                   |  |  |

| DC62c              | 4             | 10  | μA                                                                                                                                                                       | 125°C |      |                                                   |  |  |

| DC62e              | 4             | 15  | μA                                                                                                                                                                       | 25°C  |      | — Timer 1 w/32 kHz Crystal: ∆I⊤i32 <sup>(2)</sup> |  |  |

| DC62f              | 6             | 15  | μA                                                                                                                                                                       | 85°C  | 5V   |                                                   |  |  |

| DC62g              | 5             | 15  | μA                                                                                                                                                                       | 125°C |      |                                                   |  |  |

| DC63a              | 30            | 55  | μA                                                                                                                                                                       | 25°C  |      |                                                   |  |  |

| DC63b              | 34            | 55  | μA                                                                                                                                                                       | 85°C  | 3.3V |                                                   |  |  |

| DC63c              | 35            | 55  | μA                                                                                                                                                                       | 125°C |      | BOR On: ∆IBOR <sup>(2)</sup>                      |  |  |

| DC63e              | 36            | 60  | μA                                                                                                                                                                       | 25°C  |      | BOR ON: AIBOR-                                    |  |  |

| DC63f              | 39            | 60  | μA                                                                                                                                                                       | 85°C  | 5V   |                                                   |  |  |

| DC63g              | 40            | 60  | μA                                                                                                                                                                       | 125°C | 1    |                                                   |  |  |

| DC66a              | 20            | 35  | μA                                                                                                                                                                       | 25°C  |      |                                                   |  |  |

| DC66b              | 22            | 35  | μA                                                                                                                                                                       | 85°C  | 3.3V |                                                   |  |  |

| DC66c              | 23            | 35  | μA                                                                                                                                                                       | 125°C | 1    | Low Voltage Detect. they (2)                      |  |  |

| DC66e              | 24            | 40  | μA                                                                                                                                                                       | 25°C  |      | Low Voltage Detect: ∆ILvD <sup>(2)</sup>          |  |  |

| DC66f              | 26            | 40  | μA                                                                                                                                                                       | 85°C  | 5V   |                                                   |  |  |

| DC66g              | 26            | 40  | μA                                                                                                                                                                       | 125°C | 1    |                                                   |  |  |

**Note 1:** Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled high. LVD, BOR, WDT, etc. are all switched off.

**2:** The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

| AC CHARACTERISTICS |        |                                   | Standard Operating Conditions: 2.5V to 5.5V     (unless otherwise stated)     Operating temperature   -40°C ≤TA ≤+85°C for Industrial     -40°C ≤TA ≤+125°C for Extended |                    |                     |       |                                   |  |  |

|--------------------|--------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|-------|-----------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>     | Min                                                                                                                                                                      | Тур <sup>(2)</sup> | Max                 | Units | Conditions                        |  |  |

| OS50               | Fplli  | PLL Input Frequency Range         |                                                                                                                                                                          | _                  | 10                  | MHz   | EC with 4x PLL                    |  |  |

|                    |        |                                   | 4                                                                                                                                                                        | -                  | 10                  | MHz   | EC with 8x PLL                    |  |  |

|                    |        |                                   | 4                                                                                                                                                                        | -                  | 7.5 <sup>(4)</sup>  | MHz   | EC with 16x PLL                   |  |  |

|                    |        |                                   | 4                                                                                                                                                                        | —                  | 10                  | MHz   | XT with 4x PLL                    |  |  |

|                    |        |                                   | 4                                                                                                                                                                        | —                  | 10                  | MHz   | XT with 8x PLL                    |  |  |

|                    |        |                                   | 4                                                                                                                                                                        | —                  | 7.5 <sup>(4)</sup>  | MHz   | XT with 16x PLL                   |  |  |

|                    |        |                                   | 5 <sup>(3)</sup>                                                                                                                                                         | —                  | 10                  | MHz   | HS/2 with 4x PLL                  |  |  |

|                    |        |                                   | 5 <sup>(3)</sup>                                                                                                                                                         | —                  | 10                  | MHz   | HS/2 with 8x PLL                  |  |  |

|                    |        |                                   | 5 <sup>(3)</sup>                                                                                                                                                         | —                  | 7.5 <sup>(4)</sup>  | MHz   | HS/2 with 16x PLL                 |  |  |

|                    |        |                                   | 4                                                                                                                                                                        | —                  | 8.33 <sup>(3)</sup> | MHz   | HS/3 with 4x PLL                  |  |  |

|                    |        |                                   | 4                                                                                                                                                                        | —                  | 8.33 <sup>(3)</sup> | MHz   | HS/3 with 8x PLL                  |  |  |

|                    |        |                                   | 4                                                                                                                                                                        | -                  | 7.5 <sup>(4)</sup>  | MHz   | HS/3 with 16x PLL                 |  |  |

| OS51               | Fsys   | On-Chip PLL Output <sup>(2)</sup> | 16                                                                                                                                                                       |                    | 120                 | MHz   | EC, XT, HS/2, HS/3 modes with PLL |  |  |

| OS52               | TLOC   | PLL Start-up Time (Lock Tim       | e) —                                                                                                                                                                     | 20                 | 50                  | μs    |                                   |  |  |

#### TABLE 23-15: PLL CLOCK TIMING SPECIFICATIONS (VDD = 2.5 TO 5.5 V)

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** Limited by oscillator frequency range.

- 4: Limited by device operating frequency range.

#### TABLE 23-16: PLL JITTER

| AC CHAI      | RACTERISTICS   | (unless | Standard Operating Conditions: 2.5V to 5.5V     (unless otherwise stated)     Operating temperature   -40°C ≤TA ≤+85°C for Industrial     -40°C ≤TA ≤+125°C for Extended |       |       |                   |                   |  |  |

|--------------|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------------------|-------------------|--|--|

| Param<br>No. | Characteristic | Min     | Typ <sup>(1)</sup>                                                                                                                                                       | Max   | Units | Conditions        |                   |  |  |

| OS61         | x4 PLL         | —       | 0.251                                                                                                                                                                    | 0.413 | %     | -40°C ≤TA ≤+85°C  | VDD = 3.0 to 3.6V |  |  |

|              |                |         | 0.251                                                                                                                                                                    | 0.413 | %     | -40°C ≤TA ≤+125°C | VDD = 3.0 to 3.6V |  |  |

|              |                |         | 0.256                                                                                                                                                                    | 0.47  | %     | -40°C ≤TA ≤+85°C  | VDD = 4.5 to 5.5V |  |  |

|              |                |         | 0.256                                                                                                                                                                    | 0.47  | %     | -40°C ≤TA ≤+125°C | VDD = 4.5 to 5.5V |  |  |

|              | x8 PLL         | _       | 0.355                                                                                                                                                                    | 0.584 | %     | -40°C ≤TA ≤+85°C  | VDD = 3.0 to 3.6V |  |  |

|              |                | —       | 0.355                                                                                                                                                                    | 0.584 | %     | -40°C ≤TA ≤+125°C | VDD = 3.0 to 3.6V |  |  |

|              |                | —       | 0.362                                                                                                                                                                    | 0.664 | %     | -40°C ≤TA ≤+85°C  | VDD = 4.5 to 5.5V |  |  |

|              |                | _       | 0.362                                                                                                                                                                    | 0.664 | %     | -40°C ≤TA ≤+125°C | VDD = 4.5 to 5.5V |  |  |

|              | x16 PLL        |         | 0.67                                                                                                                                                                     | 0.92  | %     | -40°C ≤TA ≤+85°C  | VDD = 3.0 to 3.6V |  |  |

|              |                |         | 0.632                                                                                                                                                                    | 0.956 | %     | -40°C ≤TA ≤+85°C  | VDD = 4.5 to 5.5V |  |  |

|              |                | _       | 0.632                                                                                                                                                                    | 0.956 | %     | -40°C ≤TA ≤+125°C | VDD = 4.5 to 5.5V |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

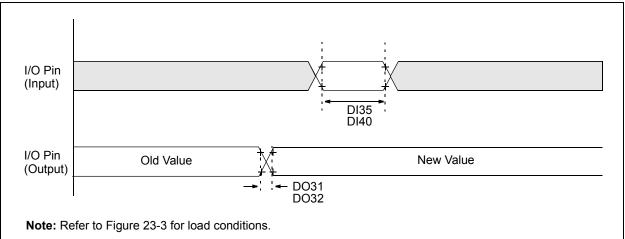

| TABLE 23-20: CL | LKOUT AND I/O TI | MING REQUIREMENTS |

|-----------------|------------------|-------------------|

|-----------------|------------------|-------------------|

| AC CHARACTERISTICS (unless of |        |                                     | Standard Open<br>(unless otherw<br>Operating temp | vise state | e <b>d)</b><br>-40°C ≤⊺ |     | C for Indu |            |

|-------------------------------|--------|-------------------------------------|---------------------------------------------------|------------|-------------------------|-----|------------|------------|

| Param<br>No.                  | Symbol | Characteristic <sup>(1)(2)(3)</sup> |                                                   | Min        | Typ <sup>(4)</sup>      | Max | Units      | Conditions |

| DO31                          | TioR   | Port output rise time               |                                                   | _          | 7                       | 20  | ns         |            |

| DO32                          | TIOF   | Port output fall time               |                                                   | —          | 7                       | 20  | ns         |            |

| DI35                          | TINP   | INTx pin high or low                | time (output)                                     | 20         | —                       |     | ns         |            |

| DI40                          | Trbp   | CNx high or low time                | CNx high or low time (input)                      |            | _                       | _   | ns         |            |

Note 1: These parameters are asynchronous events not related to any internal clock edges

2: Measurements are taken in RC mode and EC mode where CLKOUT output is 4 x Tosc.

3: These parameters are characterized but not tested in manufacturing.

4: Data in "Typ" column is at 5V, 25°C unless otherwise stated.

# FIGURE 23-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

## TABLE 23-34: SPI MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                     | Standard Operating Conditions: 2.5V to 5.5V     (unless otherwise stated)     Operating temperature   -40°C ≤TA ≤+85°C for Industrial     -40°C ≤TA ≤+125°C for Extended |                    |     |       |                    |

|--------------------|-----------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                       | Min                                                                                                                                                                      | Тур <sup>(2)</sup> | Max | Units | Conditions         |

| SP70               | TscL                  | SCKx Input Low Time                                 | 30                                                                                                                                                                       | _                  |     | ns    |                    |

| SP71               | TscH                  | SCKx Input High Time                                | 30                                                                                                                                                                       | _                  |     | ns    |                    |

| SP72               | TscF                  | SCKx Input Fall Time <sup>(3)</sup>                 |                                                                                                                                                                          | 10                 | 25  | ns    |                    |

| SP73               | TscR                  | SCKx Input Rise Time <sup>(3)</sup>                 |                                                                                                                                                                          | 10                 | 25  | ns    |                    |

| SP30               | TdoF                  | SDOx Data Output Fall Time <sup>(3)</sup>           | —                                                                                                                                                                        | _                  | _   | ns    | See parameter DO32 |

| SP31               | TdoR                  | SDOx Data Output Rise Time <sup>(3)</sup>           | —                                                                                                                                                                        | —                  | _   | ns    | See parameter DO31 |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge           | —                                                                                                                                                                        | _                  | 30  | ns    |                    |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge          | 20                                                                                                                                                                       | _                  | _   | ns    |                    |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge           | 20                                                                                                                                                                       | _                  | _   | ns    |                    |

| SP50               | TssL2scH,<br>TssL2scL | SSx↓to SCKx↓or SCKx↑ input                          | 120                                                                                                                                                                      | _                  |     | ns    |                    |

| SP51               | TssH2doZ              | SS↑ to SDOx Output<br>High-impedance <sup>(4)</sup> | 10                                                                                                                                                                       | —                  | 50  | ns    |                    |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx↑ after SCKx Edge                                | 1.5 Tcy + 40                                                                                                                                                             | —                  | _   | ns    |                    |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge            | —                                                                                                                                                                        | —                  | 50  | ns    |                    |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCK is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI pins.

# TABLE 23-35: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA       | RACTER  | ISTICS           |                           | Standard Operating Conditions: 2.5V to 5.5V     (unless otherwise stated)     Operating temperature   -40°C ≤TA ≤+85°C for Industrial     -40°C ≤TA ≤+125°C for Extended |      |       |                        |  |  |

|--------------|---------|------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------------------|--|--|

| Param<br>No. | Symbol  | Charac           | teristic                  | Min <sup>(1)</sup>                                                                                                                                                       | Max  | Units | Conditions             |  |  |

| IM10         | TLO:SCL | Clock Low Time   | 100 kHz mode              | Tcy / 2 (BRG + 1)                                                                                                                                                        | —    | μs    |                        |  |  |

|              |         |                  | 400 kHz mode              | TCY / 2 (BRG + 1)                                                                                                                                                        | _    | μs    |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY / 2 (BRG + 1)                                                                                                                                                        | —    | μs    |                        |  |  |

| IM11         | THI:SCL | Clock High Time  | 100 kHz mode              | Tcy / 2 (BRG + 1)                                                                                                                                                        | —    | μs    |                        |  |  |

|              |         |                  | 400 kHz mode              | Tcy / 2 (BRG + 1)                                                                                                                                                        | —    | μs    |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY / 2 (BRG + 1)                                                                                                                                                        | —    | μs    |                        |  |  |

| IM20         | TF:SCL  | SDA and SCL      | 100 kHz mode              | —                                                                                                                                                                        | 300  | ns    | CB is specified to be  |  |  |

|              |         | Fall Time        | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                              | 300  | ns    | from 10 to 400 pF      |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                        | 100  | ns    |                        |  |  |

| IM21         | TR:SCL  | SDA and SCL      | 100 kHz mode              | _                                                                                                                                                                        | 1000 | ns    | CB is specified to be  |  |  |

|              |         | Rise Time        | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                              | 300  | ns    | from 10 to 400 pF      |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                        | 300  | ns    |                        |  |  |

| IM25         | TSU:DAT | Data Input       | 100 kHz mode              | 250                                                                                                                                                                      | _    | ns    |                        |  |  |

|              |         | Setup Time       | 400 kHz mode              | 100                                                                                                                                                                      | —    | ns    |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                        | _    | ns    |                        |  |  |

| IM26         | THD:DAT | Data Input       | 100 kHz mode              | 0                                                                                                                                                                        | _    | ns    |                        |  |  |

|              |         | Hold Time        | 400 kHz mode              | 0                                                                                                                                                                        | 0.9  | μs    |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                        | _    | ns    |                        |  |  |

| IM30         | TSU:STA | Start Condition  | 100 kHz mode              | Tcy / 2 (BRG + 1)                                                                                                                                                        | —    | μs    | Only relevant for      |  |  |

|              |         | Setup Time       | 400 kHz mode              | Tcy / 2 (BRG + 1)                                                                                                                                                        | —    | μs    | repeated Start         |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY / 2 (BRG + 1)                                                                                                                                                        | _    | μs    | condition              |  |  |

| IM31         | THD:STA | Start Condition  | 100 kHz mode              | Tcy / 2 (BRG + 1)                                                                                                                                                        | _    | μs    | After this period the  |  |  |

|              |         | Hold Time        | 400 kHz mode              | Tcy / 2 (BRG + 1)                                                                                                                                                        | —    | μs    | first clock pulse is   |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy / 2 (BRG + 1)                                                                                                                                                        | —    | μs    | generated              |  |  |

| IM33         | Tsu:sto | Stop Condition   | 100 kHz mode              | Tcy / 2 (BRG + 1)                                                                                                                                                        | —    | μs    |                        |  |  |

|              |         | Setup Time       | 400 kHz mode              | Tcy / 2 (BRG + 1)                                                                                                                                                        | —    | μs    |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy / 2 (BRG + 1)                                                                                                                                                        | —    | μs    |                        |  |  |

| IM34         | THD:STO | Stop Condition   | 100 kHz mode              | Tcy / 2 (BRG + 1)                                                                                                                                                        | —    | ns    |                        |  |  |

|              |         | Hold Time        | 400 kHz mode              | Tcy / 2 (BRG + 1)                                                                                                                                                        | —    | ns    |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY / 2 (BRG + 1)                                                                                                                                                        | _    | ns    |                        |  |  |

| IM40         | TAA:SCL | Output Valid     | 100 kHz mode              | —                                                                                                                                                                        | 3500 | ns    |                        |  |  |

|              |         | From Clock       | 400 kHz mode              | _                                                                                                                                                                        | 1000 | ns    |                        |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                        |      | ns    |                        |  |  |

| IM45         | TBF:SDA | Bus Free Time    | 100 kHz mode              | 4.7                                                                                                                                                                      |      | μs    | Time the bus must be   |  |  |

|              |         |                  | 400 kHz mode              | 1.3                                                                                                                                                                      | _    | μs    | free before a new      |  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                        |      | μs    | transmission can start |  |  |

| IM50         | Св      | Bus Capacitive L |                           | _                                                                                                                                                                        | 400  | pF    |                        |  |  |

Note 1: BRG is the value of the I<sup>2</sup>C<sup>™</sup> Baud Rate Generator. Refer to Section 21. "Inter-Integrated Circuit™ (I<sup>2</sup>C)" (DS70046) in the "*dsPIC30F Family Reference Manual*".

2: Maximum pin capacitance = 10 pF for all I<sup>2</sup>C pins (for 1 MHz mode only).

# Revision E (February 2011)

This revision includes minor typographical and formatting changes throughout the data sheet text.

The major changes are referenced by their respective section in Table A-1.

### TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                 | Update Description                                                                                                                                                        |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 20.0 "System<br>Integration"         | Added a shaded note on OSCTUN functionality in <b>Section 20.2.5 "Fast RC Oscillator (FRC)</b> ".                                                                         |

| Section 23.0 "Electrical<br>Characteristics" | Updated the maximum MIPS for the Operating MIPS vs. Voltage VDD range of 3.0-3.6V for dsPIC30F601XA-20I and dsPIC30F601XA-30I devices (see Table 23-1).                   |

|                                              | Added Operating Current (IDD) parameters DC27a and DC27b (see Table 23-5).                                                                                                |

|                                              | Added Idle Current (IIDLE) parameters DC47a and DC47b (see Table 23-6).                                                                                                   |

|                                              | Updated the maximum value for parameter DI19 and the minimum value for parameter DI29 in the I/O Pin Input Specifications (see Table 23-8).                               |

|                                              | Removed parameter D136 and updated the minimum, typical, maximum, and conditions for parameters D122 and D134 in the Program and EEPROM specifications (see Table 23-12). |