Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 30 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 68                                                                             |

| Program Memory Size        | 132KB (44K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 2K x 8                                                                         |

| RAM Size                   | 6K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 16x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6013a-30i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

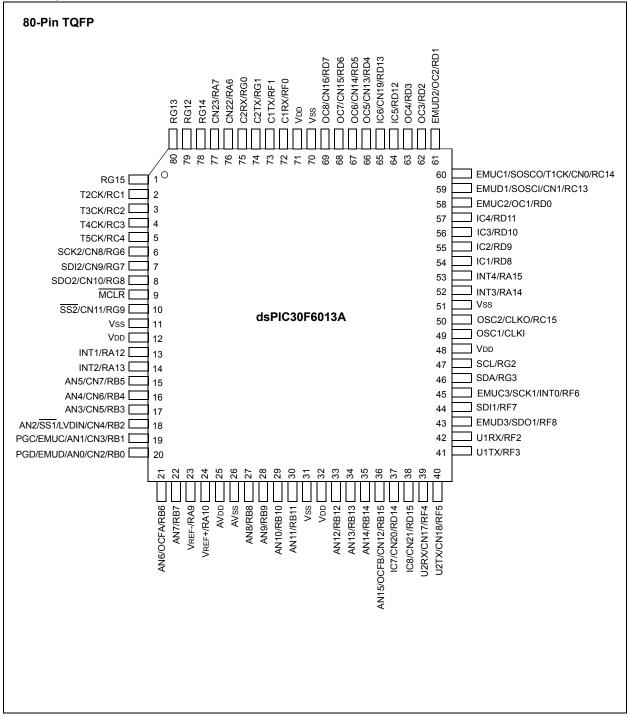

#### Pin Diagrams (Continued)

#### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

This document contains specific information for the dsPIC30F6011A/6012A/6013A/6014A Digital Signal Controller (DSC) devices. The dsPIC30F devices contain extensive Digital Signal Processor (DSP) functionality within a high-performance 16-bit microcontroller (MCU) architecture. Figure 1-1 and Figure 1-2 show device block diagrams for dsPIC30F6011A/6012A and dsPIC30F6013A/6014A, respectively.

#### 3.0 MEMORY ORGANIZATION

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

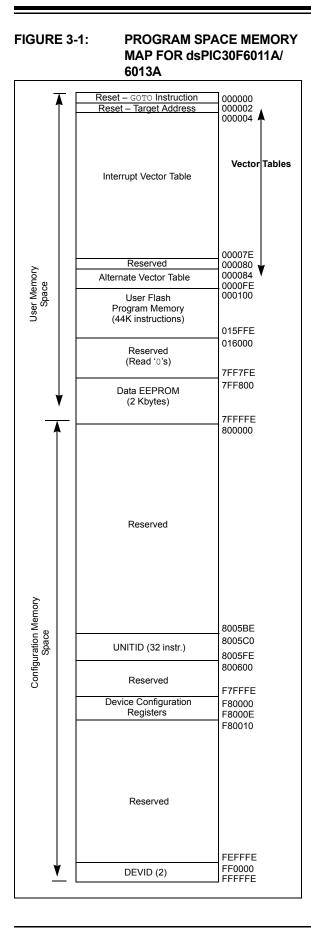

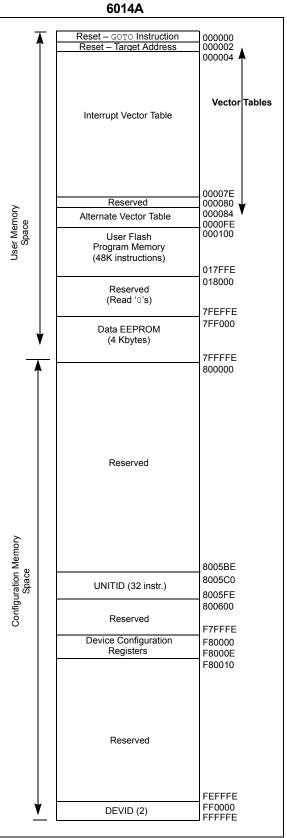

#### 3.1 Program Address Space

The program address space is 4M instruction words. It is addressable by a 24-bit value from either the 23-bit PC, table instruction Effective Address (EA), or data space EA, when program space is mapped into data space as defined by Table 3-1. Note that the program space address is incremented by two between successive program words in order to provide compatibility with data space addressing. User program space access is restricted to the lower 4M instruction word address range (0x000000 to 0x7FFFFE) for all accesses other than TBLRD/TBLWT, which use TBLPAG<7> to determine user or configuration space access. In Table 3-1, Program Space Address Construction, bit 23 allows access to the Device ID, the Unit ID and the configuration bits. Otherwise, bit 23 is always clear.

Note: The address map shown in Figure 3-1 and Figure 3-2 is conceptual, and the actual memory configuration may vary across individual devices depending on available memory.

## dsPIC30F6011A/6012A/6013A/6014A

#### FIGURE 3-2: PROGRAM SPACE MEMORY MAP FOR dsPIC30F6012A/

#### 3.2 Data Address Space

The core has two data spaces. The data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths.

#### 3.2.1 DATA SPACE MEMORY MAP

The data space memory is split into two blocks, X and Y data space. A key element of this architecture is that Y space is a subset of X space, and is fully contained within X space. In order to provide an apparent linear addressing space, X and Y spaces have contiguous addresses.

When executing any instruction other than one of the MAC class of instructions, the X block consists of the 64 Kbyte data address space (including all Y addresses). When executing one of the MAC class of instructions, the X block consists of the 64 Kbyte data address space excluding the Y address block (for data reads only). In other words, all other instructions regard the entire data memory as one composite address space. The MAC class instructions extract the Y address space from data space and address it using EAs sourced from W10 and W11. The remaining X data space is addressed using W8 and W9. Both address spaces are concurrently accessed only with the MAC class instructions.

The data space memory maps are shown in Figure 3-8 and Figure 3-9.

#### 3.2.2 DATA SPACES

The X data space is used by all instructions and supports all Addressing modes. There are separate read and write data buses. The X read data bus is the return data path for all instructions that view data space as combined X and Y address space. It is also the X address space data path for the dual operand read instructions (MAC class). The X write data bus is the only write path to data space for all instructions.

The X data space also supports Modulo Addressing for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing is only supported for writes to X data space.

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths. No writes occur across the Y bus. This class of instructions dedicates two W register pointers, W10 and W11, to always address Y data space, independent of X data space, whereas W8 and W9 always address X data space. Note that during accumulator write back, the data address space is considered a combination of X and Y data spaces, so the write occurs across the X bus. Consequently, the write can be to any address in the entire data space.

The Y data space can only be used for the data prefetch operation associated with the MAC class of instructions. It also supports Modulo Addressing for automated circular buffers. Of course, all other instructions can access the Y data address space through the X data path as part of the composite linear space.

The boundary between the X and Y data spaces is defined as shown in Figure 3-7 and Figure 3-8 and is not user programmable. Should an EA point to data outside its own assigned address space, or to a location outside physical memory, an all zero word/byte will be returned. For example, although Y address space is visible by all non-MAC instructions using any addressing mode, an attempt by a MAC instruction to fetch data from that space using W8 or W9 (X space pointers) will return 0x0000.

#### 5.1 Interrupt Priority

The user-assignable interrupt priority (IP<2:0>) bits for each individual interrupt source are located in the Least Significant 3 bits of each nibble within the IPCx register(s). Bit 3 of each nibble is not used and is read as a '0'. These bits define the priority level assigned to a particular interrupt by the user.

| Note: | The user-assignable priority levels start at |

|-------|----------------------------------------------|

|       | 0 as the lowest priority and level 7 as the  |

|       | highest priority.                            |

Since more than one interrupt request source may be assigned to a specific user-assigned priority level, a means is provided to assign priority within a given level. This method is called "Natural Order Priority" and is final.

Natural order priority is determined by the position of an interrupt in the vector table, and only affects interrupt operation when multiple interrupts with the same user-assigned priority become pending at the same time.

Table 5-1 lists the interrupt numbers and interrupt sources for the dsPIC DSC device and their associated vector numbers.

- **Note 1:** The natural order priority scheme has 0 as the highest priority and 53 as the lowest priority.

- **2:** The natural order priority number is the same as the INT number.

The ability for the user to assign every interrupt to one of seven priority levels implies that the user can assign a very high overall priority level to an interrupt with a low natural order priority. For example, the PLVD (Low-Voltage Detect) can be given a priority of 7. The INT0 (External Interrupt 0) may be assigned to priority level 1, thus giving it a very low effective priority.

| INT<br>Number | Vector<br>Number | Interrupt Source                         |

|---------------|------------------|------------------------------------------|

|               | Highest          | Natural Order Priority                   |

| 0             | 8                | INT0 – External Interrupt 0              |

| 1             | 9                | IC1 – Input Capture 1                    |

| 2             | 10               | OC1 – Output Compare 1                   |

| 3             | 11               | T1 – Timer1                              |

| 4             | 12               | IC2 – Input Capture 2                    |

| 5             | 13               | OC2 – Output Compare 2                   |

| 6             | 14               | T2 – Timer2                              |

| 7             | 15               | T3 – Timer3                              |

| 8             | 16               | SPI1                                     |

| 9             | 17               | U1RX – UART1 Receiver                    |

| 10            | 18               | U1TX – UART1 Transmitter                 |

| 11            | 19               | ADC – ADC Convert Done                   |

| 12            | 20               | NVM – NVM Write Complete                 |

| 13            | 21               | SI2C – I <sup>2</sup> C™ Slave Interrupt |

| 14            | 22               | MI2C – I <sup>2</sup> C Master Interrupt |

| 15            | 23               | Input Change Interrupt                   |

| 16            | 24               | INT1 – External Interrupt 1              |

| 17            | 25               | IC7 – Input Capture 7                    |

| 18            | 26               | IC8 – Input Capture 8                    |

| 19            | 27               | OC3 – Output Compare 3                   |

| 20            | 28               | OC4 – Output Compare 4                   |

| 21            | 29               | T4 – Timer4                              |

| 22            | 30               | T5 – Timer5                              |

| 23            | 31               | INT2 – External Interrupt 2              |

| 24            | 32               | U2RX – UART2 Receiver                    |

| 25            | 33               | U2TX – UART2 Transmitter                 |

| 26            | 34               | SPI2                                     |

| 27            | 35               | C1 – Combined IRQ for CAN1               |

| 28            | 36               | IC3 – Input Capture 3                    |

| 29            | 37               | IC4 – Input Capture 4                    |

| 30            | 38               | IC5 – Input Capture 5                    |

| 31            | 39               | IC6 – Input Capture 6                    |

| 32            | 40               | OC5 – Output Compare 5                   |

| 33            | 41               | OC6 – Output Compare 6                   |

| 34            | 42               | OC7 – Output Compare 7                   |

| 35            | 43               | OC8 – Output Compare 8                   |

| 36            | 44               | INT3 – External Interrupt 3              |

| 37            | 45               | INT4 – External Interrupt 4              |

| 38            | 46               | C2 – Combined IRQ for CAN2               |

| 39-40         | 47-48            | Reserved                                 |

| 41            | 49               | DCI – Codec Transfer Done <sup>(1)</sup> |

| 42            | 50               | LVD – Low-Voltage Detect                 |

| 43-53         | 51-61            | Reserved                                 |

|               | Lowest           | Natural Order Priority                   |

| Note 1:       | Reserved of      | on dsPIC30F6011A and dsPIC30F6013A       |

Note 1: Reserved on dsPIC30F6011A and dsPIC30F6013A because the DCI module is not available on these devices.

#### TABLE 5-1:INTERRUPT VECTOR TABLE

## dsPIC30F6011A/6012A/6013A/6014A

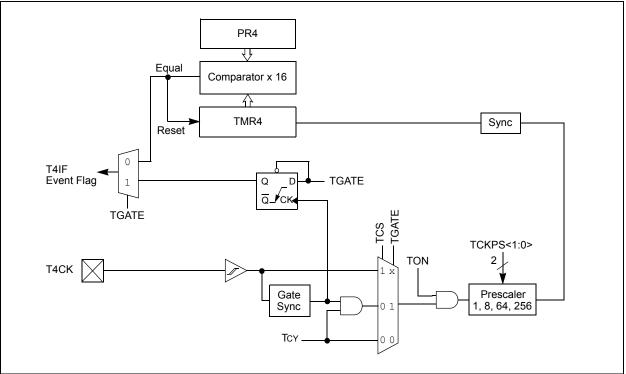

#### FIGURE 11-2: 16-BIT TIMER4 BLOCK DIAGRAM

#### 12.1.2 CAPTURE BUFFER OPERATION

Each capture channel has an associated FIFO buffer which is four 16-bit words deep. There are two status flags which provide status on the FIFO buffer:

- ICBFNE Input Capture Buffer Not Empty

- ICOV Input Capture Overflow

The ICBFNE will be set on the first input capture event and remain set until all capture events have been read from the FIFO. As each word is read from the FIFO, the remaining words are advanced by one position within the buffer.

In the event that the FIFO is full with four capture events and a fifth capture event occurs prior to a read of the FIFO, an overflow condition will occur and the ICOV bit will be set to a logic '1'. The fifth capture event is lost and is not stored in the FIFO. No additional events will be captured until all four events have been read from the buffer.

If a FIFO read is performed after the last read and no new capture event has been received, the read will yield indeterminate results.

### 12.1.3 TIMER2 AND TIMER3 SELECTION MODE

The input capture module consists of up to 8 input capture channels. Each channel can select between one of two timers for the time base, Timer2 or Timer3.

Selection of the timer resource is accomplished through SFR bit, ICTMR (ICxCON<7>). Timer3 is the default timer resource available for the input capture module.

#### 12.1.4 HALL SENSOR MODE

When the input capture module is set for capture on every edge, rising and falling, ICM<2:0> = 001, the following operations are performed by the input capture logic:

- The input capture interrupt flag is set on every edge, rising and falling.

- The interrupt on Capture mode setting bits, ICI<1:0>, is ignored since every capture generates an interrupt.

- A capture overflow condition is not generated in this mode.

#### 12.2 Input Capture Operation During Sleep and Idle Modes

An input capture event will generate a device wake-up or interrupt, if enabled, if the device is in CPU Idle or Sleep mode.

Independent of the timer being enabled, the input capture module will wake-up from the CPU Sleep or Idle mode when a capture event occurs if ICM<2:0> = 111and the interrupt enable bit is asserted. The same wakeup can generate an interrupt if the conditions for processing the interrupt have been satisfied. The wake-up feature is useful as a method of adding extra external pin interrupts.

#### 12.2.1 INPUT CAPTURE IN CPU SLEEP MODE

CPU Sleep mode allows input capture module operation with reduced functionality. In the CPU Sleep mode, the ICI<1:0> bits are not applicable and the input capture module can only function as an external interrupt source.

The capture module must be configured for interrupt only on rising edge (ICM<2:0> = 111) in order for the input capture module to be used while the device is in Sleep mode. The prescale settings of 4:1 or 16:1 are not applicable in this mode.

### 12.2.2 INPUT CAPTURE IN CPU IDLE MODE

CPU Idle mode allows input capture module operation with full functionality. In the CPU Idle mode, the Interrupt mode selected by the ICI<1:0> bits is applicable, as well as the 4:1 and 16:1 capture prescale settings which are defined by control bits ICM<2:0>. This mode requires the selected timer to be enabled. Moreover, the ICSIDL bit must be asserted to a logic '0'.

If the input capture module is defined as ICM<2:0> = 111 in CPU Idle mode, the input capture pin will serve only as an external interrupt pin.

#### 12.3 Input Capture Interrupts

The input capture channels have the ability to generate an interrupt based upon the selected number of capture events. The selection number is set by control bits ICI<1:0> (ICxCON<6:5>).

Each channel provides an interrupt flag (ICxIF) bit. The respective capture channel interrupt flag is located in the corresponding IFSx status register.

Enabling an interrupt is accomplished via the respective capture channel interrupt enable (ICxIE) bit. The capture interrupt enable bit is located in the corresponding IEC control register.

| SFR Name Addr. Bit 15 |   |          |          |          |        |        |        |          |           |                                     |        |       |        |       |          |       |                     |

|-----------------------|---|----------|----------|----------|--------|--------|--------|----------|-----------|-------------------------------------|--------|-------|--------|-------|----------|-------|---------------------|

| 0010                  |   | Bit 14 B | Bit 13 E | Bit 12 E | Bit 11 | Bit 10 | Bit 9  | Bit 8    | Bit 7     | Bit 6                               | Bit 5  | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | Reset State         |

| 0180                  |   |          |          |          |        |        | Output | Compare  | 1 Secon   | Output Compare 1 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 0182                  |   |          |          |          |        |        | Out    | out Comp | are 1 Ma  | Output Compare 1 Main Register      | _      |       |        |       |          |       | 0000 0000 0000 0000 |

| 0184 —                |   | 0        | OCSIDL   |          |        | 1      | 1      |          | Ι         |                                     | Ι      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 0186                  |   |          |          |          |        |        | Output | Compare  | 2 Secon   | Output Compare 2 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 0188                  |   |          |          |          |        |        | Out    | out Comp | are 2 Ma  | Output Compare 2 Main Register      | _      |       |        |       |          |       | 0000 0000 0000 0000 |

| 018A —                |   | 0        | OCSIDL   |          |        | 1      | 1      |          | Ι         |                                     | I      | OCFLT | OCTSE  |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 018C                  |   |          |          |          |        |        | Output | Compare  | 3 Secon   | Output Compare 3 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 018E                  |   |          |          |          |        |        | Out    | out Comp | are 3 Mai | Output Compare 3 Main Register      | L      |       |        |       |          |       | 0000 0000 0000 0000 |

| 0190 —                |   |          | OCSIDL   |          |        | 1      |        | I        | I         | I                                   | I      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 0192                  |   |          |          |          |        |        | Output | Compare  | 4 Secon   | Output Compare 4 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 0194                  |   |          |          |          |        |        | Out    | out Comp | are 4 Ma  | Output Compare 4 Main Register      | L      |       |        |       |          |       | 0000 0000 0000 0000 |

| 0196 —                |   | 00       | OCSIDL   |          |        | 1      | 1      |          | Ι         | I                                   | I      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 0198                  |   |          |          |          |        |        | Output | Compare  | 5 Secon   | Output Compare 5 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 019A                  |   |          |          |          |        |        | Out    | out Comp | are 5 Mai | Output Compare 5 Main Register      |        |       |        |       |          |       | 0000 0000 0000 0000 |

| 019C —                |   | 00       | OCSIDL   |          |        | 1      |        |          | Ι         |                                     | -      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 019E                  |   |          |          |          |        |        | Output | Compare  | 6 Secon   | Output Compare 6 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 01A0                  |   |          |          |          |        |        | Out    | out Comp | are 6 Mai | Output Compare 6 Main Register      | _      |       |        |       |          |       | 0000 0000 0000 0000 |

| 01A2 —                |   |          | OCSIDL   |          |        |        |        |          | Ι         |                                     | Ι      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 01A4                  |   |          |          |          |        |        | Output | Compare  | 7 Secon   | Output Compare 7 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 01A6                  |   |          |          |          |        |        | Out    | out Comp | are 7 Mai | Output Compare 7 Main Register      |        |       |        |       |          |       | 0000 0000 0000 0000 |

| 01A8 —                |   | 00       | OCSIDL   |          |        | 1      |        |          | Ι         |                                     | -      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| 01AA                  |   |          |          |          |        |        | Output | Compare  | 8 Secon   | Output Compare 8 Secondary Register | ster   |       |        |       |          |       | 0000 0000 0000 0000 |

| 01AC                  |   |          |          |          |        |        | Out    | out Comp | are 8 Ma  | Output Compare 8 Main Register      | -<br>- |       |        |       |          |       | 0000 0000 0000 0000 |

| 01AE                  | I | 00       | OCSIDL   |          |        |        |        | I        | Ι         | Ι                                   | -      | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000 0000 0000 0000 |

| TABLE 14-1: SPI1 REGISTER MAP <sup>(1)</sup> | 14-1:            | SPI1     | REGIS                     | TER M                                                                                                                                    | <b>дР</b> <sup>(1)</sup> |           |                     |            |             |                             |          |       |       |       |                   |        |        |                                                    |

|----------------------------------------------|------------------|----------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------|---------------------|------------|-------------|-----------------------------|----------|-------|-------|-------|-------------------|--------|--------|----------------------------------------------------|

| SFR<br>Name                                  | Addr.            | Bit 15   | Bit 14                    | Addr. Bit 15 Bit 14 Bit 13 Bit 12 Bit 11                                                                                                 | Bit 12                   | Bit 11    | Bit 10 Bit 9 Bit 8  | Bit 9      | Bit 8       | Bit 7 Bit 6                 | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 4 Bit 3 Bit 2 | Bit 1  | Bit 0  | Reset State                                        |

| SPI1STAT 0220 SPIEN                          | 0220             | SPIEN    | Ι                         | SPISIDL                                                                                                                                  | Ι                        | I         | I                   | I          | Ι           |                             | SPIROV   |       | I     | Ι     |                   | SPITBF | SPIRBF | SPITBF SPIRBF 0000 0000 0000                       |

| SPI1CON                                      | 0222             | Ι        | FRMEN                     | FRMEN SPIFSD                                                                                                                             | Ι                        | DISSDO    | MODE16 SMP CKE SSEN | SMP        | CKE         | SSEN                        | СКР      | MSTEN | SPRE2 | SPRE1 | SPRE0             | PPRE1  | PPRE0  | MSTEN SPREZ SPRE1 SPRE0 PPRE1 PPRE0 0000 0000 0000 |

| SPI1BUF 0224                                 | 0224             |          |                           |                                                                                                                                          |                          |           |                     | Trè        | ansmit an   | Transmit and Receive Buffer | Buffer   |       |       |       |                   |        |        | 0000 0000 0000 0000                                |

| Legend:<br>Note 1:                           | — = ∟<br>Refer t | unimplem | ented bit, i<br>PIC30F Fé | — = unimplemented bit, read as '0'<br>Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields. | ince Mari                | ual" (DS7 | 0046) for de        | scription: | s of regist | ter bit field               | <u>s</u> |       |       |       |                   |        |        |                                                    |

|                                              |                  |          |                           |                                                                                                                                          |                          |           |                     |            |             |                             |          |       |       |       |                   |        |        |                                                    |

# SPI2 REGISTER MAP<sup>(1)</sup> TABLE 14-2:

| SFR Name Addr. Bit 15 Bit 14 Bit 13 Bit 12 | Addr. | Bit 15 | Bit 14 | Bit 13       | Bit 12 | Bit 11 | Bit 10 Bit 9 | Bit 9 | Bit 8     | Bit 8 Bit 7 Bit 6           |        | Bit 5 | Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 | Bit 3 | Bit 2        |        | Bit 0  | Reset State                                                                            |

|--------------------------------------------|-------|--------|--------|--------------|--------|--------|--------------|-------|-----------|-----------------------------|--------|-------|-------------------------------|-------|--------------|--------|--------|----------------------------------------------------------------------------------------|

| SPI2STAT                                   | 0226  | SPIEN  | Ι      | SPISIDL      | Ι      | I      | I            | I     | Ι         | I                           | SPIROV |       | 1                             | Ι     | Ι            | SPITBF | SPIRBF | SPITBF SPIRBF 0000 0000 0000                                                           |

| SPI2CON                                    | 0228  |        | FRMEN  | FRMEN SPIFSD |        | DISSDO | MODE 16      | SMP   | CKE       | SSEN                        | СКР    | MSTEN | SPRE2                         | SPRE1 | <b>SPRE0</b> | PPRE1  | PPRE0  | DISSDO MODE16 SMP CKE SSEN CKP MSTEN SPRE2 SPRE1 SPRE0 PPRE1 PPRE0 0000 0000 0000 0000 |

| SPI2BUF                                    | 022A  |        |        |              |        |        |              | Tra   | nsmit and | Transmit and Receive Buffer | Buffer |       |                               |       |              |        |        | 0000 0000 0000 0000                                                                    |

— = unimplemented bit, read as '0'

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields. Legend: Note 1:

## dsPIC30F6011A/6012A/6013A/6014A

#### 15.4.1 10-BIT MODE SLAVE TRANSMISSION

Once a slave is addressed in this fashion with the full 10-bit address (we will refer to this state as "PRIOR\_ADDR\_MATCH"), the master can begin sending data bytes for a slave reception operation.

#### 15.4.2 10-BIT MODE SLAVE RECEPTION

Once addressed, the master can generate a Repeated Start, reset the high byte of the address and set the R\_W bit without generating a Stop bit, thus initiating a slave transmit operation.

#### 15.5 Automatic Clock Stretch

In the Slave modes, the module can synchronize buffer reads and write to the master device by clock stretching.

#### 15.5.1 TRANSMIT CLOCK STRETCHING

Both 10-bit and 7-bit Transmit modes implement clock stretching by asserting the SCLREL bit after the falling edge of the ninth clock, if the TBF bit is cleared, indicating the buffer is empty.

In Slave Transmit modes, clock stretching is always performed irrespective of the STREN bit.

Clock synchronization takes place following the ninth clock of the transmit sequence. If the device samples an ACK on the falling edge of the ninth clock and if the TBF bit is still clear, then the SCLREL bit is automatically cleared. The SCLREL being cleared to '0' will assert the SCL line low. The user's ISR must set the SCLREL bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the I2CTRN before the master device can initiate another transmit sequence.

- Note 1: If the user loads the contents of I2CTRN, setting the TBF bit before the falling edge of the ninth clock, the SCLREL bit will not be cleared and clock stretching will not occur.

- **2:** The SCLREL bit can be set in software, regardless of the state of the TBF bit.

#### 15.5.2 RECEIVE CLOCK STRETCHING

The STREN bit in the I2CCON register can be used to enable clock stretching in Slave Receive mode. When the STREN bit is set, the SCL pin will be held low at the end of each data receive sequence.

#### 15.5.3 CLOCK STRETCHING DURING 7-BIT ADDRESSING (STREN = 1)

When the STREN bit is set in Slave Receive mode, the SCL line is held low when the buffer register is full. The method for stretching the SCL output is the same for both 7 and 10-bit Addressing modes.

Clock stretching takes place following the ninth clock of the receive sequence. On the falling edge of the ninth clock at the end of the ACK sequence, if the RBF bit is set, the SCLREL bit is automatically cleared, forcing the SCL output to be held low. The user's ISR must set the SCLREL bit before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the I<sup>2</sup>CRCV before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring.

| Note 1: | If the user reads the contents of the    |

|---------|------------------------------------------|

|         | I2CRCV, clearing the RBF bit before the  |

|         | falling edge of the ninth clock, the     |

|         | SCLREL bit will not be cleared and clock |

|         | stretching will not occur.               |

2: The SCLREL bit can be set in software regardless of the state of the RBF bit. The user should be careful to clear the RBF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

#### 15.5.4 CLOCK STRETCHING DURING 10-BIT ADDRESSING (STREN = 1)

Clock stretching takes place automatically during the addressing sequence. Because this module has a register for the entire address, it is not necessary for the protocol to wait for the address to be updated.

After the address phase is complete, clock stretching will occur on each data receive or transmit sequence as was described earlier.

#### 15.6 Software Controlled Clock Stretching (STREN = 1)

When the STREN bit is '1', the SCLREL bit may be cleared by software to allow software to control the clock stretching. The logic will synchronize writes to the SCLREL bit with the SCL clock. Clearing the SCLREL bit will not assert the SCL output until the module detects a falling edge on the SCL output and SCL is sampled low. If the SCLREL bit is cleared by the user while the SCL line has been sampled low, the SCL output will be asserted (held low). The SCL output will remain low until the SCLREL bit is set, and all other devices on the I<sup>2</sup>C bus have deasserted SCL. This ensures that a write to the SCLREL bit will not violate the minimum high time requirement for SCL.

If the STREN bit is '0', a software write to the SCLREL bit will be disregarded and have no effect on the SCLREL bit.

#### 15.7 Interrupts

The I<sup>2</sup>C module generates two interrupt flags, MI2CIF (I<sup>2</sup>C Master Interrupt Flag) and SI2CIF (I<sup>2</sup>C Slave Interrupt Flag). The MI2CIF interrupt flag is activated on completion of a master message event. The SI2CIF interrupt flag is activated on detection of a message directed to the slave.

#### 15.8 Slope Control

The I<sup>2</sup>C standard requires slope control on the SDA and SCL signals for Fast mode (400 kHz). The control bit, DISSLW, enables the user to disable slew rate control if desired. It is necessary to disable the slew rate control for 1 MHz mode.

#### 15.9 IPMI Support

The control bit, IPMIEN, enables the module to support Intelligent Peripheral Management Interface (IPMI). When this bit is set, the module accepts and acts upon all addresses.

#### 15.10 General Call Address Support

The general call address can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledgement.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R\_W = 0.

The general call address is recognized when the General Call Enable (GCEN) bit is set (I2CCON<7> = 1). Following a Start bit detection, 8 bits are shifted into I2CRSR and the address is compared with I2CADD, and is also compared with the general call address which is fixed in hardware.

If a general call address match occurs, the I2CRSR is transferred to the I2CRCV after the eighth clock, the RBF flag is set and on the falling edge of the ninth bit (ACK bit), the master event interrupt flag (MI2CIF) is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the I2CRCV to determine if the address was device specific or a general call address.

#### 15.11 I<sup>2</sup>C Master Support

As a master device, six operations are supported:

- Assert a Start condition on SDA and SCL.

- · Assert a Restart condition on SDA and SCL.

- Write to the I2CTRN register initiating transmission of data/address.

- Generate a Stop condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an ACK condition at the end of a received byte of data.

#### 15.12 I<sup>2</sup>C Master Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the data direction bit. In this case, the data direction bit ( $R_W$ ) is logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an ACK bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the data direction bit. In this case, the data direction bit (R\_W) is logic '1'. Thus, the first byte transmitted is a 7-bit slave address, followed by a '1' to indicate receive bit. Serial data is received via SDA while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an ACK bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

#### 15.12.1 I<sup>2</sup>C MASTER TRANSMISSION

Transmission of a data byte, a 7-bit address, or the second half of a 10-bit address is accomplished by simply writing a value to the I2CTRN register. The user should only write to I2CTRN when the module is in a Wait state. This action will set the Buffer Full Flag (TBF) and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. The Transmit Status Flag, TRSTAT (I2CSTAT<14>), indicates that a master transmit is in progress.

#### 15.12.2 I<sup>2</sup>C MASTER RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (I2CCON<3>). The  $I^2C$  module must be Idle before the RCEN bit is set, otherwise the RCEN bit will be disregarded. The Baud Rate Generator begins counting and, on each rollover, the state of the SCL pin ACK and data are shifted into the I2CRSR on the rising edge of each clock.

## dsPIC30F6011A/6012A/6013A/6014A

NOTES:

#### 16.3.4 TRANSMIT INTERRUPT

The transmit interrupt flag (U1TXIF or U2TXIF) is located in the corresponding interrupt flag register.

The transmitter generates an edge to set the UxTXIF bit. The condition for generating the interrupt depends on the UTXISEL control bit:

- 1. If UTXISEL = 0, an interrupt is generated when a word is transferred from the transmit buffer to the Transmit Shift register (UxTSR). This implies that the transmit buffer has at least one empty word.

- 2. If UTXISEL = 1, an interrupt is generated when a word is transferred from the transmit buffer to the Transmit Shift register (UxTSR) and the transmit buffer is empty.

Switching between the two Interrupt modes during operation is possible and sometimes offers more flexibility.

#### 16.3.5 TRANSMIT BREAK

Setting the UTXBRK bit (UxSTA<11>) will cause the UxTX line to be driven to logic '0'. The UTXBRK bit overrides all transmission activity. Therefore, the user should generally wait for the transmitter to be Idle before setting UTXBRK.

To send a break character, the UTXBRK bit must be set by software and must remain set for a minimum of 13 baud clock cycles. The UTXBRK bit is then cleared by software to generate Stop bits. The user must wait for a duration of at least one or two baud clock cycles in order to ensure a valid Stop bit(s) before reloading the UxTXB, or starting other transmitter activity. Transmission of a break character does not generate a transmit interrupt.

#### 16.4 Receiving Data

#### 16.4.1 RECEIVING IN 8-BIT OR 9-BIT DATA MODE

The following steps must be performed while receiving 8-bit or 9-bit data:

- 1. Set up the UART (see Section 16.3.1 "Transmitting in 8-bit data mode").

- 2. Enable the UART (see Section 16.3.1 "Transmitting in 8-bit data mode").

- A receive interrupt will be generated when one or more data words have been received, depending on the receive interrupt settings specified by the URXISEL bits (UxSTA<7:6>).

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read the received data from UxRXREG. The act of reading UxRXREG will move the next word to the top of the receive FIFO, and the PERR and FERR values will be updated.

#### 16.4.2 RECEIVE BUFFER (UXRXB)

The receive buffer is 4 words deep. Including the Receive Shift register (UxRSR), the user effectively has a 5-word deep FIFO buffer.

URXDA (UxSTA<0>) = 1 indicates that the receive buffer has data available. URXDA = 0 implies that the buffer is empty. If a user attempts to read an empty buffer, the old values in the buffer will be read and no data shift will occur within the FIFO.

The FIFO is reset during any device Reset. It is not affected when the device enters or wakes up from a Power-Saving mode.

#### 16.4.3 RECEIVE INTERRUPT

The receive interrupt flag (U1RXIF or U2RXIF) can be read from the corresponding interrupt flag register. The interrupt flag is set by an edge generated by the receiver. The condition for setting the receive interrupt flag depends on the settings specified by the URXISEL<1:0> (UxSTA<7:6>) control bits.

- a) If URXISEL<1:0> = 00 or 01, an interrupt is generated every time a data word is transferred from the Receive Shift register (UxRSR) to the receive buffer. There may be one or more characters in the receive buffer.

- b) If URXISEL<1:0> = 10, an interrupt is generated when a word is transferred from the Receive Shift register (UxRSR) to the receive buffer, which as a result of the transfer, contains 3 characters.

- c) If URXISEL<1:0> = 11, an interrupt is set when a word is transferred from the Receive Shift register (UxRSR) to the receive buffer, which as a result of the transfer, contains 4 characters (i.e., becomes full).

Switching between the Interrupt modes during operation is possible, though generally not advisable during normal operation.

#### 16.5 Reception Error Handling

#### 16.5.1 RECEIVE BUFFER OVERRUN ERROR (OERR BIT)

The OERR bit (UxSTA<1>) is set if all of the following conditions occur:

- a) The receive buffer is full.

- b) The Receive Shift register is full, but unable to transfer the character to the receive buffer.

- c) The Stop bit of the character in the UxRSR is detected, indicating that the UxRSR needs to transfer the character to the buffer.

Once OERR is set, no further data is shifted in UxRSR (until the OERR bit is cleared in software or a Reset occurs). The data held in UxRSR and UxRXREG remains valid.

#### 17.6.2 PRESCALER SETTING

There is a programmable prescaler with integral values ranging from 1 to 64, in addition to a fixed divide-by-2 for clock generation. The time quantum (TQ) is a fixed unit of time derived from the oscillator period, and is given by Equation 17-1.

| Note: | FCAN   | must   | not   | exceed   | 30     | MHz.    | lf |

|-------|--------|--------|-------|----------|--------|---------|----|

|       | CANC   | KS = 0 | , the | n Fcy mu | ist no | ot exce | ed |

|       | 7.5 Mł | Ηz.    |       |          |        |         |    |

#### EQUATION 17-1: TIME QUANTUM FOR CLOCK GENERATION

$T_Q = 2 (BRP < 5:0 > +1) / FCAN$

#### 17.6.3 PROPAGATION SEGMENT

This part of the bit time is used to compensate physical delay times within the network. These delay times consist of the signal propagation time on the bus line and the internal delay time of the nodes. The Prop Seg can be programmed from 1 TQ to 8 TQ by setting the PRSEG<2:0> bits (CiCFG2<2:0>).

#### 17.6.4 PHASE SEGMENTS

The phase segments are used to optimally locate the sampling of the received bit within the transmitted bit time. The sampling point is between Phase1 Seg and Phase2 Seg. These segments are lengthened or shortened by resynchronization. The end of the Phase1 Seg determines the sampling point within a bit period. The segment is programmable from 1 TQ to 8 TQ. Phase2 Seg provides delay to the next transmitted data transition. The segment is programmable from 1 TQ to 8 TQ, or it may be defined to be equal to the greater of Phase1 Seg or the information processing time (2 TQ). The Phase1 Seg is initialized by setting bits SEG1PH<2:0> (CiCFG2<5:3>), and Phase2 Seg is initialized by setting SEG2PH<2:0> (CiCFG2<10:8>).

The following requirement must be fulfilled while setting the lengths of the phase segments:

Prop Seg + Phase1 Seg > = Phase2 Seg

#### 17.6.5 SAMPLE POINT

The sample point is the point of time at which the bus level is read and interpreted as the value of that respective bit. The location is at the end of Phase1 Seg. If the bit timing is slow and contains many TQ, it is possible to specify multiple sampling of the bus line at the sample point. The level determined by the CAN bus then corresponds to the result from the majority decision of three values. The majority samples are taken at the sample point and twice before with a distance of TQ/2. The CAN module allows the user to choose between sampling three times at the same point or once at the same point, by setting or clearing the SAM bit (CiCFG2<6>).

Typically, the sampling of the bit should take place at about 60-70% through the bit time, depending on the system parameters.

#### 17.6.6 SYNCHRONIZATION

To compensate for phase shifts between the oscillator frequencies of the different bus stations, each CAN controller must be able to synchronize to the relevant signal edge of the incoming signal. When an edge in the transmitted data is detected, the logic will compare the location of the edge to the expected time (Synchronous Segment). The circuit will then adjust the values of Phase1 Seg and Phase2 Seg. There are 2 mechanisms used to synchronize.

#### 17.6.6.1 Hard Synchronization

Hard synchronization is only done whenever there is a 'recessive' to 'dominant' edge during bus Idle indicating the start of a message. After hard synchronization, the bit time counters are restarted with the Sync Seg. Hard synchronization forces the edge which has caused the hard synchronization to lie within the synchronization segment of the restarted bit time. If a hard synchronization is done, there will not be a resynchronization within that bit time.

#### 17.6.6.2 Resynchronization

As a result of resynchronization, Phase1 Seg may be lengthened or Phase2 Seg may be shortened. The amount of lengthening or shortening of the phase buffer segment has an upper bound known as the synchronization jump width, and is specified by the SJW<1:0> bits (CiCFG1<7:6>). The value of the synchronization jump width will be added to Phase1 Seg or subtracted from Phase2 Seg. The resynchronization jump width is programmable between 1 To and 4 To.

The following requirement must be fulfilled while setting the SJW<1:0> bits:

Phase2 Seg > Synchronization Jump Width

| IXA <sup>(1</sup>   |

|---------------------|

| )F601               |

| IC3(                |

| dsP                 |

| FOR                 |

| EGISTER MAP FOR     |

| TER                 |

| GIS                 |

| N RE                |

| TION                |

| INTEGRATIO          |

| SYSTEM II           |

| <b>TABLE 20-7</b> : |

| TABI                |

| SFR<br>Name                        | Addr | Bit 15      | SFR         Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 1           Name         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | Bit 13    | Bit 12 | Bit 11 | 0     | Bit 9     | Bit 9 Bit 8 | Bit 7 | Bit 6          | Bit 5                      | Bit 4         | Bit 3         | Bit 2 | Bit 1    | Bit 0 | Reset State                                                                                                                         |

|------------------------------------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|--------|-------|-----------|-------------|-------|----------------|----------------------------|---------------|---------------|-------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| RCON 0740 TRAPR IOPUWR BGST LVDEN  | 0740 | TRAPR       | IOPUWR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BGST      | LVDEN  |        | LVDL  | -VDL<3:0> |             | EXTR  | SWR            | EXTR SWR SWDTEN WDTO SLEEP | WDTO          | SLEEP         | IDLE  | BOR      | POR   | POR Depends on type of Reset.                                                                                                       |

| OSCCON 0742                        | 0742 |             | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | COSC<2:0> |        | I      | z     | NOSC<2:0> | 4           | POST  | POST<1:0> LOCK | LOCK                       | I             | CF            | Ι     | LPOSCEN  | OSWEN | <ul> <li>LPOSCEN OSWEN Depends on Configuration bits.</li> </ul>                                                                    |

| OSCTUN 0744                        | 0744 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | 1      | 1      |       |           |             | 1     |                | I                          | 1             |               | TUN   | TUN<3:0> |       | 0000 0000 0000 0000                                                                                                                 |

| PMD1 0770 T5MD T4MD T3MD T2MD T1MD | 0770 | <b>T5MD</b> | T4MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T3MD      | T2MD   | T1MD   |       |           | DCIMD       | I2CMD | U2MD           | U1MD                       | <b>SPI2MD</b> | <b>SPI1MD</b> | C2MD  | C1MD     | ADCMD | DCIMD I2CMD U2MD U1MD SPI2MD SP11MD C2MD C1MD ADCMD 0000 0000 0000                                                                  |

| PMD2                               | 0772 | IC8MD       | IC7MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IC6MD     | IC5MD  | IC4MD  | IC3MD | IC2MD     | IC1MD       | OC8MD | OC7MD          | OC6MD                      | OC5MD         | OC4MD         | OC3MD | OC2MD    | OC1MD | PMD2 0772 IC8MD IC7MD IC6MD IC5MD IC4MD IC3MD IC2MD IC1MD OC8MD OC8MD OC6MD OC6MD OC6MD OC4MD OC3MD OC2MD OC1MD 0000 0000 0000 0000 |

| -puene                             |      | = unimple   | $$ = unimplemented bit read as $0^{\circ}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | read as   | ,u,    |        |       |           |             |       |                |                            |               |               |       |          |       |                                                                                                                                     |

Legena: Note 1

— = unimplemented bit, read as '0' Refer to the "dsP/C30F Family Reference Manual" (DS70046) for descriptions of register bit fields. ÷

# DEVICE CONFIGURATION REGISTER MAP<sup>(1)</sup> 20-8: TABLE

|                    | .0-02                    | IABLE 20-0. DEVICE CONFIGURATION REGISTER MARY                                    | 911NOO                      |                   |            |              |                                                                                                                                                                  |                     |                           |       |       |            |        |       |            |            |       |

|--------------------|--------------------------|-----------------------------------------------------------------------------------|-----------------------------|-------------------|------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------|-------|-------|------------|--------|-------|------------|------------|-------|

| Name               | Address                  | Bit 15                                                                            | Bit 14                      | Bit 13            | Bit 12     | Bit 11       | Bit 10                                                                                                                                                           | Bit 9               | Bit 8                     | Bit 7 | Bit 6 | Bit 5      | Bit 4  | Bit 3 | Bit 2      | Bit 1      | Bit 0 |

| FOSC               | F80000                   | FCKSM<1:0>                                                                        | 1<1:0>                      | I                 |            | I            |                                                                                                                                                                  | FOS<2:0>            |                           |       | I     | I          |        |       | FPR<4:0>   |            |       |

| FWDT               | F80002                   | FWDTEN                                                                            | I                           | I                 | l          | I            | I                                                                                                                                                                | I                   | I                         | I     | I     | FWPSA<1:0> | A<1:0> |       | FWPSB<3:0> | 3<3:0>     |       |

| FBORPOR            | FBORPOR F80004           | MCLREN                                                                            | Ι                           | I                 |            | I            | PWMPIN <sup>(2)</sup>                                                                                                                                            | HPOL <sup>(2)</sup> | DMMPIN(Z) HPOL(Z) LPOL(Z) | BOREN |       | BORV<1:0>  | <1:0>  | -     |            | FPWRT<1:0> | <1:0> |

| FBS                | F80006                   | Ι                                                                                 | Ι                           | RBS               | RBS<1:0>   | I            | Ι                                                                                                                                                                | Ι                   | EBS                       | Ι     | I     | Ι          | Ι      |       | BSS<2:0>   |            | BWRP  |

| FSS                | F80008                   | Ι                                                                                 | I                           | RSS<1:0>          | <1:0>      | I            | Ι                                                                                                                                                                | ESS                 | ESS<1:0>                  | Ι     |       |            | Ι      |       | SSS<2:0>   |            | SWRP  |

| FGS                | F8000A                   | Ι                                                                                 | Ι                           | Ι                 | -          | Ι            | -                                                                                                                                                                | Ι                   | Ι                         | Ι     |       | -          | -      |       | <0:1>SS5   | 1:0>       | GWRP  |

| FICD               | F8000C                   | BKBUG                                                                             | COE                         | Ι                 | Ι          | Ι            | Ι                                                                                                                                                                | Ι                   | Ι                         | Ι     | Ι     | Ι          | Ι      | -     | —          | ICS<1:0>   | 1:0>  |

| Legend:<br>Note 1: | — = unimp<br>Refer to th | — = unimplemented bit, read as '0'<br>Refer to the " <i>dsPIC30F Family Ref</i> e | t, read as '0<br>Family Ref | r'<br>ference Man | ual" (DS70 | 046) for des | Legend: — = unimplemented bit, read as '0'<br>Note 1: Refer to the " <i>asPIC30F Family Reference Manual"</i> (DS70046) for descriptions of register bit fields. | gister bit fie      | jds.                      |       |       |            |        |       |            |            |       |

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields. These bits are reserved (read as '1' and must be programmed as '1'). ÷ ä

## dsPIC30F6011A/6012A/6013A/6014A

| Base    |                      |        |                 |                                       | #             | # . 6          |                          |

|---------|----------------------|--------|-----------------|---------------------------------------|---------------|----------------|--------------------------|

| Instr # | Assembly<br>Mnemonic |        | Assembly Syntax | Description                           | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

| 66      | RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f         | 1             | 1              | N,Z                      |

|         |                      | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f      | 1             | 1              | N,Z                      |

|         |                      | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws       | 1             | 1              | N,Z                      |

| 67      | SAC                  | SAC    | Acc,#Slit4,Wdo  | Store Accumulator                     | 1             | 1              | None                     |

|         |                      | SAC.R  | Acc,#Slit4,Wdo  | Store Rounded Accumulator             | 1             | 1              | None                     |

| 68      | SE                   | SE     | Ws,Wnd          | Wnd = sign-extended Ws                | 1             | 1              | C,N,Z                    |

| 69      | SETM                 | SETM   | f               | f = 0xFFFF                            | 1             | 1              | None                     |

|         |                      | SETM   | WREG            | WREG = 0xFFFF                         | 1             | 1              | None                     |

|         |                      | SETM   | Ws              | Ws = 0xFFFF                           | 1             | 1              | None                     |

| 70      | SFTAC                | SFTAC  | Acc,Wn          | Arithmetic Shift Accumulator by (Wn)  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|         |                      | SFTAC  | Acc,#Slit6      | Arithmetic Shift Accumulator by Slit6 | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 71      | SL                   | SL     | f               | f = Left Shift f                      | 1             | 1              | C,N,OV,Z                 |

|         |                      | SL     | f,WREG          | WREG = Left Shift f                   | 1             | 1              | C,N,OV,Z                 |

|         |                      | SL     | Ws,Wd           | Wd = Left Shift Ws                    | 1             | 1              | C,N,OV,Z                 |

|         |                      | SL     | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns            | 1             | 1              | N,Z                      |

|         |                      | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5           | 1             | 1              | N,Z                      |

| 72      | SUB                  | SUB    | Acc             | Subtract Accumulators                 | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|         |                      | SUB    | f               | f = f - WREG                          | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUB    | f,WREG          | WREG = f - WREG                       | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUB    | #lit10,Wn       | Wn = Wn - lit10                       | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUB    | Wb,Ws,Wd        | Wd = Wb - Ws                          | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUB    | Wb,#lit5,Wd     | Wd = Wb - lit5                        | 1             | 1              | C,DC,N,OV,Z              |

| 73      | SUBB                 | SUBB   | f               | $f = f - WREG - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUBB   | f,WREG          | WREG = f - WREG - $(\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUBB   | #lit10,Wn       | $Wn = Wn - lit10 - (\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUBB   | Wb,Ws,Wd        | $Wd = Wb - Ws - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUBB   | Wb,#lit5,Wd     | $Wd = Wb - lit5 - (\overline{C})$     | 1             | 1              | C,DC,N,OV,Z              |

| 74      | SUBR                 | SUBR   | f               | f = WREG - f                          | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUBR   | f,WREG          | WREG = WREG - f                       | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUBR   | Wb,Ws,Wd        | Wd = Ws - Wb                          | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUBR   | Wb,#lit5,Wd     | Wd = lit5 - Wb                        | 1             | 1              | C,DC,N,OV,Z              |

| 75      | SUBBR                | SUBBR  | f               | $f = WREG - f - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUBBR  | f,WREG          | WREG = WREG -f - $(\overline{C})$     | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUBBR  | Wb,Ws,Wd        | $Wd = Ws - Wb - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |

|         |                      | SUBBR  | Wb,#lit5,Wd     | $Wd = lit5 - Wb - (\overline{C})$     | 1             | 1              | C,DC,N,OV,Z              |

| 76      | SWAP                 | SWAP.b | Wn              | Wn = nibble swap Wn                   | 1             | 1              | None                     |

|         |                      | SWAP   | Wn              | Wn = byte swap Wn                     | 1             | 1              | None                     |

| 77      | TBLRDH               | TBLRDH | Ws,Wd           | Read Prog<23:16> to Wd<7:0>           | 1             | 2              | None                     |

| 78      | TBLRDL               | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd                 | 1             | 2              | None                     |

| 79      | TBLWTH               | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16>          | 1             | 2              | None                     |

| 80      | TBLWTL               | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>                | 1             | 2              | None                     |

| 81      | ULNK                 | ULNK   |                 | Unlink frame pointer                  | 1             | 1              | None                     |

| 82      | XOR                  | XOR    | f               | f = f .XOR. WREG                      | 1             | 1              | N,Z                      |

|         |                      | XOR    | f,WREG          | WREG = f .XOR. WREG                   | 1             | 1              | N,Z                      |

|         |                      | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd                   | 1             | 1              | N,Z                      |

|         |                      | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws                      | 1             | 1              | N,Z                      |

|         |                      | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5                    | 1             | 1              | N,Z                      |

| 83      | ZE                   | ZE     | Ws,Wnd          | Wnd = Zero-extend Ws                  | 1             | 1              | C,Z,N                    |

#### TABLE 21-2: INSTRUCTION SET OVERVIEW (CONTINUED)

#### 23.1 DC Characteristics

#### TABLE 23-1: OPERATING MIPS VS. VOLTAGE

| Von Benge | Tomp Bongo     | Max MIPS                      |    |  |  |  |

|-----------|----------------|-------------------------------|----|--|--|--|

| VDD Range | Temp Range     | dsPIC30F601XA-30I dsPIC30F601 |    |  |  |  |

| 4.5-5.5V  | -40°C to 85°C  | 30                            | —  |  |  |  |

| 4.5-5.5V  | -40°C to 125°C | —                             | 20 |  |  |  |

| 3.0-3.6V  | -40°C to 85°C  | 15                            | —  |  |  |  |

| 3.0-3.6V  | -40°C to 125°C | —                             | 10 |  |  |  |

| 2.5-3.0V  | -40°C to 85°C  | 10                            | —  |  |  |  |

#### TABLE 23-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                                                         |                | Min                                 | Тур | Max  | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------|-----|------|------|

| dsPIC30F601xA-30I                                                                                                                                                                                                              |                |                                     |     |      |      |

| Operating Junction Temperature Range                                                                                                                                                                                           | TJ             | -40                                 |     | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                            | T <sub>A</sub> | -40                                 |     | +85  | °C   |