Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                   |                                                                                |

|--------------------------|--------------------------------------------------------------------------------|

| oduct Status             | Active                                                                         |

|                          |                                                                                |

| ore Processor            | dsPIC                                                                          |

| ore Size                 | 16-Bit                                                                         |

| peed                     | 20 MIPS                                                                        |

| onnectivity              | CANbus, I <sup>2</sup> C, SPI, UART/USART                                      |

| eripherals               | AC'97, Brown-out Detect/Reset, I <sup>2</sup> S, LVD, POR, PWM, WDT            |

| umber of I/O             | 68                                                                             |

| ogram Memory Size        | 144KB (48K x 24)                                                               |

| ogram Memory Type        | FLASH                                                                          |

| PROM Size                | 4K x 8                                                                         |

| M Size                   | 8K x 8                                                                         |

| ltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| ta Converters            | A/D 16x12b                                                                     |

| cillator Type            | Internal                                                                       |

| erating Temperature      | -40°C ~ 125°C (TA)                                                             |

| ounting Type             | Surface Mount                                                                  |

| ckage / Case             | 80-TQFP                                                                        |

| ipplier Device Package   | 80-TQFP (12x12)                                                                |

| rchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6014a-20e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **CMOS Technology:**

- · Low-power, high-speed Flash technology

- Wide operating voltage range (2.5V to 5.5V)

- Industrial and Extended temperature ranges

- · Low power consumption

#### dsPIC30F6011A/6012A/6013A/6014A Controller Families

|               |      | Progr | am Memory    | SRAM  | EEPROM | Timer  | Input | Output          | Codec                   | ADC                | RT |   | TM               | Z  |

|---------------|------|-------|--------------|-------|--------|--------|-------|-----------------|-------------------------|--------------------|----|---|------------------|----|

| Device        | Pins | Bytes | Instructions | Bytes | Bytes  | 16-bit | Cap   | Comp/Std<br>PWM | Interface               | 12-bit<br>100 Ksps | ΠA | " | l <sup>2</sup> C | CA |

| dsPIC30F6011A | 64   | 132K  | 44K          | 6144  | 2048   | 5      | 8     | 8               | _                       | 16 ch              | 2  | 2 | 1                | 2  |

| dsPIC30F6012A | 64   | 144K  | 48K          | 8192  | 4096   | 5      | 8     | 8               | AC'97, I <sup>2</sup> S | 16 ch              | 2  | 2 | 1                | 2  |

| dsPIC30F6013A | 80   | 132K  | 44K          | 6144  | 2048   | 5      | 8     | 8               | _                       | 16 ch              | 2  | 2 | 1                | 2  |

| dsPIC30F6014A | 80   | 144K  | 48K          | 8192  | 4096   | 5      | 8     | 8               | AC'97, I <sup>2</sup> S | 16 ch              | 2  | 2 | 1                | 2  |

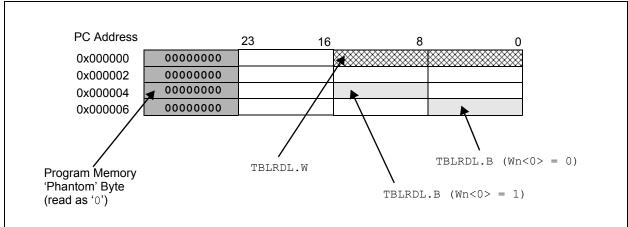

# 3.1.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

This architecture fetches 24-bit wide program memory. Consequently, instructions are always aligned. However, as the architecture is modified Harvard, data can also be present in program space.

There are two methods by which program space can be accessed: via special table instructions, or through the remapping of a 16K word program space page into the upper half of data space (see Section 3.1.2 "Data Access From Program Memory using Program Space Visibility"). The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lsw of any address within program space, without going through data space. The TBLRDH and TBLWTH instructions are the only method whereby the upper 8 bits of a program space word can be accessed as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the Least Significant Data Word, and TBLRDH and TBLWTH access the space which contains the Most Significant Data Byte.

Figure 3-3 shows how the EA is created for table operations and data space accesses (PSV = 1). Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

A set of table instructions are provided to move byte or word sized data to and from program space.

1. TBLRDL: Table Read Low

Word: Read the lsw of the program address; P<15:0> maps to D<15:0>.

Byte: Read one of the LSBs of the program address:

P<7:0> maps to the destination byte when byte select = 0;

P<15:8> maps to the destination byte when byte select = 1.

- TBLWTL: Table Write Low (refer to Section 6.0

"Flash Program Memory" for details on Flash

Programming)

- 3. TBLRDH: Table Read High

*Word:* Read the most significant word of the program address; P<23:16> maps to D<7:0>; D<15:8> will always be = 0.

Byte: Read one of the MSBs of the program address;

P<23:16> maps to the destination byte when byte select = 0;

The destination byte will always be = 0 when byte select = 1.

TBLWTH: Table Write High (refer to Section 6.0

"Flash Program Memory" for details on Flash

Programming).

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. Should a misaligned read or write be attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed, whereas if it occurred on a write, the instruction will be executed but the write will not occur. In either case, a trap will then be executed, allowing the system and/or user to examine the machine state prior to execution of the address fault.

FIGURE 3-10: DATA ALIGNMENT

| ,    | 15 <b>MSB</b> | 8 | 7 LSB  | 0 |      |

|------|---------------|---|--------|---|------|

| 0001 | Byte1         |   | Byte 0 |   | 0000 |

| 0003 | Byte3         |   | Byte 2 |   | 0002 |

| 0005 | Byte5         |   | Byte 4 |   | 0004 |

|      |               |   |        |   | -    |

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A sign-extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions, including the DSP instructions, operate only on words.

#### 3.2.5 NEAR DATA SPACE

An 8 Kbyte 'near' data space is reserved in X address memory space between 0x0000 and 0x1FFF, which is directly addressable via a 13-bit absolute address field within all memory direct instructions. The remaining X address space and all of the Y address space is addressable indirectly. Additionally, the whole of X data space is addressable using MOV instructions, which support memory direct addressing with a 16-bit address field.

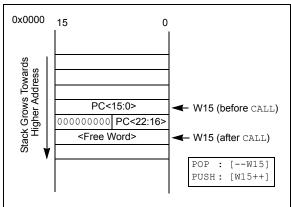

#### 3.2.6 SOFTWARE STACK

The dsPIC DSC devices contain a software stack. W15 is used as the Stack Pointer.

The Stack Pointer always points to the first available free word and grows from lower addresses towards higher addresses. It pre-decrements for stack pops and post-increments for stack pushes as shown in Figure 3-11. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

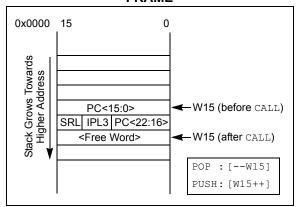

Note: A PC push during exception processing will concatenate the SRL register to the MSB of the PC prior to the push.

There is a Stack Pointer Limit register (SPLIM) associated with the Stack Pointer. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word aligned. Whenever an Effective Address (EA) is generated using W15 as a source or destination pointer, the address thus generated is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a Stack Error Trap will not occur. The Stack Error Trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a Stack Error Trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value, 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800, thus preventing the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

FIGURE 3-11: CALL STACK FRAME

## FIGURE 5-2: INTERRUPT STACK FRAME

- Note 1: The user can always lower the priority level by writing a new value into SR. The Interrupt Service Routine must clear the interrupt flag bits in the IFSx register before lowering the processor interrupt priority, in order to avoid recursive interrupts.

- 2: The IPL3 bit (CORCON<3>) is always clear when interrupts are being processed. It is set only during execution of traps.

The RETFIE (return from interrupt) instruction will unstack the Program Counter and STATUS registers to return the processor to its state prior to the interrupt sequence.

#### 5.5 Alternate Vector Table

In program memory, the Interrupt Vector Table (IVT) is followed by the Alternate Interrupt Vector Table (AIVT), as shown in Table 5-1. Access to the alternate vector table is provided by the ALTIVT bit in the INTCON2 register. If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors. The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

If the AIVT is not required, the program memory allocated to the AIVT may be used for other purposes. AIVT is not a protected section and may be freely programmed by the user.

#### 5.6 Fast Context Saving

A context saving option is available using shadow registers. Shadow registers are provided for the DC, N, OV, Z and C bits in SR, and the registers W0 through W3. The shadows are only one level deep. The shadow registers are accessible using the PUSH.S and POP.S instructions only.

When the processor vectors to an interrupt, the PUSH.S instruction can be used to store the current value of the aforementioned registers into their respective shadow registers.

If an ISR of a certain priority uses the PUSH.S and POP.S instructions for fast context saving, then a higher priority ISR should not include the same instructions. Users must save the key registers in software during a lower priority interrupt if the higher priority ISR uses fast context saving.

#### 5.7 External Interrupt Requests

The interrupt controller supports up to five external interrupt request signals, INT0-INT4. These inputs are edge sensitive; they require a low-to-high or a high-to-low transition to generate an interrupt request. The INTCON2 register has five bits, INT0EP-INT4EP, that select the polarity of the edge detection circuitry.

#### 5.8 Wake-up from Sleep and Idle

The interrupt controller may be used to wake-up the processor from either Sleep or Idle modes, if Sleep or Idle mode is active when the interrupt is generated.

If an enabled interrupt request of sufficient priority is received by the interrupt controller, then the standard interrupt request is presented to the processor. At the same time, the processor will wake-up from Sleep or Idle and begin execution of the Interrupt Service Routine (ISR) needed to process the interrupt request.

#### 7.0 DATA EEPROM MEMORY

Note:

This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

The Data EEPROM Memory is readable and writable during normal operation over the entire VDD range. The data EEPROM memory is directly mapped in the program memory address space.

The four SFRs used to read and write the program Flash memory are used to access data EEPROM memory, as well. As described in **Section 6.5 "Control Registers"**, these registers are:

- NVMCON

- NVMADR

- NVMADRU

- NVMKEY

The EEPROM data memory allows read and write of single words and 16-word blocks. When interfacing to data memory, NVMADR in conjunction with the NVMADRU register are used to address the EEPROM location being accessed. TBLRDL and TBLWTL instructions are used to read and write data EEPROM. The dsPIC30F devices have up to 8 Kbytes (4K words) of data EEPROM with an address range from 0x7FF000 to 0x7FFFFE.

A word write operation should be preceded by an erase of the corresponding memory location(s). The write typically requires 2 ms to complete but the write time will vary with voltage and temperature.

A program or erase operation on the data EEPROM does not stop the instruction flow. The user is responsible for waiting for the appropriate duration of time before initiating another data EEPROM write/erase operation. Attempting to read the data EEPROM while a programming or erase operation is in progress results in unspecified data.

Control bit WR initiates write operations similar to program Flash writes. This bit cannot be cleared, only set, in software. They are cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The address register NVMADR remains unchanged.

**Note:** Interrupt flag bit NVMIF in the IFS0 register is set when write is complete. It must be cleared in software.

#### 7.1 Reading the Data EEPROM

A TBLRD instruction reads a word at the current program word address. This example uses W0 as a pointer to data EEPROM. The result is placed in register W4 as shown in Example 7-1.

#### **EXAMPLE 7-1:** DATA EEPROM READ

MOV #LOW\_ADDR\_WORD,W0 ; Init Pointer

MOV #HIGH\_ADDR\_WORD,W1

MOV W1,TBLPAG

TBLRDL [ W0 ], W4 ; read data EEPROM

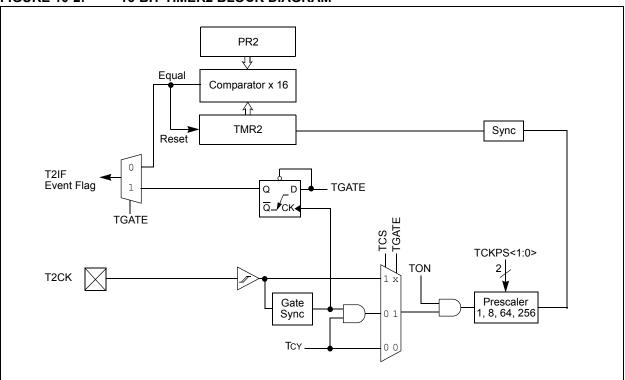

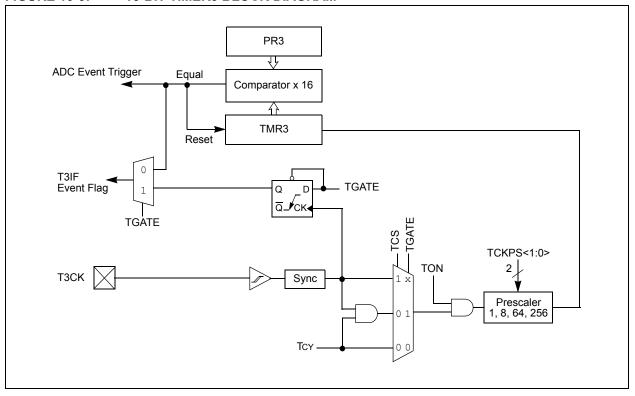

FIGURE 10-2: 16-BIT TIMER2 BLOCK DIAGRAM

FIGURE 10-3: 16-BIT TIMER3 BLOCK DIAGRAM

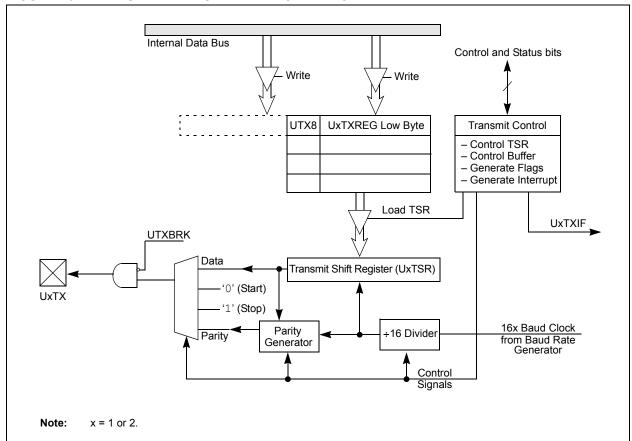

# 16.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART) MODULE

Note:

This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the Universal Asynchronous Receiver Transmitter communications module.

#### 16.1 UART Module Overview

The key features of the UART module are:

- Full-duplex, 8 or 9-bit data communication

- Even, odd or no parity options (for 8-bit data)

- · One or two Stop bits

- Fully integrated Baud Rate Generator with 16-bit prescaler

- Baud rates range from 38 bps to 1.875 Mbps at a 30 MHz instruction rate

- · 4-word deep transmit data buffer

- · 4-word deep receive data buffer

- · Parity, framing and buffer overrun error detection

- Support for interrupt only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- · Loopback mode for diagnostic support

FIGURE 16-1: UART TRANSMITTER BLOCK DIAGRAM

NOTES:

| <b>TABLE 17-2</b> : |          | CAN2 REGISTER MAP <sup>(1)</sup>              | EGISTEF                                      | ₹ MAP              | <del>-</del>             | •               |              | •                                              | •           | •                                                      |                                             |              |                          | •                                            |        |            |       |                     |

|---------------------|----------|-----------------------------------------------|----------------------------------------------|--------------------|--------------------------|-----------------|--------------|------------------------------------------------|-------------|--------------------------------------------------------|---------------------------------------------|--------------|--------------------------|----------------------------------------------|--------|------------|-------|---------------------|

| SFR Name            | Addr.    | Bit 15                                        | Bit 14                                       | Bit 13             | Bit 12                   | Bit 11          | Bit 10       | Bit 9                                          | Bit 8       | Bit 7                                                  | Bit 6                                       | Bit 5        | Bit 4                    | Bit 3                                        | Bit 2  | Bit 1      | Bit 0 | Reset State         |

| C2RXF0SID           | 03C0     | I                                             | I                                            | I                  | Receive                  |                 | e Filter 0 s | Acceptance Filter 0 Standard Identifier <10:0> | dentifier < | <10:0>                                                 |                                             |              |                          |                                              |        | ы́<br>l    | EXIDE | nonn nnnn nooo      |

| C2RXF0EIDH 03C2     | 03C2     | 1                                             | 1                                            | I                  | 1                        |                 |              |                                                | Receive     | Receive Acceptance Filter 0 Extended Identifier <17:6> | Filter 0 Ext                                | ended Ide    | entifier <1              | 49:2                                         |        |            |       | nnnn nnnn nnnn 0000 |

| C2RXF0EIDL          | 03C4     | Receive                                       | Receive Acceptance Filter 0 Extended Id      | ∋ Filter 0 E>      | xtended Ic               | dentifier <5:0> | <b>^</b>     | 1                                              | 1           | I                                                      | ı                                           | 1            | 1                        | I                                            | ı      | 1          | 1     | 0000 0000 00nn nnnn |

| C2RXF1SID           | 9308     | I                                             | I                                            | I                  |                          |                 | Re           | ceive Acc                                      | eptance     | Receive Acceptance Filter 1 Standard Identifier <10:0> | lard Identifi                               | er <10:0>    |                          |                                              |        | 1          | EXIDE | nonn nnnn nnnn nooo |

| C2RXF1EIDH          | 03CA     | I                                             | Ι                                            | I                  | Ι                        |                 |              |                                                | Receive     | Receive Acceptance Filter 1 Extended Identifier <17:6> | Filter 1 Ext                                | ended Ide    | entifier <1              | 49:2                                         |        |            |       | nnnn nnnn nnnn 0000 |

| C2RXF1EIDL          | 03CC     | Receive                                       | Receive Acceptance Filter 1 Extended Ide     | ∋ Filter 1 E>      | xtended Ic               | dentifier <5:0> | <b>^</b>     | I                                              | 1           | I                                                      | ı                                           | 1            | 1                        | I                                            | ı      | 1          | ı     | 0000 0000 00nn nnnn |

| C2RXF2SID           | 03D0     | 1                                             | I                                            | 1                  |                          |                 | Re           | ceive Acc                                      | eptance     | Receive Acceptance Filter 2 Standard Identifier <10:0> | lard Identifi                               | er <10:0>    |                          |                                              |        | 1          | EXIDE | ngnn nnnn nnnn ngoo |

| C2RXF2EIDH          | 03D2     | -                                             | I                                            | I                  | I                        |                 |              |                                                | Receive     | Receive Acceptance Filter 2 Extended Identifier <17:6> | Filter 2 Ext                                | ended Ide    | entifier <1              | <9:2                                         |        |            |       | nnnn nnnn nnnn 0000 |

| C2RXF2EIDL          | 03D4     | Receive                                       | Receive Acceptance Filter 2 Extended Id      | ∋ Filter 2 E>      | xtended Ic               | dentifier <5:0> | <b>^</b> 0.  | I                                              | I           | I                                                      | I                                           | I            | ı                        | I                                            | ı      | 1          | ı     | 0000 0000 00nn nnnn |

| C2RXF3SID           | 8QE0     | I                                             | 1                                            | I                  |                          |                 | Re           | ceive Acc                                      | eptance     | Receive Acceptance Filter 3 Standard Identifier <10:0> | lard Identifi                               | er <10:0>    |                          |                                              |        | 1          | EXIDE | nonn nnnn nnnn nooo |

| C2RXF3EIDH 03DA     | 03DA     |                                               | I                                            | Ι                  | Ι                        |                 |              |                                                | Receive     | Receive Acceptance Filter 3 Extended Identifier <17:6> | Filter 3 Ext                                | ended Ide    | entifier <1              | 49:2                                         |        |            |       | nnnn nnnn 0000      |

|                     | 03DC     | Receive                                       | Receive Acceptance Filter 3 Extended Id      | ∋ Filter 3 E>      | xtended Ic               | dentifier <5:0> | <b>^</b> 0.  | 1                                              | 1           | I                                                      | I                                           | 1            | ı                        | I                                            | I      | 1          | 1     | 0000 0000 00nn nnnn |

| C2RXF4SID           | 03E0     | 1                                             | 1                                            | 1                  |                          |                 | Re           | ceive Acc                                      | eptance     | Receive Acceptance Filter 4 Standard Identifier <10:0> | lard Identifi                               | er <10:0>    |                          |                                              |        | 1          | EXIDE | nonn nnnn nnnn nooo |

| C2RXF4EIDH 03E2     | 03E2     | I                                             | I                                            | Ι                  | l                        |                 |              |                                                | Receive     | Receive Acceptance Filter 4 Extended Identifier <17:6> | Filter 4 Ext                                | ended Ide    | entifier <1              | 49:2                                         |        |            |       | nnnn nnnn 0000      |

| C2RXF4EIDL 03E4     | 03E4     | Receive                                       | Receive Acceptance Filter 4 Extended Ide     | ∋ Filter 4 E>      | xtended Ic               | dentifier <5:0> | <b>^</b> 0.  | 1                                              | 1           | I                                                      | I                                           | 1            | ı                        | I                                            | Ι      | 1          | 1     | 0000 0000 00nn nnnn |

| C2RXF5SID 03E8      | 03E8     | 1                                             | I                                            | 1                  |                          |                 | Re           | ceive Acc                                      | eptance     | Receive Acceptance Filter 5 Standard Identifier <10:0> | lard Identifi                               | er <10:0>    |                          |                                              |        | 1          | EXIDE | nonn nnnn nooo      |

| C2RXF5EIDH 03EA     | 03EA     | 1                                             | 1                                            | I                  | 1                        |                 |              |                                                | Receive     | Receive Acceptance Filter 5 Extended Identifier <17:6> | Filter 5 Ext                                | ended Ide    | entifier <1              | 49:2                                         |        |            |       | nnnn nnnn nnnn 0000 |

| C2RXF5EIDL 03EC     | 03EC     | Receive                                       | Receive Acceptance Filter 5 Extended Id      | Filter 5 Example 5 | xtended Ic               | dentifier <5:0> | <b>^</b> 0   | I                                              | 1           | I                                                      | I                                           | 1            | 1                        | I                                            | I      | 1          | I     | 0000 0000 00nn nnnn |

| C2RXM0SID           | 03F0     | I                                             | I                                            | 1                  |                          |                 | Re           | ceive Acc                                      | eptance l   | Receive Acceptance Mask 0 Standard Identifier <10:0>   | dard Identifi                               | ier <10:0>   |                          |                                              |        | 1          | MIDE  | nonn nnnn nnnn nooo |

| C2RXM0EIDH          | 03F2     | 1                                             | 1                                            | I                  | 1                        |                 |              |                                                | Receive     | Receive Acceptance Mask 0 Extended Identifier <17:6>   | Mask 0 Ext                                  | ended Ide    | entifier <1              | <9:2                                         |        |            |       | nnnn nnnn nnnn 0000 |

|                     | 03F4     | Receive                                       | Receive Acceptance Mask 0 Extended Id        | Mask 0 E;          | xtended k                | dentifier <5:0> | <0:          | 1                                              | 1           | 1                                                      | I                                           | I            | 1                        | 1                                            | ı      | 1          |       | 0000 0000 00nn nnnn |

| C2RXM1SID           | 03F8     | Ι                                             | I                                            | 1                  |                          |                 | Re           | ceive Acc                                      | eptance l   | Receive Acceptance Mask 1 Standard Identifier <10:0>   | dard Identifi                               | ier <10:0>   |                          |                                              |        | 1          | MIDE  | nonn nnnn nooo      |

|                     | 03FA     | 1                                             | 1                                            | 1                  | I                        |                 |              |                                                | Receive     | Receive Acceptance Mask 1 Extended Identifier <17:6>   | Mask 1 Ext                                  | ended Ide    | entifier <1              | <9:2                                         |        |            |       | nnnn nnnn nnnn 0000 |

| DΓ                  | 03FC     | Receive                                       | Receive Acceptance Mask 1 Extended Id        | Mask 1 E           | xtended k                | dentifier <5:0> | <0:          | I                                              | I           | I                                                      | I                                           | 1            | ı                        | I                                            | I      | 1          | 1     | 0000 0000 00nn nnnn |

| C2TX2SID            |          | Transm                                        | Transmit Buffer 2 Standard Identifier <10:6> | tandard Ide        | ntifier <10              | <9:0            | I            | 1                                              | 1           | Trar                                                   | Transmit Buffer 2 Standard Identifier <5:0> | r 2 Standa   | ırd Identif              | ier <5:0>                                    |        | SRR        | TXIDE | nnnn nnnn 000n nnnn |

| C2TX2EID            | 0402     | Transmit Buffer 2 Extended Identifier <17:14> | er 2 Extende                                 | d Identifier       | <17:14>                  | 1               | 1            | 1                                              | 1           |                                                        | Transn                                      | nit Buffer . | 2 Extende                | Transmit Buffer 2 Extended Identifier <13:6> | <13:6> |            |       | nnnn nnnn 0000 nnnn |

| C2TX2DLC            | 0404     | Tr                                            | Transmit Buffer 2 Extended Identifier <5:0>  | r 2 Extend         | ed Identifi              | er <5:0>        |              | TXRTR                                          | TXRB1       | TXRB0                                                  |                                             | DLC<3:0>     | :3:0>                    |                                              | 1      | 1          | 1     | nnnn nnnn nnnn      |

| C2TX2B1             | 0406     |                                               |                                              | Transr             | Transmit Buffer          | 2 Byte 1        |              |                                                |             |                                                        |                                             | Transı       | nit Buffer               | Transmit Buffer 2 Byte 0                     |        |            |       | nnnn nnnn nnnn      |

|                     | 0408     |                                               |                                              | Transr             | Transmit Buffer 2 Byte 3 | 2 Byte 3        |              |                                                |             |                                                        |                                             | Transı       | Transmit Buffer 2 Byte 2 | 2 Byte 2                                     |        |            |       | nnnn nnnn nnnn nnnn |

|                     | 040A     |                                               |                                              | Transr             | Transmit Buffer          |                 |              |                                                |             |                                                        |                                             | Transı       | Transmit Buffer 2 Byte 4 | 2 Byte 4                                     |        |            |       | uuuu uuuu uuuu      |

|                     | 040C     |                                               |                                              | Transr             | Transmit Buffer          | 2 Byte 7        |              |                                                |             |                                                        |                                             | Transı       | nit Buffer               | Transmit Buffer 2 Byte 6                     |        |            |       | nnnn nnnn nnnn nnnn |

| _                   | 040E     | -                                             | 1                                            | Ī                  | 1                        | I               | 1            | 1                                              | 1           | I                                                      | TXABT T                                     | TXLARB T     | TXERR                    | TXREQ                                        | 1      | TXPRI<1:0> |       | 0000 0000 0000 0000 |

| C2TX1SID            |          | Transm                                        | Transmit Buffer 1 Standard Identifier <10:   | tandard Ide        | ntifier <10              | <9:0            | Ι            | Ι                                              | I           | Trar                                                   | Transmit Buffer 1 Standard Identifier <5:0> | r 1 Standa   | ırd Identif              | ier <5:0>                                    |        | SRR 1      | TXIDE | nnnn n000 nnnn      |

| C2TX1EID            |          | Transmit Buffer 1 Extended Identifier <17:14> | er 1 Extende                                 | d Identifier       | <17:14>                  | -               | Ι            |                                                | -           |                                                        | Transn                                      | nit Buffer   | 1 Extende                | Transmit Buffer 1 Extended Identifier <13:6> | <13:6> |            |       | uuuu 0000 uuuu      |

| C2TX1DLC            | 0414     | Tr                                            | Transmit Buffer 1 Extended Identifier <5:0>  | r 1 Extend         | ed Identifi              | er <5:0>        |              | TXRTR                                          | TXRB1       | TXRB0                                                  |                                             | DLC<3:0>     | :3:0>                    |                                              | 1      | 1          | 1     | nnnn nnnn nnnn      |

| legend:             | u = unir | ), se pear tid patrementemented bit read as   | — = unimple                                  | mented bit.        | read as                  | ,0,             |              |                                                |             |                                                        |                                             |              |                          |                                              |        |            |       |                     |

Legend: u = uninitialized bit, — = unimplemented bit, read as '0'

Note 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

#### REGISTER 20-2: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-----|-----|----------|-------|-------|-------|--|

| _     | _   | _   | _   | TUN<3:0> |       |       |       |  |

| bit 7 |     |     |     |          |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 -4 Unimplemented: Read as '0'

bit 3-0 **TUN<3:0>:** Lower two bits of TUN field. The four bit field specified by TUN<3:0> specifies the user tuning capability for the internal fast RC oscillator (nominal 7.37 MHz).

0111 = Maximum Frequency

0110 =

0101 =

0100 =

0011 =

0010 =

0001 =

0000 = Center Frequency, Oscillator is running at calibrated frequency

1111 =

1110 =

1101 =

1100 =

1011 =

1010 =

1001 =

1000 = Minimum Frequency

Any interrupt that is individually enabled (using the corresponding IE bit) and meets the prevailing priority level will be able to wake-up the processor. The processor will process the interrupt and branch to the ISR. The Sleep status bit in RCON register is set upon wake-up.

#### Note:

In spite of various delays applied (TPOR, TLOCK and TPWRT), the crystal oscillator (and PLL) may not be active at the end of the time-out (e.g., for low-frequency crystals). In such cases, if FSCM is enabled, then the device will detect this as a clock failure and process the clock failure trap, the FRC oscillator will be enabled, and the user will have to re-enable the crystal oscillator. If FSCM is not enabled, then the device will simply suspend execution of code until the clock is stable, and will remain in Sleep until the oscillator clock has started.

All Resets will wake-up the processor from Sleep mode. Any Reset, other than POR, will set the Sleep status bit. In a POR, the Sleep bit is cleared.

If Watchdog Timer is enabled, then the processor will wake-up from Sleep mode upon WDT time-out. The Sleep and WDTO status bits are both set.

#### 20.7.2 IDLE MODE

In Idle mode, the clock to the CPU is shutdown while peripherals keep running. Unlike Sleep mode, the clock source remains active.

Several peripherals have a control bit in each module that allows them to operate during Idle.

LPRC fail-safe clock remains active if clock failure detect is enabled.

The processor wakes up from Idle if at least one of the following conditions is true:

- On any interrupt that is individually enabled (IE bit is '1') and meets the required priority level

- On any Reset (POR, BOR, MCLR)

- · On WDT time-out

Upon wake-up from Idle mode, the clock is re-applied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction.

Any interrupt that is individually enabled (using IE bit) and meets the prevailing priority level will be able to wake-up the processor. The processor will process the interrupt and branch to the ISR. The IDLE status bit in RCON register is set upon wake-up.

Any Reset, other than POR, will set the Idle status bit. On a POR, the Idle bit is cleared.

If Watchdog Timer is enabled, then the processor will wake-up from Idle mode upon WDT time-out. The Idle and WDTO status bits are both set.

Unlike wake-up from Sleep, there are no time delays involved in wake-up from Idle.

#### 20.8 Device Configuration Registers

The Configuration bits in each device Configuration register specify some of the device modes and are programmed by a device programmer, or by using the In-Circuit Serial Programming (ICSP) feature of the device. Each device Configuration register is a 24-bit register, but only the lower 16 bits of each register are used to hold configuration data. There are seven device Configuration registers available to the user:

- FOSC (0xF80000): Oscillator Configuration register

- FWDT (0xF80002): Watchdog Timer Configuration register

- FBORPOR (0xF80004): BOR and POR Configuration register

- FBS (0xF80006): Boot Code Segment Configuration register

- 5. FSS (0xF80008): Secure Code Segment Configuration register

- FGS (0xF8000A): General Code Segment Configuration register

- FICD (0xF8000C): Debug Configuration Register

The placement of the Configuration bits is automatically handled when you select the device in your device programmer. The desired state of the Configuration bits may be specified in the source code (dependent on the language tool used), or through the programming interface. After the device has been programmed, the application software may read the Configuration bit values through the table read instructions. For additional information, please refer to the "dsPIC30F Flash Programming Specification" (DS70102) and the "dsPIC30F Family Reference Manual" (DS70046).

Note:

If the code protection Configuration Fuse bits (FBS(BSS<2:0>), FSS(SSS<2:0>), FGS<GSS>, FGS<GWRP>) have been programmed, an erase of the entire codeprotected device is only possible at voltages VDD  $\geq 4.5 \text{V}.$

TABLE 21-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr# | Assembly<br>Mnemonic |                | Assembly Syntax                  | Description                                                                    | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------|----------------------|----------------|----------------------------------|--------------------------------------------------------------------------------|---------------|----------------|--------------------------|

| 29             | DIV                  | DIV.S          | Wm, Wn                           | Signed 16/16-bit Integer Divide                                                | 1             | 18             | N,Z,C,OV                 |

|                |                      | DIV.SD         | Wm, Wn                           | Signed 32/16-bit Integer Divide                                                | 1             | 18             | N,Z,C,OV                 |

|                |                      | DIV.U          | Wm, Wn                           | Unsigned 16/16-bit Integer Divide                                              | 1             | 18             | N,Z,C,OV                 |

|                |                      | DIV.UD         | Wm, Wn                           | Unsigned 32/16-bit Integer Divide                                              | 1             | 18             | N,Z,C,OV                 |

| 30             | DIVF                 | DIVF           | Wm,Wn                            | Signed 16/16-bit Fractional Divide                                             | 1             | 18             | N,Z,C,OV                 |

| 31             | DO                   | DO             | #lit14,Expr                      | Do code to PC + Expr, lit14 + 1 times                                          | 2             | 2              | None                     |

|                |                      | DO             | Wn, Expr                         | Do code to PC + Expr, (Wn) + 1 times                                           | 2             | 2              | None                     |

| 32             | ED                   | ED             | Wm*Wm, Acc, Wx, Wy, Wxd          | Euclidean Distance (no accumulate)                                             | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 33             | EDAC                 | EDAC           | Wm*Wm, Acc, Wx, Wy, Wxd          | Euclidean Distance                                                             | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 34             | EXCH                 | EXCH           | Wns,Wnd                          | Swap Wns with Wnd                                                              | 1             | 1              | None                     |

| 35             | FBCL                 | FBCL           | Ws,Wnd                           | Find Bit Change from Left (MSb) Side                                           | 1             | 1              | С                        |

| 36             | FF1L                 | FF1L           | Ws,Wnd                           | Find First One from Left (MSb) Side                                            | 1             | 1              | С                        |

| 37             | FF1R                 | FF1R           | Ws, Wnd                          | Find First One from Right (LSb) Side                                           | 1             | 1              | С                        |

| 38             | GOTO                 | GOTO           | Expr                             | Go to address                                                                  | 2             | 2              | None                     |

|                |                      | GOTO           | Wn                               | Go to indirect                                                                 | 1             | 2              | None                     |

| 39             | INC                  | INC            | f                                | f = f + 1                                                                      | 1             | 1              | C,DC,N,OV,Z              |

|                |                      | INC            | f,WREG                           | WREG = f + 1                                                                   | 1             | 1              | C,DC,N,OV,Z              |

|                |                      | INC            | Ws,Wd                            | Wd = Ws + 1                                                                    | 1             | 1              | C,DC,N,OV,Z              |

| 40             | INC2                 | INC2           | f                                | f = f + 2                                                                      | 1             | 1              | C,DC,N,OV,Z              |

|                |                      | INC2           | f,WREG                           | WREG = f + 2                                                                   | 1             | 1              | C,DC,N,OV,Z              |

|                |                      | INC2           | Ws,Wd                            | Wd = Ws + 2                                                                    | 1             | 1              | C,DC,N,OV,Z              |

| 41             | IOR                  | IOR            | f                                | f = f .IOR. WREG                                                               | 1             | 1              | N,Z                      |

|                |                      | IOR            | f,WREG                           | WREG = f .IOR. WREG                                                            | 1             | 1              | N,Z                      |

|                |                      | IOR            | #lit10,Wn                        | Wd = lit10 .IOR. Wd                                                            | 1             | 1              | N,Z                      |

|                |                      | IOR            | Wb, Ws, Wd                       | Wd = Wb .IOR. Ws                                                               | 1             | 1              | N,Z                      |

|                |                      | IOR            | Wb,#lit5,Wd                      | Wd = Wb .IOR. lit5                                                             | 1             | 1              | N,Z                      |

| 42             | LAC                  | LAC            | Wso,#Slit4,Acc                   | Load Accumulator                                                               | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 43             | LNK                  | LNK            | #lit14                           | Link frame pointer                                                             | 1             | 1              | None                     |

| 44             | LSR                  | LSR            | f                                | f = Logical Right Shift f                                                      | 1             | 1              | C,N,OV,Z                 |

|                |                      | LSR            | f,WREG                           | WREG = Logical Right Shift f                                                   | 1             | 1              | C,N,OV,Z                 |

|                |                      | LSR            | Ws,Wd                            | Wd = Logical Right Shift Ws                                                    | 1             | 1              | C,N,OV,Z                 |

|                |                      | LSR            | Wb, Wns, Wnd                     | Wnd = Logical Right Shift Wb by Wns                                            | 1             | 1              | N,Z                      |

|                |                      | LSR            | Wb, #lit5, Wnd                   | Wnd = Logical Right Shift Wb by lit5                                           | 1             | 1              | N,Z                      |

| 45             | MAC                  | MAC            | Wm*Wn, Acc, Wx, Wxd, Wy, Wyd     | Multiply and Accumulate                                                        | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                |                      | MAC            | AWB Wm*Wm, Acc, Wx, Wxd, Wy, Wyd | Square and Accumulate                                                          | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 46             | MOV                  | MOV            | f,Wn                             | Move f to Wn                                                                   | 1             | 1              | None                     |

| .0             | 110 V                | MOV            | f                                | Move f to f                                                                    | 1             | 1              | N,Z                      |

|                |                      | MOV            | f,WREG                           | Move f to WREG                                                                 | 1             | 1              | N,Z                      |

|                |                      | MOV            | #lit16,Wn                        | Move 16-bit literal to Wn                                                      | 1             | 1              | None                     |

|                |                      | MOV.b          | #11t18,Wn                        | Move 8-bit literal to Wn                                                       | 1             | 1              | None                     |

|                |                      | MOV.D          | Wn, f                            | Move Wn to f                                                                   | 1             | 1              | None                     |

|                |                      | MOV            |                                  | Move Ws to Wd                                                                  | 1             | 1              | None                     |

|                |                      | MOV            | Wso, Wdo                         |                                                                                | 1             |                |                          |

|                |                      | I PIUV         | WREG, f                          | Move WREG to f                                                                 | 1             | 1              | N,Z                      |

|                |                      |                |                                  | Mayo Double from \\(\frac{1}{2}\)/22 + 4\ 42 \\\(\frac{1}{2}\)                 | 1             | r              | None                     |

|                |                      | MOV.D<br>MOV.D | Wns,Wd<br>Ws,Wnd                 | Move Double from W(ns):W(ns + 1) to Wd  Move Double from Ws to W(nd + 1):W(nd) | 1             | 2              | None<br>None             |

#### 23.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC30F electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

For detailed information about the dsPIC30F architecture and core, refer to "dsPIC30F Family Reference Manual" (DS70046).

Absolute maximum ratings for the dsPIC30F family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                      | 40°C to +125°C       |

|-------------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                                 | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD and MCLR)(1)                     | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                                                  | 0.3V to +5.5V        |

| Voltage on MCLR with respect to Vss                                                 | 0V to +13.25V        |

| Maximum current out of Vss pin                                                      | 300 mA               |

| Maximum current into VDD pin <sup>(2)</sup>                                         |                      |

| Input clamp current, IiK (VI < 0 or VI > VDD)                                       | ±20 mA               |

| Output clamp current, lok (Vo < 0 or Vo > VDD)                                      | ±20 mA               |

| Maximum output current sunk by any I/O pin                                          | 25 mA                |

| Maximum output current sourced by any I/O pin                                       | 25 mA                |

| Maximum current sunk by all ports                                                   | 200 mA               |

| Maximum current sourced by all ports <sup>(2)</sup>                                 | 200 mA               |

| Note 1: Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater the | <u>-</u>             |

Note 1: Voltage spikes below VSs at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latchup. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP pin, rather than pulling this pin directly to VSs.

2: Maximum allowable current is a function of device maximum power dissipation. See Table 23-2 for PDMAX.

**†NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 23.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC30F AC characteristics and timing parameters.

TABLE 23-13: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 2.5V to 5.5V             |

|--------------------|---------------------------------------------------------|

|                    | (unless otherwise stated)                               |

| AC CHARACTERISTICS | Operating temperature -40°C ≤TA ≤+85°C for Industrial   |

|                    | -40°C ≤TA ≤+125°C for Extended                          |

|                    | Operating voltage VDD range as described in Table 23-1. |

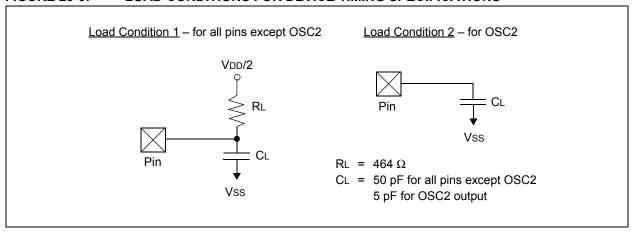

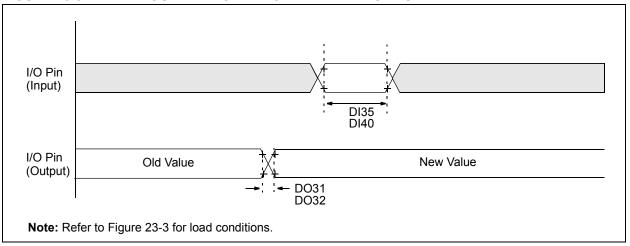

#### FIGURE 23-3: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

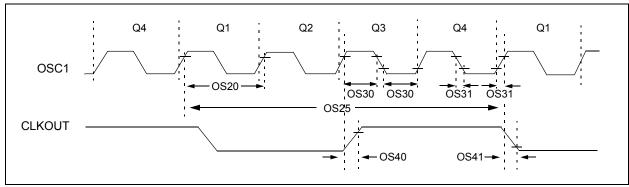

#### FIGURE 23-4: EXTERNAL CLOCK TIMING

#### FIGURE 23-5: CLKOUT AND I/O TIMING CHARACTERISTICS

#### TABLE 23-20: CLKOUT AND I/O TIMING REQUIREMENTS

| AC CHAR      | ACTERISTI | cs                    | Standard Oper<br>(unless otherw<br>Operating temp | vise state | e <b>d)</b><br>-40°C ≤ī | ¯a ≤+85°( |       |            |

|--------------|-----------|-----------------------|---------------------------------------------------|------------|-------------------------|-----------|-------|------------|

| Param<br>No. | Symbol    | Characterist          | ic <sup>(1)(2)(3)</sup>                           | Min        | Typ <sup>(4)</sup>      | Max       | Units | Conditions |

| DO31         | TioR      | Port output rise time | Port output rise time                             |            | 7                       | 20        | ns    |            |

| DO32         | TioF      | Port output fall time |                                                   | _          | 7                       | 20        | ns    |            |

| DI35         | TINP      | INTx pin high or low  | time (output)                                     | 20         | _                       |           | ns    |            |

| DI40         | TRBP      | CNx high or low time  | (input)                                           | 2 Tcy      | _                       |           | ns    |            |

- Note 1: These parameters are asynchronous events not related to any internal clock edges

- 2: Measurements are taken in RC mode and EC mode where CLKOUT output is 4 x Tosc.

- 3: These parameters are characterized but not tested in manufacturing.

- **4:** Data in "Typ" column is at 5V, 25°C unless otherwise stated.

NOTES:

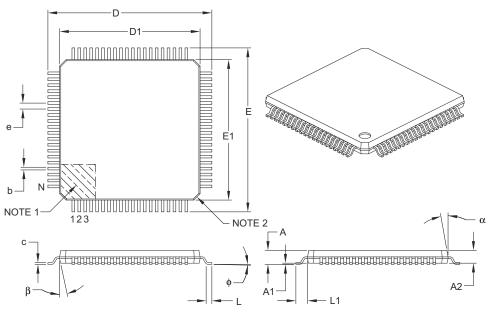

#### 24.0 PACKAGING INFORMATION

#### 24.1 Package Marking Information

64-Lead TQFP

### 80-Lead TQFP

#### Example

#### Example

Legend: XX...X Customer-specific information

Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

By-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (©3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

#### 80-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |           | MILLIMETERS | }    |  |

|--------------------------|------------------|-----------|-------------|------|--|

|                          | Dimension Limits | MIN       | NOM         | MAX  |  |

| Number of Leads          | N                |           | 80          |      |  |

| Lead Pitch               | е                |           | 0.50 BSC    |      |  |

| Overall Height           | A                | _         | _           | 1.20 |  |

| Molded Package Thickness | A2               | 0.95      | 1.00        | 1.05 |  |

| Standoff                 | A1               | 0.05      | -           | 0.15 |  |

| Foot Length              | L                | 0.45      | 0.60        | 0.75 |  |

| Footprint                | L1               |           | 1.00 REF    |      |  |

| Foot Angle               | ф                | 0°        | 3.5°        | 7°   |  |

| Overall Width            | E                |           | 14.00 BSC   |      |  |

| Overall Length           | D                | 14.00 BSC |             |      |  |

| Molded Package Width     | E1               | 12.00 BSC |             |      |  |

| Molded Package Length    | D1               | 12.00 BSC |             |      |  |

| Lead Thickness           | С                | 0.09      | _           | 0.20 |  |

| Lead Width               | b                | 0.17      | 0.22        | 0.27 |  |

| Mold Draft Angle Top     | α                | 11°       | 12°         | 13°  |  |

| Mold Draft Angle Bottom  | β                | 11°       | 12°         | 13°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-092B

NOTES:

| Output Compare Module                                   | 85     | Erasing a Row of Program Memory                     | 53       |

|---------------------------------------------------------|--------|-----------------------------------------------------|----------|

| Register Map                                            |        | Initiating the Programming Sequence                 |          |

| Timing Characteristics                                  |        | Loading Write Latches                               |          |

| Timing Requirements                                     |        | Protection Against Accidental Writes to OSCCON      | 149      |

| Output Compare Operation During CPU Idle Mode           | 88     | D.                                                  |          |

| Output Compare Sleep Mode Operation                     | 88     | R                                                   |          |

| P                                                       |        | Reader Response                                     |          |

|                                                         |        | Reset                                               |          |

| Packaging Information                                   |        | Reset Sequence                                      |          |

| Marking                                                 |        | Reset Sources                                       | 47       |

| Peripheral Module Disable (PMD) Registers               |        | Reset Sources                                       | 47       |

| Pinout Descriptions                                     | 14     | Brown-out Reset (BOR)                               |          |

| POR. See Power-on Reset. PORTA                          |        | Illegal Instruction Trap<br>Trap Lockout            |          |

| Register Map for dsPIC30F6013A/6014A                    | 63     | Uninitialized W Register Trap                       |          |

| PORTB                                                   | 03     | Watchdog Time-out                                   |          |

| Register Map for dsPIC30F6011A/6012A/6013A/             | /6014A | Reset Timing Characteristics                        |          |

| 63                                                      | 001111 | Reset Timing Requirements                           |          |

| PORTC                                                   |        | Resets                                              |          |

| Register Map for dsPIC30F6011A/6012A                    | 63     | Brown-out Rest (BOR), Programmable                  | 155      |

| Register Map for dsPIC30F6013A/6014A                    |        | POR with Long Crystal Start-up Time                 |          |

| PORTD                                                   |        | POR, Operating without FSCM and PWRT                |          |

| Register Map for dsPIC30F6011A/6012A                    | 64     | Power-on Reset (POR)                                |          |

| Register Map for dsPIC30F6013A/6014A                    | 64     | RTSP Operation                                      | 52       |

| PORTF                                                   |        | Run-Time Self-Programming (RTSP)                    | 51       |

| Register Map for dsPIC30F6011A/6012A                    |        | S                                                   |          |

| Register Map for dsPIC30F6013A/6014A                    | 64     |                                                     |          |

| PORTG                                                   |        | Serial Peripheral Interface. See SPI                |          |

| Register Map for dsPIC30F6011A/6012A/6013A/             | /      | Simple Capture Event Mode                           | 81       |

| 6014A                                                   | 65     | Buffer Operation                                    |          |

| Power Saving Modes                                      |        | Hall Sensor Mode                                    |          |

| Idle                                                    |        | Prescaler                                           |          |

| Sleep                                                   |        | Timer2 and Timer3 Selection Mode                    |          |

| Power-Down Current (IPD)                                |        | Simple OC/PWM Mode Timing Requirements              |          |

| Power-on Reset (POR)                                    |        | Simple Output Compare Match Mode<br>Simple PWM Mode |          |

| Oscillator Start-up Timer (OST)                         |        | Input Pin Fault Protection                          |          |

| Power Saving Modes                                      |        | Period                                              |          |

| Power-Saving Modes  Power-Saving Modes (Sleep and Idle) |        | Software Simulator (MPLAB SIM)                      |          |

| Power-up Timer                                          | 143    | Software Stack Pointer, Frame Pointer               |          |

| Timing Characteristics                                  | 188    | CALL Stack Frame                                    |          |

| Timing Requirements                                     |        | SPI Module                                          |          |

| Program Address Space                                   |        | Framed SPI Support                                  |          |

| Construction                                            |        | Operating Function Description                      |          |

| Data Access from Program Memory                         |        | Operation During CPU Idle Mode                      | 93       |

| Using Program Space Visibility                          |        | Operation During CPU Sleep Mode                     | 93       |

| Data Access from Program Memory                         |        | SDOx Disable                                        |          |

| Using Table Instructions                                | 28     | Slave Select Synchronization                        |          |

| Data Access from, Address Generation                    | 27     | SPI1 Register Map                                   |          |

| Data Space Window into Operation                        |        | SPI2 Register Map                                   | 94       |

| Data Table Access (Least Significant Word)              |        | Timing Characteristics                              |          |

| Data Table Access (MSB)                                 |        | Master Mode (CKE = 0)                               |          |

| Memory Map for dsPIC30F6011A/6013A                      |        | Master Mode (CKE = 1)                               |          |

| Memory Map for dsPIC30F6012A/6014A                      | 26     | Slave Mode (CKE = 1)                                | 200, 201 |

| Table Instructions                                      |        | Timing Requirements                                 | 400      |

| TBLRDH                                                  |        | Master Mode (CKE = 0)                               |          |

| TBLRDL                                                  |        | Master Mode (CKE = 1)                               |          |

| TBLWTH                                                  |        | Slave Mode (CKE = 0)                                |          |

| TBLWTL                                                  |        |                                                     |          |

| Program and EEPROM Characteristics                      |        | Word and Byte CommunicationSTATUS Register          |          |

| Programmable                                            |        | Symbols used in Opcode Descriptions                 |          |

| Programmar's Model                                      |        | System Integration                                  |          |

| Programmer's Model                                      |        | Register Map for dsPIC30F601xA                      |          |

| Programming Operations                                  |        | regions map for doi 10001 00 1/1 (                  |          |

| Algorithm for Program Flash                             |        |                                                     |          |