# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Not For New Designs                                                    |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                       |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 50MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | DMA, LCD, WDT                                                          |

| Number of I/O              | 38                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 16K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                           |

| Data Converters            | A/D 6x16b, 4x24b                                                       |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkm33z128clh5r |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 Ordering parts

## 1.1 Determining valid order-able parts

Valid order-able part numbers are provided on the web. To determine the order-able part numbers for this device, go to freescale.com and perform a part number search for the following device numbers:

- MKM13Z64CHH5

- MKM14Z64CHH5

- MKM14Z128CHH5

- MKM32Z64CLH5

- MKM33Z64CLH5

- MKM33Z128CLH5

- MKM32Z64CLL5

- MKM33Z64CLL5

- MKM33Z128CLL5

- MKM34Z128CLL5

- MKM38Z128CLL5

## 2 Part identification

## 2.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

## 2.2 Format

Part numbers for this device have the following format:

Q K M S R FFF T PP CC N

## 2.3 Fields

Following table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description                    | Values                                                                                                                                                                   |

|-------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q     | Qualification status           | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Pre-qualification (Proto)</li> </ul>                                                                      |

| К     | Main family                    | K = Kinetis                                                                                                                                                              |

| М     | Sub family                     | <ul> <li>M1 = Metering only (No LCD support)</li> <li>M3 = Metering with LCD support</li> </ul>                                                                          |

| S     | Number of Sigma Delta (SD) ADC | <ul> <li>2 = 1 SD ADC with PGA and 1 SD ADC</li> <li>3 = 2 SD ADC with PGA and 1 SD ADC</li> <li>4 = 2 SD ADC with PGA and 2 SD ADC</li> <li>8 = Same as '4'.</li> </ul> |

| R     | Silicon revision               | <ul> <li>Z = Initial</li> <li>(Blank) = Main</li> <li>A = Revision after main</li> </ul>                                                                                 |

| FFF   | Program flash memory size      | <ul> <li>64 = 64 KB</li> <li>128 = 128 KB</li> </ul>                                                                                                                     |

| Т     | Temperature range (°C)         | • C = -40 to 85                                                                                                                                                          |

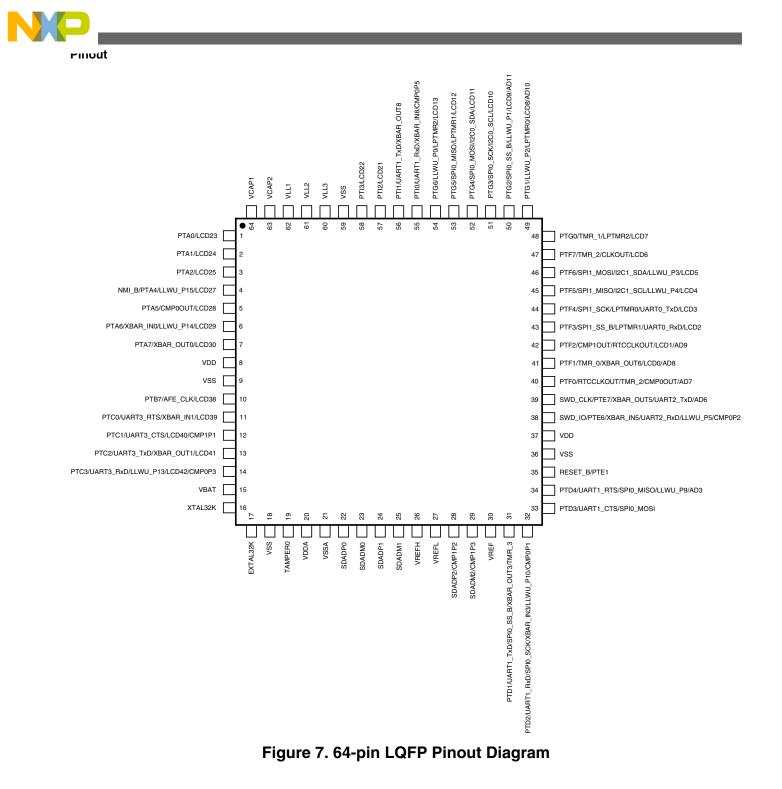

| PP    | Package identifier             | <ul> <li>HH = 44 LGA (5 mm x 5 mm)</li> <li>LH = 64 LQFP (10 mm x 10 mm)</li> <li>LL = 100 LQFP (14 mm x 14 mm)</li> </ul>                                               |

| CC    | Maximum CPU frequency (MHz)    | • 5 = 50 MHz                                                                                                                                                             |

| N     | Packaging type                 | <ul> <li>R = Tape and reel</li> <li>(Blank) = Trays</li> </ul>                                                                                                           |

## 2.4 Example

This is an example part number:

• MKM34Z128CLL5

## 3 Terminology and guidelines

### 3.1 Definition: Operating requirement

An *operating requirement* is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.

### 3.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol          | Description                                    | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

### 3.8.2 Example 2

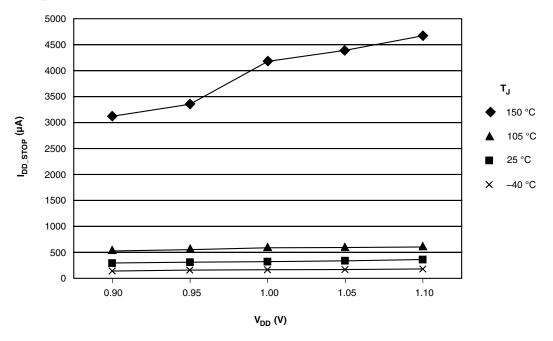

This is an example of a chart that shows typical values for various voltage and temperature conditions:

## 3.9 Typical value conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description          | Value | Unit |

|-----------------|----------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature  | 25    | C°   |

| V <sub>DD</sub> | 3.3 V supply voltage | 3.3   | V    |

## 4 Ratings

## 4.1 Thermal handling ratings

| Symbol           | Description                   | Min. | Max. | Unit | Notes |

|------------------|-------------------------------|------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | -55  | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | —    | 260  | °C   | 2     |

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

## 4.2 Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level | _    | 3    |      | 1     |

1. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

## 4.3 ESD handling ratings

| Symbol            | Description                                                                   | Min.  | Max.  | Unit | Notes |

|-------------------|-------------------------------------------------------------------------------|-------|-------|------|-------|

| V <sub>HBM</sub>  | Electrostatic discharge voltage, human body model (All pins except RESET pin) | -4000 | +4000 | V    | 1     |

|                   | Electrostatic discharge voltage, human body model (RESET pin only)            | -2500 | +2500 | V    | 1     |

| V <sub>CDM</sub>  | Electrostatic discharge voltage, charged-device model (for corner pins)       | -750  | +750  | V    | 2     |

| V <sub>CDM</sub>  | Electrostatic discharge voltage, charged-device model                         | -500  | +500  | V    | 3     |

| V <sub>PESD</sub> | Powered ESD voltage                                                           | -6000 | +6000 | V    |       |

| I <sub>LAT</sub>  | Latch-up current at ambient temperature of 105°C                              | -100  | +100  | mA   |       |

1. Determined according to JEDEC Standard JESD22-A114, *Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)*.

2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

3. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

## 4.4 Voltage and current operating ratings

| Symbol               | Description                                                               | Min.                  | Max.                   | Unit |

|----------------------|---------------------------------------------------------------------------|-----------------------|------------------------|------|

| V <sub>DD</sub>      | Digital supply voltage                                                    | -0.3                  | 3.6                    | V    |

| V <sub>DIO</sub>     | Digital input voltage (except RESET, EXTAL, and XTAL)                     | -0.3                  | V <sub>DD</sub> + 0.3  | V    |

| V <sub>DTamper</sub> | Tamper input voltage                                                      | -0.3                  | V <sub>BAT</sub> + 0.3 | V    |

| V <sub>AIO</sub>     | Analog <sup>1</sup> , RESET, EXTAL, and XTAL input voltage                | -0.3                  | V <sub>DD</sub> + 0.3  | V    |

| Ι <sub>D</sub>       | Instantaneous maximum current single pin limit (applies to all port pins) | -25                   | 25                     | mA   |

| V <sub>DDA</sub>     | Analog supply voltage                                                     | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3  | V    |

| V <sub>BAT</sub>     | RTC battery supply voltage                                                | -0.3                  | 3.6                    | V    |

1. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

## 5 General

### 5.1 AC electrical characteristics

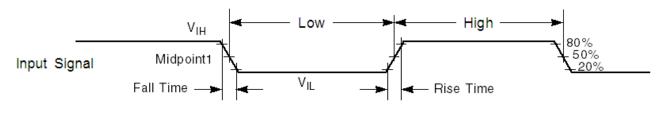

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL}$  +  $(V_{IH} - V_{IL})/2$ .

Figure 1. Input signal measurement reference

### 5.2 Nonswitching electrical specifications

General

### 5.2.1 Voltage and current operating requirements

Table 1. Voltage and current operating requirements

| Symbol                                  | Description                                                                                                                                                        | Min.                  | Max.                 | Unit                                      | Notes |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|-------------------------------------------|-------|

| V <sub>DD</sub>                         | Supply voltage when AFE is operational                                                                                                                             | 2.7                   | 3.6                  | V                                         |       |

|                                         | Supply voltage when AFE is NOT operational                                                                                                                         | 1.71                  | 3.6                  | V                                         |       |

| V <sub>DDA</sub>                        | Analog supply voltage                                                                                                                                              | 2.7                   | 3.6                  | V                                         |       |

| $V_{DD} - V_{DDA}$                      | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                                                                                          | -0.1                  | 0.1                  | V                                         |       |

| $V_{SS} - V_{SSA}$                      | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage                                                                                                          | -0.1                  | 0.1                  | V                                         |       |

| V <sub>BAT</sub>                        | RTC battery supply voltage                                                                                                                                         | 1.71                  | 3.6                  | V                                         | 1     |

| V <sub>IH</sub>                         | Input high voltage                                                                                                                                                 |                       |                      |                                           |       |

|                                         | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                                                                                        | $0.7 \times V_{DD}$   | _                    | V                                         |       |

| V <sub>IL</sub> I<br>V <sub>HYS</sub> I | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                                                       | $0.75 \times V_{DD}$  | —                    | V                                         |       |

| V <sub>IL</sub>                         | Input low voltage                                                                                                                                                  |                       |                      |                                           |       |

|                                         | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$                                                                                                       | —                     | $0.35 \times V_{DD}$ | V                                         |       |

|                                         | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                                                       | —                     | $0.3 \times V_{DD}$  | V                                         |       |

| V <sub>HYS</sub>                        | Input hysteresis                                                                                                                                                   | $0.06 \times V_{DD}$  | _                    | V                                         |       |

| I <sub>ICDIO</sub>                      | Digital pin negative DC injection current — single pin                                                                                                             |                       |                      |                                           |       |

|                                         | • V <sub>IN</sub> < V <sub>SS</sub> -0.3V                                                                                                                          | -5                    | —                    | mA                                        |       |

| I <sub>ICAIO</sub>                      | Analog <sup>2</sup> , EXTAL, and XTAL pin DC injection current — single pin                                                                                        |                       |                      | m۸                                        |       |

|                                         | <ul> <li>V<sub>IN</sub> &lt; V<sub>SS</sub>-0.3V (Negative current injection)</li> </ul>                                                                           | -3                    | _                    | V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V |       |

|                                         | <ul> <li>V<sub>IN</sub> &gt; V<sub>DD</sub>+0.3V (Positive current injection)</li> </ul>                                                                           | —                     | +3                   |                                           |       |

| I <sub>ICcont</sub>                     | Contiguous pin DC injection current —regional limit,<br>includes sum of negative injection currents or sum of<br>positive injection currents of 16 contiguous pins |                       |                      |                                           |       |

|                                         | Negative current injection                                                                                                                                         | -25                   | _                    | mA                                        |       |

|                                         | Positive current injection                                                                                                                                         | —                     | +25                  |                                           |       |

| V <sub>RFVBAT</sub>                     | V <sub>BAT</sub> voltage required to retain the VBAT register file                                                                                                 | V <sub>POR_VBAT</sub> | _                    | V                                         |       |

1. V<sub>BAT</sub> always needs to be there for the chip to be operational.

2. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

## 5.2.2 LVD and POR operating requirements

Table 2. V<sub>DD</sub> supply LVD and POR operating requirements

| Symbol            | Description                                                 | Min. | Тур. | Max. | Unit | Notes |

|-------------------|-------------------------------------------------------------|------|------|------|------|-------|

| V <sub>POR</sub>  | Falling VDD POR detect voltage                              | 0.8  | 1.1  | 1.5  | V    |       |

| V <sub>LVDH</sub> | Falling low-voltage detect threshold — high range (LVDV=01) | 2.48 | 2.56 | 2.64 | V    |       |

Table continues on the next page ...

| Symbol           | Description                                                                                           | Min. | Max. | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>OL</sub>  | Output low voltage — high-drive strength                                                              |      |      |      |       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 20 mA                                  | _    | 0.5  | V    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OL</sub> = 10 mA                                 | _    | 0.5  | V    |       |

|                  | Output low voltage — low-drive strength                                                               |      |      |      |       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 5 mA                                   | —    | 0.5  | V    |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OL}} = 2.5 \text{ mA}$ | _    | 0.5  | V    |       |

| I <sub>OLT</sub> | Output low current total for all ports                                                                |      | 100  | mA   |       |

| I <sub>OZ</sub>  | Hi-Z (off-state) leakage current (per pin)                                                            | —    | 1    | μA   |       |

| R <sub>PU</sub>  | Internal pullup resistors                                                                             | 30   | 60   | kΩ   | 1,    |

| R <sub>PD</sub>  | Internal pulldown resistors                                                                           | 30   | 60   | kΩ   | 2     |

### Table 4. Voltage and current operating behaviors (continued)

- 1. Measured at Vinput =  $V_{SS}$

- 2. Measured at Vinput =  $V_{DD}$

### 5.2.4 Power mode transition operating behaviors

All specifications except  $t_{POR}$ , and VLLSx $\rightarrow$ RUN recovery times in the following table assume this clock configuration:

- CPU and system clocks = 50 MHz

- Bus clock = 25 MHz

- Flash clock = 25 MHz

- Temp: -40 °C, 25 °C, and 85 °C

- V<sub>DD</sub>: 1.71 V, 3.3 V, and 3.6 V

### Table 5. Power mode transition operating behaviors

| Symbol           | Description                                                                                                                                                   | Min. | Max. | Unit | Notes |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 1.71 V to execute the first instruction across the operating temperature range of the chip. | 563  | 659  | μs   | 1     |

|                  | VLLS0 → RUN                                                                                                                                                   | —    | 372  | μs   |       |

|                  | • VLLS1 → RUN                                                                                                                                                 | —    | 372  | μs   |       |

|                  | • VLLS2 $\rightarrow$ RUN                                                                                                                                     | _    | 273  | μs   |       |

|                  | VLLS3 → RUN                                                                                                                                                   | _    | 273  | μs   |       |

|                  | • VLPS → RUN                                                                                                                                                  | —    | 5.0  | μs   |       |

Table continues on the next page...

#### Symbol Description Min. Тур. Max. Unit Notes Very-low-power wait mode current at 3.0 V - all 6 I<sub>DD\_VLPW</sub> peripheral clocks disabled 162 350 μΑ • 25 °C • -40 °C 158.50 330 μΑ • 105 °C 446.94 1700 μA Stop mode current at 3.0 V IDD\_STOP • 25 °C 311.90 730 μΑ • -40 °C 364 700 • 105 °C μΑ 645.13 2250 μA Very-low-power stop mode current at 3.0 V I<sub>DD\_VLPS</sub> • 25 °C 8.56 46 μΑ • -40 °C • 105 °C 44 μΑ 1500 μΑ Very low-leakage stop mode 3 current at 3.0 V I<sub>DD\_VLLS3</sub> • 25 °C 1.98 3.5 μA • -40 °C • 105 °C 3.3 μΑ 85 μΑ Very low-leakage stop mode 2 current at 3.0 V I<sub>DD\_VLLS2</sub> • 25 °C 1.24 2.6 μΑ • -40 °C • 105 °C 2.5 μΑ 59.5 μΑ IDD\_VLLS1 Very low-leakage stop mode 1 current at 3.0 V • 25 °C 0.89 1.7 μΑ • -40 °C • 105 °C 1.6 μΑ 38.8 μA Very low-leakage stop mode 0 current at 3.0 V IDD\_VLLS0 with POR detect circuit disabled 0.35 0.67 μΑ • 25 °C • -40 °C 0.64 μA • 105 °C 38 μΑ Very low-leakage stop mode 0 current at 3.0 V IDD VLLSO with POR detect circuit enabled 0.472 0.76 μΑ • 25 °C • -40 °C 0.72 μΑ • 105 °C 38.4 μA Average current with RTC and 32 kHz disabled IDD\_VBAT at 3.0 V and VDD is OFF 0.3 1 μΑ • 25 °C 0.95 • -40 °C μΑ • 105 °C 15 μΑ

### Table 6. Power consumption operating behaviors (continued)

Table continues on the next page ...

General

### 5.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

### 5.2.8 Capacitance attributes

### Table 8. Capacitance attributes

| Symbol                 | Description                          | Min. | Max. | Unit |

|------------------------|--------------------------------------|------|------|------|

| C <sub>IN_A</sub>      | Input capacitance: analog pins       | _    | 7    | pF   |

| C <sub>IN_D</sub>      | Input capacitance: digital pins      | —    | 7    | pF   |

| C <sub>IN_D_io60</sub> | Input capacitance: fast digital pins | _    | 9    | pF   |

## 5.3 Switching specifications

## 5.3.1 Device clock specifications

### Table 9. Device clock specifications

| Symbol             | Description                      | Min. | Max. | Unit | Notes |

|--------------------|----------------------------------|------|------|------|-------|

|                    | Normal run mode                  | Э    |      |      |       |

| f <sub>SYS</sub>   | System and core clock            |      | 50   | MHz  |       |

| f <sub>BUS</sub>   | Bus clock                        |      | 25   | MHz  |       |

| f <sub>FLASH</sub> | Flash clock                      |      | 25   | MHz  |       |

| f <sub>AFE</sub>   | AFE Modulator clock              |      | 6.5  | MHz  |       |

|                    | VLPR mode <sup>1</sup>           |      |      |      |       |

| f <sub>SYS</sub>   | System and core clock            |      | 2    | MHz  |       |

| f <sub>BUS</sub>   | Bus clock                        |      | 1    | MHz  |       |

| f <sub>FLASH</sub> | Flash clock                      |      | 1    | MHz  |       |

| f <sub>AFE</sub>   | AFE Modulator clock <sup>2</sup> |      | 1.6  | MHz  |       |

1. The frequency limitations in VLPR mode here override any frequency specification listed in the timing specification for any other module.

2. AFE working in low-power mode.

### rempheral operating requirements and behaviors

| Symbol                | Description                                 | Min.     | Тур.   | Max.                                                        | Unit | Notes |

|-----------------------|---------------------------------------------|----------|--------|-------------------------------------------------------------|------|-------|

| $f_{vco}$             | VCO operating frequency                     | 11.71875 | 12.288 | 14.648437<br>5                                              | MHz  |       |

| I <sub>pll</sub>      | PLL operating current<br>• IO 3.3 V current | _        | 300    | _                                                           | μA   | 9     |

|                       | Max core voltage current                    |          | 100    |                                                             |      |       |

| f <sub>pll_ref</sub>  | PLL reference frequency range               | 31.25    | 32.768 | 39.0625                                                     | kHz  |       |

| J <sub>cyc_pll</sub>  | PLL period jitter (RMS)                     |          |        |                                                             |      | 10    |

|                       | • f <sub>vco</sub> = 12 MHz                 |          |        | 700                                                         | ps   |       |

| D <sub>lock</sub>     | Lock entry frequency tolerance              | ± 1.49   | —      | ± 2.98                                                      | %    | 11    |

| D <sub>unl</sub>      | Lock exit frequency tolerance               | ± 4.47   | —      | ± 5.97                                                      | %    |       |

| t <sub>pll_lock</sub> | Lock detector detection time                | _        | _      | $150 \times 10^{-6}$<br>+ 1075(1/<br>f <sub>pll_ref</sub> ) | S    | 12    |

### Table 18. MCG specifications (continued)

- 1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

- 2. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

- 3. Chip max freq is 50 MHz, so Mid-range with DRS = 10 and High-range of DCO cannot be used and should not be configured.

- 4. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

- 5. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- 6. Chip max freq is 50 MHz, so Mid-range with DRS = 10 and High-range of DCO cannot be used and should not be configured.

- 7. This specification is based on standard deviation (RMS) of period or frequency.

- 8. This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- 9. Excludes any oscillator currents that are also consuming power while PLL is in operation.

- 10. This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary.

- 11. Will be updated later

- 12. This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

### 6.2.2 Oscillator electrical specifications

### 6.2.2.1 Oscillator DC electrical specifications Table 19. Oscillator DC electrical specifications

| [ | Symbol   | Description    | Min. | Тур. | Max. | Unit | Notes |

|---|----------|----------------|------|------|------|------|-------|

|   | $V_{DD}$ | Supply voltage | 1.71 | —    | 3.6  | V    |       |

Table continues on the next page...

| Symbol         | Description                                                             | Min.  | Тур. | Max. | Unit | Notes |

|----------------|-------------------------------------------------------------------------|-------|------|------|------|-------|

| IDDOSC         | Supply current — low-power mode (HGO=0)                                 |       |      |      |      | 1     |

|                | • 32 kHz                                                                | _     | 500  | _    | nA   |       |

|                | • 1 MHz                                                                 | _     | 200  | _    | μA   |       |

|                | • 4 MHz                                                                 | _     | 200  | _    | μA   |       |

|                | • 8 MHz (RANGE=01)                                                      | _     | 300  | _    | μA   |       |

|                | • 16 MHz                                                                | _     | 950  | _    | μA   |       |

|                | • 24 MHz                                                                | _     | 1.2  | _    | mA   |       |

|                | • 32 MHz                                                                | _     | 1.5  | —    | mA   |       |

| IDDOSC         | Supply current — high-gain mode (HGO=1)                                 |       |      |      |      | 1     |

|                | • 32 kHz                                                                | —     | 25   | —    | μA   |       |

|                | • 1 MHz                                                                 | —     | 300  | —    | μA   |       |

|                | • 4 MHz                                                                 | _     | 400  | _    | μA   |       |

|                | • 8 MHz (RANGE=01)                                                      | _     | 500  | _    | μA   |       |

|                | • 16 MHz                                                                | _     | 2.5  | _    | mA   |       |

|                | • 24 MHz                                                                | _     | 3    | _    | mA   |       |

|                | • 32 MHz                                                                | _     | 4    | —    | mA   |       |

| C <sub>x</sub> | EXTAL load capacitance                                                  |       |      |      |      | 2, 3  |

| Cy             | XTAL load capacitance                                                   | —     | _    | —    |      | 2, 3  |

|                | Capacitance of EXTAL                                                    | 247   | _    | —    | ff   |       |

|                | <ul><li>Die level (100 LQFP)</li><li>Package level (100 LQFP)</li></ul> | 0.495 |      |      | pF   |       |

|                | Capacitance of XTAL                                                     | 265   | _    | _    | ff   |       |

|                | <ul><li>Die level (100 LQFP)</li><li>Package level (100 LQFP)</li></ul> | 0.495 |      |      | pF   |       |

| R <sub>F</sub> | Feedback resistor — low-frequency, low-power mode (HGO=0)               | —     | —    | —    | MΩ   | 2, 4  |

|                | Feedback resistor — low-frequency, high-gain mode (HGO=1)               | _     | 10   | _    | MΩ   |       |

|                | Feedback resistor — high-frequency, low-power mode (HGO=0)              | —     | _    | —    | MΩ   |       |

|                | Feedback resistor — high-frequency, high-gain mode (HGO=1)              |       | 1    |      | MΩ   |       |

Table 19. Oscillator DC electrical specifications (continued)

Table continues on the next page ...

rempheral operating requirements and behaviors

### 6.4.1.1 16-bit ADC operating conditions Table 27. 16-bit ADC operating conditions

| Symbol                  | Description                               | Conditions                                                       | Min.              | Typ. <sup>1</sup> | Max.              | Unit | Notes |

|-------------------------|-------------------------------------------|------------------------------------------------------------------|-------------------|-------------------|-------------------|------|-------|

| V <sub>DDA</sub>        | Supply voltage                            | Absolute                                                         | 1.71              |                   | 3.6               | V    |       |

| $\Delta V_{\text{DDA}}$ | Supply voltage                            | Delta to V <sub>DD</sub> (V <sub>DD</sub> – V <sub>DDA</sub> )   | -100              | 0                 | +100              | mV   | 2     |

| $\Delta V_{SSA}$        | Ground voltage                            | Delta to V <sub>SS</sub> (V <sub>SS</sub> – V <sub>SSA</sub> )   | -100              | 0                 | +100              | mV   | 2     |

| $V_{REFH}$              | ADC reference voltage high                |                                                                  | 1.13              | V <sub>DDA</sub>  | V <sub>DDA</sub>  | V    |       |

| V <sub>REFL</sub>       | ADC reference<br>voltage low              |                                                                  | V <sub>SSA</sub>  | V <sub>SSA</sub>  | V <sub>SSA</sub>  | V    |       |

| V <sub>ADIN</sub>       | Input voltage                             |                                                                  | V <sub>REFL</sub> |                   | V <sub>REFH</sub> | V    |       |

| C <sub>ADIN</sub>       | Input capacitance                         | 16-bit mode                                                      | _                 | 8                 | 10                | pF   |       |

|                         |                                           | <ul> <li>8-bit / 10-bit / 12-bit<br/>modes</li> </ul>            | _                 | 4                 | 5                 |      |       |

| R <sub>ADIN</sub>       | Input series resistance                   |                                                                  | —                 | 2                 | 5                 | kΩ   |       |

| R <sub>AS</sub>         | Analog source<br>resistance<br>(external) | 12-bit modes<br>f <sub>ADCK</sub> < 4 MHz                        | _                 | _                 | 5                 | kΩ   | 3     |

| f <sub>ADCK</sub>       | ADC conversion<br>clock frequency         | ≤ 12-bit mode                                                    | 1.0               |                   | 18.0              | MHz  | 4     |

| f <sub>ADCK</sub>       | ADC conversion<br>clock frequency         | 16-bit mode                                                      | 2.0               | _                 | 12.0              | MHz  | 4     |

| C <sub>rate</sub>       | ADC conversion                            | ≤ 12-bit modes                                                   |                   |                   |                   |      | 5     |

|                         | rate                                      | No ADC hardware averaging                                        | 20.000            | —                 | 818.330           | Ksps |       |

|                         |                                           | Continuous conversions<br>enabled, subsequent<br>conversion time |                   |                   |                   |      |       |

| C <sub>rate</sub>       | ADC conversion                            | 16-bit mode                                                      |                   |                   |                   |      | 5     |

|                         | rate                                      | No ADC hardware averaging                                        | 37.037            | _                 | 461.467           | Ksps |       |

|                         |                                           | Continuous conversions<br>enabled, subsequent<br>conversion time |                   |                   |                   |      |       |

1. Typical values assume  $V_{DDA}$  = 3.0 V, Temp = 25 °C,  $f_{ADCK}$  = 1.0 MHz, unless otherwise stated. Typical values are for reference only, and are not tested in production.

2. DC potential difference.

- 3. This resistance is external to MCU. To achieve the best results, the analog source resistance must be kept as low as possible. The results in this data sheet were derived from a system that had < 8  $\Omega$  analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1 ns.

- 4. To use the maximum ADC conversion clock frequency, CFG2[ADHSC] must be set and CFG1[ADLPC] must be clear.

- 5. For guidelines and examples of conversion rate calculation, download the ADC calculator tool.

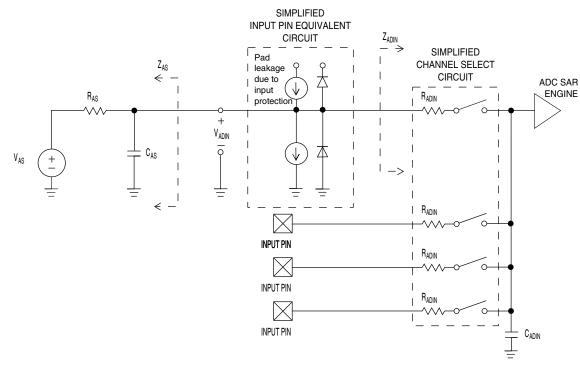

Peripheral operating requirements and behaviors

Figure 2. ADC input impedance equivalency diagram

### 6.4.1.2 16-bit ADC electrical characteristics

| Table 28. | 16-bit ADC | characteristics | (V <sub>REFH</sub> = | V <sub>DDA</sub> , | $V_{REFL} = V_{S}$ | isa) |

|-----------|------------|-----------------|----------------------|--------------------|--------------------|------|

|-----------|------------|-----------------|----------------------|--------------------|--------------------|------|

| Symbol               | Description                    | Conditions <sup>1</sup> .            | Min.         | Typ. <sup>2</sup> | Max.            | Unit             | Notes              |

|----------------------|--------------------------------|--------------------------------------|--------------|-------------------|-----------------|------------------|--------------------|

| I <sub>DDA_ADC</sub> | Supply current                 |                                      | 0.215        | —                 | 1.7             | mA               | 3                  |

|                      | ADC                            | • ADLPC = 1, ADHSC = 0               | 1.2          | 2.4               | 3.9             | MHz              | $t_{ADACK} = 1/$   |

|                      | asynchronous<br>clock source   | • ADLPC = 1, ADHSC = 1               | 2.4          | 4.0               | 6.1             | MHz              | f <sub>ADACK</sub> |

| f <sub>ADACK</sub>   |                                | • ADLPC = 0, ADHSC = 0               | 3.0          | 5.2               | 7.3             | MHz              |                    |

|                      |                                | • ADLPC = 0, ADHSC = 1               | 4.4          | 6.2               | 9.5             | MHz              |                    |

|                      | Sample Time                    | See Reference Manual chapter         | for sample t | times             |                 |                  |                    |

| TUE                  | Total unadjusted               | 12-bit modes                         | —            | ±4                | ±6.8            | LSB <sup>4</sup> | 5                  |

|                      | error                          | <ul> <li>&lt;12-bit modes</li> </ul> | _            | ±1.4              | ±2.1            |                  |                    |

| DNL                  | Differential non-<br>linearity | 12-bit modes                         | _            | ±0.7              | -1.1 to<br>+1.9 | LSB <sup>4</sup> | 5                  |

|                      |                                | <ul> <li>&lt;12-bit modes</li> </ul> | _            | ±0.2              | -0.3 to 0.5     |                  |                    |

| INL                  | Integral non-<br>linearity     | 12-bit modes                         | —            | ±1.0              | -2.7 to<br>+1.9 | LSB <sup>4</sup> | 5                  |

|                      |                                | • <12-bit modes                      | _            | ±0.5              | -0.7 to<br>+0.5 |                  |                    |

Table continues on the next page ...

### rempheral operating requirements and behaviors

| Symbol              | Description                     | Conditions <sup>1</sup> .                       | Min. | Typ. <sup>2</sup>      | Max. | Unit             | Notes                                                               |

|---------------------|---------------------------------|-------------------------------------------------|------|------------------------|------|------------------|---------------------------------------------------------------------|

| E <sub>FS</sub>     | Full-scale error                | 12-bit modes                                    |      | -4                     | -5.4 | LSB <sup>4</sup> | V <sub>ADIN</sub> =                                                 |

|                     |                                 | <li>&lt;12-bit modes</li>                       | _    | -1.4                   | -1.8 |                  | V <sub>DDA</sub> <sup>5</sup>                                       |

| EQ                  | Quantization                    | 16-bit modes                                    | _    | -1 to 0                |      | LSB <sup>4</sup> |                                                                     |

|                     | error                           | 12-bit modes                                    | _    | _                      | ±0.5 |                  |                                                                     |

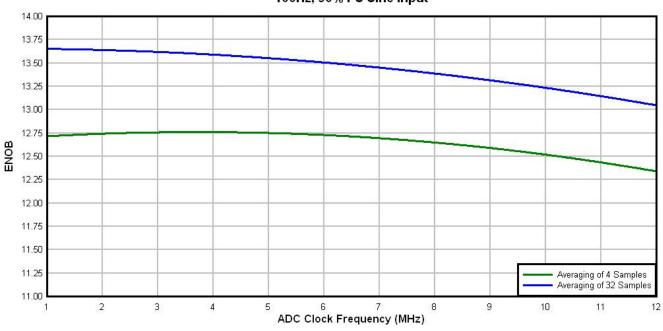

| ENOB                | Effective number                | 16-bit single-ended mode                        |      |                        |      |                  | 6                                                                   |

|                     | of bits                         | • Avg = 32                                      | 12.8 | 14.5                   | —    | bits             |                                                                     |

|                     |                                 | • Avg = 4                                       | 11.9 | 13.8                   |      | bits             |                                                                     |

|                     |                                 |                                                 | 12.2 | 13.9                   |      | bits             |                                                                     |

|                     |                                 |                                                 | 11.4 | 13.1                   | _    | bits             |                                                                     |

| SINAD               | Signal-to-noise plus distortion | See ENOB                                        | 6.02 | 2 × ENOB + 1           | 1.76 | dB               |                                                                     |

| THD                 | Total harmonic                  | 16-bit single-ended mode                        |      |                        |      |                  | 7                                                                   |

|                     | distortion                      | • Avg = 32                                      | _    | -94                    |      | dB               |                                                                     |

|                     |                                 |                                                 | _    | -85                    | _    | dB               |                                                                     |

| SFDR                | Spurious free                   | 16-bit single-ended mode                        |      |                        |      |                  | 7                                                                   |

|                     | dynamic range                   | • Avg = 32                                      | 82   | 95                     | _    | dB               |                                                                     |

|                     |                                 |                                                 | 78   | 90                     |      | dB               |                                                                     |

| EIL                 | Input leakage<br>error          |                                                 |      | $I_{ln} \times R_{AS}$ |      | mV               | I <sub>In</sub> =<br>leakage<br>current                             |

|                     |                                 |                                                 |      |                        |      |                  | (refer to<br>the MCL<br>voltage<br>and curre<br>operatin<br>ratings |

|                     | Temp sensor<br>slope            | Across the full temperature range of the device | 1.55 | 1.62                   | 1.69 | mV/°C            | 8                                                                   |

| V <sub>TEMP25</sub> | Temp sensor voltage             | 25 °C                                           | 706  | 716                    | 726  | mV               | 8                                                                   |

### Table 28. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

- 1. All accuracy numbers assume the ADC is calibrated with  $V_{REFH} = V_{DDA}$

- Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

- 4. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

8. ADC conversion clock < 3 MHz

Typical ADC 16-bit Single-Ended ENOB vs ADC Clock 100Hz, 90% FS Sine Input

Figure 3. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

### 6.4.2 CMP and 6-bit DAC electrical specifications Table 29. Comparator and 6-bit DAC electrical specifications

| Symbol             | Description                                        | Min.                  | Тур. | Max.            | Unit |

|--------------------|----------------------------------------------------|-----------------------|------|-----------------|------|

| V <sub>DD</sub>    | Supply voltage                                     | 1.71                  | _    | 3.6             | V    |

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)    | —                     | _    | 200             | μA   |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)     | —                     | —    | 20              | μA   |

| V <sub>AIN</sub>   | Analog input voltage                               | V <sub>SS</sub> – 0.3 | _    | V <sub>DD</sub> | V    |

| V <sub>AIO</sub>   | Analog input offset voltage                        | —                     | —    | 20              | mV   |

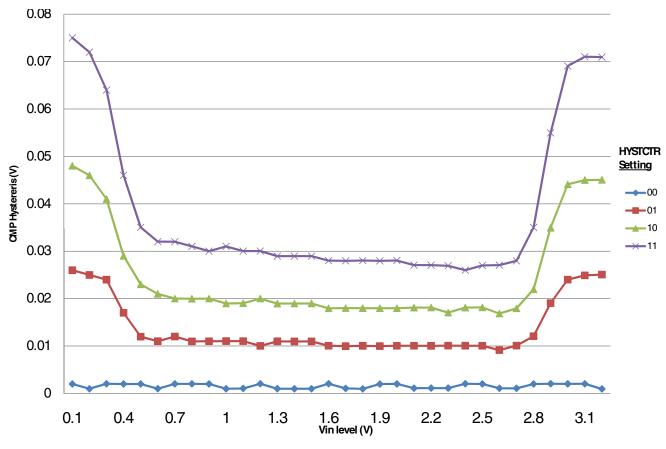

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>          |                       |      |                 |      |

|                    | • CR0[HYSTCTR] = 00                                | _                     | 5    | _               | mV   |

|                    | • CR0[HYSTCTR] = 01                                | _                     | 10   | _               | mV   |

|                    | • CR0[HYSTCTR] = 10                                | _                     | 20   | _               | mV   |

|                    | • CR0[HYSTCTR] = 11                                | —                     | 30   | _               | mV   |

| V <sub>CMPOh</sub> | Output high                                        | V <sub>DD</sub> – 0.5 | _    |                 | V    |

| V <sub>CMPOI</sub> | Output low                                         | —                     | _    | 0.5             | V    |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1) | 20                    | 50   | 200             | ns   |

Table continues on the next page ...

| Symbol             | Description                                         | Min. | Тур. | Max. | Unit             |

|--------------------|-----------------------------------------------------|------|------|------|------------------|

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN=1, PMODE=0)   | 80   | 250  | 600  | ns               |

|                    | Analog comparator initialization delay <sup>2</sup> | —    | —    | 40   | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)                   | —    | 7    | —    | μA               |

| INL                | 6-bit DAC integral non-linearity                    | -0.5 | —    | 0.5  | LSB <sup>3</sup> |

| DNL                | 6-bit DAC differential non-linearity                | -0.3 | —    | 0.3  | LSB              |

### Table 29. Comparator and 6-bit DAC electrical specifications (continued)

1. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD}$ –0.6 V.

- Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to CMP\_DACCR[DACEN], CMP\_DACCR[VRSEL], CMP\_DACCR[VOSEL], CMP\_MUXCR[PSEL], and CMP\_MUXCR[MSEL]) and the comparator output settling to a stable level.

- 3. 1 LSB =  $V_{reference}/64$

Figure 4. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 0)

| Symbol              | Description                                                       | Min.  | Тур. | Max.  | Unit  | Notes |

|---------------------|-------------------------------------------------------------------|-------|------|-------|-------|-------|

| VREFH               | Voltage reference output — user trim                              | 1.178 | —    | 1.202 | V     |       |

| VREFL               | Voltage reference output                                          | 0.38  | 0.4  | 0.42  | V     |       |

| V <sub>step</sub>   | Voltage reference trim step                                       | _     | 0.5  | _     | mV    |       |

| V <sub>tdrift</sub> | Temperature drift (Vmax - Vmin across the full temperature range) | _     | 5    | _     | mV    | 1     |

| Ac                  | Aging coefficient                                                 | _     | _    | 400   | uV/yr |       |

| I <sub>bg</sub>     | Bandgap only current                                              | _     | _    | 80    | μA    | 2     |

| I <sub>Ip</sub>     | Low-power buffer current                                          | _     | _    | 0.19  | μA    | 2     |

| I <sub>hp</sub>     | High-power buffer current                                         | _     | _    | 0.5   | mA    | 2     |

| I <sub>LOAD</sub>   | VREF buffer current                                               | _     | _    | 1     | mA    | 3     |

| $\Delta V_{LOAD}$   | Load regulation                                                   |       |      |       | mV    | 2, 4  |

|                     | • current = + 1.0 mA                                              | _     | 2    | _     |       |       |

|                     | • current = - 1.0 mA                                              |       | 5    |       |       |       |

| T <sub>stup</sub>   | Buffer startup time                                               | —     |      | 20    | ms    |       |

| V <sub>vdrift</sub> | Voltage drift (Vmax -Vmin across the full voltage range)          | —     | 0.5  | _     | mV    | 2     |

### Table 31. VREF full-range operating behaviors (continued)

1. For temp range -40  $^\circ C$  to 105  $^\circ C,$  this value is 15 mV

2. See the chip's Reference Manual for the appropriate settings of VREF Status and Control register.

- 3. See the chip's Reference Manual for the appropriate settings of SIM Miscellaneous Control Register.

- 4. Load regulation voltage is the difference between VREFH voltage with no load vs. voltage with defined load.

### Table 32. VREF limited-range operating requirements

| Symbol         | Description | Min. | Max. | Unit | Notes |

|----------------|-------------|------|------|------|-------|

| T <sub>A</sub> | Temperature | 0    | 50   | °C   |       |

### Table 33. VREF limited-range operating behaviours

| Symbol | Description                                      | Min.  | Max.  | Unit | Notes |

|--------|--------------------------------------------------|-------|-------|------|-------|

| VREFH  | Voltage reference<br>output with factory<br>trim | 1.173 | 1.225 | V    |       |

| VREFL  | Voltage reference<br>output                      | 0.38  | 0.42  | V    |       |

### 6.4.4 AFE electrical specifications

#

| Symbo<br>I                           | Description                                                                           | Conditions                                                                                                                                                                                           | Min      | Typ <sup>1</sup> | Max  | Unit   | Notes |

|--------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|------|--------|-------|

| f <sub>Nyq</sub>                     | Input bandwidth                                                                       | Normal Mode                                                                                                                                                                                          | 1.5      | 1.5              | 1.5  | kHz    |       |

|                                      |                                                                                       | Low-Power Mode                                                                                                                                                                                       | 1.5      | 1.5              | 1.5  |        |       |

| V <sub>CM</sub>                      | Input Common Mode<br>Reference                                                        |                                                                                                                                                                                                      | 0        |                  | 0.8  | V      |       |

| VIN <sub>diff</sub>                  | Input range                                                                           | Differential                                                                                                                                                                                         |          | +/- 500          |      | mV     |       |

|                                      |                                                                                       | Single Ended                                                                                                                                                                                         |          | +/- 250          |      | mV     |       |

| SNR                                  | Signal to Noise Ratio                                                                 | Normal Mode                                                                                                                                                                                          |          |                  |      | dB     |       |

|                                      |                                                                                       | <ul> <li>f<sub>IN</sub>=50Hz; common mode=0V,<br/>V<sub>pp</sub>= 500mV (differential<br/>ended)</li> <li>f<sub>IN</sub>=50Hz; common mode=0V,<br/>V<sub>pp</sub>= 500mV (full range se.)</li> </ul> | 88<br>76 | 90<br>78         |      |        |       |

|                                      |                                                                                       | Low-Power Mode<br>• $f_{IN}$ =50Hz; common mode=0V,<br>$V_{pp}$ =500mV (diff.)<br>• $f_{IN}$ =50Hz; common mode=0V,<br>$V_{pp}$ =500mV (full range se.)                                              |          |                  |      |        |       |

| ΔGain <sub>Te</sub><br><sup>mp</sup> | Gain Temperate Drift - Gain<br>error caused by<br>temperature drifts <sup>2</sup>     | <ul> <li>Gain bypassed Vpp = 500 mV<br/>(differential)</li> <li>PGA bypassed Vpp = 500 mV<br/>(differential), VCM = 0 V</li> </ul>                                                                   |          |                  | 55   | ppm/ºC |       |

| ∆Offset<br><sub>Temp</sub>           | Offset Temperate Drift -<br>Offset error caused by<br>temperature drifts <sup>3</sup> | <ul> <li>Gain bypassed Vpp = 500 mV<br/>(differential), VCM = 0 V</li> </ul>                                                                                                                         |          |                  | 30   | ppm/ºC |       |

| SINAD                                | Signal-to-Noise + Distortion<br>Ratio                                                 | Normal Mode<br>• f <sub>IN</sub> =50Hz; common mode=0V,<br>V <sub>pp</sub> = 500mV (diff.)<br>• f <sub>IN</sub> =50Hz; common mode=0V,<br>V <sub>pp</sub> = 500mV (full range se.)                   |          | 80               |      | dB     |       |

|                                      |                                                                                       | Low-Power Mode<br>• $f_{IN}$ =50Hz; common mode=0V,<br>$V_{pp}$ =500mV (diff.)<br>• $f_{IN}$ =50Hz; common mode=0V,<br>$V_{pp}$ =500mV (full range se.)                                              |          | 74               |      |        |       |

| CMMR                                 | Common Mode Rejection<br>Ratio                                                        | <ul> <li>f<sub>IN</sub>=50Hz; common mode=0V,<br/>V<sub>id</sub>=100 mV</li> </ul>                                                                                                                   |          | 90               |      | dB     |       |

| PSRR <sub>A</sub><br>c               | AC Power Supply Rejection Ratio                                                       | Gain=01, VCC = 3V ± 100mV, f <sub>IN</sub> =<br>50 Hz                                                                                                                                                |          | 60               |      | dB     |       |

| XT                                   | Crosstalk                                                                             | Gain=01, $V_{id}$ = 500 mV, $f_{IN}$ = 50 Hz                                                                                                                                                         |          |                  | -100 | dB     |       |

| f <sub>MCLK</sub>                    | Modulator Clock Frequency<br>Range                                                    | Normal Mode                                                                                                                                                                                          | 0.03     |                  | 6.5  | MHz    |       |

|                                      |                                                                                       | Low-Power Mode                                                                                                                                                                                       | 0.03     |                  | 1.6  |        |       |

| I <sub>DDA_AD</sub><br>C             | Current Consumption by ADC (each channel)                                             | Normal Mode (f <sub>MCLK</sub> = 6.144 MHz,<br>OSR= 2048)                                                                                                                                            |          |                  | 1.4  | mA     |       |

|                                      |                                                                                       | Low-Power Mode (f <sub>MCLK</sub> = 0.768MHz,<br>OSR= 256)                                                                                                                                           |          |                  | 0.5  |        |       |

Peripheral operating requirements and behaviors

| Description                                 | Min. | Max. | Unit | Notes |

|---------------------------------------------|------|------|------|-------|

| Rise time input <ul> <li>Master</li> </ul>  | 1    |      | ns   |       |

| Slave                                       | 1    |      |      |       |

| Fall time input <ul> <li>Master</li> </ul>  | 1    |      | ns   |       |

| Slave                                       | 1    |      |      |       |

| Rise time output <ul> <li>Master</li> </ul> | 30.4 |      | ns   |       |

| Slave                                       | 30.4 |      |      |       |

| Fall time output                            | 33.5 |      | ns   |       |

| Master     Slave                            | 29.0 |      |      |       |

Table 38. SPI switching characteristics at 1.7 V (1.7 - 3.6) (continued)

### Table 39. SPI switching characteristics at 2.7 V (2.7 - 3.6)

| Description                                                           | Min. | Max. | Unit | Notes |

|-----------------------------------------------------------------------|------|------|------|-------|

| Data Setup Time (inputs, tSUI)<br>• Master                            | 29   |      | ns   |       |

| Slave                                                                 | 4    |      |      |       |

| Input Data Hold Time (inputs, tHI) <ul> <li>Master</li> </ul>         | 0    |      | ns   |       |

| Slave                                                                 | 1    |      |      |       |

| Data hold time (outputs, tHO)<br>• Master                             | 0    |      | ns   |       |

| Slave                                                                 | 0    |      |      |       |

| Data Valid Out Time (after SCK edge, tDVO) <ul> <li>Master</li> </ul> | 49   |      | ns   |       |

| Slave                                                                 | 49   |      |      |       |

| Rise time input <ul> <li>Master</li> </ul>                            | 1    |      | ns   |       |

| Slave                                                                 | 1    |      |      |       |

| Fall time input <ul> <li>Master</li> </ul>                            | 1    |      | ns   |       |

| • Slave                                                               | 1    |      |      |       |

| Rise time output <ul> <li>Master</li> </ul>                           | 17.3 |      | ns   |       |

| • Slave                                                               | 17.3 |      |      |       |

| Fall time output<br>• Master                                          | 16.6 |      | ns   |       |

| Slave                                                                 | 16.0 |      |      |       |

## 6.7 Human-Machine Interfaces (HMI)

### 8.2.3 44-pin LGA

The following figure represents44-pin LGA pinouts: