Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Active                                                                         |

|-------------------------|--------------------------------------------------------------------------------|

| Туре                    | SC3850 Six Core                                                                |

| Interface               | Ethernet, I <sup>2</sup> C, PCI, RGMII, Serial RapidIO, SGMII, SPI, UART/USART |

| Clock Rate              | 1GHz                                                                           |

| Non-Volatile Memory     | ROM (96kB)                                                                     |

| On-Chip RAM             | 6.375MB                                                                        |

| Voltage - I/O           | 1.00V, 1.50V, 2.50V                                                            |

| Voltage - Core          | 1.00V                                                                          |

| Operating Temperature   | 0°C ~ 105°C                                                                    |

| Mounting Type           | Surface Mount                                                                  |

| Package / Case          | 783-BBGA, FCBGA                                                                |

| Supplier Device Package | 783-FCPBGA (29x29)                                                             |

| Purchase URL            | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=msc8157esvt1000a                  |

|                         |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 | Pin A  | ssignment                          |

|---|--------|------------------------------------|

|   | 1.1    | FC-PBGA Ball Layout Diagram        |

|   | 1.2    | Signal Lists                       |

| 2 | Electr | ical Characteristics               |

|   | 2.1    | Maximum Ratings                    |

|   | 2.2    | Recommended Operating Conditions40 |

|   | 2.3    | Thermal Characteristics41          |

|   | 2.4    | CLKIN/MCLKIN Requirements41        |

|   | 2.5    | DC Electrical Characteristics41    |

|   | 2.6    | AC Timing Characteristics          |

| 3 | Hard   | ware Design Considerations73       |

| 4 | Order  | ing Information                    |

| 5 | Packa  | age Information                    |

| 6 | Produ  | act Documentation75                |

#### **List of Figures**

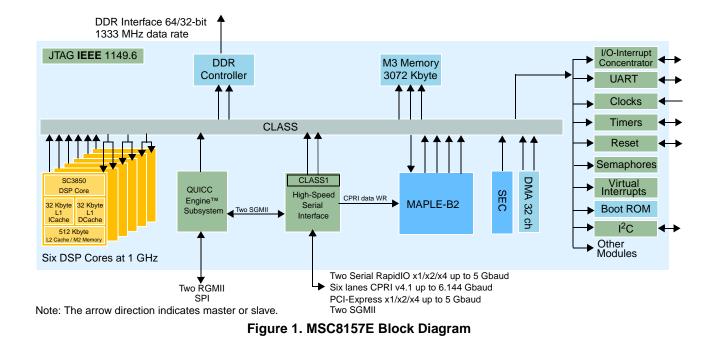

| MSC8157E Block Diagram 2                                     |

|--------------------------------------------------------------|

| MSC8157E FC-PBGA Package, Top View                           |

| Differential Voltage Definitions for Transmitter/Receiver 43 |

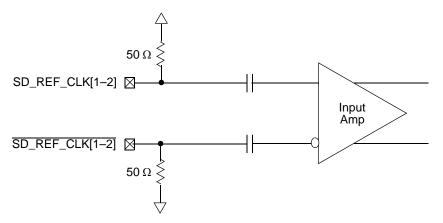

| Receiver of SerDes Reference Clocks 44                       |

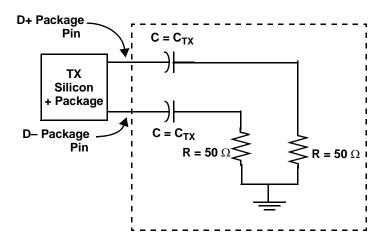

| SerDes Transmitter and Receiver Reference Circuits 45        |

| Differential Reference Clock Input DC Requirements           |

| (External DC-Coupled) 46                                     |

| Differential Reference Clock Input DC Requirements           |

| (External AC-Coupled) 46                                     |

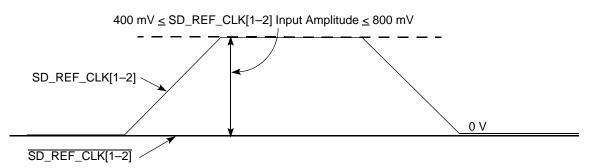

| Single-Ended Reference Clock Input DC Requirements 47        |

| DDR3 SDRAM Interface Input Timing Diagram 55                 |

| .MCK to MDQS Timing                                          |

|                                                              |

| Figure 11.DDR SDRAM Output Timing                                       |

|-------------------------------------------------------------------------|

| Figure 12.DDR3 Controller Bus AC Test Load                              |

| Figure 13.DDR3 SDRAM Differential Timing Specifications 57              |

| Figure 14.Differential Measurement Points for Rise and Fall Time 59     |

| Figure 15.Single-Ended Measurement Points for Rise and Fall Time        |

| Matching                                                                |

| Figure 16.Test Measurement Load61                                       |

| Figure 17. Single Frequency Sinusoidal Jitter Limits for Data Rates for |

| 3.125 Gbps and Below64                                                  |

| Figure 18. Single Frequency Sinusoidal Jitter Limits for Data Rate 5.0  |

| Gbps 64                                                                 |

| Figure 19.SGMII AC Test/Measurement Load                                |

| Figure 20. Single Frequency Sinusoidal Jitter Limits for Baud Rate      |

| <3.125 Gbps 67                                                          |

| Figure 21. Single Frequency Sinusoidal Jitter Limits for Baud Rate      |

| 3.125 Gbps 67                                                           |

| Figure 22.Timer AC Test Load 68                                         |

| Figure 23.MII Management Interface Timing                               |

| Figure 24.RGMII AC Timing and Multiplexing 69                           |

| Figure 25.SPI AC Test Load 70                                           |

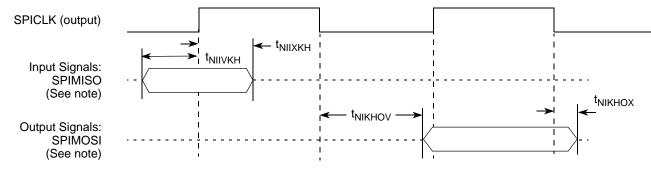

| Figure 26.SPI AC Timing in Slave Mode (External Clock) 70               |

| Figure 27.SPI AC Timing in Master Mode (Internal Clock) 71              |

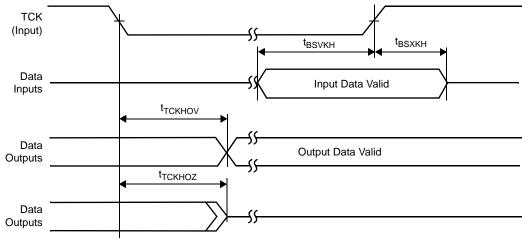

| Figure 28.Test Clock Input Timing                                       |

| Figure 29.Boundary Scan (JTAG) Timing 72                                |

| Figure 30.Test Access Port Timing73                                     |

| Figure 31.TRST Timing                                                   |

| Figure 32.MSC8157E Mechanical Information, 783-ball FC-PBGA             |

| Package                                                                 |

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>3</sup> | Power Rail<br>Name |

|-------------|----------------------------|-----------------------|--------------------|

| M5          | NC                         | Non-user              | N/A                |

| M6          | NC                         | Non-user              | N/A                |

| M7          | VSS                        | Ground                | N/A                |

| M8          | VDD                        | Power                 | N/A                |

| M9          | VSS                        | Ground                | N/A                |

| M10         | VDD                        | Power                 | N/A                |

| M11         | VSS                        | Ground                | N/A                |

| M12         | VDD                        | Power                 | N/A                |

| M13         | VSS                        | Ground                | N/A                |

| M14         | VDD                        | Power                 | N/A                |

| M15         | VSS                        | Ground                | N/A                |

| M16         | VDD                        | Power                 | N/A                |

| M17         | VSS                        | Ground                | N/A                |

| M18         | VDD                        | Power                 | N/A                |

| M19         | VSS                        | Ground                | N/A                |

| M20         | VDD                        | Power                 | N/A                |

| M21         | NC                         | NC                    | N/A                |

| M22         | NC                         | NC                    | N/A                |

| M23         | SD_A_TX                    | 0                     | SXPVDD             |

| M24         | SD_A_TX                    | 0                     | SXPVDD             |

| M25         | SXPVDD                     | Power                 | N/A                |

| M26         | SXPVSS                     | Ground                | N/A                |

| M27         | SD_A_RX                    | I                     | SXCVDD             |

| M28         | SD_A_RX                    | I                     | SXCVDD             |

| N1          | MRAS                       | 0                     | GVDD               |

| N2          | VSS                        | Ground                | N/A                |

| N3          | NC                         | Non-user              | N/A                |

| N4          | GVDD                       | Power                 | N/A                |

| N5          | VSS                        | Ground                | N/A                |

| N6          | MODT1                      | 0                     | GVDD               |

| N7          | CRPEVDD                    | Power                 | N/A                |

| N8          | VSS                        | Ground                | N/A                |

| N9          | CRPEVDD                    | Power                 | N/A                |

| N10         | VSS                        | Ground                | N/A                |

| N11         | CRPEVDD                    | Power                 | N/A                |

| N12         | VSS                        | Ground                | N/A                |

| N13         | VDD                        | Power                 | N/A                |

| N14         | VSS                        | Ground                | N/A                |

| N15         | VDD                        | Power                 | N/A                |

| N16         | VSS                        | Ground                | N/A                |

| N17         | VDD                        | Power                 | N/A                |

| N18         | VSS                        | Ground                | N/A                |

| N19         | VDD                        | Power                 | N/A                |

| N20         | VSS                        | Ground                | N/A                |

| N21         | NC                         | NC                    | N/A                |

| N22         | NC                         | NC                    | N/A                |

## Table 1. Signal List by Ball Number (continued)

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>3</sup> | Power Rail<br>Name |

|-------------|----------------------------|-----------------------|--------------------|

| AB1         | MDQS8                      | I/O                   | GVDD               |

| AB2         | MDM8                       | 0                     | GVDD               |

| AB3         | MECC2                      | I/O                   | GVDD               |

| AB4         | MECC1                      | I/O                   | GVDD               |

| AB5         | NC                         | Non-user              | N/A                |

| AB6         | MAPAR_IN                   | I                     | GVDD               |

| AB7         | MBA2                       | 0                     | GVDD               |

| AB8         | MDQ2                       | I/O                   | GVDD               |

| AB9         | MDQ1                       | I/O                   | GVDD               |

| AB10        | MDQ0                       | I/O                   | GVDD               |

| AB11        | VSS                        | Ground                | N/A                |

| AB12        | M3VDD                      | Power                 | N/A                |

| AB13        | VSS                        | Ground                | N/A                |

| AB14        | M3VDD                      | Power                 | N/A                |

| AB15        | VSS                        | Ground                | N/A                |

| AB16        | CPRIVDD                    | Power                 | N/A                |

| AB17        | VSS                        | Ground                | N/A                |

| AB18        | CPRIVDD                    | Power                 | N/A                |

| AB19        | NC                         | NC                    | N/A                |

| AB20        | NC                         | Non-user              | N/A                |

| AB21        | NC                         | NC                    | N/A                |

| AB22        | NC                         | NC                    | N/A                |

| AB23        | NC                         | NC                    | N/A                |

| AB24        | NC                         | NC                    | N/A                |

| AB25        | SXPVDD                     | Power                 | N/A                |

| AB26        | SXPVSS                     | Ground                | N/A                |

| AB27        | SD_E_RX                    | I                     | SXCVDD             |

| AB28        | SD_E_RX                    | I                     | SXCVDD             |

| AC1         | VSS                        | Ground                | N/A                |

| AC2         | GVDD                       | Power                 | N/A                |

| AC3         | MECC4                      | I/O                   | GVDD               |

| AC4         | VSS                        | Ground                | N/A                |

| AC5         | GVDD                       | Power                 | N/A                |

| AC6         | MDQ25                      | I/O                   | GVDD               |

| AC7         | VSS                        | Ground                | N/A                |

| AC8         | GVDD                       | Power                 | N/A                |

| AC9         | MDQ3                       | I/O                   | GVDD               |

| AC10        | VSS                        | Ground                | N/A                |

| AC11        | GVDD                       | Power                 | N/A                |

| AC12        | VSS                        | Ground                | N/A                |

| AC13        | M3VDD                      | Power                 | N/A                |

| AC14        | VSS                        | Ground                | N/A                |

| AC15        | CPRIVDD                    | Power                 | N/A                |

| AC16        | VSS                        | Ground                | N/A                |

| AC17        | NC                         | NC                    | N/A                |

| AC18        | NC                         | NC                    | N/A                |

## Table 1. Signal List by Ball Number (continued)

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>3</sup> | Power Rail<br>Name |

|-------------|----------------------------|-----------------------|--------------------|

| AC19        | NC                         | NC                    | N/A                |

| AC20        | NC                         | Non-user              | N/A                |

| AC21        | NC                         | NC                    | N/A                |

| AC22        | NC                         | NC                    | N/A                |

| AC23        | NC                         | NC                    | N/A                |

| AC24        | NC                         | NC                    | N/A                |

| AC25        | SD_F_TX                    | 0                     | SXPVDD             |

| AC26        | SD_F_TX                    | 0                     | SXPVDD             |

| AC27        | SXCVSS                     | Ground                | N/A                |

| AC28        | SXCVDD                     | Power                 | N/A                |

| AD1         | MECC7                      | I/O                   | GVDD               |

| AD2         | MECC6                      | I/O                   | GVDD               |

| AD3         | MECC0                      | I/O                   | GVDD               |

| AD4         | MECC5                      | I/O                   | GVDD               |

| AD5         | MECC3                      | I/O                   | GVDD               |

| AD6         | MDQ24                      | I/O                   | GVDD               |

| AD7         | MDM0                       | 0                     | GVDD               |

| AD8         | MDQS0                      | I/O                   | GVDD               |

| AD9         | MDQS0                      | I/O                   | GVDD               |

| AD10        | MDQ4                       | I/O                   | GVDD               |

| AD11        | MDQ6                       | I/O                   | GVDD               |

| AD12        | VSS                        | Non-user              | N/A                |

| AD13        | VSS                        | Non-user              | N/A                |

| AD14        | VSS                        | Non-user              | N/A                |

| AD15        | VSS                        | Ground                | N/A                |

| AD16        | VSS                        | Ground                | N/A                |

| AD17        | NC                         | NC                    | N/A                |

| AD18        | SD_PLL2_AVDD               | Power                 | N/A                |

| AD19        | NC                         | NC                    | N/A                |

| AD20        | NC                         | NC                    | N/A                |

| AD21        | NC                         | NC                    | N/A                |

| AD22        | NC                         | NC                    | N/A                |

| AD23        | NC                         | NC                    | N/A                |

| AD24        | NC                         | NC                    | N/A                |

| AD25        | SXPVDD                     | Power                 | N/A                |

| AD26        | SXPVSS                     | Ground                | N/A                |

| AD27        | SD_F_RX                    | 1                     | SXCVDD             |

| AD28        | SD_F_RX                    | 1                     | SXCVDD             |

| AE1         | MDQS2                      | I/O                   | GVDD               |

| AE2         | VSS                        | Ground                | N/A                |

| AE3         | MDQ18                      | I/O                   | GVDD               |

| AE4         | GVDD                       | Power                 | N/A                |

| AE5         | VSS                        | Ground                | N/A                |

| AE6         | MDQ29                      | I/O                   | GVDD               |

| AE7         | GVDD                       | Power                 | N/A                |

| AE8         | VSS                        | Ground                | N/A                |

## Table 1. Signal List by Ball Number (continued)

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>3</sup> | Power Rail<br>Name |

|-------------|----------------------------|-----------------------|--------------------|

| B24         | GPIO25/TMR2/RCW_SRC1       | I/O                   | NVDD               |

| F24         | GPIO26/TMR3                | I/O                   | NVDD               |

| E24         | GPIO27/TMR4/RCW_SRC0       | I/O                   | NVDD               |

| G19         | GPIO28/UART_RXD/CP_LOS1    | I/O                   | NVDD               |

| A20         | GPIO29/UART_TXD/CP_LOS2    | I/O                   | NVDD               |

| J28         | GPIO3/DRQ1/IRQ3/RC3        | I/O                   | NVDD               |

| C25         | GPIO30/I2C_SCL             | I/O                   | NVDD               |

| A21         | GPIO31/I2C_SDA             | I/O                   | NVDD               |

| K22         | GPIO4/DDN1/IRQ4/RC4        | I/O                   | NVDD               |

| D24         | GPIO5/IRQ5/RC5/CP_SYNC4    | I/O                   | NVDD               |

| F25         | GPIO6/IRQ6/RC6/CP_SYNC5    | I/O                   | NVDD               |

| K26         | GPIO7/IRQ7/RC7/CP_SYNC6    | I/O                   | NVDD               |

| F28         | GPIO8/IRQ8/RC8             | I/O                   | NVDD               |

| J23         | GPIO9/IRQ9/RC9             | I/O                   | NVDD               |

| A4          | GVDD                       | Power                 | N/A                |

| A7          | GVDD                       | Power                 | N/A                |

| AA4         | GVDD                       | Power                 | N/A                |

| AA9         | GVDD                       | Power                 | N/A                |

| AC11        | GVDD                       | Power                 | N/A                |

| AC2         | GVDD                       | Power                 | N/A                |

| AC5         | GVDD                       | Power                 | N/A                |

| AC8         | GVDD                       | Power                 | N/A                |

| AE10        | GVDD                       | Power                 | N/A                |

| AE4         | GVDD                       | Power                 | N/A                |

| AE7         | GVDD                       | Power                 | N/A                |

| AG11        | GVDD                       | Power                 | N/A                |

| AG2         | GVDD                       | Power                 | N/A                |

| AG5         | GVDD                       | Power                 | N/A                |

| AG8         | GVDD                       | Power                 | N/A                |

| C2          | GVDD                       | Power                 | N/A                |

| C5          | GVDD                       | Power                 | N/A                |

| E4          | GVDD                       | Power                 | N/A                |

| E7          | GVDD                       | Power                 | N/A                |

| G2          | GVDD                       | Power                 | N/A                |

| G5          | GVDD                       | Power                 | N/A                |

| J4          | GVDD                       | Power                 | N/A                |

| L2          | GVDD                       | Power                 | N/A                |

| L5          | GVDD                       | Power                 | N/A                |

| N4          | GVDD                       | Power                 | N/A                |

| R2          | GVDD                       | Power                 | N/A                |

| R5          | GVDD                       | Power                 | N/A                |

| R7          | GVDD                       | Power                 | N/A                |

| T8          | GVDD                       | Power                 | N/A<br>N/A         |

| U4          | GVDD                       | Power                 | N/A<br>N/A         |

| U4<br>U7    | GVDD                       | Power                 | N/A<br>N/A         |

| 07<br>V8    | GVDD                       | Power                 | N/A<br>N/A         |

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>3</sup> | Power Rail<br>Name |

|-------------|----------------------------|-----------------------|--------------------|

| M6          | NC                         | Non-user              | N/A                |

| N21         | NC                         | NC                    | N/A                |

| N22         | NC                         | NC                    | N/A                |

| N3          | NC                         | Non-user              | N/A                |

| P21         | NC                         | NC                    | N/A                |

| P23         | NC                         | NC                    | N/A                |

| P24         | NC                         | NC                    | N/A                |

| P3          | NC                         | Non-user              | N/A                |

| P5          | NC                         | Non-user              | N/A                |

| R21         | NC                         | NC                    | N/A                |

| R22         | NC                         | NC                    | N/A                |

| R23         | NC                         | NC                    | N/A                |

| R24         | NC                         | NC                    | N/A                |

| T21         | NC                         | NC                    | N/A                |

| T22         | NC                         | Non-user              | N/A                |

| T23         | NC                         | Non-user              | N/A                |

| T24         | NC                         | NC                    | N/A                |

| U21         | NC                         | NC                    | N/A                |

| U22         | NC                         | NC                    | N/A                |

| U23         | NC                         | NC                    | N/A                |

| U24         | NC                         | NC                    | N/A                |

| V21         | NC                         | NC                    | N/A                |

| V22         | NC                         | NC                    | N/A                |

| V23         | NC                         | NC                    | N/A                |

| V24         | NC                         | NC                    | N/A                |

| V25         | NC                         | NC                    | N/A                |

| V26         | NC                         | NC                    | N/A                |

| W21         | NC                         | NC                    | N/A                |

| W22         | NC                         | NC                    | N/A                |

| W23         | NC                         | NC                    | N/A                |

| W26         | NC                         | NC                    | N/A                |

| Y21         | NC                         | NC                    | N/A                |

| Y22         | NC                         | NC                    | N/A                |

| Y23         | NC                         | NC                    | N/A                |

| Y24         | NC                         | NC                    | N/A                |

| Y25         | NC                         | NC                    | N/A                |

| Y26         | NC                         | NC                    | N/A                |

| Y5          | NC                         | Non-user              | N/A                |

| D15         | NMI                        |                       | QVDD               |

| F15         | NMI_OUT/CP_RX_INT          | 0                     | QVDD               |

| D21         | NVDD                       | Power                 | N/A                |

| D25         | NVDD                       | Power                 | N/A                |

| E19         | NVDD                       | Power                 | N/A                |

| E23         | NVDD                       | Power                 | N/A                |

| G25         | NVDD                       | Power                 | N/A                |

| H20         | NVDD                       | Power                 | N/A                |

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>3</sup> | Power Rail<br>Name |

|-------------|----------------------------|-----------------------|--------------------|

| H23         | NVDD                       | Power                 | N/A                |

| H27         | NVDD                       | Power                 | N/A                |

| J21         | NVDD                       | Power                 | N/A                |

| K25         | NVDD                       | Power                 | N/A                |

| L21         | NVDD                       | Power                 | N/A                |

| AH14        | PLL0_AVDD                  | Power                 | N/A                |

| AH15        | PLL1_AVDD                  | Power                 | N/A                |

| AH16        | PLL2_AVDD                  | Power                 | N/A                |

| C17         | PORESET                    | 1                     | QVDD               |

| G15         | QVDD                       | Power                 | N/A                |

| H14         | QVDD                       | Power                 | N/A                |

| J27         | RC21                       | I                     | NVDD               |

| J24         | RCW_LSEL0/RC17             | I/O                   | NVDD               |

| K24         | RCW_LSEL1/RC18             | I/O                   | NVDD               |

| J26         | RCW_LSEL2/RC19             | I/O                   | NVDD               |

| J25         | RCW_LSEL3/RC20             | I/O                   | NVDD               |

| M27         | SD_A_RX                    | I                     | SXCVDD             |

| M28         | SD_A_RX                    | I                     | SXCVDD             |

| M23         | SD_A_TX                    | 0                     | SXPVDD             |

| M24         | SD_A_TX                    | 0                     | SXPVDD             |

| P27         | SD_B_RX                    | I                     | SXCVDD             |

| P28         | SD_B_RX                    | I                     | SXCVDD             |

| N25         | SD_B_TX                    | 0                     | SXPVDD             |

| N26         | SD_B_TX                    | 0                     | SXPVDD             |

| T27         | SD_C_RX                    | I                     | SXCVDD             |

| T28         | SD_C_RX                    | I                     | SXCVDD             |

| R25         | SD_C_TX                    | 0                     | SXPVDD             |

| R26         | SD_C_TX                    | 0                     | SXPVDD             |

| V27         | SD_D_RX                    | I                     | SXCVDD             |

| V28         | SD_D_RX                    | I                     | SXCVDD             |

| U25         | SD_D_TX                    | 0                     | SXPVDD             |

| U26         | SD_D_TX                    | 0                     | SXPVDD             |

| AB27        | SD_E_RX                    |                       | SXCVDD             |

| AB28        | SD_E_RX                    | I                     | SXCVDD             |

| AA25        | SD_E_TX                    | 0                     | SXPVDD             |

| AA26        | SD_E_TX                    | 0                     | SXPVDD             |

| AD27        | SD_F_RX                    | l                     | SXCVDD             |

| AD28        | SD_F_RX                    |                       | SXCVDD             |

| AC25        | SD_F_TX                    | 0                     | SXPVDD             |

| AC26        | SD_F_TX                    | 0                     | SXPVDD             |

| AF27        | SD_G_RX                    |                       | SXCVDD             |

| AF28        | SD_G_RX                    |                       | SXCVDD             |

| AE25        | SD_G_TX                    | 0                     | SXPVDD             |

| AE26        | SD_G_TX                    | 0                     | SXPVDD             |

| AH27        | SD_H_RX                    | I                     | SXCVDD             |

| AH28        | SD_H_RX                    | I                     | SXCVDD             |

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>3</sup> | Power Rail<br>Name |

|-------------|----------------------------|-----------------------|--------------------|

| W27         | SXCVSS                     | Ground                | N/A                |

| AB25        | SXPVDD                     | Power                 | N/A                |

| AD25        | SXPVDD                     | Power                 | N/A                |

| AE21        | SXPVDD                     | Power                 | N/A                |

| AE23        | SXPVDD                     | Power                 | N/A                |

| AF25        | SXPVDD                     | Power                 | N/A                |

| AH25        | SXPVDD                     | Power                 | N/A                |

| M25         | SXPVDD                     | Power                 | N/A                |

| N23         | SXPVDD                     | Power                 | N/A                |

| P25         | SXPVDD                     | Power                 | N/A                |

| T25         | SXPVDD                     | Power                 | N/A                |

| AB26        | SXPVSS                     | Ground                | N/A                |

| AD26        | SXPVSS                     | Ground                | N/A                |

| AF21        | SXPVSS                     | Ground                | N/A                |

| AF23        | SXPVSS                     | Ground                | N/A                |

| AF26        | SXPVSS                     | Ground                | N/A                |

| AH26        | SXPVSS                     | Ground                | N/A                |

| M26         | SXPVSS                     | Ground                | N/A                |

| N24         | SXPVSS                     | Ground                | N/A                |

| P26         | SXPVSS                     | Ground                | N/A                |

| T26         | SXPVSS                     | Ground                | N/A                |

| E17         | тск                        |                       | QVDD               |

| F17         | TDI                        |                       | QVDD               |

| B14         | TDO                        | 0                     | QVDD               |

| B15         | TMS                        |                       | QVDD               |

| G17         | TRST                       |                       | QVDD               |

| F10         | VDD                        | Power                 | N/A                |

| F8          | VDD                        | Power                 | N/A                |

| G7          | VDD                        | Power                 | N/A                |

| G9          | VDD                        | Power                 | N/A                |

| H10         | VDD                        | Power                 | N/A                |

| H16         | VDD                        | Power                 | N/A                |

| H18         | VDD                        | Power                 | N/A                |

| H8          | VDD                        | Power                 | N/A                |

| J11         | VDD                        | Power                 | N/A                |

| J13         | VDD                        | Power                 | N/A                |

| J15         | VDD                        | Power                 | N/A                |

| J17         | VDD                        | Power                 | N/A                |

| J19         | VDD                        | Power                 | N/A                |

| J7          | VDD                        | Power                 | N/A                |

| J9          | VDD                        | Power                 | N/A                |

| K10         | VDD                        | Power                 | N/A                |

| K12         | VDD                        | Power                 | N/A                |

| K14         | VDD                        | Power                 | N/A                |

| K16         | VDD                        | Power                 | N/A                |

| K18         | VDD                        | Power                 | N/A                |

|             |                            |                       |                    |

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>3</sup> | Power Rail<br>Name |

|-------------|----------------------------|-----------------------|--------------------|

| U8          | VSS                        | Ground                | N/A                |

| V11         | VSS                        | Ground                | N/A                |

| V13         | VSS                        | Ground                | N/A                |

| V15         | VSS                        | Ground                | N/A                |

| V17         | VSS                        | Ground                | N/A                |

| V19         | VSS                        | Ground                | N/A                |

| V2          | VSS                        | Ground                | N/A                |

| V7          | VSS                        | Ground                | N/A                |

| V9          | VSS                        | Ground                | N/A                |

| W1          | VSS                        | Ground                | N/A                |

| W10         | VSS                        | Ground                | N/A                |

| W12         | VSS                        | Ground                | N/A                |

| W14         | VSS                        | Ground                | N/A                |

| W16         | VSS                        | Ground                | N/A                |

| W18         | VSS                        | Ground                | N/A                |

| W2          | VSS                        | Ground                | N/A                |

| W20         | VSS                        | Ground                | N/A                |

| W4          | VSS                        | Ground                | N/A                |

| W8          | VSS                        | Ground                | N/A                |

| Y11         | VSS                        | Ground                | N/A                |

| Y13         | VSS                        | Ground                | N/A                |

| Y15         | VSS                        | Ground                | N/A                |

| Y17         | VSS                        | Ground                | N/A                |

| Y19         | VSS                        | Ground                | N/A                |

| Y7          | VSS                        | Ground                | N/A                |

| Y9          | VSS                        | Ground                | N/A                |

| D27         | VSS'                       | Ground                | N/A                |

2. NC signals should be disconnected for compatibility with future revisions of the device. Non-user signals are reserved for manufacturing and test purposes only. The assigned signal name is used to indicate whether the signal must be unconnected (Reserved), pulled down (VSS or SXCVSS), or pulled up (VDD).

Pin types are: Ground = all VSS connections; Power = all VDD connections; I = Input; O = Output; I/O = Input/Output; NC = not connected; non-user = connect as specified under Signal Name.

4. Connect power inputs to the power supplies via external filters. See the MSC8157 Design Checklist (AN4110) for details.

| Term                                 | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Differential Waveform                | The differential waveform is constructed by subtracting the inverting signal ( $\overline{SD}[A-J]TX$ , for example) from the non-inverting signal ( $\overline{SD}[A-J]TX$ , for example) within a differential pair. There is only one signal trace curve in a differential waveform. The voltage represented in the differential waveform is not referenced to ground. Refer to Figure 3 as an example for differential waveform.                                                                                                                                                                                                  |

| Common Mode Voltage, V <sub>cm</sub> | The common mode voltage is equal to half of the sum of the voltages between each conductor of a balanced interchange circuit and ground. In this example, for SerDes output,<br>$V_{cm_out} = (V_{SD_{A-J_TX} + V_{SD_{A-J_TX}}) \div 2 = (A + B) \div 2$ , which is the arithmetic mean of the two complimentary output voltages within a differential pair. In a system, the common mode voltage may often differ from one component's output to the other's input. It may be different between the receiver input and driver output circuits within the same component. It is also referred to as the DC offset on some occasions. |

To illustrate these definitions using real values, consider the example of a current mode logic (CML) transmitter that has a common mode voltage of 2.25 V and outputs, TD and TD. If these outputs have a swing from 2.0 V to 2.5 V, the peak-to-peak voltage swing of each signal (TD or TD) is 500 mV p-p, which is referred to as the single-ended swing for each signal. Because the differential signaling environment is fully symmetrical in this example, the transmitter output differential swing (V<sub>OD</sub>) has the same amplitude as each signal single-ended swing. The differential output signal ranges between 500 mV and -500 mV. In other words, V<sub>OD</sub> is 500 mV in one phase and -500 mV in the other phase. The peak differential voltage (V<sub>DIFFp</sub>) is 500 mV. The peak-to-peak differential voltage (V<sub>DIFFp</sub>) is 1000 mV p-p.

## 2.5.2.2 SerDes Reference Clock Receiver Characteristics

The SerDes reference clock inputs are applied to an internal PLL whose output creates the clock used by the corresponding SerDes lanes. The SerDes reference clock inputs are SD\_REF\_CLK1/SD\_REF\_CLK1 or SD\_REF\_CLK2/SD\_REF\_CLK2. Figure 4 shows a receiver reference diagram of the SerDes reference clocks.

Figure 4. Receiver of SerDes Reference Clocks

The characteristics of the clock signals are as follows:

- The supply voltage requirements for V<sub>DDSXC</sub> are as specified in Table 4.

- The SerDes reference clock receiver reference circuit structure is as follows:

- The SD\_REF\_CLK[1–2] and SD\_REF\_CLK[1–2] are internally AC-coupled differential inputs as shown in Figure 4. Each differential clock input (SD\_REF\_CLK[1–2] or SD\_REF\_CLK[1–2] has on-chip 50-Ω termination to SXCVSS followed by on-chip AC-coupling.

- The external reference clock driver must be able to drive this termination.

- The SerDes reference clock input can be either differential or single-ended. Refer to the differential mode and single-ended mode descriptions below for detailed requirements.

- The maximum average current requirement also determines the common mode voltage range.

To meet the input amplitude requirement, the reference clock inputs may need to be DC- or AC-coupled externally. For the best noise performance, the reference of the clock could be DC- or AC-coupled into the unused phase (SD\_REF\_CLK[1–2]) through the same source impedance as the clock input (SD\_REF\_CLK[1–2]) in use.

## 2.5.3.2 DC-Level Requirements for PCI Express Configurations

The DC-level requirements for PCI Express implementations have separate requirements for the Tx and Rx lines. The MSC8157E supports a 2.5 Gbps and a 5 Gbps PCI Express interface defined by the *PCI Express Base Specification, Revision 2.0.* The transmitter specifications for 2.5 Gbps are defined in Table 11 and the receiver specifications are defined in Table 12. For 5 Gbps, the transmitter specifications are defined in Table 13 and the receiver specifications are defined in Table 14.

Note: Specifications are valid at the recommended operating conditions listed in Table 4.

| Parameter                                            | Symbol                   | Min | Nom  | Max  | Units | Condition                                                                                                                                                                                                                                                            |

|------------------------------------------------------|--------------------------|-----|------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Differential peak-to-peak output voltage swing       | V <sub>TX-DIFFp-p</sub>  | 800 | 1000 | 1200 | mV    | $V_{TX-DIFFp-p} = 2 \times  V_{TX-D+} - V_{TX-D-} ,$<br>Measured at the package pins with a test load of 50 $\Omega$ to GND on each pin.                                                                                                                             |

| De-emphasized differential output<br>voltage (ratio) | V <sub>TX-DE-RATIO</sub> | 3.0 | 3.5  | 4.0  | dB    | Ratio of the V <sub>TX-DIFFp-p</sub> of the second<br>and following bits after a transition<br>divided by the V <sub>TX-DIFFp-p</sub> of the first bit<br>after a transition.<br>Measured at the package pins with a<br>test load of 50 $\Omega$ to GND on each pin. |

| DC differential Tx impedance                         | Z <sub>TX-DIFF-DC</sub>  | 80  | 100  | 120  | Ω     | Tx DC differential mode low Impedance                                                                                                                                                                                                                                |

| DC single-ended TX impedance                         | Z <sub>TX-DC</sub>       | 40  | 50   | 60   | Ω     | Required Tx D+ as well as D– DC<br>Impedance during all states                                                                                                                                                                                                       |

Table 11. PCI Express (2.5 Gbps) Differential Transmitter (Tx) Output DC Specifications

### Table 12. PCI Express (2.5 Gbps) Differential Receiver (Rx) Input DC Specifications

| Parameter                               | Symbol                           | Min | Nom  | Мах  | Units | Notes |

|-----------------------------------------|----------------------------------|-----|------|------|-------|-------|

| Differential input peak-to-peak voltage | V <sub>RX-DIFFp-p</sub>          | 120 | 1000 | 1200 | mV    | 1     |

| DC differential Input Impedance         | Z <sub>RX-DIFF-DC</sub>          | 80  | 100  | 120  | Ω     | 2     |

| DC input impedance                      | Z <sub>RX-DC</sub>               | 40  | 50   | 60   | Ω     | 3     |

| Powered down DC input impedance         | Z <sub>RX-HIGH-IMP-DC</sub>      | 50  | —    | —    | KΩ    | 4     |

| Electrical idle detect threshold        | V <sub>RX-IDLE-DET-DIFFp-p</sub> | 65  | —    | 175  | mV    | 5     |

### Table 14. PCI Express (5 Gbps) Differential Receiver (Rx) Input DC Specifications (continued)

|                                                 |                                                                                                       | Nom                                                                                                                                                                   | Max                                                                                                                                                                                                                                 | Units                                                                                                                                                                                                                                                                                     | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <sub>-D-</sub>   Measured at the pa             | ackage pins with                                                                                      | a test load of t                                                                                                                                                      | 50 Ω to GND o                                                                                                                                                                                                                       | n each pin.                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| nce. Impedance durin<br>SSM), there is a 5 ms t | g all LTSSM sta                                                                                       | tes. When trans                                                                                                                                                       | sitioning from a                                                                                                                                                                                                                    | fundamental r                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| uring all LTSSM states                          | . When transitior                                                                                     | ning from a fund                                                                                                                                                      | lamental reset                                                                                                                                                                                                                      | to detect (the i                                                                                                                                                                                                                                                                          | nitial state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| power is present or fur                         | ndamental reset                                                                                       | is asserted. Th                                                                                                                                                       | is helps ensure                                                                                                                                                                                                                     | e that the recei                                                                                                                                                                                                                                                                          | ver detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| )<br>F                                          | uring all LTSSM states<br>ransition time before th<br>DC Impedance when th<br>power is present or fur | uring all LTSSM states. When transitior<br>ransition time before the receiver termi<br>DC Impedance when the receiver termin<br>power is present or fundamental reset | uring all LTSSM states. When transitioning from a func-<br>ransition time before the receiver termination values m<br>IC Impedance when the receiver terminations do not h<br>power is present or fundamental reset is asserted. Th | uring all LTSSM states. When transitioning from a fundamental reset<br>ransition time before the receiver termination values must be met on<br>DC Impedance when the receiver terminations do not have power. The<br>power is present or fundamental reset is asserted. This helps ensure | IC Impedance (50 $\pm$ 20% tolerance). Measured at the package pins with a test load<br>uring all LTSSM states. When transitioning from a fundamental reset to detect (the in<br>ransition time before the receiver termination values must be met on all unconfigure<br>IC Impedance when the receiver terminations do not have power. The Rx DC com-<br>power is present or fundamental reset is asserted. This helps ensure that the receiver<br>a receiver is powered on when it is not. This term must be measured at 300 mV above |

5.  $V_{RX-IDLE-DET-DIFF_{p-p}} = 2 \times |V_{RX-D+} - V_{RX-D-}|$ . Measured at the package pins of the receiver

## 2.5.3.3 DC Level Requirements for Serial RapidIO Configurations

Note: Specifications are valid at the recommended operating conditions listed in Table 4.

### Table 15. Serial RapidIO Transmitter DC Specifications for Transfer Rates $\leq$ 3.125 Gbaud

| Parameter                                                                         | Symbol              | Min   | Nom | Max  | Units | Condition                       |

|-----------------------------------------------------------------------------------|---------------------|-------|-----|------|-------|---------------------------------|

| Output voltage                                                                    | V <sub>O</sub>      | -0.40 | —   | 2.30 | V     |                                 |

| Long run differential output voltage                                              | V <sub>DIFFPP</sub> | 800   | —   | 1600 | mVp-p | L[A–J]TECR0[AMP_RED] = 0b000000 |

| Short run differential output voltage                                             | V <sub>DIFFPP</sub> | 500   | —   | 1000 | mVp-p | L[A–J]TECR0[AMP_RED] = 0b001000 |

| DC differential TX impedance                                                      | ZTX-DIFF-DC         | 80    | 100 | 120  | Ω     |                                 |

| Note: Voltage relative to COMMON of either signal comprising a differential pair. |                     |       |     |      |       |                                 |

### Table 16. Serial RapidIO Receiver DC Specifications for Transfer Rates $\leq$ 3.125 Gbaud

| Parameter                                                                                                                                         | Symbol          | Min Nom |   | Мах  | Units |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------|---|------|-------|--|--|

| Differential input voltage                                                                                                                        | V <sub>IN</sub> | 200     | _ | 1600 | mVp-p |  |  |

| DC differential RX impedance ZRX-DIFF-DC 80 100 120                                                                                               |                 |         |   |      |       |  |  |

| Notes:       1. Voltage relative to COMMON of either signal comprising a differential pair.         2. Specifications are for Long and Short Run. |                 |         |   |      |       |  |  |

#### Table 17. Serial RapidIO Transmitter DC Specifications for Short Run at 5 Gbaud

| Parameter                                                              | Symbol  | Min | Nom | Max | Units | Condition                                            |

|------------------------------------------------------------------------|---------|-----|-----|-----|-------|------------------------------------------------------|

| Output differential voltage (into floating load Rload = $100 \Omega$ ) | T_Vdiff | 400 |     | 750 | mV    | Amplitude setting<br>L[A–J]TECR0[AMP_RED] = 0b001101 |

| Differential resistance                                                | T_Rd    | 80  | 100 | 120 | Ω     |                                                      |

### Table 18. Serial RapidIO Receiver DC Specifications for Short Run at 5 Gbaud

| Parameter                  | Symbol  | Min | Nom | Max  | Units |

|----------------------------|---------|-----|-----|------|-------|

| Input differential voltage | R_Vdiff | 125 |     | 1200 | mV    |

| Differential resistance    | R_Rdin  | 80  |     | 120  | Ω     |

### Table 19. Serial RapidIO Transmitter DC Specifications for Long Run at 5 Gbaud

| Parameter                                                              | Symbol  | Min | Nom | Max  | Units | Conditions                                                                          |

|------------------------------------------------------------------------|---------|-----|-----|------|-------|-------------------------------------------------------------------------------------|

| Output differential voltage (into floating load Rload = 100 $\Omega$ ) | T_Vdiff | 800 |     | 1200 | mV    | Amplitude setting<br>L[A–J]TECR0[AMP_RED] = 0b000000<br>(with de-emphasis disabled) |

rical Characteristics

| Parameter                                      | Symbol <sup>1</sup>   | Min                  | Max                  | Unit | Notes |

|------------------------------------------------|-----------------------|----------------------|----------------------|------|-------|

| MDQ/MECC/MDM output setup with respect to MDQS | t <sub>DDKHDS</sub> , |                      |                      |      | 5, 6  |

| 1333 MHz data rate                             | t <sub>DDKLDS</sub>   | 250                  | —                    | ps   |       |

| 1200 MHz data rate                             |                       | 275                  | —                    | ps   |       |

| 1066 MHz data rate                             |                       | 300                  | —                    | ps   |       |

| 800 MHz data rate                              |                       | 375                  | —                    | ps   |       |

| 667 MHz data rate                              |                       | 450                  | —                    | ps   |       |

| MDQ/MECC/MDM output hold with respect to MDQS  | t <sub>DDKHDX</sub>   |                      |                      |      | 5     |

| 1333 MHz data rate                             | t <sub>DDKLDX</sub>   | 250                  | —                    | ps   |       |

| 1200 MHz data rate                             |                       | 275                  | —                    | ps   |       |

| 1066 MHz data rate                             |                       | 300                  | —                    | ps   |       |

| 800 MHz data rate                              |                       | 375                  | —                    | ps   |       |

| 667 MHz data rate                              |                       | 450                  | —                    | ps   |       |

| MDQS preamble                                  | t <sub>DDKHMP</sub>   | $0.9 	imes t_{MCK}$  | —                    | ns   | —     |

| MDQS postamble                                 | t <sub>DDKHME</sub>   | $0.4 \times t_{MCK}$ | $0.6 \times t_{MCK}$ | ns   | _     |

#### Table 30. DDR SDRAM Output AC Timing Specifications (continued)

**1.** The symbols used for timing specifications follow the pattern of t<sub>(tirst two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state) for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.</sub></sub>

2. All MCK/MCK referenced measurements are made from the crossing of the two signals.

3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS.

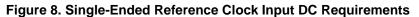

4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK(n) clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. This will typically be set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these two parameters have been set to the same adjustment value. See the MSC8157E Reference Manual for a description and understanding of the timing modifications enabled by use of these bits.

Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the MSC8157E.

At recommended operating conditions with V<sub>DDDDR</sub> (1.5 V) ± 5%.

**Note:** For the ADDR/CMD setup and hold specifications in Table 30, it is assumed that the clock control register is set to adjust the memory clocks by <sup>1</sup>/<sub>2</sub> applied cycle.

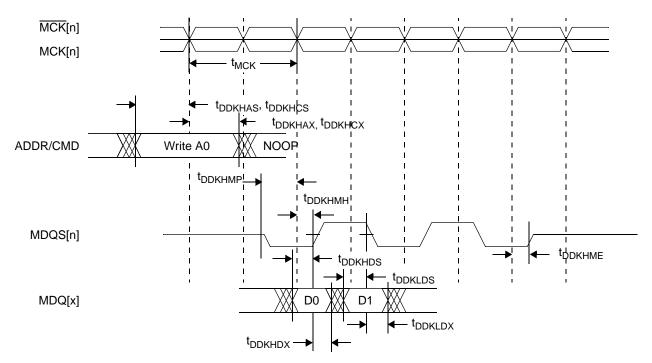

Figure 10 shows the DDR SDRAM output timing for the MCK to MDQS skew measurement (t<sub>DDKHMH</sub>).

Figure 10. MCK to MDQS Timing

Figure 11 shows the DDR SDRAM output timing diagram.

Figure 11. DDR SDRAM Output Timing

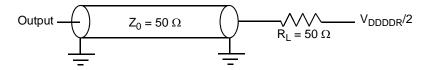

Figure 12 provides the AC test load for the DDR3 controller bus.

Figure 12. DDR3 Controller Bus AC Test Load

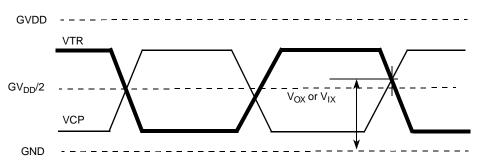

## 2.6.1.3 DDR3 SDRAM Differential Timing Specifications

This section describes the DC and AC differential timing specifications for the DDR3 SDRAM controller interface. Figure 13 shows the differential timing specification.

Figure 13. DDR3 SDRAM Differential Timing Specifications

Note: VTR specifies the true input signal (such as MCK or MDQS) and VCP is the complementary input signal (such as  $\overline{MCK}$  or  $\overline{MDQS}$ ).

Table 31 provides the DDR3 differential specifications for the differential signals MDQS/MDQS and MCK/MCK.

#### Table 35. PCI Express 2.0 (5.0 Gbps) Differential Transmitter (Tx) Output AC Specifications

| Parameter                                | Symbol                   | Min    | Nom    | Max    | Units | Comments                                                                                                                                          |

|------------------------------------------|--------------------------|--------|--------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Unit Interval                            | UI                       | 199.94 | 200.00 | 200.06 | ps    | Each UI is 400 ps ± 300 ppm. UI does not<br>account for spread spectrum clock dictated<br>variations. See note 1.                                 |

| Minimum Tx eye width                     | T <sub>TX-EYE</sub>      | 0.75   | _      | —      | UI    | The maximum Transmitter jitter can be derived<br>as: $T_{TX-MAX-JITTER} = 1 - T_{TX-EYE} = 0.25$ UI.<br>See notes 2 and 3.                        |

| Tx RMS deterministic jitter > 1.5 MHz    | T <sub>TX-HF-DJ-DD</sub> | _      | —      | 0.15   | ps    | _                                                                                                                                                 |

| Tx RMS deterministic<br>jitter < 1.5 MHz | T <sub>TX-LF-RMS</sub>   | _      | 3.0    | —      | ps    | Reference input clock RMS jitter (< 1.5 MHz) at pin < 1 ps                                                                                        |

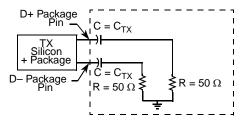

| AC coupling capacitor                    | C <sub>TX</sub>          | 75     | _      | 200    | nF    | All transmitters must be AC coupled. The AC coupling is required either within the media or within the transmitting component itself. See note 4. |

2. Specified at the measurement point into a timing and voltage test load as shown in Figure 16 and measured over any 250 consecutive Tx UIs.

3. A T<sub>TX-EYE</sub> = 0.75 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-MAX-JITTER</sub> = 0.25 UI for the Transmitter collected over any 250 consecutive Tx UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> median is less than half of the total Tx jitter budget collected over any 250 consecutive Tx UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value.

4. The DSP device SerDes transmitter does not have a built-in C<sub>TX</sub>. An external AC coupling capacitor is required.

### Table 36. PCI Express 2.0 (5.0 Gbps) Differential Receiver (Rx) Input AC Specifications

| Parameter                                                                    | Symbol                   | Min          | Nom    | Max    | Units | Conditions                                                                                                       |

|------------------------------------------------------------------------------|--------------------------|--------------|--------|--------|-------|------------------------------------------------------------------------------------------------------------------|

| Unit Interval                                                                | UI                       | 199.40       | 200.00 | 200.06 | ps    | Each UI is 400 ps ±300 ppm. UI does not account<br>for spread spectrum clock dictated variations. See<br>Note 1. |

| Max Rx inherent timing error                                                 | T <sub>RX-TJ-CC</sub>    | —            | —      | 0.4    | UI    | The maximum inherent total timing error for<br>common REF_CLK Rx architecture                                    |

| Maximum time between the jitter median and maximum deviation from the median | T <sub>RX-TJ-DC</sub>    | —            | —      | 0.34   | UI    | Max Rx inherent total timing error                                                                               |

| Max Rx inherent deterministic timing error                                   | T <sub>RX-DJ-DD-CC</sub> | —            | _      | 0.30   | UI    | The maximum inherent deterministic timing error<br>for common REF_CLK Rx architecture                            |

| Max Rx inherent deterministic timing error                                   | T <sub>RX-DJ-DD-DC</sub> | —            | _      | 0.24   | UI    | The maximum inherent deterministic timing error<br>for common REF_CLK Rx architecture                            |

| Note: No test load is nece                                                   | ssarily accosted wit     | h this value | e.     | •      | •     | ·                                                                                                                |

The AC timing and voltage parameters must be verified at the measurement point. The package pins of the device must be connected to the test/measurement load within 0.2 inches of that load, as shown in Figure 16.

**Note:** The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary. If the vendor does not explicitly state where the measurement point is located, the measurement point is assumed to be the D+ and D- package pins.

Figure 16. Test Measurement Load

rical Characteristics

## 2.6.2.4 Serial RapidIO AC Timing Specifications

Note: Specifications are valid at the recommended operating conditions listed in Table 4.

Table 37 defines the transmitter AC specifications for the Serial RapidIO interface at frequencies up to 3.125 Gbaud. The AC timing specifications do not include REF\_CLK jitter.

### Table 37. Serial RapidIO Transmitter AC Timing Specifications Up to 3.125 Gbaud

| Characteristic             | Symbol         | Min          | Nom | Мах          | Unit   |

|----------------------------|----------------|--------------|-----|--------------|--------|

| Deterministic Jitter       | J <sub>D</sub> | —            | _   | 0.17         | UI p-p |

| Total Jitter               | J <sub>T</sub> | —            | _   | 0.35         | UI p-p |

| Unit Interval: 1.25 GBaud  | UI             | 800 – 100ppm | 800 | 800 + 100ppm | ps     |

| Unit Interval: 2.5 GBaud   | UI             | 400 – 100ppm | 400 | 400 + 100ppm | ps     |

| Unit Interval: 3.125 GBaud | UI             | 320 – 100ppm | 320 | 320 + 100ppm | ps     |

Table 38 defines the Receiver AC specifications for the Serial RapidIO interface at frequencies up to 3.125 Gbaud. The AC timing specifications do not include REF\_CLK jitter.

### Table 38. Serial RapidIO Receiver AC Timing Specifications Up to 3.125 Gbaud

| Characteristic                                                                                                                                                      | Symbol          | Min                | Nom           | Max                 | Unit         | Notes           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|---------------|---------------------|--------------|-----------------|

| Deterministic Jitter Tolerance                                                                                                                                      | J <sub>D</sub>  | —                  | _             | 0.37                | UI p-p       | 1               |

| Combined Deterministic and Random Jitter<br>Tolerance                                                                                                               | $J_DR$          | —                  | _             | 0.55                | UI p-p       | 1               |