Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | HC08                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | SCI, SPI                                                  |

| Peripherals                | LVD, POR, PWM                                             |

| Number of I/O              | 13                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 128 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 10x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | 16-SOIC                                                   |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908qb4mdwe |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC68HC908QB8 MC68HC908QB4 MC68HC908QY8

Data Sheet

M68HC08 Microcontrollers

MC68HC908QB8 Rev. 3 04/2010

freescale.com

# NP,

**General Description**

| Pin<br>Name | Description                     | Input/Output |

|-------------|---------------------------------|--------------|

|             | PTB4 — General-purpose I/O port | Input/Output |

| PTB4        | RxD — ESCI receive data I/O     | Input/Output |

|             | AD8 — A/D channel 8 input       | Input        |

|             | PTB5 — General-purpose I/O port | Input/Output |

| PTB5        | TxD — ESCI transmit data I/O    | Output       |

|             | AD9 — A/D channel 9 input       | Input        |

| DTDO        | PTB6 — General-purpose I/O port | Input/Output |

| PTB6        | TCH2 — Timer channel 2 I/O      | Input/Output |

| DTDZ        | PTB7 — General-purpose I/O port | Input/Output |

| PTB7        | TCH3 — Timer channel 3 I/O      | Input/Output |

## Table 1-2. Pin Functions (Continued)

## **1.6 Pin Function Priority**

Table 1-3 is meant to resolve the priority if multiple functions are enabled on a single pin.

## NOTE

Upon reset all pins come up as input ports regardless of the priority table.

|                     | •                                                                                               |

|---------------------|-------------------------------------------------------------------------------------------------|

| Pin Name            | Highest-to-Lowest Priority Sequence                                                             |

| PTA0 <sup>(1)</sup> | $AD0 \rightarrow TCH0 \rightarrow KBI0 \rightarrow PTA0$                                        |

| PTA1 <sup>(1)</sup> | $AD1 \rightarrow TCH1 \rightarrow KBI1 \rightarrow PTA1$                                        |

| PTA2                | $\overline{\text{IRQ}} \rightarrow \text{TCLK} \rightarrow \text{KBI2} \rightarrow \text{PTA2}$ |

| PTA3                | $\overline{\text{RST}} \rightarrow \text{KBI3} \rightarrow \text{PTA3}$                         |

| PTA4 <sup>(1)</sup> | $OSC2 \rightarrow AD2 \rightarrow KBI4 \rightarrow PTA4$                                        |

| PTA5 <sup>(1)</sup> | $OSC1 \rightarrow AD3 \rightarrow KBI5 \rightarrow PTA5$                                        |

| PTB0 <sup>(1)</sup> | $AD4 \rightarrow SPSCK \rightarrow PTB0$                                                        |

| PTB1 <sup>(1)</sup> | $AD5 \rightarrow MOSI \rightarrow PTB1$                                                         |

| PTB2 <sup>(1)</sup> | $AD6 \rightarrow MISO \rightarrow PTB2$                                                         |

| PTB3 <sup>(1)</sup> | $AD7 \rightarrow \overline{SS} \rightarrow PTB3$                                                |

| PTB4 <sup>(1)</sup> | $AD8 \rightarrow RxD \rightarrow PTB4$                                                          |

| PTB5 <sup>(1)</sup> | $AD9 \rightarrow TxD \rightarrow PTB5$                                                          |

| PTB6                | $TCH2 \rightarrow PTB6$                                                                         |

| PTB7                | $TCH3 \rightarrow PTB7$                                                                         |

Table 1-3. Function Priority in Shared Pins

1. When a pin is to be used as an ADC pin, the I/O port function should be left as an input and all other shared modules should be disabled. The ADC does not override additional modules using the pin.

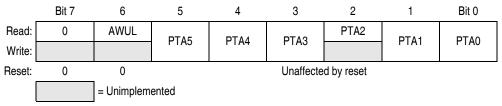

## Chapter 2 Memory

## 2.1 Introduction

The central processor unit (CPU08) can address 64 Kbytes of memory space. The memory map, shown in Figure 2-1.

## 2.2 Unimplemented Memory Locations

Executing code from an unimplemented location will cause an illegal address reset. In Figure 2-1, unimplemented locations are shaded.

## 2.3 Reserved Memory Locations

Accessing a reserved location can have unpredictable effects on MCU operation. In Figure 2-1, register locations are marked with the word Reserved or with the letter R.

## 2.4 Direct Page Registers

Figure 2-2 shows the memory mapped registers of the MC68HC908QB8. Registers with addresses between \$0000 and \$00FF are considered direct page registers and all instructions including those with direct page addressing modes can access them. Registers between \$0100 and \$FFFF require non-direct page addressing modes. See Chapter 7 Central Processor Unit (CPU) for more information on addressing modes.

#### Memory

| \$0000<br>↓<br>\$003F | IDIRECT PAGE REGISTERS<br>64 BYTES  |                            |                       |

|-----------------------|-------------------------------------|----------------------------|-----------------------|

| \$0040<br>↓<br>\$013F | RAM<br>256 BYTES                    | <br>RESERVED<br>64 BYTES   | \$0040<br>↓<br>\$007F |

| \$0140<br>↓<br>\$27FF | UNIMPLEMENTED<br>9920 BYTES         | RAM<br>128 BYTES           | \$0080<br>↓<br>\$00FF |

| \$2800<br>↓<br>\$2A1F | AUXILIARY ROM<br>544 BYTES          | RESERVED<br>64 BYTES       | \$0100<br>↓<br>\$013F |

| \$2A20<br>↓<br>\$2F7D | UNIMPLEMENTED<br>1374 BYTES         |                            |                       |

| \$2F7E<br>↓<br>\$2FFF | AUXILIARY ROM<br>130 BYTES          |                            |                       |

| \$3000<br>↓<br>\$DDFF | UNIMPLEMENTED<br>44,544 BYTES       |                            |                       |

| \$DE00<br>↓<br>\$FDFF | FLASH MEMORY<br>8192 BYTES          | RESERVED<br>4096 BYTES     | \$DE00<br>↓<br>\$EDFF |

| \$FE00<br>↓<br>\$FE1F | MISCELLANEOUS REGISTERS<br>32 BYTES | FLASH MEMORY<br>4096 BYTES | \$EE00<br>↓<br>\$FDFF |

| \$FE20<br>↓<br>\$FF7D | MONITOR ROM<br>350 BYTES            |                            |                       |

| \$FF7E<br>↓<br>\$FFAF | UNIMPLEMENTED<br>50BYTES            |                            |                       |

| \$FFB0<br>↓<br>\$FFBD | FLASH<br>14 BYTES                   |                            |                       |

| \$FFBE<br>↓<br>\$FFC1 | MISCELLANEOUS REGISTERS<br>4 BYTES  |                            |                       |

| \$FFC2<br>↓<br>\$FFCF | FLASH<br>14 BYTES                   |                            |                       |

| \$FFD0<br>↓<br>\$FFFF | USER VECTORS<br>48 BYTES            |                            |                       |

|                       |                                     |                            |                       |

MC68HC908QB8 and MC68HC908QY8 Memory Map MC68HC908QB4 Memory Map

## 4.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

## 4.5.1 Wait Mode

The AWU module remains inactive in wait mode.

## 4.5.2 Stop Mode

When the AWU module is enabled (AWUIE = 1 in the keyboard interrupt enable register) it is activated automatically upon entering stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode. The AWU counters start from 0 each time stop mode is entered.

## 4.6 Registers

The AWU shares registers with the keyboard interrupt (KBI) module, the port A I/O module and configuration register 2. The following I/O registers control and monitor operation of the AWU:

- Port A data register (PTA)

- Keyboard interrupt status and control register (KBSCR)

- Keyboard interrupt enable register (KBIER)

- Configuration register 1 (CONFIG1)

- Configuration register 2 (CONFIG2)

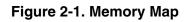

## 4.6.1 Port A I/O Register

The port A data register (PTA) contains a data latch for the state of the AWU interrupt request, in addition to the data latches for port A.

Figure 4-2. Port A Data Register (PTA)

## AWUL — Auto Wakeup Latch

This is a read-only bit which has the value of the auto wakeup interrupt request latch. The wakeup request signal is generated internally. There is no PTA6 port or any of the associated bits such as PTA6 data direction or pullup bits.

- 1 = Auto wakeup interrupt request is pending

- 0 = Auto wakeup interrupt request is not pending

## NOTE

PTA5–PTA0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 12.2.1 Port A Data Register.

#### **Configuration Register (CONFIG)**

### IRQPUD — IRQ Pin Pullup Control Bit

1 = Internal pullup is disconnected

0 = Internal pullup is connected between  $\overline{IRQ}$  pin and  $V_{DD}$

### IRQEN — IRQ Pin Function Selection Bit

- 1 = Interrupt request function active in pin

- 0 = Interrupt request function inactive in pin

### ESCIBDSRC — ESCI Baud Rate Clock Source Bit

ESCIBDSRC controls the clock source used for the ESCI. The setting of the bit affects the frequency at which the ESCI operates.

1 = Internal data bus clock used as clock source for ESCI

0 = BUSCLKX4 used as clock source for ESCI

## **OSCENINSTOP**— Oscillator Enable in Stop Mode Bit

OSCENINSTOP, when set, will allow the clock source to continue to generate clocks in stop mode. This function can be used to keep the auto-wakeup running while the rest of the microcontroller stops. When clear, the clock source is disabled when the microcontroller enters stop mode.

1 = Oscillator enabled to operate during stop mode

0 = Oscillator disabled during stop mode

#### RSTEN — RST Pin Function Selection

- 1 = Reset function active in pin

- 0 =Reset function inactive in pin

#### NOTE

The RSTEN bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

| _               | Bit 7 | 6       | 5       | 4       | 3       | 2     | 1    | Bit 0 |  |

|-----------------|-------|---------|---------|---------|---------|-------|------|-------|--|

| Read:<br>Write: | COPRS | LVISTOP | LVIRSTD | LVIPWRD | LVITRIP | SSREC | STOP | COPD  |  |

| Reset:          | 0     | 0       | 0       | 0       | U       | 0     | 0    | 0     |  |

| POR:            | 0     | 0       | 0       | 0       | 0       | 0     | 0    | 0     |  |

|                 |       |         |         |         |         |       |      |       |  |

U = Unaffected

#### Figure 5-2. Configuration Register 1 (CONFIG1)

#### COPRS (Out of Stop Mode) — COP Reset Period Selection Bit

1 = COP reset short cycle =  $8176 \times BUSCLKX4$

0 = COP reset long cycle = 262,128 × BUSCLKX4

# COPRS (In Stop Mode) — Auto Wakeup Period Selection Bit, depends on OSCSTOPEN in CONFIG2 and external clock source

1 = Auto wakeup short cycle =  $512 \times (INTRCOSC \text{ or } BUSCLKX4)$

0 = Auto wakeup long cycle =  $16,384 \times (INTRCOSC \text{ or BUSCLKX4})$

#### LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

1 = LVI enabled during stop mode

0 = LVI disabled during stop mode

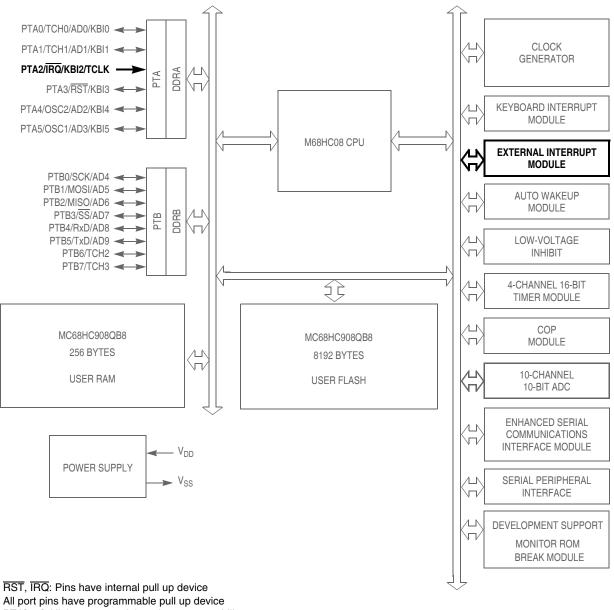

#### External Interrupt (IRQ)

PTA[0:5]: Higher current sink and source capability

## Figure 8-1. Block Diagram Highlighting IRQ Block and Pin

When set, the IMASK bit in INTSCR masks the IRQ interrupt request. A latched interrupt request is not presented to the interrupt priority logic unless IMASK is clear.

#### NOTE

The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including the IRQ interrupt request.

A falling edge on the IRQ pin can latch an interrupt request into the IRQ latch. An IRQ vector fetch, software clear, or reset clears the IRQ latch.

## Chapter 9 Keyboard Interrupt Module (KBI)

## 9.1 Introduction

The keyboard interrupt module (KBI) provides independently maskable external interrupts.

The KBI shares its pins with general-purpose input/output (I/O) port pins. See Figure 9-1 for port location of these shared pins.

## 9.2 Features

Features of the keyboard interrupt module include:

- Keyboard interrupt pins with separate keyboard interrupt enable bits and one keyboard interrupt mask

- Programmable edge-only or edge and level interrupt sensitivity

- Edge sensitivity programmable for rising or falling edge

- Level sensitivity programmable for high or low level

- Pullup or pulldown device automatically enabled based on the polarity of edge or level detect

- Exit from low-power modes

## 9.3 Functional Description

The keyboard interrupt module controls the enabling/disabling of interrupt functions on the KBI pins. These pins can be enabled/disabled independently of each other. See Figure 9-2.

## 9.3.1 Keyboard Operation

Writing to the KBIEx bits in the keyboard interrupt enable register (KBIER) independently enables or disables each KBI pin. The polarity of the keyboard interrupt is controlled using the KBIPx bits in the keyboard interrupt polarity register (KBIPR). Edge-only or edge and level sensitivity is controlled using the MODEK bit in the keyboard status and control register (KBISCR).

Enabling a keyboard interrupt pin also enables its internal pullup or pulldown device based on the polarity enabled. On falling edge or low level detection, a pullup device is configured. On rising edge or high level detection, a pulldown device is configured.

The keyboard interrupt latch is set when one or more enabled keyboard interrupt inputs are asserted.

- If the keyboard interrupt sensitivity is edge-only, for KBIPx = 0, a falling (for KBIPx = 1, a rising) edge on a keyboard interrupt input does not latch an interrupt request if another enabled keyboard pin is already asserted. To prevent losing an interrupt request on one input because another input remains asserted, software can disable the latter input while it is asserted.

- If the keyboard interrupt is edge and level sensitive, an interrupt request is present as long as any enabled keyboard interrupt input is asserted.

#### **Oscillator Module (OSC)**

Figure 11-3 shows how BUSCLKX4 is derived from INTCLK and OSC2 can output BUSCLKX4 by setting OSC2EN.

## 11.3.2.1 Internal Oscillator Trimming

OSCTRIM allows a clock period adjustment of +127 and -128 steps. Increasing the OSCTRIM value increases the clock period, which decreases the clock frequency. Trimming allows the internal clock frequency to be fine tuned to the target frequency.

All devices are factory programmed with a trim value that is stored in FLASH memory at location \$FFC0. The trim value is not automatically loaded into the OSCTRIM register. User software must copy the trim value from \$FFC0 into OSCTRIM if needed. The factory trim value provides the accuracy required for communication using forced monitor mode. Some production programmers erase the factory trim value, so confirm with your programmer vendor that the trim value at \$FFC0 is preserved, or is re-trimmed. Trimming the device in the user application board will provide the most accurate trim value.

## 11.3.2.2 Internal to External Clock Switching

When external clock source (external OSC, RC, or XTAL) is desired, the user must perform the following steps:

- 1. For external crystal circuits only, configure OSCOPT[1:0] to external crystal. To help precharge an external crystal oscillator, momentarily configure OSC2 as an output and drive it high for several cycles. This can help the crystal circuit start more robustly.

- Configure OSCOPT[1:0] and ECFS[1:0] according to 11.8.1 Oscillator Status and Control Register. The oscillator module control logic will then enable OSC1 as an external clock input and, if the external crystal option is selected, OSC2 will also be enabled as the clock output. If RC oscillator option is selected, enabling the OSC2 output may change the bus frequency.

- 3. Create a software delay to provide the stabilization time required for the selected clock source (crystal, resonator, RC). A good rule of thumb for crystal oscillators is to wait 4096 cycles of the crystal frequency; i.e., for a 4-MHz crystal, wait approximately 1 ms.

- 4. After the stabilization delay has elapsed, set ECGON.

After ECGON set is detected, the OSC module checks for oscillator activity by waiting two external clock rising edges. The OSC module then switches to the external clock. Logic provides a coherent transition. The OSC module first sets ECGST and then stops the internal oscillator.

## 11.3.2.3 External to Internal Clock Switching

After following the procedures to switch to an external clock source, it is possible to go back to the internal source. By clearing the OSCOPT[1:0] bits and clearing the ECGON bit, the external circuit will be disengaged. The bus clock will be derived from the selected internal clock source based on the ICFS[1:0] bits.

## 11.3.3 External Oscillator

The external oscillator option is designed for use when a clock signal is available in the application to provide a clock source to the MCU. The OSC1 pin is enabled as an input by the oscillator module. The clock signal is used directly to create BUSCLKX4 and also divided by two to create BUSCLKX2.

In this configuration, the OSC2 pin cannot output BUSCLKX4. The OSC2EN bit will be forced clear to enable alternative functions on the pin.

## 11.6 OSC During Break Interrupts

There are no status flags associated with the OSC module.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

## 11.7 I/O Signals

The OSC shares its pins with general-purpose input/output (I/O) port pins. See Figure 11-1 for port location of these shared pins.

## 11.7.1 Oscillator Input Pin (OSC1)

The OSC1 pin is an input to the crystal oscillator amplifier, an input to the RC oscillator circuit, or an input from an external clock source.

When the OSC is configured for internal oscillator, the OSC1 pin can be used as a general-purpose input/output (I/O) port pin or other alternative pin function.

## 11.7.2 Oscillator Output Pin (OSC2)

For the XTAL oscillator option, the OSC2 pin is the output of the crystal oscillator amplifier.

When the OSC is configured for internal oscillator, external clock, or RC, the OSC2 pin can be used as a general-purpose I/O port pin or other alternative pin function. When the oscillator is configured for internal or RC, the OSC2 pin can be used to output BUSCLKX4.

| Option                                     | OSC2 Pin Function                                                                                                      |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| XTAL oscillator                            | Inverting OSC1                                                                                                         |

| External clock                             | General-purpose I/O or alternative pin function                                                                        |

| Internal oscillator<br>or<br>RC oscillator | Controlled by OSC2EN bit<br>OSC2EN = 0: General-purpose I/O or alternative pin function<br>OSC2EN = 1: BUSCLKX4 output |

Table 11-1. OSC2 Pin Function

Oscillator Module (OSC)

## 11.8 Registers

The oscillator module contains two registers:

- Oscillator status and control register (OSCSC)

- Oscillator trim register (OSCTRIM)

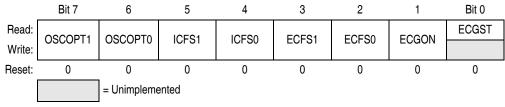

## 11.8.1 Oscillator Status and Control Register

The oscillator status and control register (OSCSC) contains the bits for switching between internal and external clock sources. If the application uses an external crystal, bits in this register are used to select the crystal oscillator amplifier necessary for the desired crystal. While running off the internal clock source, the user can use bits in this register to select the internal clock source frequency.

## OSCOPT1:OSCOPT0 — OSC Option Bits

These read/write bits allow the user to change the clock source for the MCU. The default reset condition has the bus clock being derived from the internal oscillator. See 11.3.2.2 Internal to External Clock Switching for information on changing clock sources.

| OSCOPT1 | OSCOPT0 | Oscillator Modes                                          |

|---------|---------|-----------------------------------------------------------|

| 0       | 0       | Internal oscillator (frequency selected using ICFSx bits) |

| 0       | 1       | External oscillator clock                                 |

| 1       | 0       | External RC                                               |

| 1       | 1       | External crystal (range selected using ECFSx bits)        |

## ICFS1:ICFS0 — Internal Clock Frequency Select Bits

These read/write bits enable the frequency to be increased for applications requiring a faster bus clock when running off the internal oscillator. The WAIT instruction has no effect on the oscillator logic. BUSCLKX2 and BUSCLKX4 continue to drive to the SIM module.

| ICFS1 | ICFS0 | Internal Clock Frequency          |

|-------|-------|-----------------------------------|

| 0     | 0     | 4.0 MHz — default reset condition |

| 0     | 1     | 8.0 MHz                           |

| 1     | 0     | 12.8 MHz                          |

| 1     | 1     | Reserved                          |

Oscillator Module (OSC)

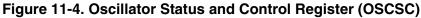

## 12.3.2 Data Direction Register B

Data direction register B (DDRB) determines whether each port B pin is an input or an output. Writing a 1 to a DDRB bit enables the output buffer for the corresponding port B pin; a 0 disables the output buffer.

Figure 12-6. Data Direction Register B (DDRB)

#### DDRB[7:0] — Data Direction Register B Bits

These read/write bits control port B data direction. Reset clears DDRB[7:0], configuring all port B pins as inputs.

1 = Corresponding port B pin configured as output

0 = Corresponding port B pin configured as input

NOTE

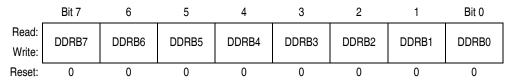

Avoid glitches on port B pins by writing to the port B data register before changing data direction register B bits from 0 to 1. Figure 12-7 shows the port B I/O logic.

Figure 12-7. Port B I/O Circuit

When DDRBx is a 1, reading PTB reads the PTBx data latch. When DDRBx is a 0, reading PTB reads the logic level on the PTBx pin. The data latch can always be written, regardless of the state of its data direction bit.

#### Enhanced Serial Communications Interface (ESCI) Module

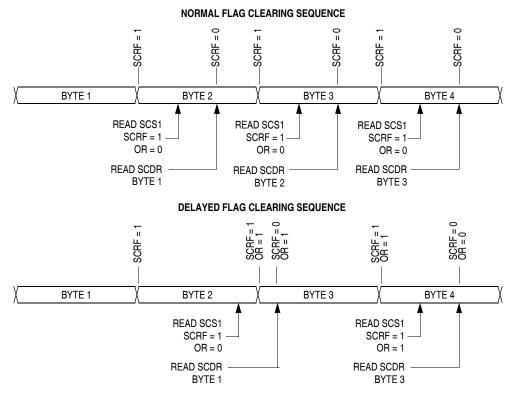

Figure 13-13. Flag Clearing Sequence

## FE — Receiver Framing Error Bit

This clearable, read-only bit is set when a 0 is accepted as the stop bit. FE generates an ESCI error interrupt request if the FEIE bit in SCC3 also is set. Clear the FE bit by reading SCS1 with FE set and then reading the SCDR.

1 = Framing error detected

0 = No framing error detected

## PE — Receiver Parity Error Bit

This clearable, read-only bit is set when the ESCI detects a parity error in incoming data. PE generates a PE interrupt request if the PEIE bit in SCC3 is also set. Clear the PE bit by reading SCS1 with PE set and then reading the SCDR.

1 = Parity error detected

0 = No parity error detected

## 13.8.5 ESCI Status Register 2

ESCI status register 2 (SCS2) contains flags to signal these conditions:

- Break character detected

- Reception in progress

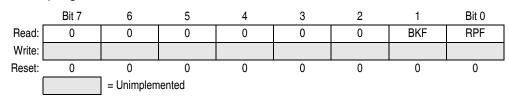

Figure 13-14. ESCI Status Register 2 (SCS2)

## **BKF** — Break Flag Bit

This clearable, read-only bit is set when the ESCI detects a break character on the RxD pin. In SCS1, the FE and SCRF bits are also set. In 9-bit character transmissions, the R8 bit in SCC3 is cleared. BKF does not generate a interrupt request. Clear BKF by reading SCS2 with BKF set and then reading the SCDR. Once cleared, BKF can become set again only after 1s again appear on the RxD pin followed by another break character.

1 = Break character detected

0 = No break character detected

#### **RPF** — Reception in Progress Flag Bit

This read-only bit is set when the receiver detects a 0 during the RT1 time period of the start bit search. RPF does not generate an interrupt request. RPF is reset after the receiver detects false start bits (usually from noise or a baud rate mismatch), or when the receiver detects an idle character. Polling RPF before disabling the ESCI module or entering stop mode can show whether a reception is in progress.

1 = Reception in progress

0 = No reception in progress

## 13.8.6 ESCI Data Register

The ESCI data register (SCDR) is the buffer between the internal data bus and the receive and transmit shift registers. Reset has no effect on data in the ESCI data register.

|        | Bit 7               | 6  | 5  | 4  | 3  | 2  | 1  | Bit 0 |

|--------|---------------------|----|----|----|----|----|----|-------|

| Read:  | R7                  | R6 | R5 | R4 | R3 | R2 | R1 | R0    |

| Write: | T7                  | T6 | T5 | T4 | T3 | T2 | T1 | T0    |

| Reset: | Unaffected by reset |    |    |    |    |    |    |       |

#### Figure 13-15. ESCI Data Register (SCDR)

#### R7/T7:R0/T0 — Receive/Transmit Data Bits

Reading SCDR accesses the read-only received data bits, R7:R0. Writing to SCDR writes the data to be transmitted, T7:T0.

NOTE

Do not use read-modify-write instructions on the ESCI data register.

#### Serial Peripheral Interface (SPI) Module

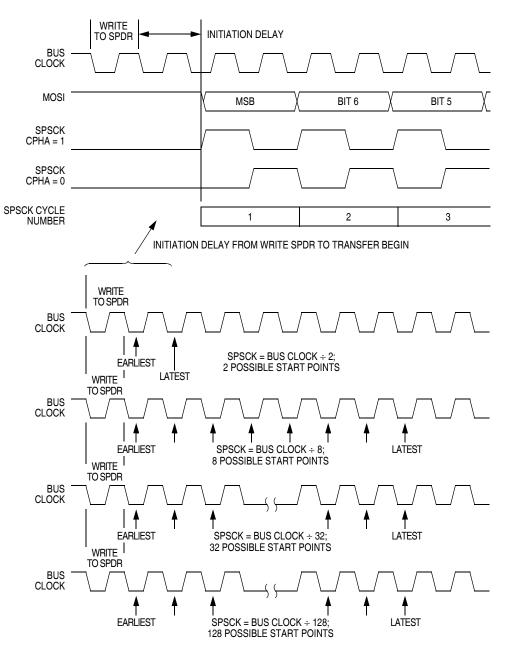

Figure 15-7. Transmission Start Delay (Master)

Interrupts

In a slave SPI (MSTR = 0), MODF generates an SPI receiver/error interrupt request if the ERRIE bit is set. The MODF bit does not clear the SPE bit or reset the SPI in any way. Software can abort the SPI transmission by clearing the SPE bit of the slave.

NOTE

A high on the SS pin of a slave SPI puts the MISO pin in a high impedance state. Also, the slave SPI ignores all incoming SPSCK clocks, even if it was already in the middle of a transmission.

To clear the MODF flag, read the SPSCR with the MODF bit set and then write to the SPCR register. This entire clearing mechanism must occur with no MODF condition existing or else the flag is not cleared.

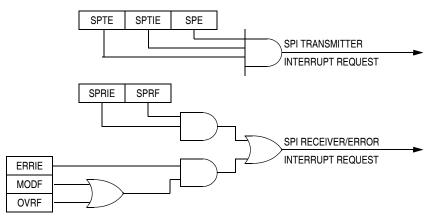

## 15.4 Interrupts

Four SPI status flags can be enabled to generate interrupt requests. See Table 15-1.

| Flag              | Request                              |

|-------------------|--------------------------------------|

| SPTE              | SPI transmitter interrupt request    |

| Transmitter empty | (SPTIE = 1, SPE = 1)                 |

| SPRF              | SPI receiver interrupt request       |

| Receiver full     | (SPRIE = 1)                          |

| OVRF              | SPI receiver/error interrupt request |

| Overflow          | (ERRIE = 1)                          |

| MODF              | SPI receiver/error interrupt request |

| Mode fault        | (ERRIE = 1)                          |

Table 15-1. SPI Interrupts

Reading the SPI status and control register with SPRF set and then reading the receive data register clears SPRF. The clearing mechanism for the SPTE flag is requires only a write to the transmit data register.

The SPI transmitter interrupt enable bit (SPTIE) enables the SPTE flag to generate transmitter interrupt requests, provided that the SPI is enabled (SPE = 1).

The SPI receiver interrupt enable bit (SPRIE) enables SPRF to generate receiver interrupt requests, regardless of the state of SPE. See Figure 15-11.

Figure 15-11. SPI Interrupt Request Generation

Timer Interface Module (TIM)

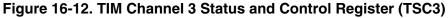

## 16.8.4 TIM Channel Status and Control Registers

Each of the TIM channel status and control registers does the following:

- · Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

## CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the counter registers matches the value in the TIM channel x registers.

Clear CHxF by reading the TSCx register with CHxF set and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

## Chapter 18 Electrical Specifications

## **18.1 Introduction**

This section contains electrical and timing specifications.

## **18.2 Absolute Maximum Ratings**

Maximum ratings are the extreme limits to which the microcontroller unit (MCU) can be exposed without permanently damaging it.

NOTE

This device is not guaranteed to operate properly at the maximum ratings. Refer to 18.5 5-V DC Electrical Characteristics and 18.8 3-V DC Electrical Characteristics for guaranteed operating conditions.

| Characteristic <sup>(1)</sup>                                                         | Symbol                               | Value                          | Unit |

|---------------------------------------------------------------------------------------|--------------------------------------|--------------------------------|------|

| Supply voltage                                                                        | V <sub>DD</sub>                      | -0.3 to +6.0                   | V    |

| Input voltage                                                                         | V <sub>IN</sub>                      | $V_{SS}$ –0.3 to $V_{DD}$ +0.3 | V    |

| Mode entry voltage, IRQ pin                                                           | V <sub>TST</sub>                     | V <sub>SS</sub> –0.3 to +9.1   | V    |

| Maximum current per pin excluding<br>PTA0–PTA5, V <sub>DD</sub> , and V <sub>SS</sub> | I                                    | ±15                            | mA   |

| Maximum current for pins PTA0–PTA5                                                    | I <sub>PTA0</sub> _I <sub>PTA5</sub> | ±25                            | mA   |

| Storage temperature                                                                   | T <sub>STG</sub>                     | -55 to +150                    | °C   |

| Maximum current out of V <sub>SS</sub>                                                | I <sub>MVSS</sub>                    | 100                            | mA   |

| Maximum current into V <sub>DD</sub>                                                  | I <sub>MVDD</sub>                    | 100                            | mA   |

1. Voltages references to V<sub>SS</sub>.

## NOTE

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. For proper operation, it is recommended that  $V_{IN}$  and  $V_{OUT}$  be constrained to the range  $V_{SS} \leq (V_{IN} \text{ or } V_{OUT}) \leq V_{DD}$ . Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (for example, either  $V_{SS}$  or  $V_{DD}$ .)