Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | HC08                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | SCI, SPI                                                  |

| Peripherals                | LVD, POR, PWM                                             |

| Number of I/O              | 13                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 10x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                           |

| Supplier Device Package    | 16-TSSOP                                                  |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908qb8mdte |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

\_\_\_\_\_

| 16.8.2 | TIM Counter Registers                    | 185 |

|--------|------------------------------------------|-----|

|        | TIM Counter Modulo Registers             |     |

| 16.8.4 | TIM Channel Status and Control Registers | 186 |

| 16.8.5 | TIM Channel Registers                    | 188 |

# Chapter 17 Development Support

| 17.1     | Introduction                              | 191 |

|----------|-------------------------------------------|-----|

| 17.2     | Break Module (BRK)                        | 191 |

| 17.2.1   | Functional Description                    | 191 |

| 17.2.1.1 | 1 Flag Protection During Break Interrupts | 193 |

| 17.2.1.2 | 2 TIM During Break Interrupts             | 193 |

| 17.2.1.3 | 3 COP During Break Interrupts             | 193 |

| 17.2.2   | Break Module Registers                    | 194 |

| 17.2.2.1 | 1 Break Status and Control Register       | 194 |

| 17.2.2.2 | 2 Break Address Registers                 | 194 |

| 17.2.2.3 | 3 Break Auxiliary Register                | 195 |

| 17.2.2.4 | 4 Break Status Register                   | 195 |

| 17.2.2.5 | 5 Break Flag Control Register             | 195 |

| 17.2.3   | Low-Power Modes                           | 196 |

| 17.3     | Monitor Module (MON)                      | 196 |

| 17.3.1   | Functional Description                    | 196 |

| 17.3.1.1 | 1 Normal Monitor Mode                     | 200 |

| 17.3.1.2 | 2 Forced Monitor Mode                     | 201 |

| 17.3.1.3 | 3 Monitor Vectors                         | 201 |

| 17.3.1.4 | 4 Data Format                             | 202 |

| 17.3.1.5 | 5 Break Signal                            | 202 |

| 17.3.1.6 | 6 Baud Rate                               | 202 |

| 17.3.1.7 |                                           |     |

| 17.3.2   | Security                                  | 206 |

|          |                                           |     |

# Chapter 18 Electrical Specifications

| 18.1  | Introduction                             | 207 |

|-------|------------------------------------------|-----|

| 18.2  | Absolute Maximum Ratings                 | 207 |

| 18.3  | Functional Operating Range               | 208 |

| 18.4  | Thermal Characteristics                  | 208 |

| 18.5  | 5-V DC Electrical Characteristics        | 209 |

| 18.6  | Typical 5-V Output Drive Characteristics | 210 |

| 18.7  | 5-V Control Timing                       | 211 |

| 18.8  | 3-V DC Electrical Characteristics        | 212 |

| 18.9  | Typical 3-V Output Drive Characteristics | 213 |

| 18.10 | 3-V Control Timing                       | 214 |

| 18.11 | Oscillator Characteristics               | 215 |

| 18.12 | Supply Current Characteristics           | 217 |

#### Memory

| Addr.  | Register Name                                        |                  | Bit 7       | 6                               | 5              | 4         | 3          | 2         | 1                | Bit 0            |

|--------|------------------------------------------------------|------------------|-------------|---------------------------------|----------------|-----------|------------|-----------|------------------|------------------|

|        | ESCI Status Register 2                               | Read:            | 0           | 0                               | 0              | 0         | 0          | 0         | BKF              | RPF              |

| \$0014 | (SCS2)                                               | Write:           |             |                                 |                |           |            |           |                  |                  |

|        | See page 129.                                        | Reset:           | 0           | 0                               | 0              | 0         | 0          | 0         | 0                | 0                |

|        | ESCI Data Register                                   | Read:            | R7          | R6                              | R5             | R4        | R3         | R2        | R1               | R0               |

| \$0015 | (SCDR)                                               | Write:           | T7          | T6                              | T5             | T4        | Т3         | T2        | T1               | Т0               |

|        | See page 129.                                        | Reset:           |             |                                 |                | Unaffecte | d by reset |           |                  |                  |

| \$0016 | ESCI Baud Rate Register<br>(SCBR)                    | Read:<br>Write:  | LINT        | LINR                            | SCP1           | SCP0      | R          | SCR2      | SCR1             | SCR0             |

|        | See page 130.                                        | Reset:           | 0           | 0                               | 0              | 0         | 0          | 0         | 0                | 0                |

| \$0017 | ESCI Prescaler Register<br>(SCPSC)                   | Read:<br>Write:  | PDS2        | PDS1                            | PDS0           | PSSB4     | PSSB3      | PSSB2     | PSSB1            | PSSB0            |

|        | See page 131.                                        | Reset:           | 0           | 0                               | 0              | 0         | 0          | 0         | 0                | 0                |

|        | ESCI Arbiter Control                                 | Read:            | AM1         | ALOST                           | AM0            | ACLK      | AFIN       | ARUN      | AROVFL           | ARD8             |

| \$0018 | Register (SCIACTL)                                   | Write:           | AIVIT       |                                 | AIVIO          | AULK      |            |           |                  |                  |

|        | See page 135.                                        | Reset:           | 0           | 0                               | 0              | 0         | 0          | 0         | 0                | 0                |

|        | ESCI Arbiter Data Register                           | Read:            | ARD7        | ARD6                            | ARD5           | ARD4      | ARD3       | ARD2      | ARD1             | ARD0             |

| \$0019 | (SCIADAT)                                            | Write:           |             |                                 |                |           |            |           |                  |                  |

|        | See page 136.                                        | Reset:           | 0           | 0                               | 0              | 0         | 0          | 0         | 0                | 0                |

|        | Keyboard Status and                                  | Read:            | 0           | 0                               | 0              | 0         | KEYF       | 0         | IMASKK           | MODEK            |

| \$001A | Control Register (KBSCR)                             | Write:           |             |                                 |                |           |            | ACKK      |                  |                  |

|        | See page 87.                                         | Reset:           | 0           | 0                               | 0              | 0         | 0          | 0         | 0                | 0                |

|        | Keyboard Interrupt                                   | Read:            | 0           | AWUIE                           | KBIE5          | KBIE4     | KBIE3      | KBIE2     | KBIE1            | KBIE0            |

| \$001B | Enable Register (KBIER)                              | Write:           |             |                                 |                |           |            |           |                  |                  |

|        | See page 88.                                         | Reset:           | 0           | 0                               | 0              | 0         | 0          | 0         | 0                | 0                |

| ¢0010  | Keyboard Interrupt Polarity                          | Read:            | 0           | 0                               | KBIP5          | KBIP4     | KBIP3      | KBIP2     | KBIP1            | KBIP0            |

| \$001C | Register (KBIPR)<br>See page 88.                     | Write:<br>Reset: | 0           | 0                               | 0              | 0         | 0          | 0         | 0                | 0                |

|        | IRQ Status and Control                               | Read:            | 0           | 0                               | 0              | 0         | IRQF       | 0         | 0                | 0                |

| \$001D | Register (INTSCR)                                    | Write:           | 0           | 0                               | 0              | 0         | INQL       | ACK       | IMASK            | MODE             |

| ψυυτD  | See page 81.                                         | Reset:           | 0           | 0                               | 0              | 0         | 0          | 0         | 0                | 0                |

| \$001E | Configuration Register 2<br>(CONFIG2) <sup>(1)</sup> | Read:<br>Write:  | IRQPUD      | IRQEN                           | R              | R         | R          | ESCIBDSRC | OSCENIN-<br>STOP | RSTEN            |

| 400 IL | See page 57.                                         | Reset:           | 0           | 0                               | 0              | 0         | 0          | 0         | 0                | 0 <sup>(2)</sup> |

|        |                                                      |                  | 1. One-time | writable regis<br>set to 0 by a | ter after each | reset.    |            | č         | 5                | -                |

|        |                                                      |                  |             | set to o by a                   | power-on res   |           |            |           |                  |                  |

|        |                                                                                                                              | _               |          |         |         |           |                  |        |       |       |

|--------|------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|---------|---------|-----------|------------------|--------|-------|-------|

| \$001F | Configuration Register 1<br>(CONFIG1) <sup>(1)</sup>                                                                         | Read:<br>Write: | COPRS    | LVISTOP | LVIRSTD | LVIPWRD   | LVITRIP          | SSREC  | STOP  | COPD  |

|        | See page 58.                                                                                                                 | Reset:          | 0        | 0       | 0       | 0         | 0 <sup>(2)</sup> | 0      | 0     | 0     |

|        | <ol> <li>One-time writable register after each reset.</li> <li>LVITRIP reset to 0 by a power-on reset (POR) only.</li> </ol> |                 |          |         |         |           |                  |        |       |       |

| \$0020 | TIM Status and Control<br>Register (TSC)                                                                                     | Read:<br>Write: | TOF<br>0 | TOIE    | TSTOP   | 0<br>TRST | 0                | PS2    | PS1   | PS0   |

|        | See page 183.                                                                                                                | Reset:          | 0        | 0       | 1       | 0         | 0                | 0      | 0     | 0     |

|        | TIM Counter Register High                                                                                                    | Read:           | Bit 15   | Bit 14  | Bit 13  | Bit 12    | Bit 11           | Bit 10 | Bit 9 | Bit 8 |

\$0021 (TCNTH) See page 185.

Write:

Reset:

0

0

0

R

0

= Reserved

0

U = Unaffected

0

= Unimplemented

MC68HC908QB8 Data Sheet, Rev. 3

0

0

#### Analog-to-Digital Converter (ADC10) Module

charging. If externally available, connect the  $V_{\text{REFL}}$  pin to the same potential as  $V_{\text{SSA}}$  at the single point ground location.

# 3.7.5 ADC10 Channel Pins (ADn)

The ADC10 has multiple input channels. Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. 0.01  $\mu$ F capacitors with good high-frequency characteristics are sufficient. These capacitors are not necessary in all cases, but when used they must be placed as close as possible to the package pins and be referenced to V<sub>SSA</sub>.

# 3.8 Registers

These registers control and monitor operation of the ADC10:

- ADC10 status and control register, ADSCR

- ADC10 data registers, ADRH and ADRL

- ADC10 clock register, ADCLK

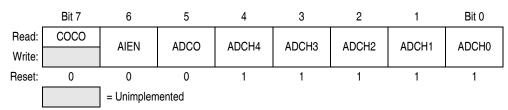

# 3.8.1 ADC10 Status and Control Register

This section describes the function of the ADC10 status and control register (ADSCR). Writing ADSCR aborts the current conversion and initiates a new conversion (if the ADCH[4:0] bits are equal to a value other than all 1s).

### Figure 3-3. ADC10 Status and Control Register (ADSCR)

### COCO — Conversion Complete Bit

COCO is a read-only bit which is set each time a conversion is completed. This bit is cleared whenever the status and control register is written or whenever the data register (low) is read.

1 = Conversion completed

0 = Conversion not completed

### AIEN — ADC10 Interrupt Enable Bit

When this bit is set, an interrupt is generated at the end of a conversion. The interrupt signal is cleared when the data register is read or the status/control register is written.

1 = ADC10 interrupt enabled

0 = ADC10 interrupt disabled

### ADCO — ADC10 Continuous Conversion Bit

When this bit is set, the ADC10 will begin to convert samples continuously (continuous conversion mode) and update the result registers at the end of each conversion, provided the ADCH[4:0] bits do not decode to all 1s. The ADC10 will continue to convert until the MCU enters reset, the MCU enters stop mode (if ACLKEN is clear), ADCLK is written, or until ADSCR is written again. If stop is entered

Analog-to-Digital Converter (ADC10) Module

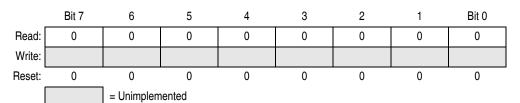

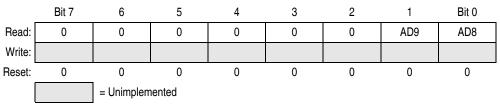

# 3.8.2 ADC10 Result High Register (ADRH)

This register holds the MSBs of the result and is updated each time a conversion completes. All other bits read as 0s. Reading ADRH prevents the ADC10 from transferring subsequent conversion results into the result registers until ADRL is read. If ADRL is not read until the after next conversion is completed, then the intermediate conversion result will be lost. In 8-bit mode, this register contains no interlocking with ADRL.

Figure 3-5. ADC10 Data Register High (ADRH), 10-Bit Mode

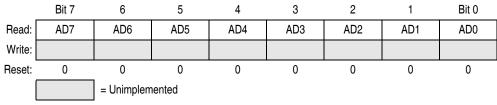

# 3.8.3 ADC10 Result Low Register (ADRL)

This register holds the LSBs of the result. This register is updated each time a conversion completes. Reading ADRH prevents the ADC10 from transferring subsequent conversion results into the result registers until ADRL is read. If ADRL is not read until the after next conversion is completed, then the intermediate conversion result will be lost. In 8-bit mode, there is no interlocking with ADRH.

Figure 3-6. ADC10 Data Register Low (ADRL)

# 4.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

### 4.5.1 Wait Mode

The AWU module remains inactive in wait mode.

## 4.5.2 Stop Mode

When the AWU module is enabled (AWUIE = 1 in the keyboard interrupt enable register) it is activated automatically upon entering stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode. The AWU counters start from 0 each time stop mode is entered.

# 4.6 Registers

The AWU shares registers with the keyboard interrupt (KBI) module, the port A I/O module and configuration register 2. The following I/O registers control and monitor operation of the AWU:

- Port A data register (PTA)

- Keyboard interrupt status and control register (KBSCR)

- Keyboard interrupt enable register (KBIER)

- Configuration register 1 (CONFIG1)

- Configuration register 2 (CONFIG2)

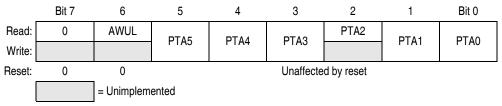

## 4.6.1 Port A I/O Register

The port A data register (PTA) contains a data latch for the state of the AWU interrupt request, in addition to the data latches for port A.

Figure 4-2. Port A Data Register (PTA)

### AWUL — Auto Wakeup Latch

This is a read-only bit which has the value of the auto wakeup interrupt request latch. The wakeup request signal is generated internally. There is no PTA6 port or any of the associated bits such as PTA6 data direction or pullup bits.

- 1 = Auto wakeup interrupt request is pending

- 0 = Auto wakeup interrupt request is not pending

### NOTE

PTA5–PTA0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 12.2.1 Port A Data Register.

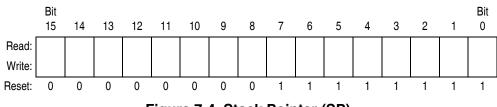

### 7.3.3 Stack Pointer

The stack pointer is a 16-bit register that contains the address of the next location on the stack. During a reset, the stack pointer is preset to \$00FF. The reset stack pointer (RSP) instruction sets the least significant byte to \$FF and does not affect the most significant byte. The stack pointer decrements as data is pushed onto the stack and increments as data is pulled from the stack.

In the stack pointer 8-bit offset and 16-bit offset addressing modes, the stack pointer can function as an index register to access data on the stack. The CPU uses the contents of the stack pointer to determine the conditional address of the operand.

Figure 7-4. Stack Pointer (SP)

#### NOTE

The location of the stack is arbitrary and may be relocated anywhere in random-access memory (RAM). Moving the SP out of page 0 (\$0000 to \$00FF) frees direct address (page 0) space. For correct operation, the stack pointer must point only to RAM locations.

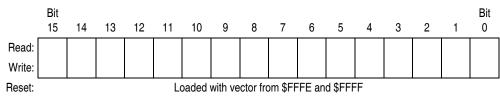

## 7.3.4 Program Counter

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

Normally, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, and interrupt operations load the program counter with an address other than that of the next sequential location.

During reset, the program counter is loaded with the reset vector address located at \$FFFE and \$FFFF. The vector address is the address of the first instruction to be executed after exiting the reset state.

Figure 7-5. Program Counter (PC)

**Central Processor Unit (CPU)**

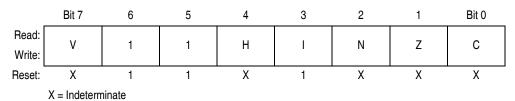

# 7.3.5 Condition Code Register

The 8-bit condition code register contains the interrupt mask and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code register.

Figure 7-6. Condition Code Register (CCR)

### V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

- 1 = Overflow

- 0 = No overflow

### H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

1 = Carry between bits 3 and 4

0 = No carry between bits 3 and 4

### I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

- 1 = Interrupts disabled

- 0 = Interrupts enabled

### NOTE

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

After the I bit is cleared, the highest-priority interrupt request is serviced first. A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack and restores the interrupt mask from the stack. After any reset, the interrupt mask is set and can be cleared only by the clear interrupt mask software instruction (CLI).

### N — Negative Flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

1 = Negative result

0 = Non-negative result

**Functional Description**

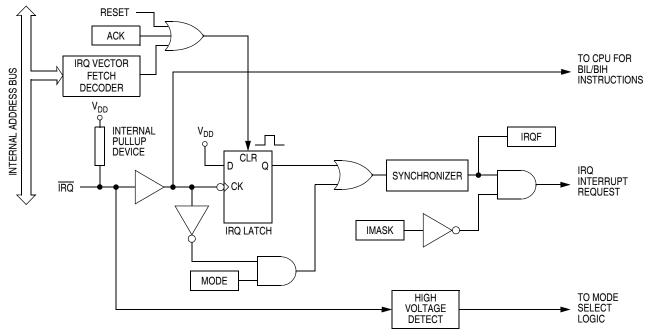

Figure 8-2. IRQ Module Block Diagram

## 8.3.1 MODE = 1

If the MODE bit is set, the IRQ pin is both falling edge sensitive and low level sensitive. With MODE set, both of the following actions must occur to clear the IRQ interrupt request:

- Return of the IRQ pin to a high level. As long as the IRQ pin is low, the IRQ request remains active.

- IRQ vector fetch or software clear. An IRQ vector fetch generates an interrupt acknowledge signal to clear the IRQ latch. Software generates the interrupt acknowledge signal by writing a 1 to ACK in INTSCR. The ACK bit is useful in applications that poll the IRQ pin and require software to clear the IRQ latch. Writing to ACK prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACK does not affect subsequent transitions on the IRQ pin. A falling edge that occurs after writing to ACK latches another interrupt request. If the IRQ mask bit, IMASK, is clear, the CPU loads the program counter with the IRQ vector address.

The IRQ vector fetch or software clear and the return of the IRQ pin to a high level may occur in any order. The interrupt request remains pending as long as the IRQ pin is low. A reset will clear the IRQ latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

Use the BIH or BIL instruction to read the logic level on the IRQ pin.

### 8.3.2 MODE = 0

If the MODE bit is clear, the IRQ pin is falling edge sensitive only. With MODE clear, an IRQ vector fetch or software clear immediately clears the IRQ latch.

The IRQF bit in INTSCR can be read to check for pending interrupts. The IRQF bit is not affected by IMASK, which makes it useful in applications where polling is preferred.

### NOTE

When using the level-sensitive interrupt trigger, avoid false IRQ interrupts by masking interrupt requests in the interrupt routine.

# Keyboard Interrupt Module (KBI)

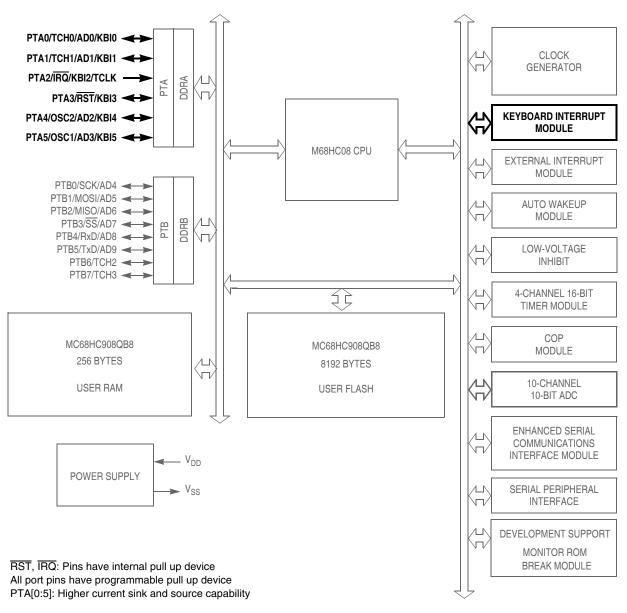

### Figure 9-1. Block Diagram Highlighting KBI Block and Pins

### 9.3.1.1 MODEK = 1

If the MODEK bit is set, the keyboard interrupt inputs are both edge and level sensitive. The KBIPx bit will determine whether a edge sensitive pin detects rising or falling edges and on level sensitive pins whether the pin detects low or high levels. With MODEK set, both of the following actions must occur to clear a keyboard interrupt request:

• Return of all enabled keyboard interrupt inputs to a deasserted level. As long as any enabled keyboard interrupt pin is asserted, the keyboard interrupt remains active.

# Chapter 11 Oscillator Module (OSC)

# 11.1 Introduction

The oscillator (OSC) module is used to provide a stable clock source for the MCU system and bus.

The OSC shares its pins with general-purpose input/output (I/O) port pins. See Figure 11-1 for port location of these shared pins. The OSC2EN bit is located in the port A pull enable register (PTAPUEN) on this MCU. See Chapter 12 Input/Output Ports (PORTS) for information on PTAPUEN register.

# 11.2 Features

The bus clock frequency is one fourth of any of these clock source options:

- 1. Internal oscillator: An internally generated, fixed frequency clock, trimmable to  $\pm$  0.4%. There are three choices for the internal oscillator,12.8 MHz, 8 MHz, or 4 MHz. The 4-MHz internal oscillator is the default option out of reset.

- 2. External oscillator: An external clock that can be driven directly into OSC1.

- 3. External RC: A built-in oscillator module (RC oscillator) that requires an external R connection only. The capacitor is internal to the chip.

- 4. External crystal: A built-in XTAL oscillator that requires an external crystal or ceramic-resonator. There are three crystal frequency ranges supported, 8–32 MHz, 1–8 MHz, and 32–100 kHz.

# **11.3 Functional Description**

The oscillator contains these major subsystems:

- Internal oscillator circuit

- Internal or external clock switch control

- External clock circuit

- External crystal circuit

- External RC clock circuit

#### ECFS1:ECFS0 — External Crystal Frequency Select Bits

These read/write bits enable the specific amplifier for the crystal frequency range. Refer to oscillator characteristics table in the Electricals section for information on maximum external clock frequency versus supply voltage.

| ECFS1 | ECFS0 | External Crystal Frequency |

|-------|-------|----------------------------|

| 0     | 0     | 8 MHz – 32 MHz             |

| 0     | 1     | 1 MHz – 8 MHz              |

| 1     | 0     | 32 kHz – 100 kHz           |

| 1     | 1     | Reserved                   |

#### ECGON — External Clock Generator On Bit

This read/write bit enables the OSC1 pin as the clock input to the MCU, so that the switching process can be initiated. This bit is cleared by reset. This bit is ignored in monitor mode with the internal oscillator bypassed.

- 1 = External clock enabled

- 0 = External clock disabled

#### ECGST — External Clock Status Bit

This read-only bit indicates whether an external clock source is engaged to drive the system clock.

- 1 = An external clock source engaged

- 0 = An external clock source disengaged

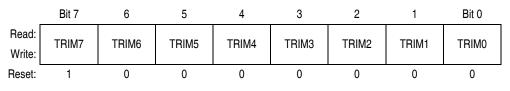

### 11.8.2 Oscillator Trim Register (OSCTRIM)

Figure 11-5. Oscillator Trim Register (OSCTRIM)

### TRIM7–TRIM0 — Internal Oscillator Trim Factor Bits

These read/write bits change the internal capacitance used by the internal oscillator. By measuring the period of the internal clock and adjusting this factor accordingly, the frequency of the internal clock can be fine tuned. Increasing (decreasing) this factor by one increases (decreases) the period by approximately 0.2% of the untrimmed oscillator period. The oscillator period is based on the oscillator frequency selected by the ICFS bits in OSCSC.

Applications using the internal oscillator should copy the internal oscillator trim value at location \$FFC0 into this register to trim the clock source.

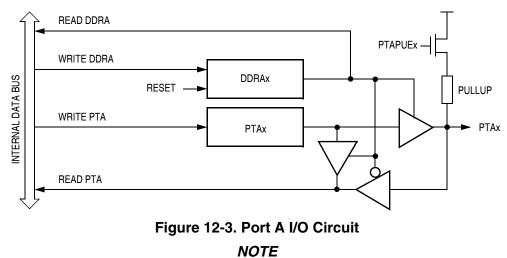

Figure 12-3 does not apply to PTA2

When DDRAx is a 1, reading PTA reads the PTAx data latch. When DDRAx is a 0, reading PTA reads the logic level on the PTAx pin. The data latch can always be written, regardless of the state of its data direction bit.

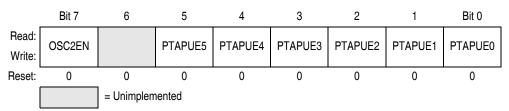

# 12.2.3 Port A Input Pullup Enable Register

The port A input pullup enable register (PTAPUE) contains a software configurable pullup device for each of the port A pins. Each bit is individually configurable and requires the corresponding data direction register, DDRAx, to be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRAx bit is configured as output.

### OSC2EN — Enable PTA4 on OSC2 Pin

This read/write bit configures the OSC2 pin function when internal oscillator or RC oscillator option is selected. This bit has no effect for the XTAL or external oscillator options.

- 1 = OSC2 pin outputs the internal or RC oscillator clock (BUSCLKX4)

- 0 = OSC2 pin configured for PTA4 I/O, having all the interrupt and pullup functions

# PTAPUE[5:0] — Port A Input Pullup Enable Bits

These read/write bits are software programmable to enable pullup devices on port A pins.

- 1 = Corresponding port A pin configured to have internal pullup if its DDRA bit is set to 0

- 0 = Pullup device is disconnected on the corresponding port A pin regardless of the state of its DDRA bit

#### Enhanced Serial Communications Interface (ESCI) Module

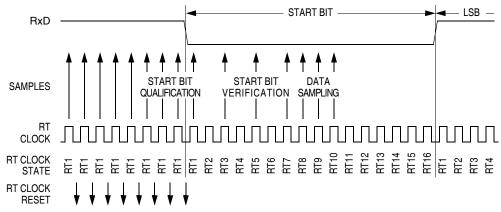

### 13.3.3.3 Data Sampling

The receiver samples the RxD pin at the RT clock rate. The RT clock is an internal signal with a frequency 16 times the baud rate. To adjust for baud rate mismatch, the RT clock is resynchronized at these times (see Figure 13-6):

- After every start bit

- After the receiver detects a data bit change from 1 to 0 (after the majority of data bit samples at RT8, RT9, and RT10 returns a valid 1 and the majority of the next RT8, RT9, and RT10 samples returns a valid 0)

To locate the start bit, data recovery logic does an asynchronous search for a 0 preceded by three 1s. When the falling edge of a possible start bit occurs, the RT clock begins to count to 16.

Figure 13-6. Receiver Data Sampling

To verify the start bit and to detect noise, data recovery logic takes samples at RT3, RT5, and RT7. Table 13-1 summarizes the results of the start bit verification samples.

| RT3, RT5, and RT7 Samples | Start Bit Verification | Noise Flag |

|---------------------------|------------------------|------------|

| 000                       | Yes                    | 0          |

| 001                       | Yes                    | 1          |

| 010                       | Yes                    | 1          |

| 011                       | No                     | 0          |

| 100                       | Yes                    | 1          |

| 101                       | No                     | 0          |

| 110                       | No                     | 0          |

| 111                       | No                     | 0          |

Table 13-1. Start Bit Verification

If start bit verification is not successful, the RT clock is reset and a new search for a start bit begins.

To determine the value of a data bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 13-2 summarizes the results of the data bit samples.

| RT8, RT9, and RT10 Samples | Data Bit Determination | Noise Flag |

|----------------------------|------------------------|------------|

| 000                        | 0                      | 0          |

| 001                        | 0                      | 1          |

| 010                        | 0                      | 1          |

| 011                        | 1                      | 1          |

| 100                        | 0                      | 1          |

| 101                        | 1                      | 1          |

| 110                        | 1                      | 1          |

| 111                        | 1                      | 0          |

Table 13-2. Data Bit Recovery

#### NOTE

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit.

To verify a stop bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 13-3 summarizes the results of the stop bit samples.

| RT8, RT9, and RT10 Samples | Framing Error Flag | Noise Flag |

|----------------------------|--------------------|------------|

| 000                        | 1                  | 0          |

| 001                        | 1                  | 1          |

| 010                        | 1                  | 1          |

| 011                        | 0                  | 1          |

| 100                        | 1                  | 1          |

| 101                        | 0                  | 1          |

| 110                        | 0                  | 1          |

| 111                        | 0                  | 0          |

Table 13-3. Stop Bit Recovery

### 13.3.3.4 Framing Errors

If the data recovery logic does not detect a 1 where the stop bit should be in an incoming character, it sets the framing error bit, FE, in SCS1. A break character also sets the FE bit because a break character has no stop bit. The FE bit is set at the same time that the SCRF bit is set.

### 13.3.3.5 Baud Rate Tolerance

A transmitting device may be operating at a baud rate below or above the receiver baud rate. Accumulated bit time misalignment can cause one of the three stop bit data samples to fall outside the actual stop bit. Then a noise error occurs. If more than one of the samples is outside the stop bit, a framing error occurs. In most applications, the baud rate tolerance is much more than the degree of misalignment that is likely to occur.

As the receiver samples an incoming character, it resynchronizes the RT clock on any valid falling edge within the character. Resynchronization within characters corrects misalignments between transmitter bit times and receiver bit times.

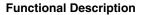

#### 14.4.2.1 Power-On Reset

When power is first applied to the MCU, the power-on reset module (POR) generates a pulse to indicate that power on has occurred. The SIM counter counts out 4096 BUSCLKX4 cycles. Sixty-four BUSCLKX4 cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur.

At power on, the following events occur:

- A POR pulse is generated.

- The internal reset signal is asserted.

- The SIM enables the oscillator to drive BUSCLKX4.

- Internal clocks to the CPU and modules are held inactive for 4096 BUSCLKX4 cycles to allow stabilization of the oscillator.

- The POR bit of the SIM reset status register (SRSR) is set.

See Figure 14-6.

Figure 14-6. POR Recovery

### 14.4.2.2 Computer Operating Properly (COP) Reset

An input to the SIM is reserved for the COP reset signal. The overflow of the COP counter causes an internal reset and sets the COP bit in the SIM reset status register (SRSR). The SIM actively pulls down the RST pin for all internal reset sources.

To prevent a COP module time out, write any value to location \$FFFF. Writing to location \$FFFF clears the COP counter and stages 12–5 of the SIM counter. The SIM counter output, which occurs at least every  $(2^{12} - 2^4)$  BUSCLKX4 cycles, drives the COP counter. The COP should be serviced as soon as possible out of reset to guarantee the maximum amount of time before the first time out.

The COP module is disabled during a break interrupt with monitor mode when BDCOP bit is set in break auxiliary register (BRKAR).

### 14.4.2.3 Illegal Opcode Reset

The SIM decodes signals from the CPU to detect illegal instructions. An illegal instruction sets the ILOP bit in the SIM reset status register (SRSR) and causes a reset.

# Chapter 17 Development Support

# 17.1 Introduction

This section describes the break module, the monitor module (MON), and the monitor mode entry methods.

# 17.2 Break Module (BRK)

The break module can generate a break interrupt that stops normal program flow at a defined address to enter a background program.

Features include:

- Accessible input/output (I/O) registers during the break Interrupt

- Central processor unit (CPU) generated break interrupts

- Software-generated break interrupts

- Computer operating properly (COP) disabling during break interrupts

# 17.2.1 Functional Description

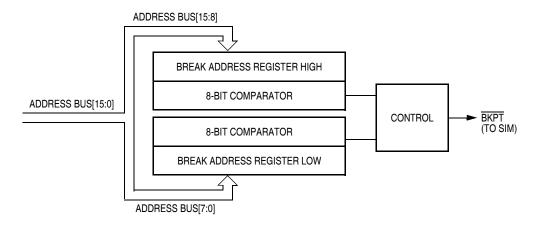

When the internal address bus matches the value written in the break address registers, the break module issues a breakpoint signal (BKPT) to the system integration module (SIM). The SIM then causes the CPU to load the instruction register with a software interrupt instruction (SWI). The program counter vectors to \$FFFC and \$FFFD (\$FEFC and \$FEFD in monitor mode).

The following events can cause a break interrupt to occur:

- A CPU generated address (the address in the program counter) matches the contents of the break address registers.

- Software writes a 1 to the BRKA bit in the break status and control register.

When a CPU generated address matches the contents of the break address registers, the break interrupt is generated. A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the microcontroller unit (MCU) to normal operation.

Figure 17-2 shows the structure of the break module.

When the internal address bus matches the value written in the break address registers or when software writes a 1 to the BRKA bit in the break status and control register, the CPU starts a break interrupt by:

- Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC and \$FFFD (\$FEFC and \$FEFD in monitor mode)

Figure 17-2. Break Module Block Diagram

The break interrupt timing is:

- When a break address is placed at the address of the instruction opcode, the instruction is not executed until after completion of the break interrupt routine.

- When a break address is placed at an address of an instruction operand, the instruction is executed before the break interrupt.

- When software writes a 1 to the BRKA bit, the break interrupt occurs just before the next instruction is executed.

By updating a break address and clearing the BRKA bit in a break interrupt routine, a break interrupt can be generated continuously.

### CAUTION

A break address should be placed at the address of the instruction opcode. When software does not change the break address and clears the BRKA bit in the first break interrupt routine, the next break interrupt will not be generated after exiting the interrupt routine even when the internal address bus matches the value written in the break address registers.

### 17.2.1.1 Flag Protection During Break Interrupts

The system integration module (SIM) controls whether or not module status bits can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See 14.8.2 Break Flag Control Register and the **Break Interrupts** subsection for each module.

### 17.2.1.2 TIM During Break Interrupts

A break interrupt stops the timer counter.

### 17.2.1.3 COP During Break Interrupts

The COP is disabled during a break interrupt in monitor mode when the BDCOP bit is set in the break auxiliary register (BRKAR).

#### **Development Support**

#### BCFE — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

### 17.2.3 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes. If enabled, the break module will remain enabled in wait and stop modes. However, since the internal address bus does not increment in these modes, a break interrupt will never be triggered.

# 17.3 Monitor Module (MON)

The monitor module allows debugging and programming of the microcontroller unit (MCU) through a single-wire interface with a host computer. Monitor mode entry can be achieved without use of the higher test voltage, V<sub>TST</sub>, as long as vector addresses \$FFFE and \$FFFF are blank, thus reducing the hardware requirements for in-circuit programming.

Features include:

- Normal user-mode pin functionality

- One pin dedicated to serial communication between MCU and host computer

- Standard non-return-to-zero (NRZ) communication with host computer

- Standard communication baud rate (7200 @ 2-MHz bus frequency)

- Execution of code in random-access memory (RAM) or FLASH

- FLASH memory security feature<sup>(1)</sup>

- FLASH memory programming interface

- Use of external 9.8304 MHz oscillator to generate internal frequency of 2.4576 MHz

- Simple internal oscillator mode of operation (no external clock or high voltage)

- Monitor mode entry without high voltage, V<sub>TST</sub>, if reset vector is blank (\$FFFE and \$FFFF contain \$FF)

- Normal monitor mode entry if V<sub>TST</sub> is applied to IRQ

### 17.3.1 Functional Description

Figure 17-9 shows a simplified diagram of monitor mode entry.

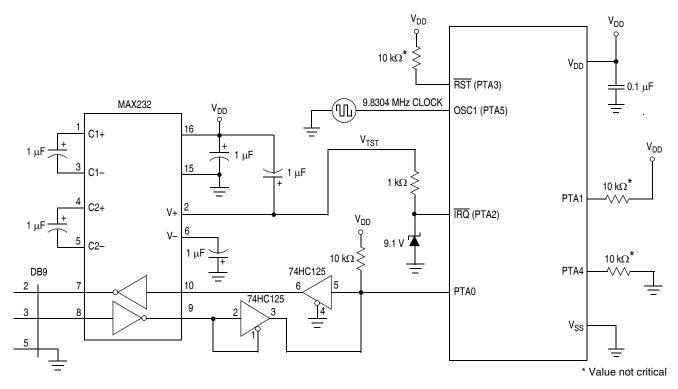

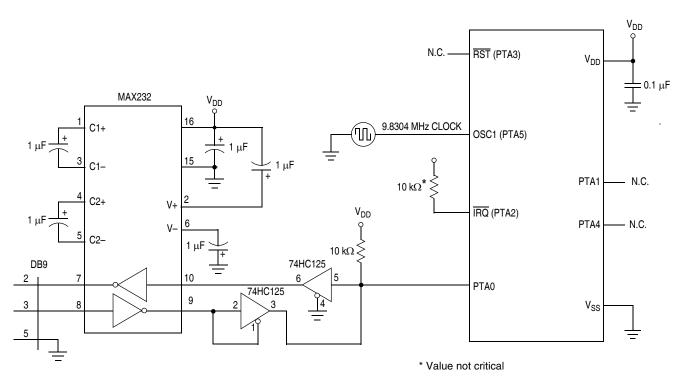

The monitor module receives and executes commands from a host computer. Figure 17-10, Figure 17-11, and Figure 17-12 show example circuits used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute code downloaded into RAM by a host computer while most MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the PTA0 pin. A level-shifting and multiplexing interface is required between PTA0 and the host computer. PTA0 is used in a wired-OR configuration and requires a pullup resistor.

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

Figure 17-10. Monitor Mode Circuit (External Clock, with High Voltage)

Figure 17-11. Monitor Mode Circuit (External Clock, No High Voltage)

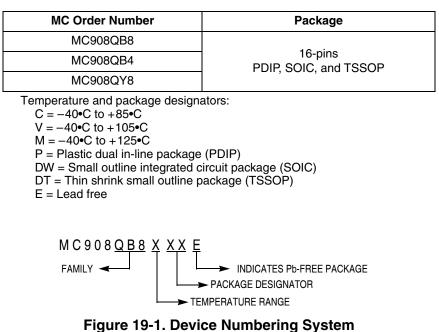

# Chapter 19 Ordering Information and Mechanical Specifications

# **19.1 Introduction**

This section contains order numbers for the MC68HC908QB8, MC68HC908QB4, and MC68HC908QY8. Dimensions are given for:

- 16-pin PDIP

- 16-pin SOIC

- 16-pin thin shrink small outline packages (TSSOP)

# **19.2 MC Order Numbers**

Table 19-1. MC Order Numbers

# **3**

# **19.3 Package Dimensions**

Refer to the following pages for detailed package dimensions.